### ISL98608

High Efficiency Power Supply for Small Size Displays

FN8711 Rev.1.00 Mar 29, 2017

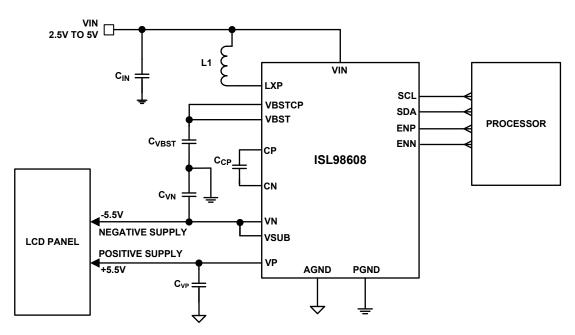

The <u>ISL98608</u> is a high efficiency power supply for small size displays, such as smart phones and tablets requiring  $\pm$ supply rails. It integrates a boost regulator, LDO and inverting charge pump that are used to generate two output rails:  $\pm$ 5.5V (default) and  $\pm$ 5.5V (default). The  $\pm$ 5.5V output voltages can be adjusted from  $\pm$ 4.5V up to  $\pm$ 7V with 50mV steps using the I<sup>2</sup>C interface.

The device integrates synchronous rectification MOSFETs for the boost regulator and inverting charge pump, which maximizes conversion efficiency.

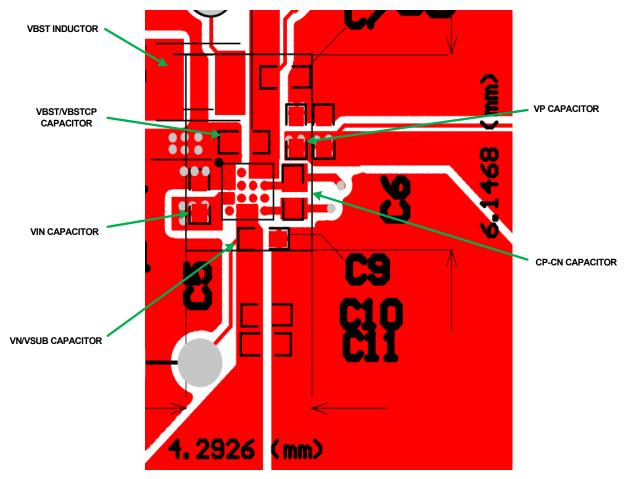

ISL98608 integrates all compensation and feedback components, which minimizes BOM count and reduces the solution PCB size to 18mm<sup>2</sup>.

The input voltage range, high efficiency operation and very low shutdown current make the device ideal for use in single cell Li-ion battery operated applications.

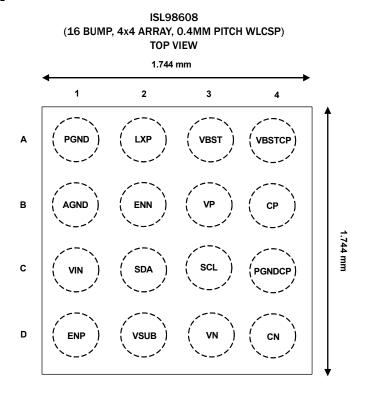

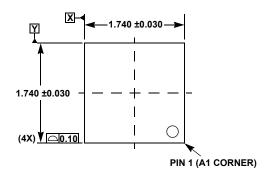

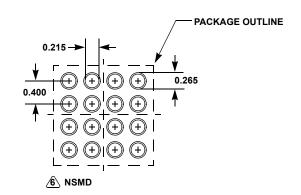

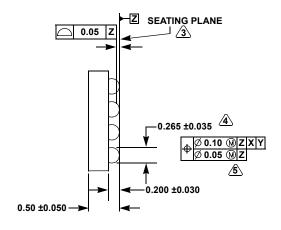

The ISL98608 is offered in a 1.744mm x1.744mm WLCSP package, and the device is specified for operation across the -40 °C to +85 °C ambient temperature range.

### **Features**

- · Two outputs:

- VP = +5.5V (default)

- VN = -5.5V (default)

- · 2.5V to 5V input voltage range

- ±4.5 to ±7V wide output range

- >89% efficiency with 12mA load between VP and VN

- 18mm<sup>2</sup> solution PCB area

- Fully integrated FETs for synchronous rectification

- · Integrated compensation and feedback circuits

- I<sup>2</sup>C adjustable output voltages and settings

- · Integrated VP/VN discharge resistors

- 1µA shutdown supply current

- · Programmable turn-on and turn-off sequencing

- 1.744mm x 1.744mm, 4x4 array WLCSP with 0.4mm pitch

### **Applications**

- · TFT-LCD smart phone displays

- · Small size/handheld displays

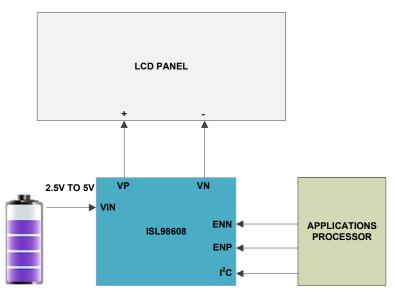

FIGURE 1. TYPICAL APPLICATION CIRCUIT: TFT-LCD SMART PHONE DISPLAY

# **Table of Contents**

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Application Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                    |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                    |

| Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                    |

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                    |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                    |

| Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                    |

| Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                    |

| Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                    |

| Typical Performance Curves                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                    |

| Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 20                                                                                 |

| Description  Modes of Operation  I <sup>2</sup> C Digital Interface  Write Operation  Read Operation  Register Descriptions and Addresses  Register Functions                                                                                                                                                                                                                                                                                               | . 20<br>. 23<br>. 23<br>. 24                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |

| Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 26                                                                                 |

| Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 28<br>. 28<br>. 28<br>. 28<br>. 29<br>. 29                                         |

| Power Supply Function Description  Regulator Output Enable/Disable  VP and VN Headroom Voltage and Output Current  Negative Charge Pump Operation (VN).  VN and VBST PFM  VP Output Hi-Z Mode  Power-On/Off Sequence  Enable Timing Control Options for VP and VN Regulators                                                                                                                                                                                | . 28<br>. 28<br>. 28<br>. 28<br>. 29<br>. 29<br>. 32                                 |

| Display Power Supply Function Description  Regulator Output Enable/Disable  VP and VN Headroom Voltage and Output Current  Negative Charge Pump Operation (VN).  VN and VBST PFM  VP Output Hi-Z Mode  Power-On/Off Sequence  Enable Timing Control Options for VP and VN Regulators  Fault Protection and Monitoring  Component Selection  Input Capacitor.  Inductor.  Output Capacitor                                                                   | . 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 34                         |

| Display Power Supply Function Description  Regulator Output Enable/Disable  VP and VN Headroom Voltage and Output Current  Negative Charge Pump Operation (VN).  VN and VBST PFM  VP Output Hi-Z Mode  Power-On/Off Sequence  Enable Timing Control Options for VP and VN Regulators  Fault Protection and Monitoring  Component Selection  Input Capacitor Inductor Output Capacitor  General Layout Guidelines                                            | . 28<br>. 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 34<br>. 34<br>. 35 |

| Display Power Supply Function Description  Regulator Output Enable/Disable VP and VN Headroom Voltage and Output Current Negative Charge Pump Operation (VN). VN and VBST PFM VP Output Hi-Z Mode Power-On/Off Sequence Enable Timing Control Options for VP and VN Regulators Fault Protection and Monitoring  Component Selection Input Capacitor. Inductor. Output Capacitor General Layout Guidelines  ISL98608 Specific Layout Guidelines.             | . 28<br>. 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 34<br>. 35<br>. 35 |

| Display Power Supply Function Description  Regulator Output Enable/Disable VP and VN Headroom Voltage and Output Current Negative Charge Pump Operation (VN). VN and VBST PFM VP Output Hi-Z Mode Power-On/Off Sequence Enable Timing Control Options for VP and VN Regulators Fault Protection and Monitoring  Component Selection Input Capacitor Inductor Output Capacitor General Layout Guidelines ISL98608 Specific Layout Guidelines ISL98608 Layout | . 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 35<br>. 35<br>. 36         |

| Display Power Supply Function Description  Regulator Output Enable/Disable VP and VN Headroom Voltage and Output Current Negative Charge Pump Operation (VN). VN and VBST PFM VP Output Hi-Z Mode Power-On/Off Sequence Enable Timing Control Options for VP and VN Regulators Fault Protection and Monitoring  Component Selection Input Capacitor. Inductor. Output Capacitor General Layout Guidelines  ISL98608 Specific Layout Guidelines.             | . 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 35<br>. 35<br>. 36         |

| Display Power Supply Function Description  Regulator Output Enable/Disable VP and VN Headroom Voltage and Output Current Negative Charge Pump Operation (VN). VN and VBST PFM VP Output Hi-Z Mode Power-On/Off Sequence Enable Timing Control Options for VP and VN Regulators Fault Protection and Monitoring  Component Selection Input Capacitor Inductor Output Capacitor General Layout Guidelines ISL98608 Specific Layout Guidelines ISL98608 Layout | . 28<br>. 28<br>. 28<br>. 28<br>. 29<br>. 32<br>. 34<br>. 34<br>. 35<br>. 35<br>. 35 |

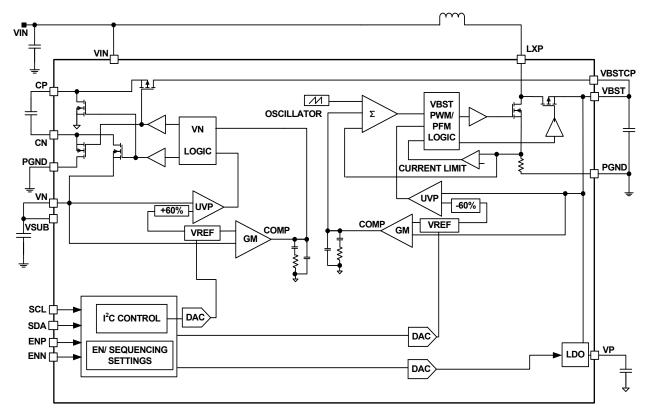

# **Block Diagram**

FIGURE 2. BLOCK DIAGRAM

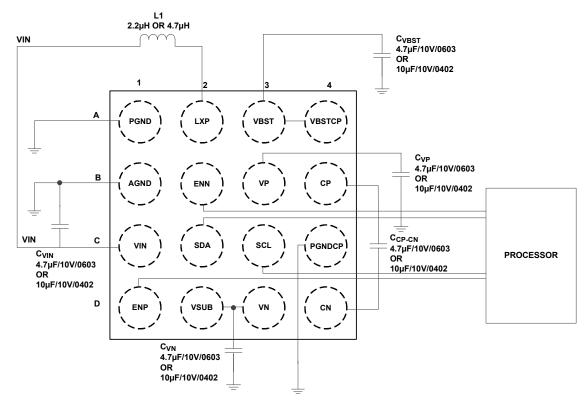

## **Application Circuit Diagram**

FIGURE 3. APPLICATION CIRCUIT DIAGRAM

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP RANGE<br>(°C) | TAPE AND REEL<br>(UNITS) | PACKAGE<br>(Rohs Compliant)           | PKG.<br>DWG. # |

|--------------------------------|-----------------|--------------------|--------------------------|---------------------------------------|----------------|

| ISL98608II55Z-T                | 6085            | -40 to +85         | 3k                       | 16 Ball (4x4 bump, 0.4mm pitch) WLCSP | W4x4.16G       |

| ISL98608IIZ-EVZ                | Evaluation Boar | d                  |                          |                                       |                |

### NOTES:

- 1. Please refer to **IB347** for details on reel specifications.

- These Intersil Pb-free WLCSP packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see product information page for <u>ISL98608</u>. For more information on MSL, please see tech brief <u>TB363</u>.

# **Pin Configuration**

# **Pin Descriptions**

| PIN NUMBER | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                   |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | PGND     | Power ground for the boost converter.                                                                                                                                                                                                                         |

| A2         | LXP      | Switch node for boost converter. Connect an inductor between the VIN and LXP pins for boost converter operation.                                                                                                                                              |

| А3         | VBST     | Boost converter output. The boost converter output supplies the power to the negative charge pump and LDO. Connect a $4.7\mu F/0603$ or $10\mu F/0402$ capacitor to ground.                                                                                   |

| A4         | VBSTCP   | Charge pump input. This pin must be connected to VBST on the PCB, so that the boost regulator provides the input voltage supply for the charge pump.                                                                                                          |

| B1         | AGND     | Analog ground                                                                                                                                                                                                                                                 |

| B2         | ENN      | VBST and VN enable input. (Note 4)                                                                                                                                                                                                                            |

| В3         | VP       | Positive regulator output. Connect a 4.7μF/0603 or 10μF/0402 capacitor to ground.                                                                                                                                                                             |

| В4         | СР       | Charge pump flying capacitor positive connection. Place a capacitor between CP and CN.                                                                                                                                                                        |

| C1         | VIN      | Input supply voltage. Connect a 4.7μF/0603 or 10μF/0402 bypass capacitor from VIN to ground.                                                                                                                                                                  |

| C2         | SDA      | Serial data connection for I <sup>2</sup> C Interface. If this pin not used, connect this pin to VIN.                                                                                                                                                         |

| С3         | SCL      | Serial data connection for I <sup>2</sup> C Interface. If this pin not used, connect this pin to VIN.                                                                                                                                                         |

| C4         | PGNDCP   | Power ground for the VN regulator.                                                                                                                                                                                                                            |

| D1         | ENP      | VBST and VP enable input. (Note 4)                                                                                                                                                                                                                            |

| D2         | VSUB     | Substrate connection. VSUB must be the most negative potential on the IC, connect VSUB to VN.                                                                                                                                                                 |

| D3         | VN       | Negative charge pump output. Connect a $4.7\mu\text{F}/0603$ or $10\mu\text{F}/0402$ capacitor to ground. Connecting either two $4.7\mu\text{F}/0603$ or $10\mu\text{F}/0402$ capacitors to ground will lower the negative charge pump output voltage ripple. |

| D4         | CN       | Charge pump flying capacitor negative connection. Place a capacitor between CP and CN.                                                                                                                                                                        |

NOTE:

<sup>4.</sup> This pin has  $1M\Omega$  (typical) pull-down to AGND.

### **Absolute Maximum Ratings**

| VBST, VBSTCP, CP, VP to AGND              | 0.3V to 8.5V               |

|-------------------------------------------|----------------------------|

| VN to AGND                                | +0.3V to -8.5V             |

| VIN, SCL, SDA, ENN, ENP to AGND           | 0.3V to 6V                 |

| LXP to AGND                               | 0.3V to VBST + 0.3V        |

| CN to AGND                                | (VN - 0.3V) to PGND + 0.3V |

| Maximum Average Current Out of VBST Pin   | 1A                         |

| Maximum Average Current Into LXP Pin      | 1A                         |

| Maximum Average Current Into CN, CP Pin   | 1A                         |

| ESD Rating                                |                            |

| Human Body Model (Tested per JESD22-A11   | .4F)                       |

| Machine Model (Tested per JESD22-A115C)   | 300V                       |

| Charged Device Model (Tested per JESD22-C | 101F)1kV                   |

| Latch-Up (Tested per JESD78D; Class II)   | 100mA                      |

|                                           |                            |

### **Thermal Information**

| Thermal Resistance (Typical)         | $\theta_{JA}$ (°C/W) | $\theta_{JB}(^{\circ}C/W)$ |

|--------------------------------------|----------------------|----------------------------|

| 4x4 Bump 0.4mm pitch WLCSP (Notes 5, | <u>6</u> ) 76        | 18                         |

| Maximum Junction Temperature         |                      | +125°C                     |

| Storage Temperature Range            | 6                    | 5°C to +150°C              |

| Pb-Free Reflow Profile               |                      | see <u>TB493</u>           |

### **Recommended Operating Conditions**

| Ambient Temperature Range                  | 40°C to +85°C   |

|--------------------------------------------|-----------------|

| VIN                                        | 2.5V to 5V      |

| VP                                         | +4.5V to +7V    |

| VN                                         | 4.5V to -7V     |

| VBST                                       | +4.65V to +7.3V |

| Output Current Maximum (between VP and VN) | 100mA           |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. For  $\theta_{JB}$ , the "board temp" is taken on the board near the edge of the package, on a copper trace at the center of one side. See tech brief <u>TB379</u>,

**Electrical Specifications**  $V_{IN} = 3.7V$ , unless otherwise noted. Typical specifications are characterized at  $T_A = +25$ °C unless otherwise noted. **Boldface limits apply across the operating temperature range, -40**°C **to +85**°C.

| PARAMETER                                    | SYMBOL                                               | TEST CONDITIONS                                                             | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNIT |

|----------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|------|-----------------|------|

| GENERAL                                      | •                                                    |                                                                             | <u> </u>        |      |                 |      |

| V <sub>IN</sub> Supply Voltage Range         | I <sub>IN</sub> Supply Voltage Range V <sub>IN</sub> |                                                                             |                 |      |                 | V    |

| V <sub>IN</sub> Supply Current               | I <sub>IN</sub>                                      | ENP = ENN = SDA = SCL = 3.7V<br>Enabled, LXP not switching                  |                 | 700  |                 | μА   |

| V <sub>IN</sub> Supply Current When Shutdown | I <sub>SHUTDN</sub>                                  | ENP = ENN = SDA = SCL = 0V                                                  |                 | 1    |                 | μΑ   |

| Undervoltage Lockout Threshold               | V <sub>UVLO</sub>                                    | V <sub>IN</sub> rising                                                      |                 | 2.32 | 2.44            | ٧    |

| Undervoltage Lockout Hysteresis              | V <sub>UVLO_HYS</sub>                                |                                                                             |                 | 216  |                 | mV   |

| BOOST REGULATOR (VBST)                       | <u>'</u>                                             |                                                                             |                 |      |                 |      |

| VBST Output Voltage                          | V <sub>VBST</sub>                                    | Register 0x06 = 0x00, no load                                               |                 | 5.65 |                 | V    |

| VBST Output Voltage Accuracy                 | V <sub>VBSTA</sub>                                   | 2.5V < V <sub>IN</sub> < 4.6V, Register 0x06 = 0x00                         | -2.5            |      | 2.5             | %    |

| VBST Output Voltage Programmable<br>Range    | V <sub>VBSTR</sub>                                   | Programmable in 50mV steps                                                  | 4.65            |      | 7.30            | V    |

| Boost nFET Current Limit                     | I <sub>LIM_VBST</sub>                                |                                                                             | 1.1             | 1.4  | 1.6             | Α    |

| VBST Output Current                          | I <sub>VBSTO</sub>                                   | 2.5V < V <sub>IN</sub> <5V, VBST = 5.65V, Register 0x06 = 0x00              | 350             |      |                 | mA   |

| Low-Side Switch ON-Resistance                | ron_vbstl                                            | T <sub>A</sub> = +25 °C, I <sub>LOAD_VBST</sub> = 100mA,<br>LXP to PGND     |                 | 110  |                 | mΩ   |

| High-Side Switch ON-Resistance               | ron_vbsth                                            | T <sub>A</sub> = +25°C, I <sub>LOAD_VBST</sub> = 100mA,<br>LXP to VBST      |                 | 145  |                 | mΩ   |

| LXP Leakage Current                          | I <sub>L_LXP</sub>                                   | VLXP = 6V, ENP = ENN = OV                                                   |                 |      | 10              | μΑ   |

| Boost Minimum Duty Cycle                     | D <sub>MIN</sub>                                     | Boost frequency = 1.45MHz                                                   |                 | 12.5 |                 | %    |

| Boost Maximum Duty Cycle                     | D <sub>MAX</sub>                                     | Boost frequency = 1.45MHz                                                   |                 | 91   |                 | %    |

| Boost Switching Frequency                    | f <sub>SWV_VBST</sub>                                | Boost frequency = default                                                   | 1.30            | 1.45 | 1.60            | MHz  |

| Boost Soft-Start Time                        | tss_vbst                                             | C <sub>VBST</sub> = 10μF (not derated), V <sub>IN</sub> > V <sub>UVLO</sub> |                 | 0.59 | 0.85            | ms   |

**Electrical Specifications**  $V_{IN} = 3.7V$ , unless otherwise noted. Typical specifications are characterized at  $T_A = +25$  °C unless otherwise noted. Boldface limits apply across the operating temperature range, -40 °C to +85 °C. (Continued)

| PARAMETER                               | SYMBOL                | TEST CONDITIONS                                                                                                  | MIN<br>(Note 7) | TYP            | MAX<br>(Note 7) | UNIT |

|-----------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-----------------|------|

| NEGATIVE REGULATOR (VN)                 | <b>'</b>              |                                                                                                                  | 1               | 1              |                 |      |

| VN Output Voltage                       | $v_{VN}$              | VN = -5.5V, Register 0x08 = 0x00, No Load                                                                        |                 | -5.5           |                 | ٧    |

| VN Output Voltage Programmable<br>Range | V <sub>VNR</sub>      | Programmable in 50mV steps                                                                                       | -7.0            |                | -4.5            | V    |

| VN Output Voltage Accuracy              | V <sub>ACC_VN</sub>   | VN = -5.5V, Register 0x08 = 0x00, Register<br>0x06 = 0x00, -100mA < I <sub>LOAD_VN</sub> < 0mA                   | -2              |                | 2               | %    |

| Charge Pump Switching Frequency         | fsw_vn                | CP Frequency = default, 50% duty cycle                                                                           | 1.30            | 1.45           | 1.60            | MHz  |

| Charge Pump Leakage Current             | I <sub>L_CP</sub>     | CP pin, CP = 6V, ENN = 0V                                                                                        |                 |                | 10              | μΑ   |

| VN Discharge Resistance                 | R <sub>DCH_VN</sub>   | VN = -1V                                                                                                         |                 | 35             |                 | Ω    |

| VN Soft-Start Time                      | t <sub>SS_VN</sub>    | C <sub>VN</sub> = 10μF (not derated), VN = -5.5V, Register<br>0x08 = 0x00, Register 0x05 b <sub>7</sub> = 0      |                 | 1.96           | 2.39            | ms   |

| POSITIVE REGULATOR (VP)                 |                       |                                                                                                                  |                 | 11             |                 |      |

| VP Output Voltage                       | V <sub>VP</sub>       | VP = 5.5V, Register 0x09 = 0x00, no load                                                                         |                 | 5.5            |                 | ٧    |

| VP Output Voltage Programmable<br>Range | V <sub>VPR</sub>      | Programmable in 50mV steps                                                                                       | 4.5             |                | 7.0             | V    |

| VP Output Voltage Accuracy              | V <sub>ACC_VP</sub>   | VP = 5.5V, Register 0x09 = 0x00, Register<br>0x06 = 0x00, 0mA < I <sub>LOAD_VP</sub> < 100mA                     | -2              |                | 2               | %    |

| VP Dropout Voltage                      | V <sub>DRP_VP</sub>   | I <sub>LOAD_VP</sub> = 100mA                                                                                     |                 |                | 100             | m۷   |

| VP Leakage Current                      | I <sub>L_VP</sub>     | VP pin, VP = 0V, ENP = 0V                                                                                        |                 |                | 2               | μΑ   |

| VP Discharge Resistance                 | R <sub>DCH_VP</sub>   | VP = 1V                                                                                                          |                 | 80             |                 | Ω    |

| VP Soft-Start                           | t <sub>SS_VP</sub>    | $C_{VP}$ = 10 $\mu$ F (not derated), VP = 5.5V, Register 0x05 $b_7$ = 0                                          |                 | 1.23           | 1.53            | ms   |

| PROTECTION                              | -1                    |                                                                                                                  |                 | I              | I               |      |

| Thermal Shutdown Temperature            | T <sub>OFF</sub>      | Die temperature (rising) when the device will disable/shutdown all outputs until it cools by T <sub>HYS</sub> °C |                 | 150            |                 | °C   |

| Thermal Shutdown Hysteresis             | T <sub>HYS</sub>      | Die temperature below T <sub>OFF</sub> °C when the device will re-enable the outputs after shutdown              |                 | 20             |                 | °C   |

| VBST Undervoltage Limit                 | V <sub>UVP_VBST</sub> |                                                                                                                  |                 | 70% of<br>VBST |                 | V    |

| VP Undervoltage Protection Threshold    | V <sub>UVP_VP</sub>   |                                                                                                                  |                 | 60% of VP      |                 | ٧    |

| VN Undervoltage Protection Threshold    | V <sub>UVP_VN</sub>   |                                                                                                                  |                 | 60% of VN      |                 | ٧    |

| Undervoltage Delay                      | V <sub>UVDELAY</sub>  | Undervoltage delay for VBST, VN, VP                                                                              |                 | 100            |                 | μs   |

| LOGIC/DIGITAL                           | 1                     |                                                                                                                  |                 | I .            |                 |      |

| Logic Input Low Voltage                 | V <sub>IL</sub>       | ENN, ENP, SCL, SDA                                                                                               |                 |                | 0.4             | ٧    |

| Logic Input High Voltage                | V <sub>IH</sub>       | ENN, ENP, SCL, SDA                                                                                               | 1.1             |                |                 | ٧    |

| I <sup>2</sup> C SCL Clock Frequency    | fclk                  | (Note 8)                                                                                                         |                 |                | 400             | kHz  |

| Debounce Time                           | t <sub>d</sub>        | ENN, ENP                                                                                                         |                 | 10             |                 | μs   |

| Internal Pull-Down Resistance           | R <sub>EN</sub>       | ENN, ENP                                                                                                         |                 | 1              |                 | МΩ   |

### NOTES:

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 8. For more detailed information regarding I<sup>2</sup>C timing characteristics refer to <u>Table 1 on page 22</u>.

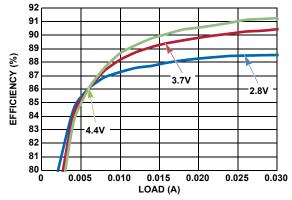

FIGURE 4. DISPLAY POWER SYSTEM EFFICIENCY,  $VP/VN = \pm 5V$

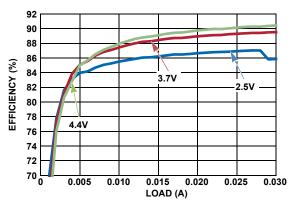

FIGURE 5. DISPLAY POWER SYSTEM EFFICIENCY,  $VP/VN = \pm 5.5V$

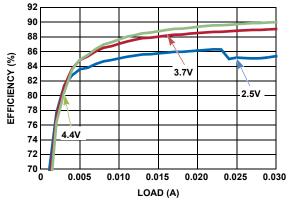

FIGURE 6. DISPLAY POWER SYSTEM EFFICIENCY,  $VP/VN = \pm 6V$

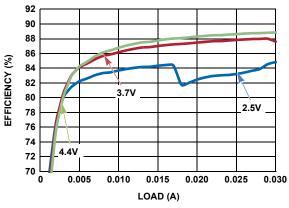

FIGURE 7. DISPLAY POWER SYSTEM EFFICIENCY,  $VP/VN = \pm 7V$

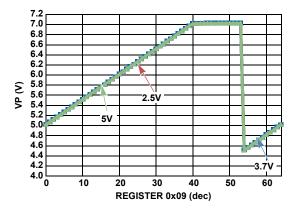

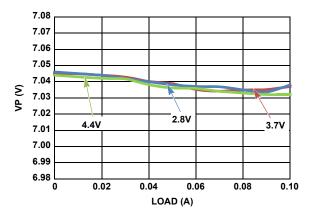

FIGURE 8. VP OUTPUT VOLTAGE RANGE

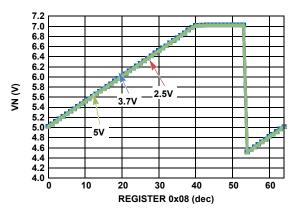

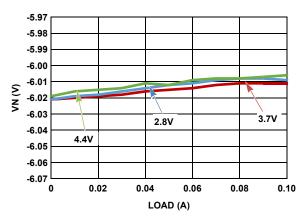

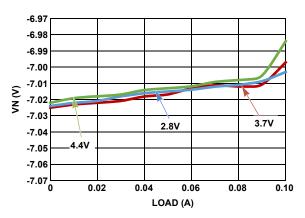

FIGURE 9. VN OUTPUT VOLTAGE RANGE

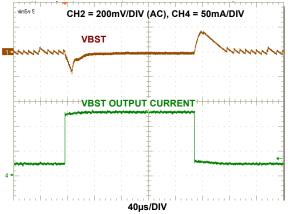

FIGURE 10. VBST LOAD TRANSIENT, VBST = 5.15V

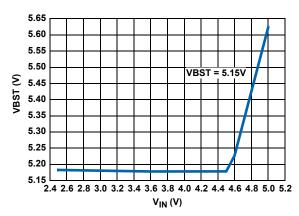

FIGURE 11. VBST, LINE REGULATION, VBST = 5.15V

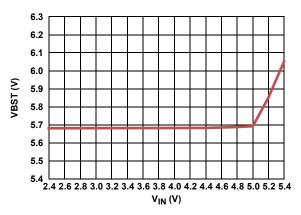

FIGURE 12. VBST, V<sub>IN</sub> HEADROOM TRACKING, VBST = 5.65V

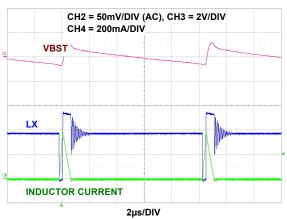

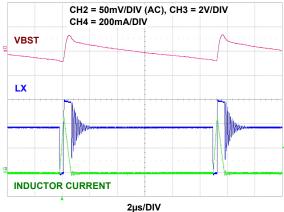

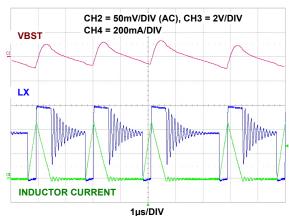

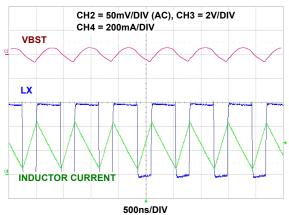

FIGURE 13. VBST RIPPLE, 10mA LOAD, VBST = 5.15V

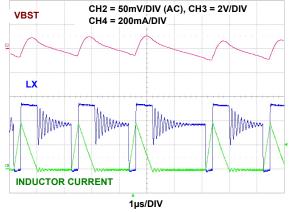

FIGURE 14. VBST RIPPLE, 50mA LOAD, VBST = 5.15V

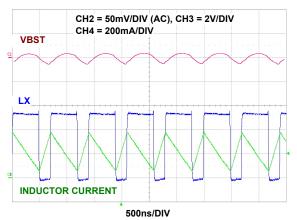

FIGURE 15. VBST RIPPLE, 150mA LOAD, VBST = 5.15V

FIGURE 16. VBST RIPPLE, 10mA LOAD, VBST = 5.65V

FIGURE 17. VBST RIPPLE, 50mA LOAD, VBST = 5.65V

FIGURE 18. VBST RIPPLE, 150mA LOAD, VBST = 5.65V

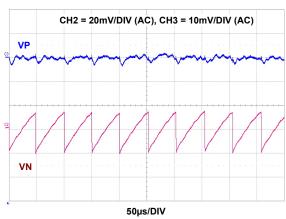

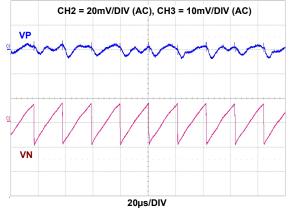

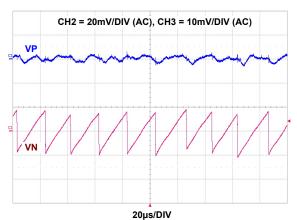

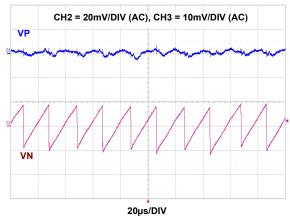

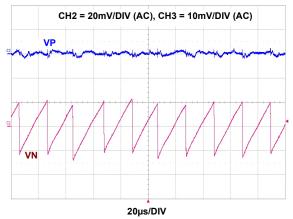

FIGURE 19. VP/VN (±5V) OUTPUT VOLTAGE RIPPLE, 2mA LOAD

FIGURE 20. VP/VN (±5V) OUTPUT VOLTAGE RIPPLE, 5mA LOAD

FIGURE 21. VP/VN ( $\pm5$ V) OUTPUT VOLTAGE RIPPLE, 30mA LOAD

FIGURE 22. VP/VN ( $\pm 5$ V) OUTPUT VOLTAGE RIPPLE, 100mA LOAD

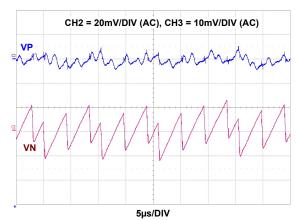

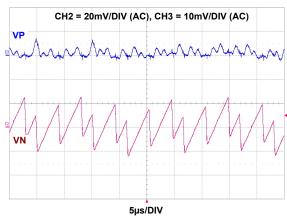

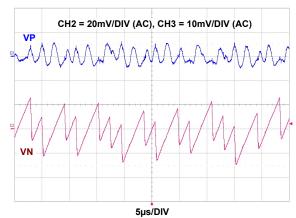

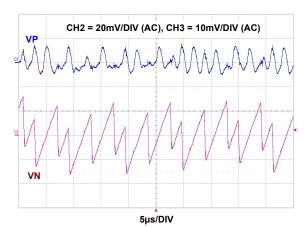

FIGURE 23. VP/VN (±5.5V) OUTPUT VOLTAGE RIPPLE, 2mA LOAD

FIGURE 24. VP/VN ( $\pm 5.5$ V) OUTPUT VOLTAGE RIPPLE, 5mA LOAD

FIGURE 25. VP/VN (±5.5V) OUTPUT VOLTAGE RIPPLE, 30mA LOAD

FIGURE 26. VP/VN ( $\pm 5.5$ V) OUTPUT VOLTAGE RIPPLE, 100mA LOAD

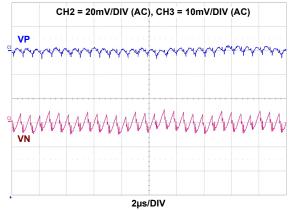

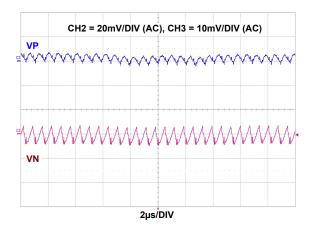

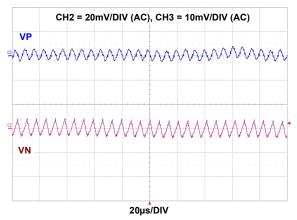

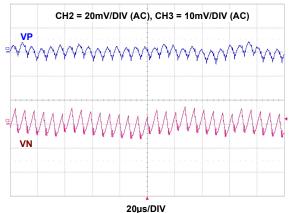

FIGURE 27. VP/VN (±6V) OUTPUT VOLTAGE RIPPLE, 2mA LOAD

FIGURE 28. VP/VN (±6V) OUTPUT VOLTAGE RIPPLE, 5mA LOAD

FIGURE 29. VP/VN ( $\pm 6$ V) OUTPUT VOLTAGE RIPPLE, 30mA LOAD

FIGURE 30. VP/VN (±6V) OUTPUT VOLTAGE RIPPLE, 100mA LOAD

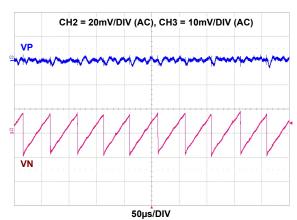

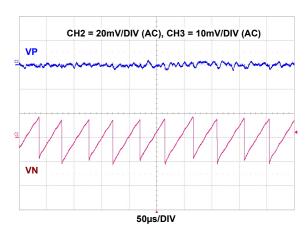

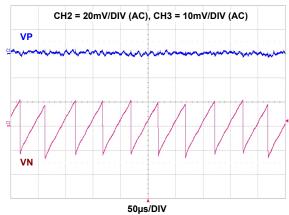

FIGURE 31. VP/VN (±7V) OUTPUT VOLTAGE RIPPLE, 2mA LOAD

FIGURE 32. VP/VN ( $\pm$ 7V) OUTPUT VOLTAGE RIPPLE, 5mA LOAD

FIGURE 33. VP/VN ( $\pm$ 7V) OUTPUT VOLTAGE RIPPLE, 30mA LOAD

FIGURE 34. VP/VN (±7V) OUTPUT VOLTAGE RIPPLE, 100mA LOAD

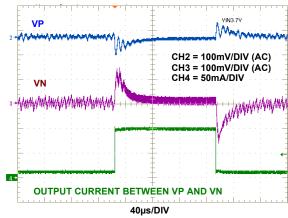

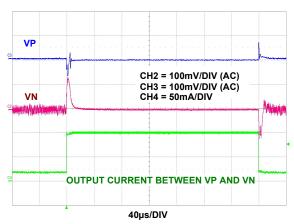

FIGURE 35. VP AND VN LOAD TRANSIENT,  $VP/VN = \pm 5V$

FIGURE 36. VP AND VN LOAD TRANSIENT,  $VP/VN = \pm 5.5V$

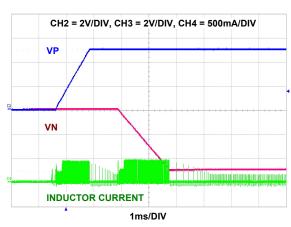

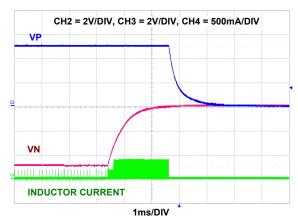

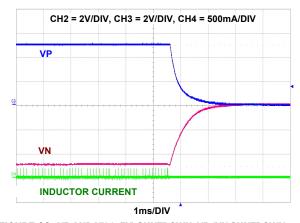

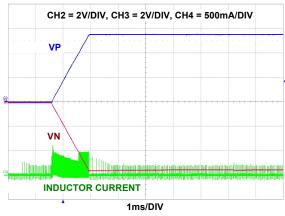

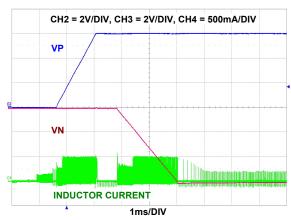

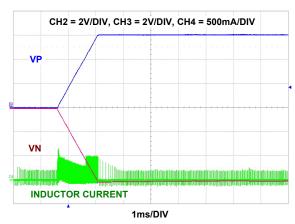

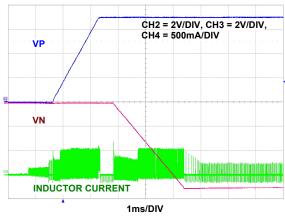

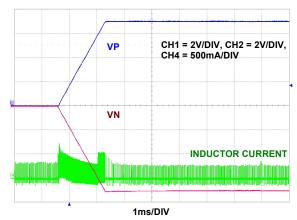

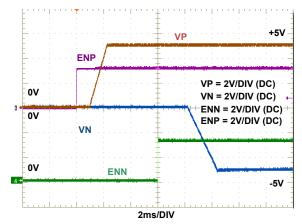

FIGURE 37. VP AND VN ( $\pm$ 5V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>  $\pm$ 0)

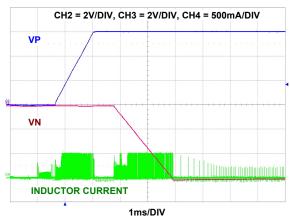

FIGURE 38. VP AND VN ( $\pm$ 5V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 < $b_4$ > = 0)

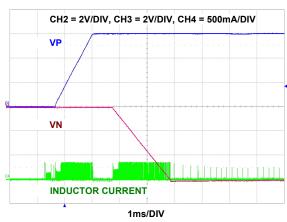

FIGURE 39. VP AND VN ( $\pm$ 5V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>04 >= 0)

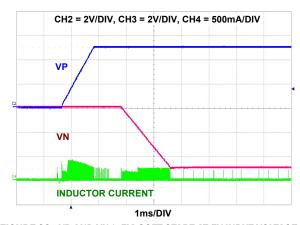

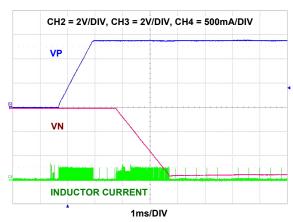

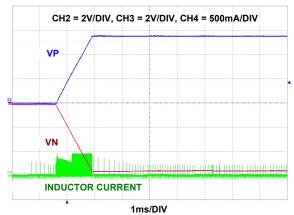

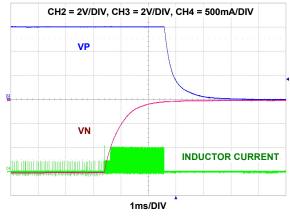

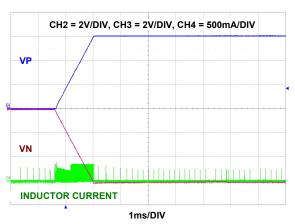

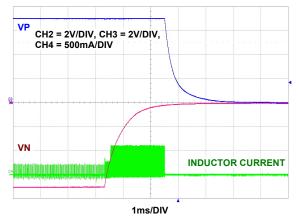

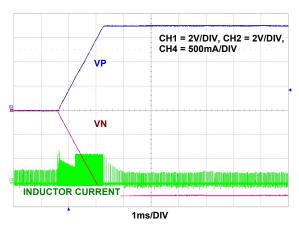

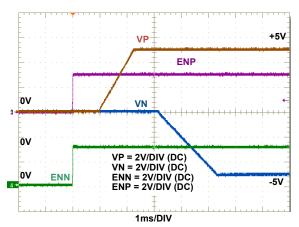

FIGURE 40. VP AND VN ( $\pm$ 5V) SHUTDOWN, VP/VN SEQUENCED (Reg 0x05 <br/>0b4> = 0)

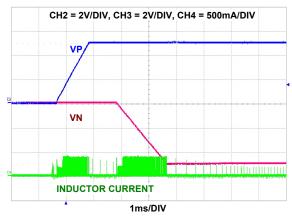

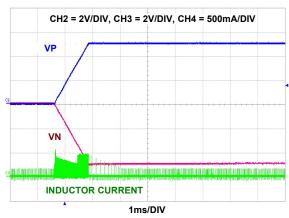

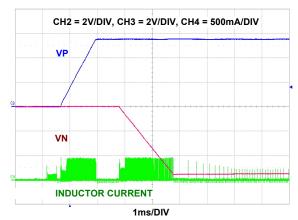

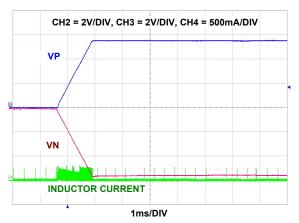

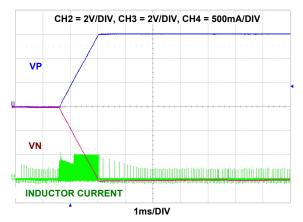

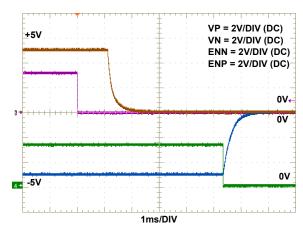

FIGURE 41. VP AND VN ( $\pm$ 5V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 < $b_4$ > = 1)

FIGURE 42. VP AND VN ( $\pm 5$ V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <br/>b4> = 1)

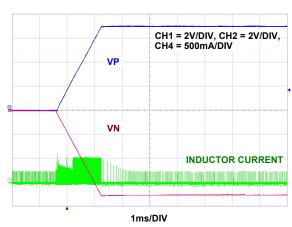

FIGURE 43. VP AND VN ( $\pm 5$ V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <ba/> = 1)

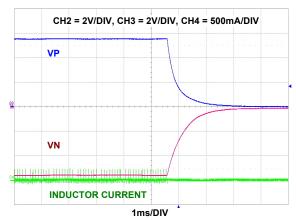

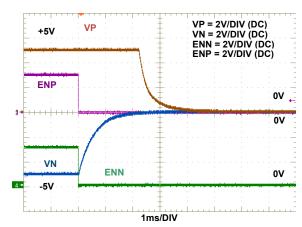

FIGURE 44. VP AND VN ( $\pm 5$ V) SHUTDOWN, VP/VN SHUTDOWN TOGETHER (Reg 0x05 <br/> <br/>  $\pm 1$ )

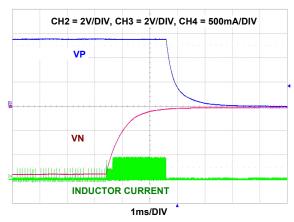

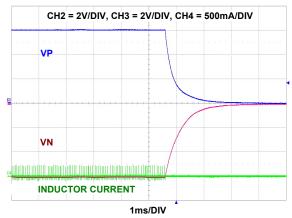

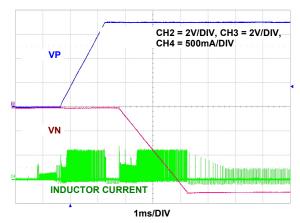

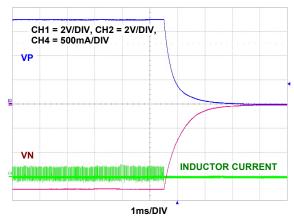

FIGURE 45. VP AND VN ( $\pm 5.5V$ ) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 < $b_4$ > = 0)

FIGURE 46. VP AND VN ( $\pm 5.5V$ ) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <b<sub>4</sub>> = 0)

FIGURE 47. VP AND VN ( $\pm$ 5.5V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>0<sub>4</sub>> = 0)

FIGURE 48. VP AND VN ( $\pm 5.5$ V) SHUTDOWN, VP/VN SEQUENCED (Reg 0x05 <br/>04> = 0)

FIGURE 49. VP AND VN ( $\pm 5.5V$ ) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <b4> = 1)

FIGURE 50. VP AND VN ( $\pm 5.5V$ ) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <ba/>+b4> = 1)

FIGURE 51. VP AND VN ( $\pm$ 5.5V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 < $b_4$ > = 1)

FIGURE 52. VP AND VN ( $\pm$ 5.5V) SHUTDOWN, VP/VN SHUTDOWN TOGETHER (Reg 0x05 <b4> = 1)

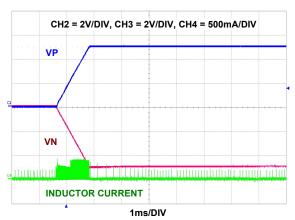

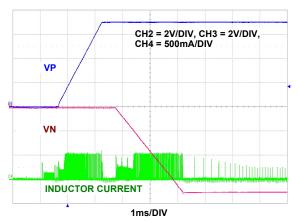

FIGURE 53. VP AND VN ( $\pm$ 6V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>0<sub>4</sub>> = 0)

FIGURE 54. VP AND VN ( $\pm 6$ V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>  $_4$ V= 0)

FIGURE 55. VP AND VN ( $\pm 6V$ ) SOFT-START AT 5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 < $b_4$ > = 0)

FIGURE 56. VP AND VN ( $\pm$ 6V) SHUTDOWN, VP/VN SEQUENCED (Reg 0x05 <br/>  $_4$  > = 0

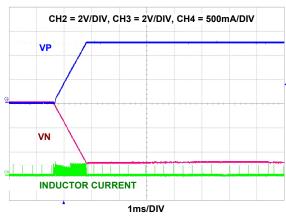

FIGURE 57. VP AND VN ( $\pm$ 6V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 < $b_4$ > = 1)

FIGURE 58. VP AND VN ( $\pm$ 6V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <br/>  $^{4}$ 5 = 1)

FIGURE 59. VP AND VN ( $\pm 6V$ ) SOFT-START AT 5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <ba/>b<sub>4</sub>> = 1)

FIGURE 60. VP AND VN ( $\pm$ 6V) SHUTDOWN, VP/VN SHUTDOWN TOGETHER (Reg 0x05 <b<sub>4</sub>> = 1)

FIGURE 61. VP AND VN ( $\pm$ 7V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>0<sub>4</sub>> = 0)

FIGURE 62. VP AND VN ( $\pm$ 7V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 < $b_4$ > = 0)

FIGURE 63. VP AND VN ( $\pm$ 7V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN SEQUENCED (Reg 0x04 <br/>0<sub>4</sub>> = 0)

FIGURE 64. VP AND VN ( $\pm$ 7V) SHUTDOWN, VP/VN SEQUENCED (Reg 0x05 <br/>04> = 0)

FIGURE 65. VP AND VN ( $\pm$ 7V) SOFT-START AT 2.5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x04 <br/>04>= 1)

FIGURE 66. VP AND VN ( $\pm$ 7V) SOFT-START AT 3.7V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x02 <br/>  $^{6}$  = 1)

FIGURE 67. VP AND VN ( $\pm$ 7V) SOFT-START AT 5V INPUT VOLTAGE, VP/VN START TOGETHER (Reg 0x02 <br/> <br/> = 1)

FIGURE 68. VP AND VN ( $\pm$ 7V) SHUTDOWN, VP/VN SHUTDOWN TOGETHER (Reg 0x05 <br/> <br/> <br/> = 1)

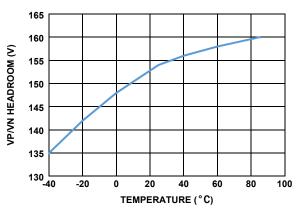

FIGURE 69. VP/VN HEADROOM vs TEMPERATURE

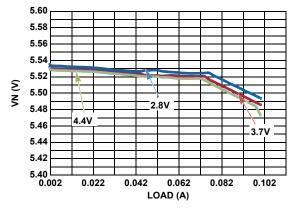

FIGURE 70. VN LOAD REGULATION, -5.5V

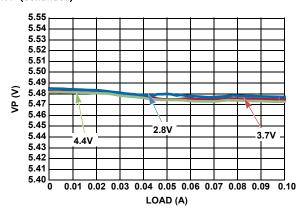

FIGURE 71. VP LOAD REGULATION, 5.5V

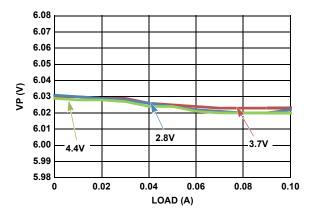

FIGURE 72. VP LOAD REGULATION, VP = 6V

FIGURE 73. VN LOAD REGULATION, VN = -6V

FIGURE 74. VP LOAD REGULATION, VP = 7V

FIGURE 75. VN LOAD REGULATION, VN = -7V

### **Application Information**

### **Description**

The ISL98608 is a display PMIC and can be used to supply power to an LCD display. Figure 76 shows the typical system application block diagram. For display power, the ISL98608 integrates a boost regulator (VBST), low dropout linear regulator (VP) and an inverting charge pump regulator (VN). The boost voltage is generated from a battery voltage ranging from 2.5V to 5V, and boost regulator output can be programmed from 4.60V to 7.3V. The VBST regulator integrates low-side NFET and high-side PFET MOSFETs for synchronous rectification.

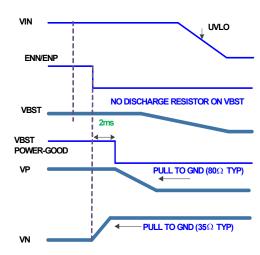

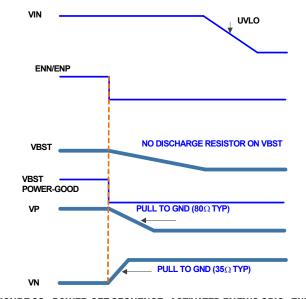

The output voltage of VBST is the input to the linear regulator (VP). The VBST output and VP regulator input are connected internally in the IC. The VP regulator supplies a positive voltage in the range of +4.5V to +7V with 50mV resolution. The output load capability of the VP regulator is 150mA.  $80\Omega$  discharge resistor discharges residual voltage when the power-OFF sequence is initiated, which helps avoid ghost image issues. The LDO is an ideal solution for the positive supply for TFT-LCD panel due to its low ripple, fast load transient response, higher efficiency and low dropout voltage.

The VN voltage is generated by a regulated inverting charge pump topology. VBSTCP is the input to the inverting charge pump, which should be connected to the VBST pin on the PCB. The VN regulator supplies negative voltage from -7V to -4.5V with

50mV resolution. The output load capability of the VN regulator is 150mA. Similar to the VP regulator, the VN regulator also integrates a discharge resistor and the value of discharge resistor is  $35\Omega$ . The VN is an ideal solution for negative supply for TFT-LCD panel due to low ripple, fast load transient response and higher efficiency.

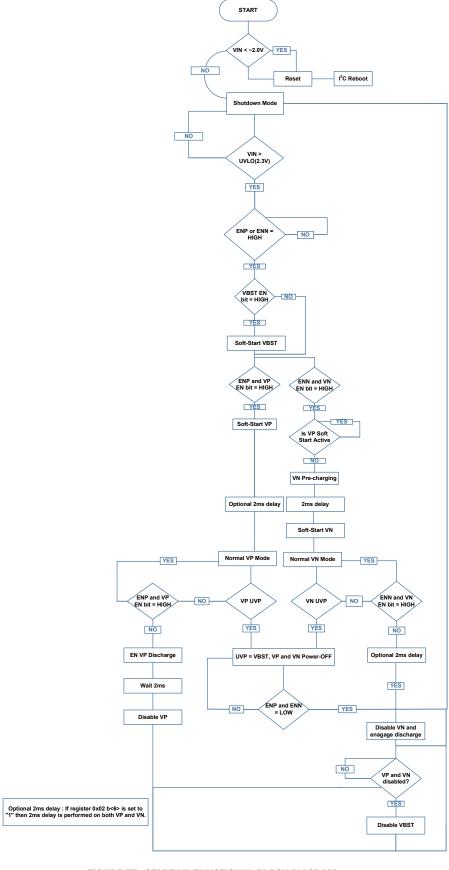

### **Modes of Operation**

#### **SHUTDOWN MODE**

The ISL98608 is in shutdown mode when the enable pins, namely ENN and ENP are pulled low. When the ENN and ENP pins are all pulled low, all the regulators are powered off and the IC is placed in shutdown mode where the current consumed from the battery is only  $1\mu$ A (typical).

### **OPERATING MODE**

The IC is in normal operating mode when the ENN and ENP are pulled high, and the current consumed from the battery is only 1mA (excluding VBST and VN switching current). After the ENN/ENP signals are pulled high, VBST, VP and VN go through power-on sequencing. Refer to "Power-On/Off Sequence" on page 29 for more details.

FIGURE 76. TYPICAL SYSTEM APPLICATION BLOCK DIAGRAM

FIGURE 77. START-UP FUNCTIONAL BLOCK DIAGRAM

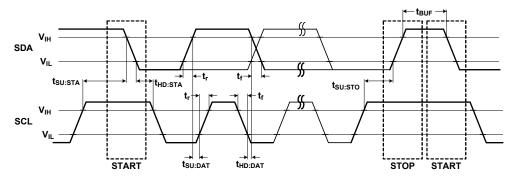

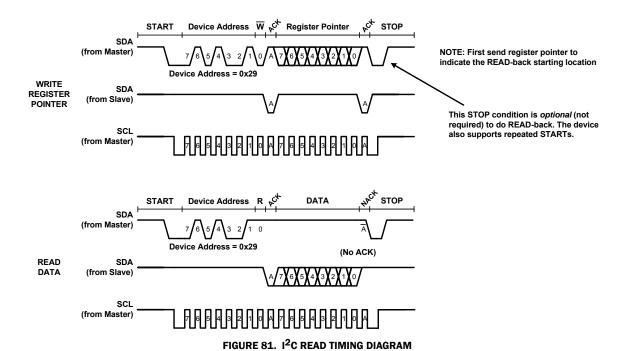

### I<sup>2</sup>C Digital Interface

The ISL98608 uses a standard I $^2$ C interface bus for communication. The two-wire interface links a master(s) and uniquely addressable slave devices. The master generates clock signals and is responsible for initiating data transfers. The serial clock is on the SCL line and the serial data (bidirectional) is on the SDA line. The ISL98608 supports clock rates up to 400kHz (Fast mode), and is backwards compatible with standard 100kHz clock rates (Standard mode).

The SDA and SCL lines must be HIGH when the bus is free - not in use. An external pull-up resistor (typically 2.2k $\Omega$  to 4.7k $\Omega$ ) or current-source is required for SDA and SCL.

The ISL98608 meets standard I<sup>2</sup>C timing specifications, see Figure 78 and Table 1, which show the standard timing definitions and specifications for I<sup>2</sup>C communication.

#### **START AND STOP CONDITION**

All I<sup>2</sup>C communication begins with a START condition - indicating the beginning of a transaction and ends with a STOP condition - signaling the end of the transaction.

A START condition is signified by a HIGH to LOW transition on the serial data line (SDA) while the serial clock line (SCL) is HIGH. A

STOP condition is signified by a LOW to HIGH transition on the SDA line while SCL is HIGH. See timing specifications in <u>Table 1</u>.

The master always initiates START and STOP conditions. After a START condition, the bus is considered "busy." After a STOP condition, the bus is considered "free." The ISL98608 also supports repeated STARTs, where the bus will remain busy for continued transaction(s).

#### **DATA VALIDITY**

The data on the SDA line must be stable (clearly defined as HIGH or LOW) during the HIGH period of the clock signal. The state of the SDA line can only change when the SCL line is LOW (except to create a START or STOP condition). See timing specifications in Table 1.

The voltage levels used to indicate a logical '0' (LOW) and logical '1' (HIGH) are determined by the  $V_{IL}$  and  $V_{IH}$  thresholds, respectively, see the "Electrical Specifications" table on page 7.

### **BYTE FORMAT**

Every byte transferred on SDA must be 8 bits in length. After every byte of data sent by the transmitter there must be an Acknowledge bit (from the receiver) to signify that the previous 8 bits were transferred successfully. Data is always transferred on SDA with the most significant bit (MSB) first. See "Acknowledge (ACK)" on page 23

FIGURE 78. I<sup>2</sup>C TIMING DEFINITIONS

TABLE 1. I<sup>2</sup>C TIMING CHARACTERISTICS

|                                                  | FAST-MODE           |                        |     |     | -MODE |      |

|--------------------------------------------------|---------------------|------------------------|-----|-----|-------|------|

| PARAMETER                                        | SYMBOL              | MIN                    | MAX | MIN | MAX   | UNIT |

| SCL Clock Frequency                              | f <sub>SCL</sub>    | 0                      | 400 | 0   | 100   | kHz  |

| Set-up Time for a START Condition                | t <sub>SU:STA</sub> | 0.6                    | -   | 4.7 | -     | μs   |

| Hold Time for a START Condition                  | t <sub>HD:STA</sub> | 0.6                    | -   | 4.0 | -     | μs   |

| Set-up Time for a STOP Condition                 | t <sub>SU:STO</sub> | 0.6                    | -   | 4.0 | -     | μs   |

| Bus Free Time between a STOP and START Condition | t <sub>BUF</sub>    | 1.3                    | -   | 4.7 | -     | μs   |

| Data Set-up Time                                 | t <sub>SU:DAT</sub> | 100                    | -   | 250 | -     | ns   |

| Data Hold Time                                   | t <sub>HD:DAT</sub> | 0                      | -   | 0   | -     | μs   |

| Rise Time of SDA and SCL (Note 9)                | t <sub>r</sub>      | 20 + 0.1C <sub>b</sub> | 300 | -   | 1000  | ns   |

| Fall Time of SDA and SCL (Note 9)                | t <sub>f</sub>      | 20 + 0.1C <sub>b</sub> | 300 | -   | 300   | ns   |

| Capacitive Load on Each Bus Line (SDA/SCL)       | C <sub>b</sub>      | -                      | 400 | -   | 400   | pF   |

NOTE:

9. C<sub>b</sub> = Total capacitance of one bus line in pF.

### **ACKNOWLEDGE (ACK)**

Each 8-bit data transfer is followed by an Acknowledge (ACK) bit from the receiver. The Acknowledge bit signifies that the previous 8 bits of data was transferred successfully (master to slave or slave to master).

When the master sends data to the slave (e.g., during a WRITE transaction), after the 8<sup>th</sup> bit of a data byte is transmitted, the master tri-states the SDA line during the 9<sup>th</sup> clock. The slave device acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

When the master receives data from the slave (e.g. during a data READ transaction), after the 8<sup>th</sup> bit is transmitted, the slave tri-states the SDA line during the 9<sup>th</sup> clock. The master acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

#### **NOT ACKNOWLEDGE (NACK)**

A Not Acknowledge (NACK) is generated when the receiver does not pull-down the SDA line during the acknowledge clock (i.e., SDA line remains HIGH during the 9<sup>th</sup> clock). This indicates to the master that it can generate a STOP condition to end the transaction and free the bus.

A NACK can be generated for various reasons, for example:

- After an I<sup>2</sup>C device address is transmitted, there is NO receiver with that address on the bus to respond.

- The receiver is busy performing an internal operation (e.g., reset, recall, etc) and cannot respond.

- The master (acting as a receiver) needs to indicate the end of a transfer with the slave (acting as a transmitter).

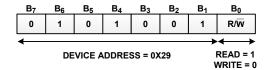

### DEVICE ADDRESS AND R/W BIT

Data transfers follow the format shown in Figures 80 and 81. After a valid START condition, the first byte sent in a transaction contains the 7-bit Device (slave) Address plus a direction ( $R/\overline{W}$ ) bit. The Device Address identifies which device (of up to 127 devices on the  $I^2C$  bus) the master wishes to communicate with.

After a START condition, the ISL98608 monitors the first 8 bits (Device Address Byte) and checks for its 7-bit Device Address in the MSBs. If it recognizes the correct Device Address it will ACK, and becomes ready for further communication. If it does not see its Device Address, it will sit idle until another START condition is issued on the bus.

To access the ISL98608, the 7-bit Device Address is 0x29 (0101001x), located in MSB bits  $\langle b_7 : b_1 \rangle$ . The eighth bit of the Device Address byte (LSB Bit  $\langle b_0 \rangle$ ) indicates the direction of transfer, Read or Write (R/ $\overline{W}$ ). A "0" indicates a Write operation the master will transmit data to the ISL98608 (receiver). A "1" indicates a Read operation - the master will receive data from the ISL98608 (transmitter) (see Figure 79).

FIGURE 79. DEVICE ADDRESS BYTE FORMAT

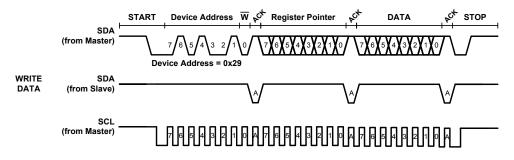

### **Write Operation**

A Write sequence requires an  $I^2C$  START condition, followed by a valid Device Address Byte with the  $R/\overline{W}$  bit set to '0', a valid Register Address Byte, a Data Byte and a STOP condition. After each valid byte is sent, the ISL98608 (slave) responds with an ACK. When the Write transaction is completed, the master should generate a STOP condition. For sent data to be latched by the ISL98608, the STOP condition should occur after a full byte (8 bits) is sent and ACK. If a STOP is generated in the middle of a byte transaction, the data will be ignored. See Figure 80 on page 24 for the ISL98608  $I^2C$  Write protocol.

### **Read Operation**

A READ sequence requires the master to first write to the ISL98608 to indicate the Register Address/pointer to read from. Send a START condition, followed by a valid Device Address Byte with the R/ $\overline{W}$  set to '0' and then a valid Register Address Byte. Then the master generates either a Repeat START condition, or a STOP condition followed by a new START condition and a valid Device Address Byte with the R/ $\overline{W}$  bit set to '1'. Then the ISL98608 is ready to send data to the master from the requested Register Address.

The ISL98608 sends out the Data Byte by asserting control of the SDA pin while the master generates clock pulses on the SCL pin. When transmission of the desired data is complete, the master generates a NACK condition followed by a STOP condition and this completes the I $^2$ C Read sequence. See Figure 81 on page 24 for the ISL98608 I $^2$ C Read protocol.

FIGURE 80. I<sup>2</sup>C WRITE TIMING DIAGRAM

### **Register Descriptions and Addresses**

<u>"Register Map" on page 26</u> contains the detailed register map, with descriptions and addresses for ISL98608 registers. Each volatile register is one byte (8-bit) in size. When writing data to adjust register settings using I<sup>2</sup>C, the data is latched-in after the 8th bit (LSB) is received.

The ISL98608 has default register settings that are applied at IC power-up, and in some cases, updated based on fuse values at first enable. The default register settings are indicated with **BOLD** face text.

NOTE: To clear/reset all the volatile registers to the default values, power cycle VIN or clear the register 0x04 Bit <b $_7>$ .

### **Register Functions**

The ISL98608 has various registers that can be used to adjust and control IC operating voltages, modes, thresholds and sequences.

### **FAULT**

The "FAULT" register (Register Address 0x04) can be used to read back the current fault status of the IC. The fault conditions that can be read back by I<sup>2</sup>C are VBST undervoltage fault, VP undervoltage fault, VN undervoltage fault and over-temperature protection (OTP) fault.

If FAULT register Bit <b $_0>$  (OTP status bit) is latched high for an OTP fault, it can be reset by simultaneously cycling ENP and ENN.

If FAULT register Bit <b $_1>$  (VBST status bit) is latched high for a VBST undervoltage fault, it can be reset by cycling ENP and ENN together.

If FAULT register Bit <br/>b2> (VN status bit) is latched high for a VN undervoltage fault, it can be reset by cycling ENN.

If FAULT register Bit <br/>b<sub>3</sub>> (VP status bit) is latched high for a VP undervoltage fault, it can be reset by cycling ENP.

All fault bits can be cleared by cycling VIN or with a software reboot (clearing register 0x04 bit<br/>bt<br/>b7>). This will reset the entire part to default settings and disable all outputs until they have sequenced up again.

#### **ENABLE**

The "ENABLE" register (Register Address 0x05) can be used to control the enable/disable state of the boost (VBST), positive LDO (VP) and negative charge pump (VN). This can also be used to sequence the regulators. Refer to "Enable Timing Control Options for VP and VN Regulators" on page 32 for details regarding the control of output regulators using the enable and I<sup>2</sup>C control. Using this register the VP and VN pull-down resistor can be enabled or disabled, soft-start time of VP and VN can be adjusted and the timing of VP sequencing can be adjusted.

Bit<4> of ENABLE register controls the delay between the ENP signal going low and the VP regulator power-off. If Bit<4> is set to 0, the VP regulator is disabled 2ms after ENP going low. If Bit<4> is set to 1, the VP regulator is disabled as soon as ENP goes low.

Bit<5> of ENABLE register controls shutdown behavior of VBST, VP and VN regulators after OTP or UV event. If Bit<5> is set to 1, then VBST, VP and VN regulators are shut off after OTP or UV event. To turn on the regulators, IC should be out of fault condition and ENP and ENN signals are recycled. Regulators can also be turned on by recycling the enable bit in the I<sup>2</sup>C register. If Bit<5> is set to 0, then regulators will turn back on as soon as fault condition is removed.

Bit<6> controls the VN and VP discharge resistor. If bit<6> is programmed to "0" then it will enable the discharge resistor where as "1" will disable the discharge resistor.

Bit<7> controls the soft-start time of VN and VP regulators. If bit<7> is set to "0" then soft-start time of VN is 1.8ms and for VP is 1.2ms whereas when set to "1", soft-start time of both VP and VN regulator is 0.7ms.

### **VBST/VN/VN VOLTAGE**

The output voltages of VBST, VP and VN regulators can be changed using the registers "VBST Voltage", "VP Voltage" and "VN Voltage", respectively. VBST Voltage is at Register Address 0x06, VN Voltage is at Register Address 0x08 and VP Voltage is at Register Address 0x09. The output voltages of all regulators can be changed from their default values using  $\rm I^2C$ .

- The VBST regulator can be programmed from +4.65V to +7.3V

- The VP regulator can be programmed from +4.5V to +7V

- The VN regulator can be programmed from -7V to -4.5V

- All are adjustable with 50mV step size.

Once the maximum VBST voltage (7.3V) is reached the algorithm will wrap around to give VBST voltage from 4.65V to 5.1V. Similarly, when maximum VP and VN voltage are reached ( $\pm$ 7V), the algorithm will wrap around to give VP/VN voltage from  $\pm$ 4.5V to  $\pm$ 4.95V.

To determine the expected output voltage for a specific register value, see the following section <u>"Output Voltage Calculation for VBST, VP and VN"</u>.

NOTE: Output voltage registers should not be changed during their respective soft-start sequence.

#### **Output Voltage Calculation for VBST, VP and VN**

The expected output voltage for each regulator can be determined using <u>Equations 1</u> through <u>3</u>. Note, N is the 5-bit register settings from 0x06, 0x08 and 0x09 in decimal.

The expected VBST voltage can be determined using Equation 1.

$$VBST(V) = VBST (Default) + N \times 50mV$$

(EQ. 1)

Once the maximum VBST voltage is reached, the algorithm will wrap around to give VBST voltage from 4.65V to 5.1V.

The expected VP voltage can be determined using Equation 2.

$$VP(V) = VP (Default) + N \times 50 mV$$

(EQ. 2)

Once the maximum VP voltage is reached, the algorithm will wrap around to give VP voltage from 4.50V to 4.95V.

The expected VN voltage can be determined using Equation 3.

$$VN(V) = VN(Default) - N \times 50 \,\text{mV}$$

(EQ. 3)

Once the minimum VN voltage is reached, the algorithm will wrap around to give VN voltage from -4.50V to -4.95V.

**Example Calculations:**

If N = 10 (decimal) VBST (Default) = 5.65V, VP/VN (Default) =  $\pm 5.5V$ :

$$VBST(V) = 5.65V + 10 \times 50mV = 6.15V$$

$$VP(V) = 5.5V + 10 \times 50mV = 6.0V$$

$$VN(V) = -5.5V - 10 \times 50 \text{ mV} = -6.0V$$

The output voltage of the VBST, VP and VN regulators can be changed using non-I $^2$ C control by blowing fuses or I $^2$ C control. When powered up, Registers 0x06, 0x08 and 0x09 read a value of 0x00 and the VBST, VN, VP voltage levels are at respective default voltage. Using I $^2$ C control, the voltage can be changed by changing the value of Registers 0x06, 0x08 and 0x09. As V $_{\rm IN}$  <POR (Power-On Reset) voltage, Registers 0x06, 0x08 and 0x09 read 0x00. Non-I $^2$ C control can also be used to change the default voltage of VBST, VN and VP by blowing fuses and still Registers 0x06, 0x08 and 0x09 read 0x00 on POR. Then, VBST, VN and VP voltage can be changed using I $^2$ C by changing Registers 0x06, 0x08 and 0x09, respectively.

### **VBST CONTROL**

In addition to output voltage adjustments, key operation parameters can be changed using  $I^2C$  to optimize the ISL98608 performance.

The "VBST CNTRL and VBST/VN Frequency" register (Register Address 0x0D) can be used to control boost PFM mode, boost FET slew rate and switching frequency of the boost and charge pump.

# **Register Map**

| REGISTER<br>ADDRESS<br>(HEX) | REGISTER<br>NAME | R/W | FUNCTION                   | BIT <b7></b7>                                                                          | BIT <b6></b6>                                                 | BIT <b<sub>5&gt;</b<sub>                                                                                            | BIT <b4></b4>                                                            | BIT <b3></b3>                                                                       | BIT <b2></b2>                                                     | BIT <b1></b1>                                                                            | BIT <b<sub>0&gt;</b<sub>                                | DEFAULT<br>VALUE<br>(HEX) | IC RESET                                                                                             |

|------------------------------|------------------|-----|----------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|

| 0x04                         | FAULT/<br>STATUS | ,   | Fault Status<br>Read-back  | Reboot 1 = Reset all digital (reverts to 0 once reboot completes) 0 = Normal operation | Not                                                           | used                                                                                                                | Start VP and<br>VN together<br>0 =<br>Sequenced<br>1 = Start<br>together | VP UVP<br>0 = Output<br>Voltage OK<br>1 = UVP<br>Detect if VP<br><60% for<br>>100µs | VN UVP 0 = Output Voltage OK 1 = UVP Detect if VN <60% for >100µs | VBST UVP<br>0 = Output<br>Voltage OK<br>1 = UVP<br>Detect if<br>VBST <70%<br>for >100 µs | OTP 0 = Temp 0k 1 = OTP detected. Temp =130°C for >10µs | 0x00                      | Cycle VIN or Bit 0 - cycle ENN and ENP Bit 1 - cycle ENN and ENP Bit 2 - cycle ENN Bit 3 - Cycle ENP |

| 0x05                         | ENABLE           | R/W | IC Enable/<br>Sequencing   | VP/VN soft-start<br>times<br>0 = VP = 1.2ms<br>VN = 1.8ms<br>1 =<br>VP = VN = 0.7ms    | VP/VN<br>Discharge<br>Resistor<br>0 = Enabled<br>1 = Disabled | Enable shut<br>down of<br>VBST/VP/VN<br>at OTP or if<br>any is UV after<br>start-up.<br>0 = Disabled<br>1 = Enabled | Delay VP off<br>0 = VP off<br>2ms after<br>ENP<br>1 = VP off<br>with ENP | Reserved                                                                            | VP Enable:<br>0 = Disable<br>1 = Enable                           | VN Enable:<br>0 = Disable<br>1 = Enable                                                  | VBST Enable:<br>0 = Disable<br>1 = Enable               | 0x27                      | Cycle VIN or<br>clear the<br>register 0x04<br>Bit <b7></b7>                                          |

| 0x06                         | VBST<br>VOLTAGE  | R/W | VBST Voltage<br>Adjustment | Not Used                                                                               | Once the max                                                  | (Default) + N x 5<br>voltage is reach<br>will wrap aroun<br>.1 options                                              | hed                                                                      |                                                                                     |                                                                   |                                                                                          |                                                         | 0x00                      | Cycle VIN or<br>clear the<br>register 0x04<br>Bit <b7></b7>                                          |

| 0x08                         | VN VOLTAGE       | R/W | VN Voltage<br>Adjustment   | Not Used                                                                               | Once the min                                                  | ult) - N x 50mV<br>voltage is reach<br>will wrap aroun<br>.95 options                                               |                                                                          |                                                                                     |                                                                   |                                                                                          |                                                         | 0x00                      | Cycle VIN or<br>clear the<br>register 0x04<br>Bit <b7></b7>                                          |

| 0x09                         | VP VOLTAGE       | R/W | VP Voltage<br>Adjustment   | Not Used                                                                               | Once the max                                                  | ult) + N x 50mV<br>voltage is reacl<br>will wrap aroun<br>95 options                                                | ned                                                                      |                                                                                     |                                                                   |                                                                                          |                                                         | 0x00                      | Cycle VIN or<br>clear the<br>register 0x04<br>Bit <b7></b7>                                          |

# Register Map (Continued)

| REGISTER<br>ADDRESS<br>(HEX) |                                             | R/W | FUNCTION                                    | BIT <b<sub>7&gt;</b<sub> | BIT <b6></b6> | BIT <b<sub>5&gt;</b<sub>                                        | BIT <b4></b4>  | BIT <b3></b3>                       | BIT <b2></b2>                                                                                                                       | BIT <b1></b1>                    | BIT <b<sub>0&gt;</b<sub> | DEFAULT<br>VALUE<br>(HEX) | IC RESET                                                    |

|------------------------------|---------------------------------------------|-----|---------------------------------------------|--------------------------|---------------|-----------------------------------------------------------------|----------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------|---------------------------|-------------------------------------------------------------|

| OxOD                         | VBST control<br>and<br>VBST/VN<br>FREQUENCY | R/W | VBST Control<br>and<br>VBST/VN<br>Frequency | Reserved                 | Reserved      | Power FET slev  00 = Sowest  01 = Slow  10 = Fast  11 = Fastest | v rate control | PFM mode  0 = Enabled  1 = Disabled | VBST and VN<br>000 = 1.00M<br>001 = 1.07M<br>010 = 1.23M<br>011 = 1.33M<br>100 = 1.45M<br>101 = 1.60M<br>110 = 1.78M<br>111 = 2.00M | Hz<br>Hz<br>Hz<br>Hz<br>Hz<br>Hz | uency                    | OxB4                      | Cycle VIN or<br>clear the<br>register 0x04<br>Bit <b7></b7> |

# **Display Power Supply Function Description**

### **Regulator Output Enable/Disable**

The boost converter, VBST, will be enabled whenever either ENP or ENN is HIGH and the VBST enable Bit <br/>

to <br/>

register is set to '1'. To disable the boost (and effectively VP and VN), ENN and ENP must be LOW, or its enable bit set to '0'.

The negative charge pump, VN, is enabled whenever ENN is HIGH and the VN enable Bit <b<sub>1</sub>> in the ENABLE register is set to '1'. To disable, ENN must be LOW, or its enable bit set to '0'.

The LDO, VP, is enabled whenever ENP is HIGH and the VP enable Bit <b<sub>2</sub>> in the ENABLE register is set to '1'. To disable ENP must be LOW, or its enable bit set to '0'.

All the ENABLE register bits  $<b_2:b_0>$  are set to '1' by default.

Note, ENP and ENN are logic level inputs with HIGH/LOW thresholds defined by the  $V_{IH}/V_{IL}$  specifications, respectively. These inputs also have 1M $\Omega$  (typical) internal pull-down resistance to ground. If the pins are left high-impedance, they will default to a LOW logic state. Refer to the "LOGIC/DIGITAL" on page 7 of the "Electrical Specifications" table for more information.

# **VP and VN Headroom Voltage and Output Current**

The VP and VN headroom voltage is defined as the difference between the VBST target voltage and maximum of VP and |VN| target voltages.

The headroom voltage must be set high enough so that both the VP LDO and VN negative Charge Pump (CP) can maintain regulation. The VBST voltage must be greater than the absolute value of the VN regulation voltage (i.e., the headroom voltage has to be >0V). Primarily, the minimum headroom voltage is a function of the maximum application load current that the IC will need to support. Fast output current peaks of only a few microseconds should not be considered - those instantaneous current peaks will be supported by the output capacitors and not by the regulator. Equation 4 shows the minimum headroom required depending upon the current.

Headroom(V) > Imax(A)X2.7 (EQ. 4)

NOTE: The headroom voltage should not be set overly high, since increasing headroom generally yields lower efficiency performance due to increased conduction losses.

For very low duty cycle where the output voltage of the VBST is very close to the input voltage, VBST starts to track the input voltage with a fixed headroom of ~600mV. This feature avoids the minimum duty cycle limitation from producing increased ripple on VBST (which feeds through to VP/VN) and ensures proper regulation of the VBST, VP and VN regulators.

For most applications, the ISL98608 default 150mV headroom voltage setting provides optimal performance for DC output current up to 100mA (maximuml). For DC output current between 100mA and 150mA (maximuml), the headroom voltage should be adjusted to 250mV. For example, if a maximum VP to

VN load of 150mA is required, while VP = 5.5V and VN = -5.5V, then the minimum boost voltage should be set to VBST = 5.75V.

### **Negative Charge Pump Operation (VN)**

The ISL98608 uses a negative charge pump with internal switches to create the VN voltage rail. The charge pump input voltage VBSTCP comes from the boost regulator output, VBST.

Regulation is achieved through a classic voltage mode architecture where an internally compensated integrator output is compared with the voltage ramp to set a duty cycle. The duty cycle controls the amount of time the output capacitor is charged during each switching cycle. The maximum duty cycle is 50%. The charge pump output capacitor (placed on the VN pin) is charged and discharged through internal current source to minimize system noise.

### **VN and VBST PFM**

The ISL98608 features light-load Pulse Frequency Modulation (PFM) mode for both the boost regulator and the charge pump, to maximize efficiency at light loads.

The device always uses PWM mode at heavy loading, but will automatically switch to PFM mode at light loads to optimize efficiency. PFM capability is enabled using the respective PFM mode enable/disable register bits.

#### **VBST PFM**

In PFM mode, the boost can be configured to either use a fixed peak current, or to automatically select the optimal peak current setting. The automatic, or "Auto" mode, is designed to dynamically adjust the peak current to maintain boost output voltage ripple at relatively fixed levels across input voltage, while improving efficiency at low input voltages. This patent pending architecture adjusts the peak current to keep the sum of inductor ramp-up and ramp-down times to a constant value of approximately 1.3\*Tpwm. This scheme also gives more consistent ripple part-to-part and keeps PWM/PFM hysteresis defined in a smaller and more optimal band across operating voltages. It is recommended to operate the part in this mode.

The VBST PFM mode features an ultrasonic Audio Band Suppression (ABS) mode, which prevents the switching frequency from falling below 30kHz to avoid audible noise. When the time interval between two consecutive switching cycles in PFM mode is more than 33ms (i.e., 30kHz frequency) the regulator reduces the peak inductor current, to maintain the frequency at 30kHz. If this is not sufficient, the regulator will add low current reverse current cycles.

### **VN PFM**

The charge pump PFM mode works by increasing the minimum pump on-time, and thereby the charge delivered per cycle, when the load is low. This allows increased ripple to be traded off against switching losses.

### **VP Output Hi-Z Mode**

The ISL98608 VP and VN regulator can be configured in a Hi-Z mode to prevent any leakage current flowing between VP and VN when the TFT-LCD is in sleep/standby mode. Using  $I^2C$  register  $0x05 < b_6 >$  can be used to disable the pull-down resistors on VP and VN giving a "Hi-Z" state of output.

### Power-On/Off Sequence

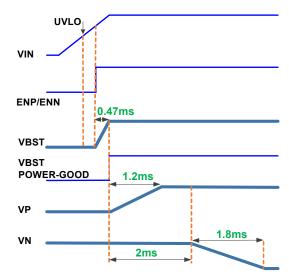

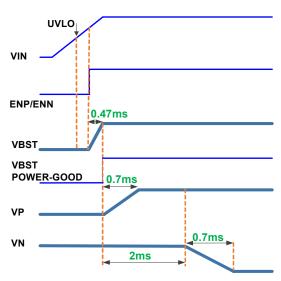

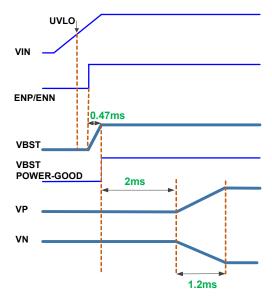

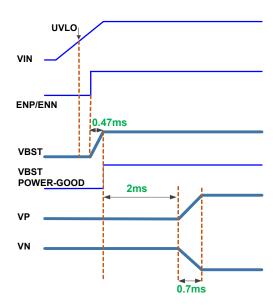

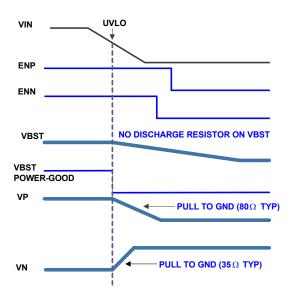

The boost regulator used to generate VP/VN, VBST, is activated when the VIN input voltage is higher than the UVLO threshold, and either ENP or ENN is high, along with their respective  $I^2C$  enable bits. To enable the VBST, Reg 0x05  $<\!b_0\!>$  should be 1 (by default this bit is set to 1). The VP output is activated if ENP is high, VBST has completed its soft-start and Reg 0x05  $<\!b_2\!>$  is 1 (by default this bit is set to 1). The VN charge pump is activated 2ms after VBST has completed soft-start, and the ENN has been pulled high, whichever comes later. To activate the VN regulator, Reg 0x05  $<\!b_1\!>$  should also be 1 (by default this bit is set to 1).

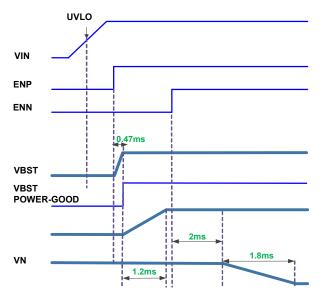

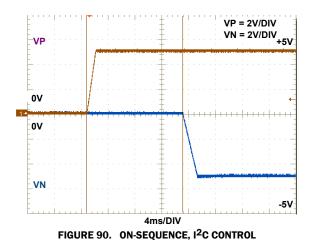

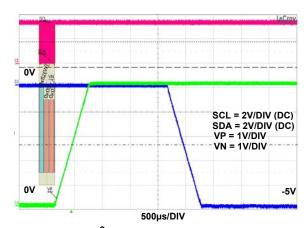

Figure 82 shows the power-on sequence for the case when the ENP and ENN all are tied together and VP/VN rail sequencing is enabled in register  $0x04 < b_4 > by$  writing "0" and VP soft-start time is 1.2ms where as VN soft-start time is 1.8ms programmed from register  $0x05 < b_7 > by$  writing "1". The VBST soft-starts if the VIN voltage is higher than the UVLO threshold and either ENN or ENP is high. When the VBST soft-start is completed, the VP regulator soft-starts in 1.2ms. The VN power-on occurs 2ms after VBST soft-start completes. The VN soft-start time takes 1.8ms. The 2ms power-on delay between VP and VN can be disabled from register  $0x04 < b_4 > by$  writing "1".

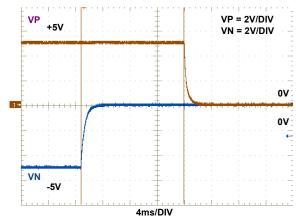

Figure 83 shows the power-on sequence for the case when the ENP and ENN all are tied together and VP/VN rail sequencing is enabled in register 0x04<b4> by writing "0" and VP/VN soft-start time is programmed to 0.7ms from register 0x05<b7> by writing "0". The VBST soft-starts if the VIN voltage is higher than the UVLO threshold and either ENN or ENP is high. When the VBST soft-start is completed, the VP regulator soft-starts in 0.7ms. The VN power-on occurs 2ms after VBST soft-start completes. The VN soft-start time takes 0.7ms. The 2ms power-on delay between VP and VN can be disabled from register 0x04<ba /> by writing "1".

Figure 84 shows the power-on sequence for the case when the ENP and ENN all are tied together and VP/VN rail sequencing is disabled in register 0x04<b4> by writing "1" and VP/VN soft-start time is programmed to 1.2ms from register 0x05<b7> by writing "0". The VBST soft-starts if the VIN voltage is higher than the UVLO threshold and either ENN or ENP is high. When the VBST soft-start is completed, the VP and VN regulator soft-starts in 1.2ms.