# ISP12160A/33 and ISP12160A/66 Intelligent, Dual SCSI Processors

## Data Sheet

## Features

- Available in two versions (collectively referred to as *ISP12160A*), with a maximum transfer rate of 528 Mbytes/sec over the PCI bus:

- □ 66-MHz, 64-bit PCI host bus interface

- □ 33-MHz, 64-bit PCI host bus interface

- Compliance with *PCI Local Bus Specification* rev 2.1

- Compliance with ANSI draft T10/1302D SCSI-3 Parallel Interface (SPI-3)

- Supports Ultra3 SCSI

- SCSI feature set: dual transition, cyclical redundancy check (CRC), domain validation

- Compliance with *PCI Bus Power Management* Interface Specification revision 1.0 (PC98)

- Two concurrently operating wide, Ultra3 SCSI channels

- Up to 160 Mbytes/sec parallel SCSI transfer rates per channel

- Supports single-ended, low voltage differential (LVD) SCSI

- SCSI initiator and target modes of operation

- Onboard RISC processor to execute operations at the I/O control-block level from the host memory

- Supports PCI dual-address cycle (64-bit addressing)

- No host intervention required to execute SCSI operations from start to finish

- Simultaneous, multiple logical threads

- JTAG boundary scan support

## **Product Description**

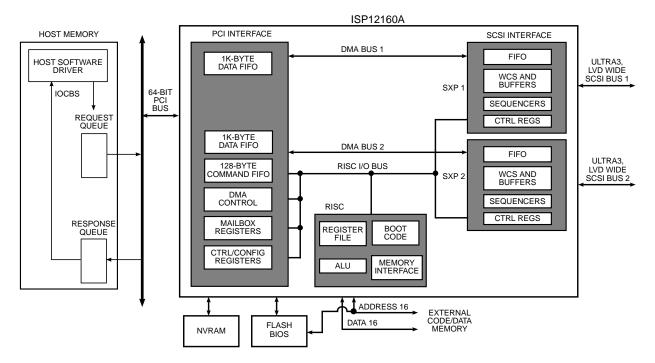

The ISP12160A supports dual channel, Ultra3 (Fast-80) SCSI functionality and is pin compatible with QLogic's ISP12160 Ultra3 SCSI processor as well as QLogic's ISP1280 dual SCSI processor. The product is a single-chip, highly integrated bus master, dual-channel SCSI I/O processor for SCSI initiator and target applications. This device interfaces the PCI bus to two Ultra3 SCSI buses and contains an onboard RISC processor. The product is a fully autonomous device, capable of managing multiple I/O operations and associated data transfers from start to finish without host intervention. The ISP12160A provides power management feature support in accordance with the *PCI Bus Power Management Interface Specification*. The ISP12160A is host-software compatible with the QLogic ISP12160 chip. The ISP12160A block diagram is illustrated in figure 1.

### **ISP Initiator and Target Firmware**

The ISP12160A firmware implements a cooperative, multitasking host adapter that provides the host system with complete SCSI command and data transport capabilities, thus freeing the host system from the demands of the SCSI bus protocol. The firmware provides two interfaces to the host system: the command interface and the SCSI transport interface. The single-threaded command interface facilitates debugging, configuration, and error recovery, while the multithreaded SCSI transport interface maximizes use of the SCSI and host buses. The ISP12160A can switch between initiator and target modes.

#### **Software Drivers**

Software drivers are available for all major operating systems. ISP12160A BIOS firmware is also available.

## **Subsystem Organization**

To maximize I/O throughput and improve host and SCSI bus utilization, the ISP12160A incorporates a high-speed proprietary RISC processor; an intelligent SCSI bus controller (SCSI executive processor [SXP]); and a host bus, dual-channel DMA controller. The SCSI bus controller and the host bus DMA controller operate independently and concurrently under the control of the onboard RISC processor for maximum system performance. The ISP12160A RISC interface requires external program and data memory.

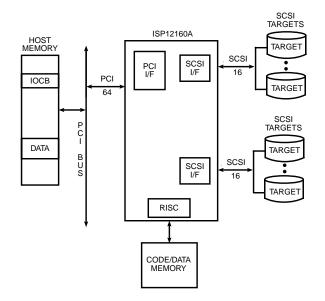

The complete I/O subsystem solution including the ISP12160A and associated supporting memory devices is shown in figure 2.

Figure 1. ISP12160A Block Diagram

Figure 2. I/O Subsystem Design Using the ISP12160A

## **Product Architecture**

The following sections describe the ISP12160A modules.

### **PCI Interface**

The ISP12160A PCI interface supports the following:

- 33-MHz or 66-MHz, 64-bit, intelligent bus master interface

- 64-bit (address and data), intelligent bus master, burst DMA host interface for fetching I/O control blocks and data transfers

- Supports PCI dual-address cycle (64-bit memory addressing)

- Backward compatible to 32-bit PCI

- Triple-channel DMA controller

- Two 1K-byte data DMA FIFOs and a 128-byte command DMA FIFO with threshold control

- 16-bit PCI target mode for communication with host

- Pipelined DMA registers for efficient scatter and gather operations

- 32-bit DMA transfer counter for I/O transfer lengths of up to four gigabytes

- Support for subsystem ID

- Support for flash BIOS PROM and serial NVRAM

- Support for PCI cache commands

- 3.3-V and 5.0-V tolerant PCI I/O buffers

The ISP12160A is designed to interface directly to the PCI bus and operate as a 64-bit DMA bus master. This operation is accomplished through a PCI bus interface unit (PBIU) that contains an onboard DMA controller. The PBIU generates and samples PCI control signals, generates host memory addresses, and facilitates the transfer of data between host memory and the onboard DMA FIFO. It also allows the host to access the ISP12160A internal registers and communicate with the onboard RISC processor through the PCI target mode operation.

The ISP12160A supports the minimum power management capabilities specified in revision 1.0 of the *PCI Bus Power Management Interface Specification*, which defines power states D0-D3, where D0 provides maximum power consumption and D3 provides minimal power consumption. The D3 power state is entered by either software (D3 *hot*) or by physically removing power (D3 *cold*). Hot and cold refer to the presence or absence of VCC, respectively.

The ISP12160A supports power states D0, D3 hot, and D3 cold.

The ISP12160A onboard DMA controller consists of three independent DMA channels that initiate transactions on the PCI bus and transfer data between the host memory and DMA FIFO. The three DMA channels consist of one command DMA channel and two data DMA channels. The command DMA channel is used mainly by the RISC processor for small transfers such as fetching commands from and writing status information to the host memory over the PCI bus. The data DMA channels transfer data between the two SCSI buses and the PCI bus. The PBIU internally arbitrates between the data DMA channels and the command DMA channel and alternately services them. Each DMA channel has a set of DMA registers that are programmed for transfers by the RISC processor.

#### **SCSI Executive Processor**

The ISP12160A SXP supports the following:

- Ultra (Fast-20), Ultra2 (Fast-40), and Ultra3 (Fast-80) SCSI synchronous data transfer rates up to 160 Mbytes/sec

- Asynchronous SCSI data transfer rates up to 12 Mbytes/sec

- Programmable SCSI processor

- □ Specialized instruction set with 16-bit microword

- $\Box$  512x16 internal RAM control store

- 32-bit, configurable SCSI transfer counter

- Command, status, message in, and message out buffers

- Device information storage area

- On-chip, LVD SCSI transceivers

- Programmable active negation

The SXP provides an autonomous, intelligent SCSI interface capable of handling complete SCSI operations. The SXP interrupts the RISC processor only to handle higher level functions such as threaded operations or error handling.

#### **RISC Processor**

The ISP12160A RISC processor supports the following:

- Execution of multiple I/O control blocks from the host memory

- Reduced host intervention and interrupt overhead

- One interrupt or less per I/O operation

The onboard RISC processor enables the ISP12160A to handle complete I/O transactions with no intervention from the host. The ISP12160A RISC processor controls the chip interfaces; executes simultaneous, multiple input/output control blocks (IOCB); and maintains the required thread information for each transfer.

#### **Interfaces**

The ISP12160A interfaces consist of the 64-bit PCI bus interface, two SCSI interfaces, RISC interface, BIOS PROM interface, and NVRAM interface. Pins that support these interfaces and other chip operations are shown in figure 3.

## Packaging

The ISP12160A is available in a 492-pin plastic ballgrid array (PBGA) package.

|                              |                                              | FLASHCS   | ISP12160A | ACK1-2/ACK1-2 4/       |                               |

|------------------------------|----------------------------------------------|-----------|-----------|------------------------|-------------------------------|

| FLASH BIOS PROM<br>INTERFACE |                                              | FLASHOE   |           | ATN1-2/ATN1-2 4        | SCSI BUS 1 AND 2<br>INTERFACE |

|                              |                                              | FLASHWR   |           | BSY1-2/BSY1-2 4        |                               |

|                              | 8/                                           | PDATA7-0  |           | CD1-2/CD1-2 4          |                               |

|                              |                                              |           |           | DIFFS1/DIFFS2 2/       |                               |

|                              |                                              |           |           | IO1-2/IO1-2 4          | 1                             |

|                              | ·                                            |           |           | MSG1-2/MSG1-2 4/       |                               |

| DIGO                         | 4/                                           | ECS3-0    |           | REQ1-2/REQ1-2          |                               |

| RISC<br>INTERFACE            |                                              | IF        |           |                        |                               |

|                              |                                              | ĪOCS      |           | SD1[15-0]/SD1[15-0] 32 |                               |

|                              | 16/                                          | RADDR15-0 |           | <                      | •                             |

|                              | 16                                           | RDATA15-0 |           | SD2[15-0]/SD2[15-0] 32 | •                             |

|                              | <b>↓</b> → →                                 | RDPAR     |           | SDP1[1-2]/SDP1[1-2] 4  |                               |

|                              | ←                                            | RISCSTB   |           | SDP2[1-2]/SDP2[1-2] 4  |                               |

|                              |                                              | ROE       |           | SEL1-2/SEL1-2 4        |                               |

|                              | ←                                            | TRIG      |           |                        | 110                           |

|                              |                                              | WE        |           |                        |                               |

|                              | <b>←</b>                                     |           |           | NVCLK                  | NVRAM                         |

|                              | 1                                            |           |           | NVCS                   | INTERFACE                     |

|                              | 1                                            | ACK64     |           | NVDATI                 |                               |

| PCI BUS<br>INTERFACE         | _ 64/                                        | AD63-0    |           | NVDATO                 |                               |

|                              | < <u> </u>                                   | BCLK      |           |                        | 4                             |

|                              |                                              | BGNT      |           |                        |                               |

|                              |                                              | BREQ      |           | BIAS1_RES/BIAS2_RES 2/ | MISCELLANEOUS                 |

|                              | 4 8/                                         | CBE7-0    |           | BSYLED1-2 2            |                               |

|                              | <b>∢                                    </b> | DEVSEL    |           | CLK                    |                               |

|                              | <u> </u>                                     | FRAME     |           | CLKOUT                 |                               |

|                              | 4                                            | IDSEL     |           | CMDCH                  |                               |

|                              |                                              | INTA >    |           | DATCH1/DATCH2 2/       |                               |

|                              | *                                            | IRDY      |           | GPIO3-0 4              |                               |

|                              | ٠                                            | M66EN     |           |                        |                               |

|                              |                                              | PAR       |           | NC (NO CONNECT) 30/    |                               |

|                              | <                                            | PAR >     |           | PLLCNT                 |                               |

|                              | <                                            | PERR      |           | PLLFILTER              |                               |

|                              | 4                                            | REQ64     |           | PLLTD                  |                               |

|                              | ۰                                            | >         |           | POD                    |                               |

|                              |                                              |           |           | тск                    |                               |

|                              | ۰                                            |           |           | TDI                    |                               |

|                              | *                                            | STOP      |           | TDO                    |                               |

|                              | <b>«</b>                                     |           |           | TEST5                  |                               |

|                              | J                                            |           |           | TEST4-0 5/             |                               |

|                              | 1                                            |           |           | TMS                    |                               |

| POWER<br>AND GROUND          | 12/                                          | VDD4      |           | TRST                   |                               |

|                              | 28                                           | VDD       |           | TSTOUT                 |                               |

|                              | 4                                            | VDDS5     |           |                        | 60                            |

|                              | <i>,</i>                                     | VDDA      |           |                        |                               |

|                              | 18,                                          | VDDSCSI   |           |                        |                               |

|                              | 92,                                          | VSS       |           |                        |                               |

|                              |                                              | VSSA      |           |                        |                               |

|                              | 18,                                          | VSSSCSI   |           |                        |                               |

|                              |                                              |           |           |                        |                               |

Figure 3. ISP12160A Functional Signal Grouping

Specifications are subject to change without notice. QLogic is a trademark of QLogic Corporation.

glogic

©March 22, 1999 QLogic Corporation, 3545 Harbor Blvd., Costa Mesa, CA 92626, (800) ON-CHIP-1 or (714) 438-2200

4