# IT8782F

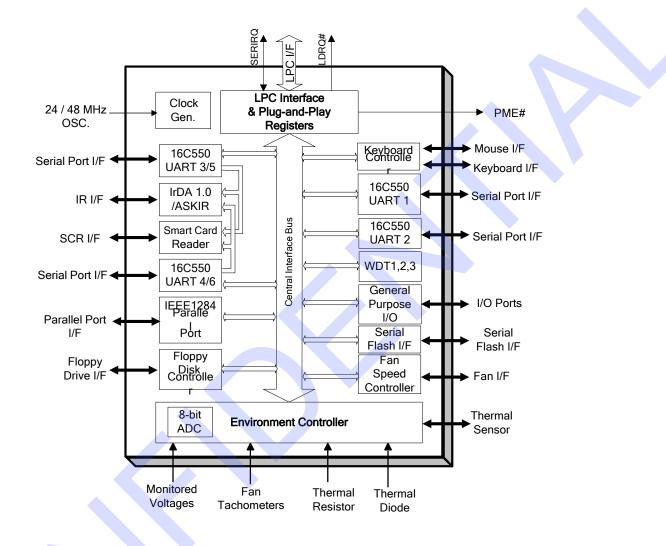

Environment Control – Low Pin Count Input / Output (EC - LPC I/O)

# **Preliminary Specification V0.2.1**

(For A Version)

# ITE TECH. INC.

Specification subject to Change without notice, AS IS and for reference only. For purchasing, please contact sales representatives. Please note that the IT8782F V0.2.1 is applicable to A version and future versions.

#### Copyright © 2012 ITE Tech. Inc.

This is Preliminary document release. All specifications are subject to change without notice. The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE Tech. Inc. for the latest document(s).

All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8782F is a trademark of ITE Tech. Inc. All other trademarks are claimed by their respective owners. All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE Tech. Inc.

Phone:

(02) 29126889

Marketing Department

Fax:

(02) 2910-2551, 2910-2552

7F, No. 233-1, Baociao Rd., Sindian City,

Taipei County 23145, Taiwan, R.O.C.

Fax:

(02) 2910-2551, 2910-2552

If you have any marketing or sales questions, please contact: **P.Y. Chang**, at ITE Taiwan: E-mail: <u>p.y.chang@ite.com.tw</u>, Tel: 886-2-29126889 X6052, Fax: 886-2-29102551

To find out more about ITE, visit our World Wide Web at: http://www.ite.com.tw

Or e-mail itesupport@ite.com.tw for more product information/services

### **Revision History**

| Section | Revision                                                                | Page No. |

|---------|-------------------------------------------------------------------------|----------|

| -       | For registers without default values, note regarding its impact on VIN, | -        |

|         | TEMP, and FAN's detection and way to prevent it added.                  |          |

## CONTENTS

| 1. | Featu  | ires           |                                                                                                                     | 1  |

|----|--------|----------------|---------------------------------------------------------------------------------------------------------------------|----|

| 2. | Gene   | ral Desci      | ription                                                                                                             | 3  |

| 3. | Block  | Diagram        | ·<br>1                                                                                                              | 5  |

|    |        | •              | ion                                                                                                                 |    |

|    |        | •              | Descriptions                                                                                                        |    |

|    |        |                |                                                                                                                     |    |

|    |        |                | Pins                                                                                                                |    |

|    |        |                | apping Options and Special Pin Routings                                                                             |    |

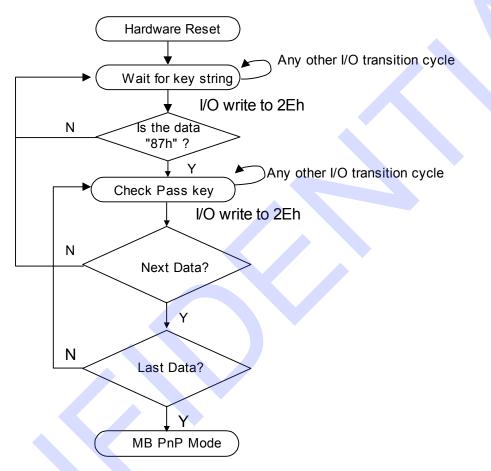

| 8. | Config | guration       |                                                                                                                     | 31 |

|    | 8.1    |                | Iring Sequence Description                                                                                          |    |

|    | 8.2    | Descrip        | tion of Configuration Registers                                                                                     | 32 |

|    |        | 8.2.1          | Logical Device Base Address                                                                                         |    |

|    | 8.3    | Global         | Configuration Registers (LDN: All)                                                                                  |    |

|    |        | 8.3.1          | Configure Control (Index=02h)                                                                                       |    |

|    |        | 8.3.2          | Logical Device Number (LDN, Index=07h)                                                                              |    |

|    |        | 8.3.3          | Chip ID Byte 1 (Index=20h, Default=87h)                                                                             |    |

|    |        | 8.3.4          | Chip ID Byte 2 (Index=21h, Default=82h).                                                                            | 39 |

|    |        | 8.3.5          | Configuration Select and Chip Version (Index=22h, Default=00h)                                                      |    |

|    |        | 8.3.6          | Clock Selection Register (Index=23h, Default=00h)                                                                   |    |

|    |        | 8.3.7          | Software Suspend and Flash I/F Control Register (Index=24h, Default=0000s0s0b, ME                                   |    |

|    |        | 8.3.8          | PnP)<br>GPIO Set 1 Multi-function Pin Selection Register (Index=25h, Default=01h)                                   | 40 |

|    |        |                | GPIO Set 2 Multi-Function Pin Selection Register (Index=26h, Default=01h)                                           |    |

|    |        |                | GPIO Set 3 Multi-Function Pin Selection Register (Index=20h, Default=00h)                                           |    |

|    |        |                | GPIO Set 4 Multi-Function Pin Selection Register (Index=28h, Default=40h)                                           |    |

|    |        |                | GPIO Set 5 Multi-Function Pin Selection Register (Index=29h, Default=00h)                                           |    |

|    |        |                | Extended 1 Multi-Function Pin Selection Register (Index=2Ah, Default=00h)                                           |    |

|    |        |                | Logical Block Lock Register (Index=2Bh, Default=00h)                                                                |    |

|    |        |                | Extended 2 Multi-Function Pin Selection Register (Index=2Ch, Default=03h)                                           |    |

|    |        |                | Test 1 Register (Index=2Eh, Default=00h)                                                                            |    |

|    |        |                | Test 2 Register (Index=2Fh, Default=00h)                                                                            |    |

|    | 8.4    | FDC Co         | onfiguration Registers (LDN=00h)                                                                                    | 47 |

|    |        | 8.4.1          | FDC Activate (Index=30h, Default=00h)                                                                               |    |

|    |        | 8.4.2          | FDC Base Address MSB Register (Index=60h, Default=03h)                                                              |    |

|    |        | 8.4.3          | FDC Base Address LSB Register (Index=61h, Default=F0h)                                                              |    |

|    |        | 8.4.4          | FDC Interrupt Level Select (Index=70h, Default=06h)                                                                 |    |

|    |        | 8.4.5          | FDC DMA Channel Select (Index=74h, Default=02h)                                                                     |    |

|    |        | 8.4.6          | FDC Special Configuration Register 1 (Index=F0h, Default=00h)                                                       | 47 |

|    | 0.5    | 8.4.7          | FDC Special Configuration Register 2 (Index=F1h, Default=00h)                                                       | 48 |

|    | 8.5    |                | Port 1 Configuration Registers (LDN=01h)                                                                            |    |

|    |        | 8.5.1<br>8.5.2 | Serial Port 1 Activate (Index=30h, Default=00h)<br>Serial Port 1 Base Address MSB Register (Index=60h, Default=03h) |    |

|    |        | 8.5.2<br>8.5.3 | Serial Port 1 Base Address ISB Register (Index=60h, Default=03h)                                                    |    |

|    |        | 8.5.4          | Serial Port 1 Interrupt Level Select (Index=70h, Default=04h)                                                       |    |

|    |        | 8.5.5          | Serial Port 1 Special Configuration Register 1 (Index=F0h, Default=04h)                                             |    |

|    | 8.6    |                | Port 2 Configuration Registers (LDN=02h)                                                                            |    |

|    | 0.0    | 8.6.1          | Serial Port 2 Activate (Index=30h, Default=00h)                                                                     |    |

|    |        | 8.6.2          | Serial Port 2 Base Address MSB Register (Index=60h, Default=02h)                                                    |    |

|    |        | 8.6.3          | Serial Port 2 Base Address LSB Register (Index=61h, Default=F8h)                                                    |    |

|    |        |                |                                                                                                                     |    |

|      | 8.6.4   | Serial Port 2 Interrupt Level Select (Index=70h, Default=03h)                         | 50   |

|------|---------|---------------------------------------------------------------------------------------|------|

|      | 8.6.5   | Serial Port 2 Special Configuration Register 1 (Index=F0h, Default=00h)               | 50   |

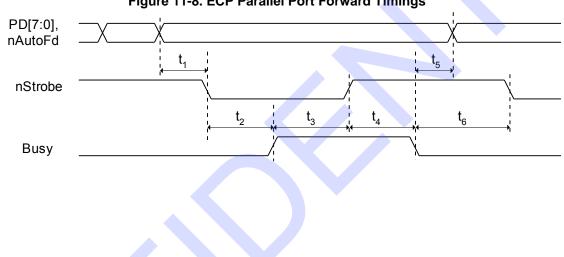

| 8.7  | Paralle | Port Configuration Registers (LDN=03h)                                                | 51   |

|      | 8.7.1   | Parallel Port Activate (Index=30h, Default=00h)                                       |      |

|      | 8.7.2   | Parallel Port Primary Base Address MSB Register (Index=60h, Default=03h)              | 51   |

|      | 8.7.3   | Parallel Port Primary Base Address LSB Register (Index=61h, Default=78h)              | .51  |

|      | 8.7.4   | Parallel Port Secondary Base Address MSB Register (Index=62h, Default=07h)            | .51  |

|      | 8.7.5   | Parallel Port Secondary Base Address LSB Register (Index=63h, Default=78h)            | 52   |

|      | 8.7.6   | Parallel Port Interrupt Level Select (Index =70h, Default=07h)                        | 52   |

|      | 8.7.7   | Parallel Port DMA Channel Select (Index=74h, Default=03h)                             |      |

|      | 8.7.8   | Parallel Port Special Configuration Register (Index=F0h, Default=03h)                 | 52   |

| 8.8  | Environ | ment Controller Configuration Registers (LDN=04h)                                     |      |

|      | 8.8.1   | Environment Controller Activate Register (Index=30h, Default=00h)                     |      |

|      | 8.8.2   | Environment Controller Base Address MSB Register (Index=60h, Default=02h)             |      |

|      | 8.8.3   | Environment Controller Base Address LSB Register (Index=61h, Default=90h)             |      |

|      | 8.8.4   | PME Direct Access Base Address MSB Register (Index=62h, Default=02h)                  |      |

|      | 8.8.5   | PME Direct Access Base Address LSB Register (Index=63h, Default=30h)                  |      |

|      | 8.8.6   | Environment Controller Interrupt Level Select (Index=70h, Default=09h)                |      |

|      | 8.8.7   | APC/PME Event Enable Register (PER) (Index=F0h, Default=00h)                          |      |

|      | 8.8.8   | APC/PME Status Register (PSR) (Index=F1h, Default=00h)                                |      |

|      | 8.8.9   | APC/PME Control Register 1 (PCR 1) (Index=F2h, Default=00h)                           |      |

|      |         | Environment Controller Special Configuration Register (Index=F3h, Default=00h)        |      |

|      |         | APC/PME Control Register 2 (PCR 2) (Index=F4h, Default=00h)                           |      |

|      |         | APC/PME Special Code Index Register (Index=F5h)                                       |      |

|      |         | APC/PME Special Code Data Register (Index=F6h)                                        |      |

| 8.9  |         | eyboard) Configuration Registers (LDN=05h)                                            | 57   |

|      | 8.9.1   | KBC (keyboard) Activate (Index=30h, Default=01h)                                      | 57   |

|      | 8.9.2   | KBC (keyboard) Data Base Address MSB Register (Index=60h, Default=00h)                |      |

|      | 8.9.3   | KBC (keyboard) Data Base Address LSB Register (Index=61h, Default=60h)                |      |

|      | 8.9.4   | KBC (keyboard) Command Base Address MSB Register (Index=62h, Default=00h)             |      |

|      | 8.9.5   | KBC (keyboard) Command Base Address LSB Register (Index=63h, Default=64h)             |      |

|      | 8.9.6   | KBC (keyboard) Interrupt Level Select (Index=70h, Default=01h)                        |      |

|      | 8.9.7   | KBC (keyboard) Interrupt Type (Index=71h, Default=02h)                                |      |

|      | 8.9.8   | KBC (keyboard) Special Configuration Register (Index=F0h, Default=08h)                |      |

| 8.10 |         | nouse) Configuration Registers (LDN=06h)                                              |      |

|      |         | KBC (mouse) Activate (Index=30h, Default=00h)                                         |      |

|      |         | KBC (mouse) Interrupt Level Select (Index=70h, Default=0Ch)                           |      |

|      |         | KBC (mouse) Interrupt Type (Index=71h, Default=02h)                                   |      |

|      |         | KBC (mouse) Special Configuration Register (Index=F0h, Default=00h)                   |      |

| 8.11 |         | Configuration Registers (LDN=07h)                                                     |      |

|      |         | SMI# Normal Run Access Base Address MSB Register (Index=60h, Default=00h)             |      |

|      |         | SMI# Normal Run Access Base Address LSB Register (Index=61h, Default=00h)             |      |

|      |         | Simple I/O Base Address MSB Register (Index=62h, Default=00h)                         |      |

|      |         | Simple I/O Base Address LSB Register (Index=63h, Default=00h)                         |      |

|      |         | Serial Flash I/F Base Address MSB Register (Index=64h, Default=00h)                   |      |

|      |         | Serial Flash I/F Base Address LSB Register (Index=65h, Default=00h)                   |      |

|      |         | Panel Button De-bounce Interrupt Level Select Register (Index=70h, Default=00h)       |      |

|      |         | Watch Dog Timer 1, 2, 3 Control Register (Index=71h,81h,91h Default=00h)              |      |

|      |         | Watch Dog Timer 1, 2, 3 Configuration Register (Index=72h, 82h, 92h Default=001s0000  |      |

|      |         | Watch Dog Timer 1,2,3 Time-Out Value (LSB) Register (Index=73h,83h,93h, Default=38h   |      |

|      |         | Watch Dog Timer 1,2,3 Time-Out Value (MSB) Register (Index=74h,84h,94h Default=00h    | 1)62 |

|      | 8.11.12 | CPIO Pin Set 1, 2, 3, 4, and 5 Polarity Registers (Index=B0h, B1h, B2h, B3h, and B4h, |      |

|      |         | Default=00h)                                                                          | 62   |

### Contents

|    |      | 8.11.13GPIO Pin Set 1, 2, 3, 4, and 5 Pin Internal Pull-up Enable Registers (Index=B8h, B9h, BA                                                                                                        |    |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |      | BBh, and BCh, Default=00h)                                                                                                                                                                             | 62 |

|    |      | 8.11.14 Simple I/O Set 1, 2, 3, 4 and 5 Enable Registers (Index=C0h, C1h, C2h, C3h, and C4h,                                                                                                           |    |

|    |      | Default=01h, 00h, 00h, 40h, 00h and 00h)                                                                                                                                                               | 62 |

|    |      | 8.11.15 Simple I/O Set 1, 2, 3, 4, and 5Output Enable Registers (Index=C8h, C9h, CAh, CBh, and                                                                                                         |    |

|    |      | CCh Default=01h, 00h, 00h, 40h, and 00h)                                                                                                                                                               | 62 |

|    |      | 8.11.16 Panel Button De-bounce 0 Input Pin Mapping Registers (Index=E0h, Default=00h)                                                                                                                  | 62 |

|    |      | 8.11.17 Panel Button De-bounce 1 Input Pin Mapping Registers (Index=E1h, Default=00h)                                                                                                                  |    |

|    |      | 8.11.18 IRQ External Routing 1-0 Input Pin Mapping Registers (Index=E3h-E2h, Default=00h)                                                                                                              |    |

|    |      | 8.11.19 IRQ External Routing 1-0 Interrupt Level Selection Register (Index=E4h, Default=00h)                                                                                                           |    |

|    |      | 8.11.20 SPI-Function Pin Selection Register (Index=EFh, Default=03h)                                                                                                                                   |    |

|    |      | 8.11.21 SMI# Control Register 1 (Index=F0h, Default=00h)                                                                                                                                               | 63 |

|    |      | 8.11.22 SMI# Control Register 2 (Index=F1h, Default=00h)                                                                                                                                               |    |

|    |      | 8.11.23 SMI# Status Register 1 (Index=F2h, Default=00h)                                                                                                                                                |    |

|    |      | 8.11.24 SMI# Status Register 2 (Index=F3h, Default=00h)                                                                                                                                                |    |

|    |      | 8.11.25 SMI# Pin Mapping Register (Index=F4h, Default=00h)                                                                                                                                             |    |

|    |      | 8.11.26 Hardware Monitor Thermal Output Pin Mapping Register (Index=F5h, Default=00h)                                                                                                                  |    |

|    |      | 8.11.27 Hardware Monitor Alert Beep Pin Mapping Register (Index=F6h, Default=00h)                                                                                                                      | 65 |

|    |      | 8.11.28 Keyboard Lock Pin Mapping Register (Index=F7h, Default=00h)                                                                                                                                    | 66 |

|    |      | 8.11.29 GP LED Blinking 1 Pin Mapping Register (Index=F8h, Default=00h)                                                                                                                                |    |

|    |      | 8.11.30 GP LED Blinking 1 Control Register (Index=F9h, Default=00h)                                                                                                                                    |    |

|    |      | 8.11.31 GP LED Blinking 2 Pin Mapping Register (Index=FAh, Default=00h)                                                                                                                                |    |

|    | 0.40 | 8.11.32 GP LED Blinking 2 Control Register (Index=FBh, Default=00h)                                                                                                                                    |    |

|    | 8.12 | Serial Port 3,4,5,6 Configuration Registers (LDN=08h,09h,0Ah,0Bh)                                                                                                                                      |    |

|    |      | 8.12.1 Serial Port 3,4,5,6 Activate (Index=30h, Default=00h)                                                                                                                                           |    |

|    |      | 8.12.2 Serial Port 3,4,5,6 Base Address MSB Register (Index=60h, Default= 03h, 02h, 03h, 02h)                                                                                                          |    |

|    |      | 8.12.3 Serial Port 3,4,5,6 Base Address LSB Register (Index=61h, Default=00h)                                                                                                                          |    |

|    |      | 8.12.4 Serial Port 3,4,5,6 Interrupt Level Select (Index=70h, Default=04h, 03h, 04h, 03h)                                                                                                              |    |

|    |      | <ul> <li>8.12.5 Serial Port 3,4,5,6 Special Configuration Register 1 (Index=F0h, Default=00h)</li> <li>8.12.6 Serial Port 3,4,5,6 Special Configuration Register 2 (Index=F1h, Default=50h)</li> </ul> |    |

|    |      | 8.12.7 Serial Port 3,4,5,6 Special Configuration Register 3 (Index=F1h, Default=50h)                                                                                                                   |    |

|    |      | 8.12.8 Serial Port 3,4,5,6 Special Configuration Register 4 (Index=F3h, Default=7Fh)                                                                                                                   |    |

| 0  | E    |                                                                                                                                                                                                        |    |

| 9. |      | onal Description                                                                                                                                                                                       |    |

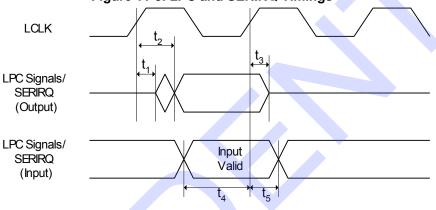

|    | 9.1  | LPC Interface                                                                                                                                                                                          |    |

|    |      | 9.1.1 LPC Transactions                                                                                                                                                                                 |    |

|    |      | 9.1.2 LDRQ# Encoding                                                                                                                                                                                   |    |

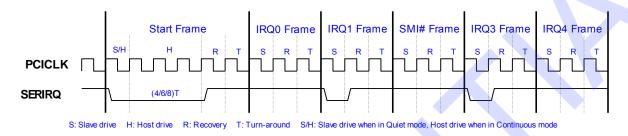

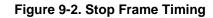

|    | 9.2  | Serialized IRQ                                                                                                                                                                                         |    |

|    |      | 9.2.1 Continuous Mode                                                                                                                                                                                  |    |

|    |      | 9.2.2 Quiet Mode                                                                                                                                                                                       | 73 |

|    |      | 9.2.3 Waveform Samples of SERIRQ Sequence                                                                                                                                                              |    |

|    | 0.0  | 9.2.4 SERIRQ Sampling Slot                                                                                                                                                                             |    |

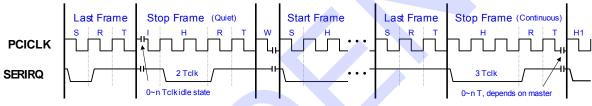

|    | 9.3  | General Purpose I/O                                                                                                                                                                                    |    |

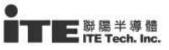

|    | 9.4  | Advanced Power Supply Control and Power Management Event (PME#)                                                                                                                                        |    |

|    | 9.5  | SPI Serial Flash Controller                                                                                                                                                                            |    |

|    |      | 9.5.1 Overview                                                                                                                                                                                         |    |

|    |      | 9.5.2 Features                                                                                                                                                                                         |    |

|    |      | 9.5.3 Register Description                                                                                                                                                                             |    |

|    |      | 9.5.3.1 Control Register (SPI_CTRL)<br>9.5.3.2 Command Register (SPI_CMD)                                                                                                                              |    |

|    |      | $\mathbf{O}$                                                                                                                                                                                           |    |

|    |      | 9.5.3.3 Address 0 Register (SPI_ADDR0)<br>9.5.3.4 Address 1 Register (SPI_ADDR1)                                                                                                                       |    |

|    |      |                                                                                                                                                                                                        |    |

|    |      | 9.5.3.5 Address 2 Register (SPI_ADDR2)                                                                                                                                                                 | 00 |

|     | 9.5.3.6<br>9.5.3.7 |                           | Register (SPI_IDA<br>Register (SPI_IDA |            |               |                  |                     |

|-----|--------------------|---------------------------|----------------------------------------|------------|---------------|------------------|---------------------|

|     | 9.5.3.8            | Output Data/I             | Input Data 2 Regis                     | ter (SPI C | DATA/ SPI     | IDATA2)          |                     |

|     | 9.5.4 Functi       | on Descriptions           | \$                                     | ·····      |               | -                |                     |

| 9.6 |                    |                           |                                        |            |               |                  |                     |

|     |                    |                           |                                        |            |               |                  |                     |

|     | •                  |                           |                                        |            |               |                  |                     |

|     | 9.6.2.1            |                           | (Base+05h, Defau                       |            |               |                  |                     |

|     | 9.6.2.2            |                           | cription                               |            |               |                  |                     |

|     |                    | 9.6.2.2.1                 | Configuration Re                       |            |               |                  |                     |

|     |                    | 9.6.2.2.2                 | Interrupt Status                       |            |               |                  |                     |

|     |                    | 9.6.2.2.3                 | Interrupt Status                       |            |               |                  |                     |

|     |                    | 9.6.2.2.4<br>9.6.2.2.5    | Interrupt Status<br>SMI# Mask Regi     |            |               |                  |                     |

|     |                    | 9.6.2.2.5                 | SMI# Mask Regi                         |            |               |                  |                     |

|     |                    | 9.6.2.2.7                 | SMI# Mask Regi                         |            |               |                  |                     |

|     |                    | 9.6.2.2.8                 | Interrupt Mask R                       |            |               |                  |                     |

|     |                    | 9.6.2.2.9                 | Interrupt Mask R                       |            |               |                  |                     |

|     |                    | 9.6.2.2.10                | Interrupt Mask R                       |            |               |                  |                     |

|     |                    | 9.6.2.2.11                | Interface Selection                    |            |               |                  |                     |

|     |                    | 9.6.2.2.12                | Fan PWM Smoot                          | thing Step | Frequency S   | election Registe | er (Index=0Bh,      |

|     |                    | Default=09h               | ı) 89                                  |            |               | -                |                     |

|     |                    | 9.6.2.2.13                | Fan Tachomete                          | er 16-bit  | Counter E     | nable Register   | (Index=0Ch,         |

|     |                    | Default=00h               |                                        |            |               |                  |                     |

|     |                    | 9.6.2.2.14                | Fan Tachometer                         |            |               |                  |                     |

|     |                    | 9.6.2.2.15                | Fan Tachometer                         |            |               |                  |                     |

|     |                    | 9.6.2.2.16                | Fan Controller M                       |            |               |                  |                     |

|     |                    | 9.6.2.2.17<br>9.6.2.2.18  | FAN_CTL Contr<br>FAN_CTL1              |            |               |                  |                     |

|     |                    |                           | /20h/40h/60h)                          |            | Control       | Register         | (IIIUEX-15II,<br>01 |

|     |                    | 9.6.2.2.19                | FAN_CTL2                               | PWM        | Control       | Register         | (Index=16h          |

|     |                    |                           | /20h/40h/60h)                          | 1 00101    | Control       | register         |                     |

|     |                    | 9.6.2.2.20                | FAN_CTL3                               |            |               |                  |                     |

|     |                    |                           | /20h/40h/60h)                          |            |               |                  |                     |

|     |                    | 9.6.2.2.21                | Fan Tachomete<br>91                    | r 1-3 Exte | nded Readir   | ng Registers (In | dex=18h-1Ah)        |

|     |                    | 9.6.2.2.22                | Fan Tachometer                         | 1-3 Exter  | nded Limit Re | aisters (Index=  | 1Bh-1Dh) 91         |

|     |                    | 9.6.2.2.23                | VIN7-VIN0 Volta                        |            |               |                  |                     |

|     |                    | 9.6.2.2.24                | VBAT Voltage R                         |            |               |                  |                     |

|     |                    | 9.6.2.2.25                | TMPIN3-1 Temp                          |            |               |                  |                     |

|     |                    | 9.6.2.2.26                | VIN7-0 Low Lim                         |            |               |                  |                     |

|     |                    | 33h, 31h)                 | 92                                     | -          |               |                  |                     |

|     |                    | 9.6.2.2.27                | TMPIN3-1 High                          |            |               |                  |                     |

|     |                    | 9.6.2.2.28                | TMPIN3-1 Low L                         |            |               |                  |                     |

|     |                    | 9.6.2.2.29                | ADC Voltage Ch                         |            |               |                  | ,                   |

|     |                    | 9.6.2.2.30                | ADC Tempera                            | ature Cr   | nannel Ena    | ble Register     | (Index=51h,         |

|     |                    | Default=00h               |                                        |            | tout limit    | Dogiotoro (la    | dov-E1h E0h         |

|     |                    | 9.6.2.2.31<br>Default=7Fh |                                        | ermal Ou   | itput Limit   | Registers (Ir    | ndex=54h-52h,       |

|     |                    | 9.6.2.2.32                | ADC Temperat                           | ure Extra  | Channel E     | Enable Registe   | r (Index=55h.       |

|     |                    | Default=00h               | ) 93                                   |            |               | -                |                     |

|     |                    | 9.6.2.2.33                | Thermal Diode                          | Zero D     | egree Adju    | st 1 Register    | (Index=56h,         |

|     |                    | Default=00h               | i) 93                                  |            |               |                  |                     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2.34 Thermal ault=00h) 93                                                                                                                                                                                                       | Diode Zero                                                                                                                                                         | Degree                                                                                                                                                       | Adjust 2                                                                | Register                              | (Index=57h,                                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | D Register (Ind                                                                                                                                                    | lex=58h De                                                                                                                                                   | fault=90h)                                                              |                                       | 94                                                                                            |

|     | 9.6.                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2.36 Thermal                                                                                                                                                                                                                    | Diode Zero                                                                                                                                                         |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ault=00h) 94                                                                                                                                                                                                                      | Desister (Inde                                                                                                                                                     |                                                                                                                                                              |                                                                         |                                       | 04                                                                                            |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Register (Index<br>ent Enable Reg                                                                                                                                  |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | requency Divi                                                                                                                                                      |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ault=00h) 94                                                                                                                                                                                                                      | equency Div                                                                                                                                                        |                                                                                                                                                              |                                                                         | register                              | (Index obli,                                                                                  |

|     | 9.6.                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2.40 Beep Fr                                                                                                                                                                                                                    | equency Divis                                                                                                                                                      | or of Volta                                                                                                                                                  | age Event                                                               | Register                              | (Index=5Eh,                                                                                   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ault=00h) 95                                                                                                                                                                                                                      | equency Diviso                                                                                                                                                     | r of Tompo                                                                                                                                                   | raturo Evo                                                              | nt Pogistor                           | (Indox=5Eb                                                                                    |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2.41 Beep Fre<br>ault=00h) 95                                                                                                                                                                                                   | equency Diviso                                                                                                                                                     | i or rempe                                                                                                                                                   |                                                                         | ni Register                           | (Index-SFII,                                                                                  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Temperature                                                                                                                                                        | Sensor H                                                                                                                                                     | ost Status                                                              | Register                              | (Index=88h,                                                                                   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ault=00000b)                                                                                                                                                                                                                      |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Temperature                                                                                                                                                        |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ex=89h, Default=0                                                                                                                                                                                                                 | 0h)                                                                                                                                                                |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2.44 External<br>lex=8Ah, Default=0                                                                                                                                                                                             | Temperature                                                                                                                                                        |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Temperature                                                                                                                                                        |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | lex=8Bh, Default=0                                                                                                                                                                                                                |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Temperature                                                                                                                                                        |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | gister (Index=8Ch, [                                                                                                                                                                                                              | Default=00h)                                                                                                                                                       |                                                                                                                                                              |                                                                         | · · · · · · · · · · · · · · · · · · · |                                                                                               |

|     | 9.6.                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2.47 External                                                                                                                                                                                                                   | Temperature S                                                                                                                                                      | Sensor Write                                                                                                                                                 | e Data (2-8                                                             | <ol><li>Register</li></ol>            | (Index=8Dh,                                                                                   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ault=h) 96                                                                                                                                                                                                                        |                                                                                                                                                                    |                                                                                                                                                              | _                                                                       |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   | Temperature                                                                                                                                                        | Sensor Ho                                                                                                                                                    | ost Contro                                                              | l Register                            | (Index=8Eh,                                                                                   |

|     | 9.6.3 Operation                                                                                                                                                                                                                                                                                                                                                                                       | ault=01h) 96                                                                                                                                                                                                                      |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       | 07                                                                                            |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | er On RESET and S                                                                                                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ing Conversion                                                                                                                                                                                                                    |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

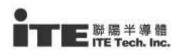

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ge and Temperatu                                                                                                                                                                                                                  |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | ut and Grounding                                                                                                                                                                                                                  |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | Tachometer                                                                                                                                                                                                                        |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

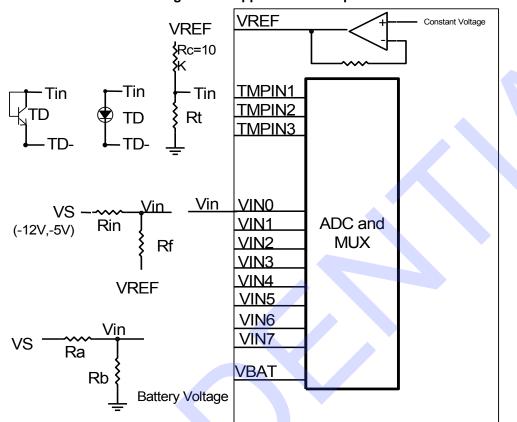

|     | 9.6.3.6 Interr                                                                                                                                                                                                                                                                                                                                                                                        | rupt of the EC                                                                                                                                                                                                                    |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       | Controller FAN CT                                                                                                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                                              |                                                                         |                                       |                                                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   |                                                                                                                                                                    | ind SmartG                                                                                                                                                   | uardian Mo                                                              | des                                   |                                                                                               |

| 9.7 |                                                                                                                                                                                                                                                                                                                                                                                                       | er (FDC)                                                                                                                                                                                                                          |                                                                                                                                                                    | Ind SmartG                                                                                                                                                   | uardian Mo                                                              | odes                                  |                                                                                               |

| 9.7 | 9.7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                    | er (FDC)                                                                                                                                                                                                                          |                                                                                                                                                                    | Ind SmartG                                                                                                                                                   | uardian Mo                                                              | odes                                  |                                                                                               |

| 9.7 | 9.7.1 Introduction<br>9.7.2 Reset                                                                                                                                                                                                                                                                                                                                                                     | er (FDC)                                                                                                                                                                                                                          |                                                                                                                                                                    | Ind SmartG                                                                                                                                                   | uardian Mo                                                              | odes                                  |                                                                                               |

| 9.7 | 9.7.1         Introduction           9.7.2         Reset           9.7.3         Hardware Re                                                                                                                                                                                                                                                                                                          | er (FDC)                                                                                                                                                                                                                          | )                                                                                                                                                                  | Ind SmartG                                                                                                                                                   | uardian Mc                                                              | odes                                  |                                                                                               |