# IT8892E/IT8893E

# **PCI Express to PCI Bridge**

# Preliminary Specification V0.7 (For F Version)

# ITE TECH. INC.

This specification is subject to Change without notice. It is provided "AS IS" and for reference only. For purchasing information, please contact the nearest ITE TECH sales representatives. Please note that the IT8892E/IT8893E V0.7 is applicable only to the F version.

#### Copyright © 2011 ITE Tech. Inc.

This is a Preliminary document release. All specifications are subject to change without notice. The material contained in this document supersedes all previous material issued for the products herein referenced. Please contact ITE Tech. Inc. for the latest document(s).

All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8892E/IT8893E is a trademark of ITE Tech. Inc. All other trademarks are claimed by their respective owners. All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

| ITE Tech. Inc.                           | Phone: | (02) 29126889             |

|------------------------------------------|--------|---------------------------|

| Marketing Department                     | Fax:   | (02) 2910-2551, 2910-2552 |

| 7F, No.233-1, Baociao Rd., Sindian City, |        |                           |

| Taipei County 23145, Taiwan, ROC         |        |                           |

If you have any marketing or sales questions, please contact: **P.Y. Chang**, at ITE Taiwan: E-mail: p.y.chang@ite.com.tw, Tel: 886-2-29126889 X6052, Fax: 886-2-29102551

You may also find the local sales representative nearest you on the ITE web site.

To find out more about ITE, visit our World Wide Web at: http://www.ite.com.tw

Or e-mail itesupport@ite.com.tw for more product information/services

# **Revision History**

| Section  | Revision                                                                                | Page No. |

|----------|-----------------------------------------------------------------------------------------|----------|

| -        | Feature update                                                                          | -        |

|          | PCI Express                                                                             |          |

|          | → Maximum payload size up to 256 bytes                                                  |          |

|          | PCI                                                                                     |          |

|          | <ul> <li>PCI</li> <li>→ Suport of up to six queues for memory read cycles</li> </ul>    |          |

|          | $\rightarrow$ Suported number of outstanding memory read cycles changed                 |          |

|          | from eight to 24                                                                        |          |

| -        | Default of the following registers updated:                                             | -        |

|          | Revision ID Register (REVID)                                                            |          |

|          | Class Code Register (CC)                                                                |          |

|          | Secondary Discard Timer (SDT)                                                           |          |

|          | Data Credit (DC)                                                                        |          |

|          | Header Credit (HC)                                                                      |          |

|          | Initial Non-Posted Flow Control Credit (INPFCC)                                         |          |

|          | Data Credit (DC)                                                                        |          |

|          | <ul> <li>Header Credit (HC)</li> <li>Memory Read Lock Enable (MRLE)</li> </ul>          |          |

|          | <ul> <li>Memory Read Lock Enable (MRLE)</li> <li>PCI Output PAD Skew Control</li> </ul> |          |

|          | <ul> <li>PCI Input PAD Skew Control</li> </ul>                                          |          |

|          | <ul> <li>Max_Read_Request Size (MRRS)</li> </ul>                                        |          |

| -        | Note below added to PCI Express related registers:                                      | _        |

|          | These bits will be hidden with legacy mode.                                             |          |

| -        | Registers below added:                                                                  | -        |

|          | • Transaction Layer Control Register1 / Transaction Layer Control                       |          |

|          | Register2                                                                               |          |

|          | Dummy Register (0000FFFFh)                                                              |          |

| 6.2.28   | Capabilities Pointer Register (CAPP)                                                    | 33       |

|          | Default and description updated                                                         |          |

| 6.2.36   | Transaction Layer Control Register (TLCR)                                               | 37       |

| 6.0.00   | Description of bit 31-15 updated                                                        | 20       |

| 6.2.39   | PCI Control Register (PCICR)                                                            | 39       |

| <u> </u> | Function of bit 12 changed into "PCI Clock Slew Control"                                |          |

# CONTENTS

| 1. | Features1 |                |                                                                                                |     |  |  |  |  |  |

|----|-----------|----------------|------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| 2. | Gener     | al Desc        | ription                                                                                        | 3   |  |  |  |  |  |

| 3. | Block     | Diagram        | ۱                                                                                              | 5   |  |  |  |  |  |

| 4. | Pin Co    | onfigurat      | lion                                                                                           | 7   |  |  |  |  |  |

|    | 4.1       | IT8892         | E Pin Configuration                                                                            | 7   |  |  |  |  |  |

|    |           |                | E Pin Configuration                                                                            |     |  |  |  |  |  |

| 5. | Pin De    | escriptio      | n                                                                                              | .13 |  |  |  |  |  |

|    |           | •              | E Pin Description                                                                              |     |  |  |  |  |  |

|    |           |                | E Pin Description                                                                              |     |  |  |  |  |  |

| 6. | Functi    | onal De        | scription                                                                                      | .21 |  |  |  |  |  |

|    | 6.1       | Registe        | er Description                                                                                 | .21 |  |  |  |  |  |

|    |           | 6.1.1          | Register Abbreviation                                                                          |     |  |  |  |  |  |

|    |           | 6.1.2          | List of PCI Configuration Registers                                                            | .21 |  |  |  |  |  |

|    | 6.2       | Registe        | er Definition of PCI Configuration Register                                                    |     |  |  |  |  |  |

|    |           | 6.2.1          | Vendor ID Register (VID)                                                                       |     |  |  |  |  |  |

|    |           | 6.2.2          | Device ID Register (DID)                                                                       |     |  |  |  |  |  |

|    |           | 6.2.3          | PCI Command Register (PCICMD)                                                                  |     |  |  |  |  |  |

|    |           | 6.2.4          | Status Register (STS)                                                                          |     |  |  |  |  |  |

|    |           | 6.2.5<br>6.2.6 | Revision ID Register (REVID)                                                                   |     |  |  |  |  |  |

|    |           | 6.2.7          | Class Code Register (CC)<br>Cache Line Size Register (CLS)                                     |     |  |  |  |  |  |

|    |           | 6.2.8          | Master Latency Timer Register (MLT)                                                            |     |  |  |  |  |  |

|    |           | 6.2.9          | Header Type Register (HEADTYP)                                                                 |     |  |  |  |  |  |

|    |           |                | BIST Register (BIST)                                                                           |     |  |  |  |  |  |

|    |           |                | Base Address Register 0 (BAR0)                                                                 |     |  |  |  |  |  |

|    |           |                | Base Address Register 1 (BAR1)                                                                 |     |  |  |  |  |  |

|    |           |                | Primary Bus Number Register (PBN)                                                              |     |  |  |  |  |  |

|    |           |                | Secondary Bus Number Register (SCBN)                                                           |     |  |  |  |  |  |

|    |           |                | Subordinate Bus Number Register (SBBN)                                                         |     |  |  |  |  |  |

|    |           |                | Secondary Latency Timer Register (SLT)                                                         |     |  |  |  |  |  |

|    |           |                | I/O Base Register (IOB)                                                                        |     |  |  |  |  |  |

|    |           |                | I/O Limit Register (IOL)<br>Secondary Status Register (SECSTS)                                 |     |  |  |  |  |  |

|    |           |                | Memory Base Register (MB)                                                                      |     |  |  |  |  |  |

|    |           |                | Memory Limit Register (ML)                                                                     |     |  |  |  |  |  |

|    |           |                | Prefetchable Memory Base Register (PMB)                                                        |     |  |  |  |  |  |

|    |           |                | Prefetchable Memory Limit Register (PML)                                                       |     |  |  |  |  |  |

|    |           |                | Prefetchable Base Upper 32 Bits Register (PMB_UPPER)                                           |     |  |  |  |  |  |

|    |           |                | Prefetchable Limit Upper 32 Bits Register (PML_UPPER)                                          |     |  |  |  |  |  |

|    |           |                | I/O Limit Upper 16 Bits Register (IOLU16)                                                      |     |  |  |  |  |  |

|    |           |                | I/O Base Upper 16 Bits Register (IOBU16)                                                       |     |  |  |  |  |  |

|    |           |                | Capabilities Pointer Register (CAPP)                                                           |     |  |  |  |  |  |

|    |           |                | Interrupt Line Register (INTRL)                                                                |     |  |  |  |  |  |

|    |           |                | Interrupt Pin Register (INTRP)                                                                 |     |  |  |  |  |  |

|    |           |                | Bridge Control Register (BRIDGE_CNT)                                                           |     |  |  |  |  |  |

|    |           |                | Initial Posted Flow Control Credit (IPTFCC)<br>Initial Non-Posted Flow Control Credit (INPFCC) |     |  |  |  |  |  |

|    |           | 6234           | Initial Completion Flow Control Credit (ICPLFCC)                                               | .37 |  |  |  |  |  |

|    |           | 6 2 35         | Link Layer Control Register (LLCR)                                                             | 37  |  |  |  |  |  |

|    |           | 6.2.36         | Transaction Layer Control Register (TLCR)                                                      | .37 |  |  |  |  |  |

|    |           |                |                                                                                                |     |  |  |  |  |  |

|     |         |             | PHY Control Register (PHYCR)                                  |    |

|-----|---------|-------------|---------------------------------------------------------------|----|

|     |         |             | PCI Port 80 Debug Register (P80DR)                            |    |

|     |         | 6.2.39      | PCI Control Register (PCICR)                                  |    |

|     |         |             | PCI PAD Skew Control Register (PPSCR)                         |    |

|     |         | 6.2.41      | Serial EEPROM Control Register (SEEPROMCR)                    | 40 |

|     |         | 6.2.42      | PCI Express Capability Identifier Register (EXP_CAPID)        | 41 |

|     |         | 6.2.43      | PCI Express Next Pointer Register (EXP_NXTP)                  | 41 |

|     |         | 6.2.44      | PCI Express Capability Register (EXP_CAP)                     | 41 |

|     |         |             | PCI Express Device Capabilities Register (EXP_DEVCAP)         |    |

|     |         |             | PCI Express Device Control Register (EXP_DEVCNTL)             |    |

|     |         | 6.2.47      | PCI Express Device Status Register (EXP_DSTS)                 | 43 |

|     |         |             | PCI Express Link Capabilities Register (EXP_LCAP)             |    |

|     |         |             | PCI Express Link Control Register (EXP_LCNTL)                 |    |

|     |         |             | PCI Express Link Status Register (EXP_LSTS)                   |    |

|     |         |             | Power Management Capability ID Register (PM_CAPID)            |    |

|     |         |             | Power Management Next Pointer Register (PM_NXTPTR)            |    |

|     |         | 6.2.53      | Power Management Capabilities Register (PM_CAP)               | 45 |

|     |         | 6.2.54      | Power Management Control and Status Register (PM_CNTLSTS)     | 46 |

|     |         |             | SSID Capability ID Register (SSID_CAPID)                      |    |

|     |         | 6.2.56      | SSID Next Pointer Register (SSID_NXTPTR)                      | 47 |

|     |         |             | SSID Register (SSID)                                          |    |

|     |         |             | Dummy Register (DMR)                                          |    |

|     |         |             | Transaction Layer Control Register1 (TLCR1)                   |    |

|     |         |             | Transaction Layer Control Register2 (TLCR2)                   |    |

|     |         |             | 7-Segment Display Register (7SDR)                             |    |

|     |         |             | GPIO Input Status (GPIOIS)                                    |    |

|     |         |             | GPIO Output Register (GPIOOR)                                 |    |

|     |         | 6.2.64      | GPIO Output Enable Register (GPIOOER)                         | 50 |

|     |         |             | GPIO Pull-Up Register (GPIOPUR)                               |    |

|     |         |             | GPIO Pull-Down Register (GPIOPDR)                             |    |

|     |         |             | Device Serial Number Enhanced Capability Header (DSN_ECAPHDR) |    |

|     |         |             | Serial Number Register (DSN_SNR)                              |    |

|     | 6.3     |             | DCk                                                           | 52 |

|     | 6.4     | Reset       | 54                                                            |    |

|     | 6.5     |             | Management                                                    |    |

|     | 6.6     |             | rrupt                                                         |    |

|     | 6.7     |             | piter                                                         |    |

|     | 6.8     |             | DM                                                            |    |

|     |         |             | Overview                                                      |    |

|     |         |             | EEPROM Read Status Operation                                  |    |

|     |         | 6.8.3       | EEPROM Write Enable Operation                                 |    |

|     |         | 6.8.4       | EEPROM Write Operation                                        |    |

|     |         | 6.8.5       | EEPROM Read Operation                                         |    |

|     |         | 6.8.6       | Suggested EEPROM Data Content                                 |    |

|     | 6.9     | • •         | Mode                                                          |    |

| 7.  | DC Cł   | naracter    | istics                                                        | 61 |

| 8.  | AC Cł   | naracter    | istics                                                        | 63 |

|     |         |             | nterface Characteristics                                      |    |

|     |         | •           | mation                                                        |    |

|     |         | •           | mation                                                        |    |

|     |         | •           |                                                               |    |

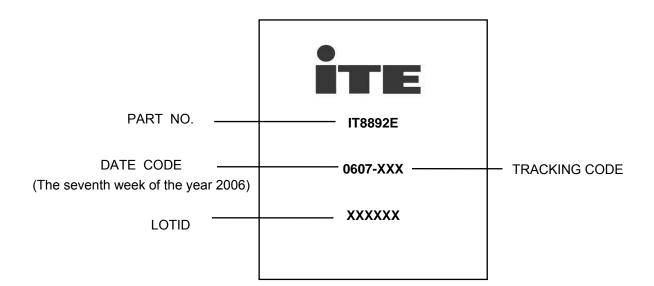

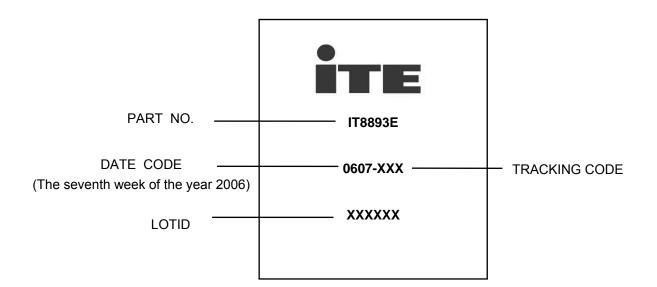

| 12. | i up iv | iai kiliy I | nformation                                                    |    |

# **FIGURES**

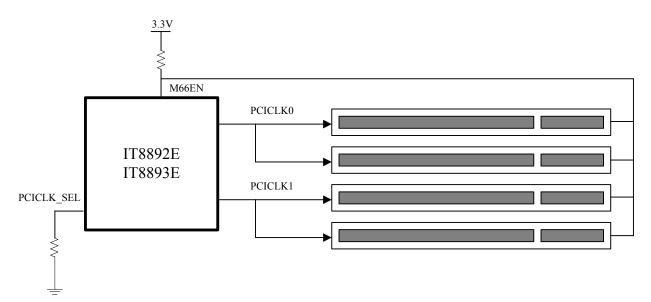

| Figure 6-1. Internal Clock Mode with 33.3MHz Output | 52 |

|-----------------------------------------------------|----|

| Figure 6-2. Internal Clock Mode with 62.5MHz Output | 53 |

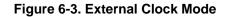

| Figure 6-3. External Clock Mode                     | 53 |

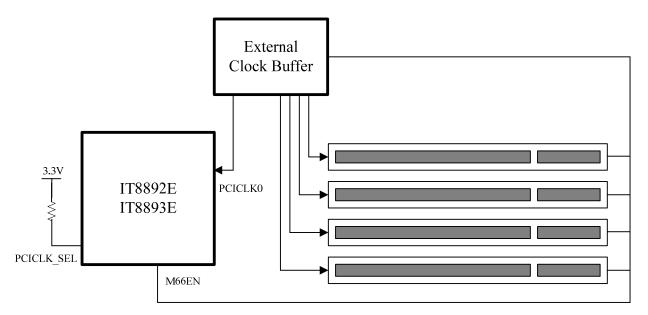

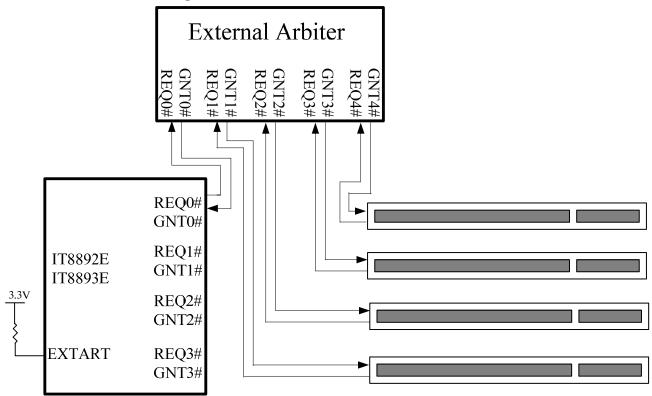

| Figure 6-4. IT8892E/IT8893E with Internal Arbiter   | 56 |

| Figure 6-5. IT8892E/IT8893E with External Arbiter   | 56 |

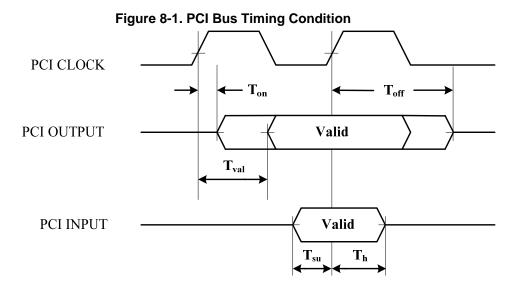

| Figure 8-1. PCI Bus Timing Condition                | 63 |

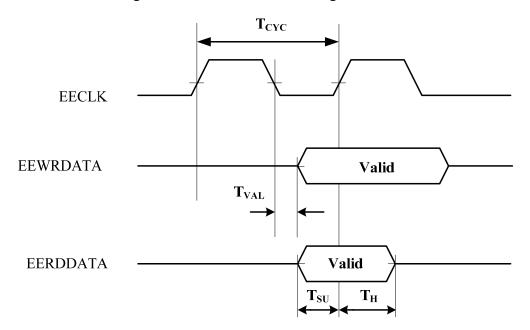

| Figure 8-2. Serial EEPROM Timing Condition          | 64 |

# **TABLES**

| Table 4-1. IT8892E Pins Listed in Numeric Order                    | 8  |

|--------------------------------------------------------------------|----|

| Table 4-2. IT8892E Pins Listed in Alphabetical Order               | 9  |

| Table 4-3. IT8893E Pins Listed in Numeric Order                    |    |

| Table 4-4. IT8893E Pins Listed in Alphabetical Order               |    |

| Table 5-1. IT8892E Pin Description of PCI Bus Interface            |    |

| Table 5-2. IT8892E Pin Description of PCI Express Interface        | 14 |

| Table 5-3. IT8892E Pin Description of Miscellaneous Signal         |    |

| Table 5-4. IT8892E Pin Description of 7-Segment Display Signal     |    |

| Table 5-5. IT8892E Pin Description of Power/Ground Signal          |    |

| Table 5-6. IT8893E Pin Description of PCI Bus Interface            | 16 |

| Table 5-7. IT8893E Pin Description of PCI Express Interface        |    |

| Table 5-8. IT8893E Pin Description of Miscellaneous Signal         |    |

| Table 5-9. IT8892E Pin Description of 7-Segment Display Signal     | 18 |

| Table 5-10. IT8893E Pin Description of Power/Ground Signal         | 18 |

| Table 6-1. List of Type 1 Header                                   |    |

| Table 6-2. List of PCI Express Capability                          |    |

| Table 6-3. List of Power Management Capability                     | 22 |

| Table 6-4. List of Subsystem ID and Subsystem Vendor ID Capability | 23 |

| Table 6-5. List of Device Serial Number Capability                 | 23 |

| Table 6-6. Reset Summary                                           | 54 |

| Table 6-7. EEPROM Data Format                                      | 57 |

| Table 6-8. Suggested EEPROM Data Content                           |    |

| Table 8-1. PCI Bus AC Table                                        |    |

| Table 8-2. Serial EEPROM AC Table                                  |    |

| Table 9-1. PCI Express AC / DC Interface Characteristics           | 65 |

|                                                                    |    |

# 1. Features

#### PCI Express

- Compliant with PCI Express Base Specification Revision 1.1

- Compliant with PCI Express to PCI/PCI-X Bridge Specification Revision 1.0

- Full 2.5GHz per direction

- Data Link Layer Cyclic Redundancy Check (CRC) generator and checker

- Automatic Retry of bad packets

- Legacy interrupt signaling

- Maximum payload size up to 256 bytes

#### PCI

- Compliant with PCI Local Bus Specification Revision 3.0

- Supports PCI 32-bit, 33/66 MHz, 3.3V, 5V tolerant

- Supports 4(IT8892E) / 2(IT8893E) external REQ/GNT pairs for internal arbiter

- Supports up to six queues for memory read cycles

- Supports up to 24 outstanding memory read cycles

#### Power Management

- Supports PCI Express Active State Power Management (ASPM) L0s, L1

- Supports link power management state L0s, L1, L23 Ready, L2, L3 link state

- Supports for PM 1.1 compatible D0, D1, D2, D3hot and D3cold device power states

- Supports PME# event propagation

- Supports side-band WAKE# signaling

#### SPI Interface

- SPI master only

- Operating at up to 25MHz

- Supports up to 16MB EEPROM utilizing 1, 2, or 3 byte addressing

#### I/O Port 80

- Supports I/O port 80 debugging on PCI side

Specifications subject to Change without Notice

- Dual 7-segment display

- Legacy Mode

- Supports PCI-to-PCI bridge with subtractive decode for legacy devices

- Built-in Regulator

- Two on-chip 3.3V to 1.8V regulators

- Supports power-on-reset

- General Purpose I/O

Supports 5 GPIOs

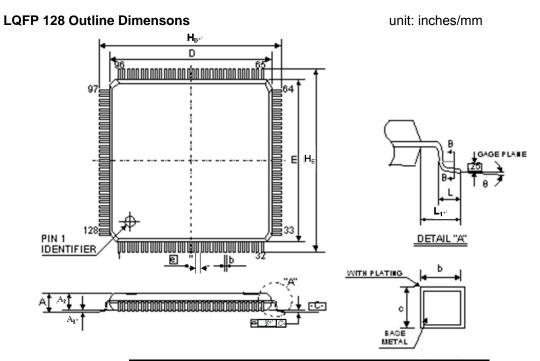

- Package - LQFP 128

- RoHS Compliant (100% Green Available)

This page is intentionally left blank.

# 2. General Description

IT8892E/IT8893E is a single-function PCI Express to PCI bridge, which is compliant with the PCI Express Base Specification Revision 1.1, PCI Local Bus Specification Revision 3.0 and PCI Express to PCI/PCI-X Bridge Specification Revision 1.0. The PCI Express interface supports a x1 lane configuration, and enables the bridge to provide high-performance operation of the data transfer rate up to 250MB/s. The PCI bus interface supports 32-bit and can operate at up to 66 MHz.

This page is intentionally left blank.

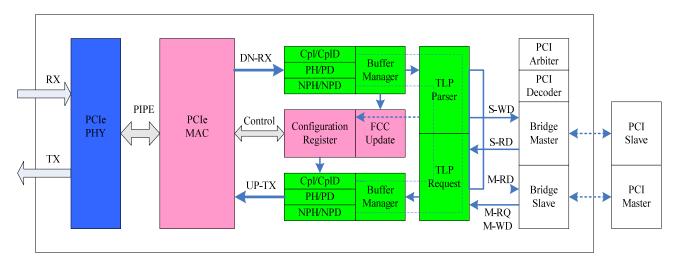

# 3. Block Diagram

This page is intentionally left blank.

# 4. Pin Configuration

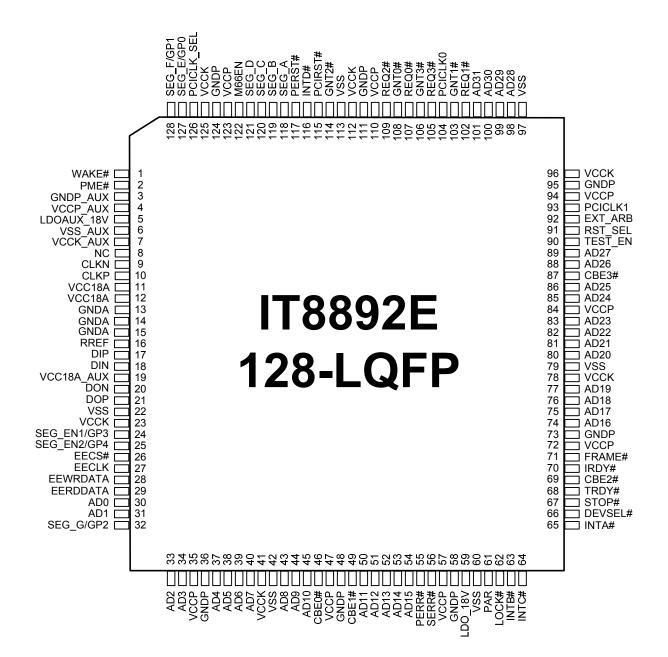

4.1 IT8892E Pin Configuration

| Pin | Signal      | Pin | Signal  | Pin | Signal  | Pin | Signal     |

|-----|-------------|-----|---------|-----|---------|-----|------------|

| 1   | WAKE#       | 33  | AD2     | 65  | INTA#   | 97  | VSS        |

| 2   | PME#        | 34  | AD3     | 66  | DEVSEL# | 98  | AD28       |

| 3   | GNDP_AUX    | 35  | VCCP    | 67  | STOP#   | 99  | AD29       |

| 4   | VCCP AUX    | 36  | GNDP    | 68  | TRDY#   | 100 | AD30       |

| 5   | LDOAUX 18V  | 37  | AD4     | 69  | CBE2#   | 100 | AD31       |

| 6   | VSS AUX     | 38  | AD5     | 70  | IRDY#   | 101 | REQ1#      |

| 7   | VCCK AUX    | 39  | AD6     | 71  | FRAME#  | 102 | GNT1#      |

| 8   | NC          | 40  | AD7     | 72  | VCCP    | 100 | PCICLK0    |

| 9   | CLKN        | 41  | VCCK    | 73  | GNDP    | 105 | REQ3#      |

| 10  | CLKP        | 42  | VSS     | 74  | AD16    | 106 | GNT#       |

| 11  | VCC18A      | 43  | AD8     | 75  | AD17    | 107 | REQ0#      |

| 12  | VCC18A      | 44  | AD9     | 76  | AD18    | 108 | GNT0#      |

| 13  | GNDA        | 45  | AD10    | 77  | AD19    | 109 | REQ2#      |

| 14  | GNDA        | 46  | CBE0#   | 78  | VCCK    | 110 | VCCP       |

| 15  | GNDA        | 47  | VCCP    | 79  | VSS     | 111 | GNDP       |

| 16  | RREF        | 48  | GNDP    | 80  | AD20    | 112 | VCCK       |

| 17  | DIP         | 49  | CBE1#   | 81  | AD21    | 113 | VSS        |

| 18  | DIN         | 50  | AD11    | 82  | AD22    | 114 | GNT2#      |

| 19  | VCC18A AUX  | 51  | AD12    | 83  | AD23    | 115 | PCIRST#    |

| 20  | DON         | 52  | AD13    | 84  | VCCP    | 116 | INTD#      |

| 21  | DOP         | 53  | AD14    | 85  | AD24    | 117 | PERST#     |

| 22  | VSS         | 54  | AD15    | 86  | AD25    | 118 | SEG A      |

| 23  | VCCK        | 55  | PERR#   | 87  | CBE3#   | 119 | SEG B      |

| 24  | SEG_EN1/GP3 | 56  | SERR#   | 88  | AD26    | 120 | SEG_C      |

| 25  | SEG EN2/GP4 | 57  | VCCP    | 89  | AD27    | 121 | SEG D      |

| 26  | EECS#       | 58  | GNDP    | 90  | TEST_EN | 122 | M66EN      |

| 27  | EECLK       | 59  | LDO_18V | 91  | RST_SEL | 123 | VCCP       |

| 28  | EEWRDATA    | 60  | VSS     | 92  | EXT_ARB | 124 | GNDP       |

| 29  | EERDDATA    | 61  | PAR     | 93  | PCICLK1 | 125 | VCCK       |

| 30  | AD0         | 62  | LOCK#   | 94  | VCCP    | 126 | PCICLK_SEL |

| 31  | AD1         | 63  | INTB#   | 95  | GNDP    | 127 | SEG_E/GP0  |

| 32  | SEG_G/GP2   | 64  | INTC#   | 96  | VCCK    | 128 | SEG_F/GP1  |

Table 4-1. IT8892E Pins Listed in Numeric Order

| Signal | Pin | Signal   | Pin | Signal      | Pin | Signal     | Pin |

|--------|-----|----------|-----|-------------|-----|------------|-----|

| AD0    | 30  | CBE0#    | 46  | INTA#       | 65  | SEG_G/GP2  | 32  |

| AD1    | 31  | CBE1#    | 49  | INTB#       | 63  | SERR#      | 56  |

| AD10   | 45  | CBE2#    | 69  | INTC#       | 64  | STOP#      | 67  |

| AD11   | 50  | CBE3#    | 87  | INTD#       | 116 | TEST_EN    | 90  |

| AD12   | 51  | CLKN     | 9   | IRDY#       | 70  | TRDY#      | 68  |

| AD13   | 52  | CLKP     | 10  | LDO_18V     | 59  | VCC18A     | 11  |

| AD14   | 53  | DEVSEL#  | 66  | LDOAUX_18V  | 5   | VCC18A     | 12  |

| AD15   | 54  | DIN      | 18  | LOCK#       | 62  | VCC18A_AUX | 19  |

| AD16   | 74  | DIP      | 17  | M66EN       | 122 | VCCK       | 23  |

| AD17   | 75  | DON      | 20  | NC          | 8   | VCCK       | 41  |

| AD18   | 76  | DOP      | 21  | PAR         | 61  | VCCK       | 78  |

| AD19   | 77  | EECLK    | 27  | PCICLK_SEL  | 126 | VCCK       | 96  |

| AD2    | 33  | EECS#    | 26  | PCICLK0     | 104 | VCCK       | 112 |

| AD20   | 80  | EERDDATA | 29  | PCICLK1     | 93  | VCCK       | 125 |

| AD21   | 81  | EEWRDATA | 28  | PCIRST#     | 115 | VCCK_AUX   | 7   |

| AD22   | 82  | EXT_ARB  | 92  | PERR#       | 55  | VCCP       | 35  |

| AD23   | 83  | FRAME#   | 71  | PERST#      | 117 | VCCP       | 47  |

| AD24   | 85  | GNDA     | 13  | PME#        | 2   | VCCP       | 57  |

| AD25   | 86  | GNDA     | 14  | REQ0#       | 107 | VCCP       | 72  |

| AD26   | 88  | GNDA     | 15  | REQ1#       | 102 | VCCP       | 84  |

| AD27   | 89  | GNDP     | 36  | REQ2#       | 109 | VCCP       | 94  |

| AD28   | 98  | GNDP     | 48  | REQ3#       | 105 | VCCP       | 110 |

| AD29   | 99  | GNDP     | 58  | RREF        | 16  | VCCP       | 123 |

| AD3    | 34  | GNDP     | 73  | RST_SEL     | 91  | VCCP_AUX   | 4   |

| AD30   | 100 | GNDP     | 95  | SEG_A       | 118 | VSS        | 22  |

| AD31   | 101 | GNDP     | 111 | SEG_B       | 119 | VSS        | 42  |

| AD4    | 37  | GNDP     | 124 | SEG_C       | 120 | VSS        | 60  |

| AD5    | 38  | GNDP_AUX | 3   | SEG_D       | 121 | VSS        | 79  |

| AD6    | 39  | GNT0#    | 108 | SEG_E/GP0   | 127 | VSS        | 97  |

| AD7    | 40  | GNT1#    | 103 | SEG_EN1/GP3 | 24  | VSS        | 113 |

| AD8    | 43  | GNT2#    | 114 | SEG_EN2/GP4 | 25  | VSS_AUX    | 6   |

| AD9    | 44  | GNT3#    | 106 | SEG_F/GP1   | 128 | WAKE#      | 1   |

# Table 4-2. IT8892E Pins Listed in Alphabetical Order

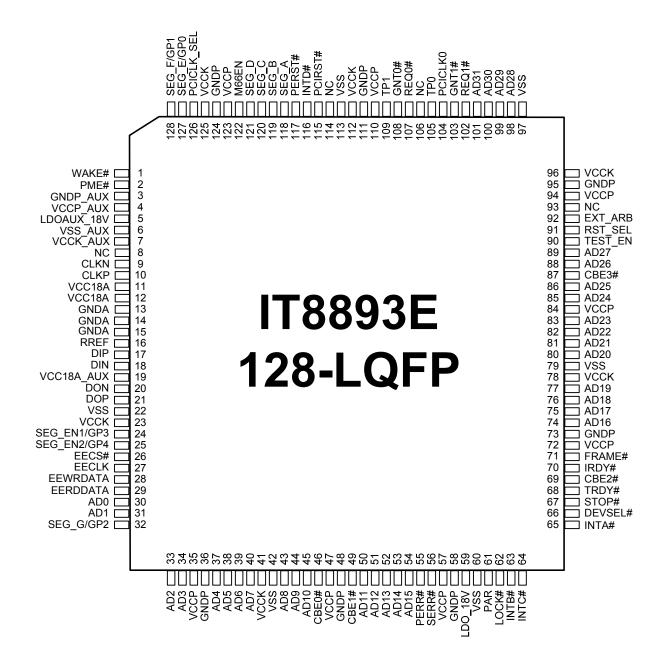

#### 4.2 IT8893E Pin Configuration

| Pin | Signal      | Pin | Signal  | Pin | Signal  | Pin | Signal     |

|-----|-------------|-----|---------|-----|---------|-----|------------|

| 1   | WAKE#       | 33  | AD2     | 65  | INTA#   | 97  | VSS        |

| 2   | PME#        | 34  | AD3     | 66  | DEVSEL# | 98  | AD28       |

| 3   | GNDP_AUX    | 35  | VCCP    | 67  | STOP#   | 99  | AD29       |

| 4   | VCCP_AUX    | 36  | GNDP    | 68  | TRDY#   | 100 | AD30       |

| 5   | LDOAUX_18V  | 37  | AD4     | 69  | CBE2#   | 101 | AD31       |

| 6   | VSS_AUX     | 38  | AD5     | 70  | IRDY#   | 102 | REQ1#      |

| 7   | VCCK_AUX    | 39  | AD6     | 71  | FRAME#  | 103 | GNT1#      |

| 8   | NC          | 40  | AD7     | 72  | VCCP    | 104 | PCICLK0    |

| 9   | CLKN        | 41  | VCCK    | 73  | GNDP    | 105 | TP0        |

| 10  | CLKP        | 42  | VSS     | 74  | AD16    | 106 | NC         |

| 11  | VCC18A      | 43  | AD8     | 75  | AD17    | 107 | REQ0#      |

| 12  | VCC18A      | 44  | AD9     | 76  | AD18    | 108 | GNT0#      |

| 13  | GNDA        | 45  | AD10    | 77  | AD19    | 109 | TP1        |

| 14  | GNDA        | 46  | CBE0#   | 78  | VCCK    | 110 | VCCP       |

| 15  | GNDA        | 47  | VCCP    | 79  | VSS     | 111 | GNDP       |

| 16  | RREF        | 48  | GNDP    | 80  | AD20    | 112 | VCCK       |

| 17  | DIP         | 49  | CBE1#   | 81  | AD21    | 113 | VSS        |

| 18  | DIN         | 50  | AD11    | 82  | AD22    | 114 | NC         |

| 19  | VCC18A_AUX  | 51  | AD12    | 83  | AD23    | 115 | PCIRST#    |

| 20  | DON         | 52  | AD13    | 84  | VCCP    | 116 | INTD#      |

| 21  | DOP         | 53  | AD14    | 85  | AD24    | 117 | PERST#     |

| 22  | VSS         | 54  | AD15    | 86  | AD25    | 118 | SEG_A      |

| 23  | VCCK        | 55  | PERR#   | 87  | CBE3#   | 119 | SEG_B      |

| 24  | SEG_EN1/GP3 | 56  | SERR#   | 88  | AD26    | 120 | SEG_C      |

| 25  | SEG_EN2/GP4 | 57  | VCCP    | 89  | AD27    | 121 | SEG_D      |

| 26  | EECS#       | 58  | GNDP    | 90  | TEST_EN | 122 | M66EN      |

| 27  | EECLK       | 59  | LDO_18V | 91  | RST_SEL | 123 | VCCP       |

| 28  | EEWRDATA    | 60  | VSS     | 92  | EXT_ARB | 124 | GNDP       |

| 29  | EERDDATA    | 61  | PAR     | 93  | NC      | 125 | VCCK       |

| 30  | AD0         | 62  | LOCK#   | 94  | VCCP    | 126 | PCICLK_SEL |

| 31  | AD1         | 63  | INTB#   | 95  | GNDP    | 127 | SEG_E/GP0  |

| 32  | SEG_G/GP2   | 64  | INTC#   | 96  | VCCK    | 128 | SEG_F/GP1  |

# Table 4-3. IT8893E Pins Listed in Numeric Order

| Signal | Pin | Signal   | Pin | Signal      | Pin | Signal     | Pin |

|--------|-----|----------|-----|-------------|-----|------------|-----|

| AD0    | 30  | CBE0#    | 46  | INTC#       | 64  | STOP#      | 67  |

| AD1    | 31  | CBE1#    | 49  | INTD#       | 116 | TEST_EN    | 90  |

| AD10   | 45  | CBE2#    | 69  | IRDY#       | 70  | TP0        | 105 |

| AD11   | 50  | CBE3#    | 87  | LDO_18V     | 59  | TP1        | 109 |

| AD12   | 51  | CLKN     | 9   | LDOAUX_18V  | 5   | TRDY#      | 68  |

| AD13   | 52  | CLKP     | 10  | LOCK#       | 62  | VCC18A     | 11  |

| AD14   | 53  | DEVSEL#  | 66  | M66EN       | 122 | VCC18A     | 12  |

| AD15   | 54  | DIN      | 18  | NC          | 8   | VCC18A_AUX | 19  |

| AD16   | 74  | DIP      | 17  | NC          | 93  | VCCK       | 23  |

| AD17   | 75  | DON      | 20  | NC          | 106 | VCCK       | 41  |

| AD18   | 76  | DOP      | 21  | NC          | 114 | VCCK       | 78  |

| AD19   | 77  | EECLK    | 27  | PAR         | 61  | VCCK       | 96  |

| AD2    | 33  | EECS#    | 26  | PCICLK_SEL  | 126 | VCCK       | 112 |

| AD20   | 80  | EERDDATA | 29  | PCICLK0     | 104 | VCCK       | 125 |

| AD21   | 81  | EEWRDATA | 28  | PCIRST#     | 115 | VCCK_AUX   | 7   |

| AD22   | 82  | EXT_ARB  | 92  | PERR#       | 55  | VCCP       | 35  |

| AD23   | 83  | FRAME#   | 71  | PERST#      | 117 | VCCP       | 47  |

| AD24   | 85  | GNDA     | 13  | PME#        | 2   | VCCP       | 57  |

| AD25   | 86  | GNDA     | 14  | REQ0#       | 107 | VCCP       | 72  |

| AD26   | 88  | GNDA     | 15  | REQ1#       | 102 | VCCP       | 84  |

| AD27   | 89  | GNDP     | 36  | RREF        | 16  | VCCP       | 94  |

| AD28   | 98  | GNDP     | 48  | RST_SEL     | 91  | VCCP       | 110 |

| AD29   | 99  | GNDP     | 58  | SEG_A       | 118 | VCCP       | 123 |

| AD3    | 34  | GNDP     | 73  | SEG_B       | 119 | VCCP_AUX   | 4   |

| AD30   | 100 | GNDP     | 95  | SEG_C       | 120 | VSS        | 22  |

| AD31   | 101 | GNDP     | 111 | SEG_D       | 121 | VSS        | 42  |

| AD4    | 37  | GNDP     | 124 | SEG_E/GP0   | 127 | VSS        | 60  |

| AD5    | 38  | GNDP_AUX | 3   | SEG_EN1/GP3 | 24  | VSS        | 79  |

| AD6    | 39  | GNT0#    | 108 | SEG_EN2/GP4 | 25  | VSS        | 97  |

| AD7    | 40  | GNT1#    | 103 | SEG_F/GP1   | 128 | VSS        | 113 |

| AD8    | 43  | INTA#    | 65  | SEG_G/GP2   | 32  | VSS_AUX    | 6   |

| AD9    | 44  | INTB#    | 63  | SERR#       | 56  | WAKE#      | 1   |

## Table 4-4. IT8893E Pins Listed in Alphabetical Order

# 5. Pin Description

## 5.1 IT8892E Pin Description

| Table 5-1. IT8892E Pin Description of PCI Bus Interface |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Pin(s) No.                                                                                                                      | Symbol                           | Attribute | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101, 100, 99,<br>98, 89, 88, 86,<br>85, 83, 82, 81,<br>80, 77, 76, 75,<br>74, 54, 53, 52,<br>51, 50, 45, 44,<br>43, 40, 39, 38, | AD[31:0]                         | PI/O      | <i>PCI Address/Data Bus(32 pins)</i><br>During the address phase, AD[31:0] contain the physical address of the<br>PCI transaction. During the data phase, AD[31:0] contain the data.                                                                                                                                                             |

| 37, 34, 33, 31,<br>30                                                                                                           |                                  |           |                                                                                                                                                                                                                                                                                                                                                  |

| 87, 69, 49, 46                                                                                                                  | CBE[3:0]#                        | PI/O      | <b>Command/Byte Enable (4 pins)</b><br>During the address phase, CBE[3:0]# contain the bus command. During<br>the data phase, CBE[3:0]# contain the byte enable. CBE0# corresponds<br>to byte 0 (AD[7:0]), and CBE3# corresponds to byte 3 (AD[31:24]).                                                                                          |

| 66                                                                                                                              | DEVSEL#                          | PI/O      | <b>Device Select</b><br>As an output, DEVSEL# indicates that the target (PCI slave) decodes its<br>address during the current bus transaction. As an input, DEVSEL#<br>indicates whether a device on the bus is selected.                                                                                                                        |

| 71                                                                                                                              | FRAME#                           | PI/O      | FRAME<br>Indicates the start of a PCI transaction.                                                                                                                                                                                                                                                                                               |

| 106, 114, 103,<br>108                                                                                                           | GNT[3:0]#                        | PI/O      | <b>Bus Grant (4 pins)</b><br>Indicates that the central arbiter granted the bus to an agent. When the internal PCI arbiter is enabled, GNT[3:0]# are outputs used to grant the bus to external devices. When the external PCI arbiter is enabled, GNT0# is an input used to grant the bus, and GNT[3:1]# are placed into a high-impedance state. |

| 65, 63, 64, 116                                                                                                                 | INTA#<br>INTB#<br>INTC#<br>INTD# | IK        | <b>Interrupt (4 pins)</b><br>Asserted to request an interrupt. After assertion, it is necessary to remain asserted until the device driver clears it. INTx# is level-sensitive and asynchronous to the CLK. All INTx# signals are mapped into Assert_INTx and Deassert_INTx messages on the PCI Express interface.                               |

| 70                                                                                                                              | IRDY#                            | PI/O      | <i>Initiator Ready</i><br>Indicates that the initiator (PCI master) is ready to transfer data.                                                                                                                                                                                                                                                   |

| 62                                                                                                                              | LOCK#                            | PI/O      | <i>Lock Atomic Operation</i><br>Indicates an atomic operation to a bridge that might require multiple<br>transactions to complete.                                                                                                                                                                                                               |

| 122                                                                                                                             | M66EN                            | IK        | 66 MHz Enable<br>Indicates whether the PCI Bus is operating at 33 or 66 MHz.                                                                                                                                                                                                                                                                     |

| 61                                                                                                                              | PAR                              | PI/O      | <b>Parity</b><br>PAR is valid one clock after the address phase. For data phases, PAR is<br>valid one clock after IRDY# is asserted on write cycles, and one clock<br>after TRDY# is asserted on read cycles. PAR has the same timing as<br>AD[31:0], except it is delayed by one clock cycle.                                                   |

| 115                                                                                                                             | PCIRST#                          | PO        | <b>PCI Reset</b><br>This pin is to make a PCI device enter an initial state. PCIRST# is driven<br>when a PCI Express reset is detected, or when the secondary bus reset<br>bit of bridge control register is set.                                                                                                                                |

| 55                                                                                                                              | PERR#                            | PI/O      | <b>Parity Error</b><br>Indicates that a Data Parity error occurrs. Driven active by the receiving agent two clocks following the data containing the bad parity.                                                                                                                                                                                 |

| Pin(s) No.            | Symbol    | Attribute | Description                                                                                                                                                                                                                                                                                                          |

|-----------------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 105, 109, 102,<br>107 | REQ[3:0]# | PI/O      | <b>Bus Request (4 pins)</b><br>Indicates that an agent requires the use of the bus. When the internal PCI arbiter is enabled, REQ[3:0]# are inputs used to service external bus requests. When the external PCI arbiter is enabled, REQ0# is an output used to request bus control, and REQ[3:1]# are unused inputs. |

| 56                    | SERR#     | PI/O      | System Error<br>Indicates that an address parity error, data parity error on the special<br>cycle command, or other catastrophic errors occur.                                                                                                                                                                       |

| 67                    | STOP#     | PI/O      | <b>STOP</b><br>Indicates that the target (bus slave) is requesting that the master stops the current transaction.                                                                                                                                                                                                    |

| 68                    | TRDY#     | PI/O      | <i>Target Read</i><br>Indicates that the target (bus slave) is ready to transfer data.                                                                                                                                                                                                                               |

| 2                     | PME#      | IK        | <b>Power Management Event</b><br>Input used to monitor the request to change the system's power state.                                                                                                                                                                                                               |

## Table 5-2. IT8892E Pin Description of PCI Express Interface

| Pin(s) No. | Symbol | Attribute | Description                                                          |

|------------|--------|-----------|----------------------------------------------------------------------|

| 18         | DIN    | AI        | Receive Minus                                                        |

|            |        |           | PCI Express differential receive signal                              |

| 17         | DIP    | AI        | Receive Plus                                                         |

|            |        |           | PCI Express differential receive signal                              |

| 117        | PERST# | IK        | PCI Express Reset                                                    |

|            |        |           | Reset IT8892E when asserted.                                         |

| 20         | DON    | AO        | Transmit Minus                                                       |

|            |        |           | PCI Express differential transmit signal.                            |

| 21         | DOP    | AO        | Transmit Plus                                                        |

|            |        |           | PCI Express differential transmit signal.                            |

| 9          | CLKN   | AI        | PCI Express Clock Input Minus                                        |

|            |        |           | PCI Express differential 100MHz reference clock.                     |

| 10         | CLKP   | AI        | PCI Express Clock Input Plus                                         |

|            |        |           | PCI Express differential 100MHz reference clock.                     |

| 1          | WAKE#  | OD        | Wake Signal                                                          |

|            |        |           | Asserted when PME# is asserted and the link remains in the L2 state. |

## Table 5-3. IT8892E Pin Description of Miscellaneous Signal

| Pin(s) No. | Symbol   | Attribute | Description                                                       |

|------------|----------|-----------|-------------------------------------------------------------------|

| 27         | EECLK    | O8        | Serial EEPROM Clock                                               |

|            |          |           | Clock for EEPROM.                                                 |

| 26         | EECS#    | O8        | Serial EEPROM Chip Select                                         |

|            |          |           | Chip select for EEPROM.                                           |

| 29         | EERDDATA | IU        | Serial EEPROM Read Data                                           |

|            |          |           | Read data from EEPROM.                                            |

| 28         | EEWRDATA | O8        | Serial EEPROM Write Data                                          |

|            |          |           | Write data to EEPROM.                                             |

| 92         | EXTARB   | IK        | External Arbiter Enable                                           |

|            |          |           | When low, the internal PCI arbiter is enabled. When high, IT8892E |

|            |          |           | requests the PCI bus from an external PCI arbiter.                |

| 16         | RREF     | AO        | 12- $k\Omega$ Resistance for Reference Current                    |

| 90         | TEST_EN  | IK        | Test Mode Enable                                                  |

| Pin(s) No. | Symbol         | Attribute | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

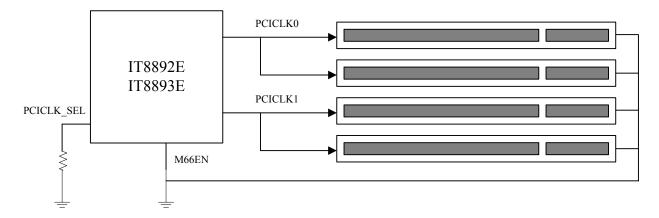

| 104        | PCICLK0        | PI/O      | <b>PCI Clock Output 0</b><br>PCICLK0 outputs the clock for external PCI devices while PCICLK_SEL is<br>pulled down whereas inputs the clock for internal PCI logic while<br>PCICLK_SEL is pulled up, which means the bridge does not provide the<br>clock to external devices. PCICLK0 outputs 62.5MHz with 50% duty cycle<br>while M66EN is high whereas 33.3MHz with 50% duty cycle while M66EN<br>is low. |

| 93         | PCICLK1        | PI/O      | <b>PCI Clock Output 1</b><br>PCICLK1 outputs the clock for external PCI devices as PCICLK0, but it does not provide the function as an input clock pin.                                                                                                                                                                                                                                                      |

| 91         | RST_SEL        | IK        | <b>Reset Source Select Pin</b><br>This pin has no functionality. Pull down this pin.                                                                                                                                                                                                                                                                                                                         |

| 126        | PCICLK_SE<br>L | IK        | <b>PCI Clock Source Select Pin</b><br>This pin is used to select the internal clock or external clock buffer as the<br>PCI clock source.                                                                                                                                                                                                                                                                     |

| 8          | NC             | -         | No Connect                                                                                                                                                                                                                                                                                                                                                                                                   |

## Table 5-4. IT8892E Pin Description of 7-Segment Display Signal

| Pin(s) No. | Symbol    | Attribute | Description                                     |

|------------|-----------|-----------|-------------------------------------------------|

| 118        | SEG_A     | PO        | 7-Segment LED A                                 |

| 119        | SEG_B     | PO        | 7-Segment LED B                                 |

| 120        | SEG_C     | PO        | 7-Segment LED C                                 |

| 121        | SEG_D     | PO        | 7-Segment LED D                                 |

| 127        | SEG_E/GP0 | PIO       | 7-Segment LED E / GPIO0                         |

| 128        | SEG_F/GP1 | PIO       | 7-Segment LED F / GPIO1                         |

| 32         | SEG_G/GP2 | PIO       | 7-Segment LED G / GPIO2                         |

| 24         | SEG_EN1/  | PIO       | 7-Segment LED Common Pin for High Digit / GPIO3 |

|            | GP3       |           |                                                 |

| 25         | SEG_EN2/  | PIO       | 7-Segment LED Common Pin for Low Digit / GPIO4  |

|            | GP4       |           |                                                 |

#### Table 5-5. IT8892E Pin Description of Power/Ground Signal

| Pin(s) No.                          | Symbol         | Attribute | Description                          |

|-------------------------------------|----------------|-----------|--------------------------------------|

| 35, 47, 57, 72,<br>84, 94, 110, 123 | VCCP           | I         | 3.3V PAD Power                       |

| 36, 48, 58, 73,<br>95, 111, 124     | GNDP           | I         | Ground of PAD                        |

| 23, 41, 78, 96,<br>112, 125         | VCCK           | I         | 1.8V Core Power                      |

| 22, 42, 60, 79,<br>97, 113,         | VSS            | I         | Ground of Core                       |

| 11, 12                              | VCC18A         |           | 1.8V Analog Transceiver Power of PHY |

| 13, 14, 15                          | GNDA           | I         | Analog Transceiver Ground of PHY     |

| 19                                  | VCC18A_AU<br>X | Ι         | 1.8V Analog AUX Power for AUX Power  |

| 7                                   | VCCK_AUX       |           | 1.8V AUX Power for Core              |

| 5                                   | LDOAUX_18<br>V | 0         | 1.8V LDO Output with Max 100mA       |

| 59                                  | LDO_18V        | 0         | 1.8V LDO Output with Max 200mA       |

| 6                                   | VSS_AUX        |           | Ground for Core of AUX Power         |

| 4                                   | VCCP_AUX       |           | 3.3V AUX Power for PAD               |

| 3                                   | GNDP_AUX       |           | Ground for PAD of AUX Power          |

#### 5.2 IT8893E Pin Description

| Pin(s) No.      | Symbol    | Attribute | Description                                                                                                                                    |

|-----------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 101, 100, 99,   | AD[31:0]  | PI/O      | PCI Address/Data Bus(32 pins)                                                                                                                  |

| 98, 89, 88, 86, |           |           | During the address phase, AD[31:0] contain the physical address of the                                                                         |

| 85, 83, 82, 81, |           |           | PCI transaction. During the data phase, AD[31:0] contain the data.                                                                             |

| 80, 77, 76, 75, |           |           |                                                                                                                                                |

| 74, 54, 53, 52, |           |           |                                                                                                                                                |

| 51, 50, 45, 44, |           |           |                                                                                                                                                |

| 43, 40, 39, 38, |           |           |                                                                                                                                                |

| 37, 34, 33, 31, |           |           |                                                                                                                                                |

| 30              |           |           |                                                                                                                                                |

| 87, 69, 49, 46  | CBE[3:0]# | PI/O      | Command/Byte Enable (4 pins)                                                                                                                   |

|                 |           |           | During the address phase, CBE[3:0]# contain the bus command. During                                                                            |

|                 |           |           | the data phase, CBE[3:0]# contain the byte enable. CBE0# corresponds                                                                           |

|                 |           | 51/2      | to byte 0 (AD[7:0]), and CBE3# corresponds to byte 3 (AD[31:24]).                                                                              |

| 66              | DEVSEL#   | PI/O      | Device Select                                                                                                                                  |

|                 |           |           | As an output, DEVSEL# indicates that the target (PCI slave) decodes its                                                                        |

|                 |           |           | address during the current bus transaction. As an input, DEVSEL#                                                                               |

| 74              |           |           | indicates whether a device on the bus is selected.                                                                                             |

| 71              | FRAME#    | PI/O      | FRAME                                                                                                                                          |

| 103, 108        | GNT[1:0]# | PI/O      | Indicates that the start of a PCI transaction. Bus Grant (2 pins)                                                                              |

| 103, 100        | GNT[1.0]# | FI/O      | Indicates that the central arbiter granted the bus to an agent. When the                                                                       |

|                 |           |           | internal PCI arbiter is enabled, GNT[1:0]# are outputs used to grant the                                                                       |

|                 |           |           | bus to external devices. When the external PCI arbiter is enabled, GNT0#                                                                       |

|                 |           |           | is an input used to grant the bus, and GNT[1]# is placed into a high-                                                                          |

|                 |           |           | impedance state.                                                                                                                               |

| 65, 63, 64, 116 | INTA#     | IK        | Interrupt (4 pins)                                                                                                                             |

|                 | INTB#     |           | Asserted to request an interrupt. After assertion, it is necessary to remain                                                                   |

|                 | INTC#     |           | asserted until the device driver clears it. INTx# is level-sensitive and                                                                       |

|                 | INTD#     |           | asynchronous to the CLK. All INTx# signals are mapped into Assert_INTx                                                                         |

|                 |           |           | and Deassert_INTx messages on the PCI Express interface.                                                                                       |

| 70              | IRDY#     | PI/O      | Initiator Ready                                                                                                                                |

|                 |           |           | Indicates that the initiator (PCI master) is ready to transfer data.                                                                           |

| 62              | LOCK#     | PI/O      | Lock Atomic Operation                                                                                                                          |

|                 |           |           | Indicates an atomic operation to a bridge that might require multiple                                                                          |

| 100             |           |           | transactions to complete.                                                                                                                      |

| 122             | M66EN     | IK        | 66 MHz Enable                                                                                                                                  |

| 04              | DAD       | PI/O      | Indicates whether the PCI Bus is operating at 33 or 66 MHz.                                                                                    |

| 61              | PAR       | PI/O      | Parity                                                                                                                                         |

|                 |           |           | PAR is valid one clock after the address phase. For data phases, PAR is valid one clock after IRDY# is asserted on write cycles, and one clock |

|                 |           |           | after TRDY# is asserted on read cycles. PAR has the same timing as                                                                             |

|                 |           |           | AD[31:0], except it is delayed by one clock cycle.                                                                                             |

| 115             | PCIRST#   | PO        | PCI Reset                                                                                                                                      |

|                 |           |           | This pin is to make a PCI device enter an initial state. PCIRST# is driven                                                                     |

|                 |           |           | when a PCI Express reset is detected, or when the secondary bus reset                                                                          |

|                 |           |           | bit of bridge control register is set.                                                                                                         |

| 55              | PERR#     | PI/O      | Parity Error                                                                                                                                   |

|                 |           |           | Indicates that a Data Parity error occurs. Driven active by the receiving                                                                      |

|                 |           |           | agent two clocks following the data containing the bad parity.                                                                                 |

| Pin(s) No. | Symbol    | Attribute | Description                                                                                                                                                                                                                                                                                                       |

|------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 102, 107   | REQ[1:0]# | PI/O      | <b>Bus Request (2 pins)</b><br>Indicates that an agent requires the use of the bus. When the internal PCI arbiter is enabled, REQ[1:0]# are inputs used to service external bus requests. When the external PCI arbiter is enabled, REQ0# is an output used to request bus control, and REQ[1]# is unused inputs. |

| 56         | SERR#     | PI/O      | System Error<br>Indicates that an address parity error, data parity error on the special<br>cycle command, or other catastrophic error occurs.                                                                                                                                                                    |

| 67         | STOP#     | PI/O      | <b>STOP</b><br>Indicates that the target (bus slave) is requesting that the master stops the current transaction.                                                                                                                                                                                                 |

| 68         | TRDY#     | PI/O      | <i>Target Ready</i><br>Indicates that the target (bus slave) is ready to transfer data.                                                                                                                                                                                                                           |

| 2          | PME#      | IK        | <b>Power Management Event</b><br>Input used to monitor the request to change the system's power state.                                                                                                                                                                                                            |

## Table 5-7. IT8893E Pin Description of PCI Express Interface

| Pin(s) No. | Symbol | Attribute | Description                                                                                |

|------------|--------|-----------|--------------------------------------------------------------------------------------------|

| 18         | DIN    | AI        | <b>Receive Minus</b><br>PCI Express differential receive signal                            |

| 17         | DIP    | AI        | <i>Receive Plus</i><br>PCI Express differential receive signal                             |

| 117        | PERST# | IK        | PCI Express Reset<br>Reset IT8893E when asserted.                                          |

| 20         | DON    | AO        | <i>Transmit Minus</i><br>PCI Express differential transmit signal.                         |

| 21         | DOP    | AO        | <i>Transmit Plus</i><br>PCI Express differential transmit signal.                          |

| 9          | CLKN   | AI        | PCI Express Clock Input Minus<br>PCI Express differential 100MHz reference clock.          |

| 10         | CLKP   | AI        | PCI Express Clock Input Plus<br>PCI Express differential 100MHz reference clock.           |

| 1          | WAKE#  | OD        | <i>Wake Signal</i><br>Asserted when PME# is asserted and the link remains in the L2 state. |

## Table 5-8. IT8893E Pin Description of Miscellaneous Signal

| Pin(s) No. | Symbol   | Attribute | Description                                                       |

|------------|----------|-----------|-------------------------------------------------------------------|

| 27         | EECLK    | O8        | Serial EEPROM Clock                                               |

|            |          |           | Clock for EEPROM.                                                 |

| 26         | EECS#    | O8        | Serial EEPROM Chip Select                                         |

|            |          |           | Chip select for EEPROM.                                           |

| 29         | EERDDATA | IU        | Serial EEPROM Read Data                                           |

|            |          |           | Read data from EEPROM.                                            |

| 28         | EEWRDATA | O8        | Serial EEPROM Write Data                                          |

|            |          |           | Write data to EEPROM.                                             |

| 92         | EXTARB   | IK        | External Arbiter Enable                                           |

|            |          |           | When low, the internal PCI arbiter is enabled. When high, IT8893E |

|            |          |           | requests the PCI bus from an external PCI arbiter.                |

| 16         | RREF     | AO        | 12- $k\Omega$ Resistance for Reference Current                    |

| 90         | TEST_EN  | IK        | Test Mode Enable                                                  |

| Pin(s) No.      | Symbol         | Attribute | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 104             | PCICLK0        | PI/O      | <b>PCI Clock Output 0</b><br>PCICLK0 outputs the clock for external PCI devices while PCICLK_SEL is<br>pulled down whereas inputs the clock for the internal PCI logic while<br>PCICLK_SEL is pulled up, which means the bridge does not provide the<br>clock to external devices. PCICLK0 outputs 62.5MHz with 50% duty cycle<br>while M66EN is high, and outputs 33.3MHz with 50% duty cycle while<br>M66EN is low. |

| 91              | RST_SEL        | IK        | <b>Reset Source Select Pin</b><br>This pin has no functionality. Pull down this pin.                                                                                                                                                                                                                                                                                                                                  |

| 126             | PCICLK_SE<br>L | IK        | <b>PCI Clock Source Select Pin</b><br>This pin is used to select the internal clock or external clock buffer as the PCI clock source.                                                                                                                                                                                                                                                                                 |

| 109, 105        | TP[1:0]        | PI        | Test Pin<br>Pull-up these pins at normal function mode.                                                                                                                                                                                                                                                                                                                                                               |

| 8, 93, 106, 114 | NC             | -         | No Connect                                                                                                                                                                                                                                                                                                                                                                                                            |

## Table 5-9. IT8892E Pin Description of 7-Segment Display Signal

| Pin(s) No. | Symbol          | Attribute | Description                                     |

|------------|-----------------|-----------|-------------------------------------------------|

| 118        | SEG_A           | PO        | 7-Segment LED A                                 |

| 119        | SEG_B           | PO        | 7-Segment LED B                                 |

| 120        | SEG_C           | PO        | 7-Segment LED C                                 |

| 121        | SEG_D           | PO        | 7-Segment LED D                                 |

| 127        | SEG_E/GP0       | PIO       | 7-Segment LED E / GPIO0                         |

| 128        | SEG_F/GP1       | PIO       | 7-Segment LED F / GPIO1                         |

| 32         | SEG_G/GP2       | PIO       | 7-Segment LED G / GPIO2                         |

| 24         | SEG_EN1/<br>GP3 | PIO       | 7-Segment LED Common Pin for High Digit / GPI03 |

| 25         | SEG_EN2/<br>GP4 | PIO       | 7-Segment LED Common Pin for Low Digit / GPIO4  |

## Table 5-10. IT8893E Pin Description of Power/Ground Signal

| Pin(s) No.                          | Symbol         | Attribute | Description                                  |

|-------------------------------------|----------------|-----------|----------------------------------------------|

| 35, 47, 57, 72,<br>84, 94, 110, 123 | VCCP           | I         | 3.3V PAD Power                               |

| 36, 48, 58, 73,<br>95, 111, 124     | GNDP           | I         | Ground of PAD                                |

| 23, 41, 78, 96,<br>112, 125         | VCCK           | I         | 1.8V Core Power                              |

| 22, 42, 60, 79,<br>97, 113,         | VSS            | I         | Ground of Core                               |

| 11, 12                              | VCC18A         | I         | 1.8V Analog Transceiver Power of PHY         |

| 13, 14, 15                          | GNDA           | I         | Analog Transceiver Ground of PHY             |

| 19                                  | VCC18A_AU<br>X | I         | 1.8V Analog AUX Power                        |

| 7                                   | VCCK_AUX       | I         | 1.8V AUX Power for Core                      |

| 5                                   | LDOAUX_18<br>V | 0         | 1.8V LDO Output with Max 100mA for AUX Power |

| 59                                  | LDO_18V        | 0         | 1.8V LDO Output with Max 200mA               |

| 6                                   | VSS_AUX        |           | Ground for Core of AUX Power                 |

| 4                                   | VCCP_AUX       | I         | 3.3V AUX Power for PAD                       |

| 3                                   | GNDP_AUX       |           | Ground for PAD of AUX Power                  |

Note: I/O cell types are described below:

I: Input PAD. IU: Input PAD with Internal Pull-Up. IK: Schmitt Trigger Input PAD. AI: Analog Input PAD. AO: Analog Output PAD. PI/O: PCI Bus Specified Input/Output PAD. PO: PCI Bus Specified Output PAD. O: Output PAD. OD: PCI Bus Specified Open Drain PAD. OB: 8mA Output PAD. All input pins are 5V tolerant except power and ground pins, PCI Express pins, EECLK, EECS#, and EEWRDATA.

This page is intentionally left blank.

#### 6. Functional Description

#### 6.1 Register Description

#### 6.1.1 Register Abbreviation

RO (READ ONLY): If a register is read only, writing data to this register has no effects.

WO (WRITE ONLY): If a register is write only, reading data to this register returns all zero.

R/W (READ/WRITE): A register with this attribute can be read and written data.

R/WS (READ/WRITE STICKY): A register with this attribute can be read and written data.

**R/WC (READ/WRITE CLEAR):** A register bit with this attribute can be read and written data. However, writing 1 clears the corresponding bit and writing 0 has no effect.

**R/WCS (READ/WRITE CLEAR STICKY):** A register bit with this attribute can be read and written data. However, writing 1 clears the corresponding bit and writing 0 has no effects.

The used radix indicator suffixes in this specification are listed below: Decimal number: "d" suffix or no suffix Binary number: "b" suffix Hexadecimal number: "h" suffix

#### 6.1.2 List of PCI Configuration Registers

| 31 24                            | 23 16                           | 15                               | 8        | 7                            | 0   | Index   |

|----------------------------------|---------------------------------|----------------------------------|----------|------------------------------|-----|---------|