### **CMOS IC FOR ELECTRONIC KEY**

IZ1990

#### **DESCRIPTION**

CMOS microcircuit is essentially an electronic carrier of the unique 64-bit digital code. The code is stored in the internal nonvolatile memory. The data exchange is performed by the protocol 1-Wire, which requires one sole data pin and the common pin. The microcircuit supports the function of the protocol 1-Wire of ROM search, which makes it possible for several devices to operate on one bus. This protocol determines the alteration conditions of the bus status and the time intervals during synchronization by the synchropulses cuts of the control device. Data read-out and writing are performed by the junior significant bit forward.

#### TRANSACTION SEQUENCE

Access sequence to IZ1990 via 1-Wire port is as follows:

- Initialization

- ROM function command

- Data read-out

#### **INITIALIZATION**

All transactions on the bus 1-Wire start with the initialization sequence. The initialization sequence consists of the reset pulse, applied by the bus master, followed by the availability pulse (or pulses), applied by the slave buses (or slave buses).

The availability pulse informs the bus master, that IZ1990 is connected to the bus and is ready for operation.

#### **ROM FUNCTIONS COMMANDS**

After the bus master has determined availability of the device, it can apply one out of four commands for operation with ROM. All commands for operation with ROM have the length of 8 bits. These commands are enumerated below (see also the diagram in Fig. 4)

## ROM Reading [33h] or [0Fh]

This command enables the bus master to read the 8-bit group code IZ1990, its unique 48-bit serial number and 8-bit control total (CRC). This command can be used only, if the bus has one device IZ1990. If the bus has more, than one slave, there will be a conflict of data, when all slave ones, when all slave ones attempt to apply at the same time

(the open drains will apply the mount AND). In IZ1990 the function ROM Reading may work with the command byte 33h or 0Fh, which ensures compatibility with the devices DS1990, which will respond only to the command word 0Fh.

### Comparison of ROM [55h] / ROM Skipping [CCh]

As the device IZ1990 contains only 64-bit ROM, the commands COMPARISON OF ROM and ROM SKIPPING from Protocol 1-Wire are not applied and do not case the response on the bus, if applied by the master.

#### Search of ROM [F0h]

When the system is started initially, the bus master may not know the numbers of the devices, connected to the bus 1-Wire or their 64-bit ROM codes. The ROM search command enables the bus master to use the exception process, in order to determine the 64-bit ROM codes of all slave devices on the bus. The ROM search process is essentially repetition of a simple procedure, consisting of three steps: bit reading, reading bit by bit supplement, and then writing of the required value of the given bit. The bus master performs this simple step procedure by each ROM bit. After completion of one entire run the bus master knows the ROM contents of one device. Numbers of the remaining devices and the codes of their ROMs can be determined by means of the additional runs.

#### SIGNALIZATION OF BUS 1-WIRE

In order to ensure integrity of data, the device IZ1990 requires the strict observance of the protocols. The protocol consists of the four types of signalization on one line: sequence of resetting with the reset pulse and availability pulse, low writing, high writing and data read-out. With exception of the availability pulse, all these signals are initialed by the master. The initialization sequence, required for start of any informational exchange with IZ1990 is indicated in Figure 1. After the reset pulse follows the availability pulse, which indicates, that the device IZ1990 is ready for reception of the ROM command. The bus master applies the reset pulse (t<sub>RSTL</sub>, minimum 480 us). Then the bus master vacates (releases) the line and switches over to the reception mode. Bus 1-Wire is pulled up to the status of the HIGH level via the pull-up resistor. After detection of the rising front at the data pin the device IZ1990 is in the stand-by mode (t<sub>PDH</sub>, from 15 to 60 us), and then applies the availability pulse (t<sub>PDL</sub>, from 60 to 240 us).

# **MASTER RX "RESET PULSE"** MASTER TX "RESET PULSE" t<sub>RSTH</sub> V<sub>PULLUP</sub> PULLUP MIN VIH MIN $V_{\rm IL\ MAX}$ 0V t<sub>RSTL</sub> t<sub>PDL</sub> t<sub>PDH</sub> RESISTOR MASTER IZ1990 $480us \le t_{RSTL} < *$ 480us ≤ $t_{RSTH}$ < $\infty$ (including recovery time) $15us \le t_{PDH} < 60us$

$60us \le t_{PDI} < 240us$

#### INITIALIZATION PROCEDURE. RESET AND AVAILABILITY PULSES

Figure 1. - Initialization of the device IZ1990

In order so as not to mask the interruption signals, applied from the other devices on the bus 1-Wire, the interval  $t_{RSTL} + t_{R}$  should always be less, than 960 us.

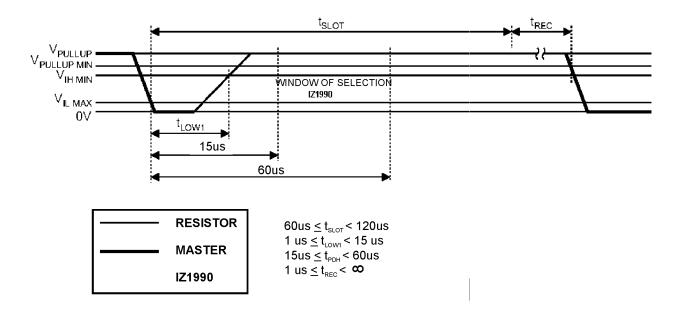

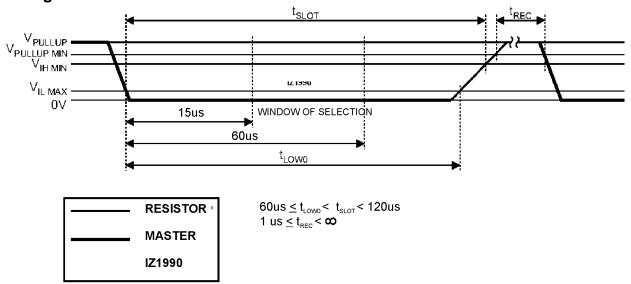

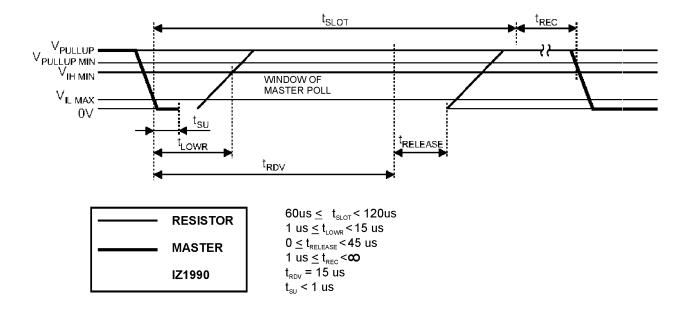

#### TIME INTERVALS OF READ-OUT / WRITING

Determinations of the time intervals for writing and read-out are illustrated in Figure 2. All time intervals are initiated by the master, which transfers the data line to the LOW level. The falling front on the data line synchronizes IZ1990 with the master, starting the delay time in IZ1990. During the write time the delay circuit determines, when IZ1990 will perform selection on the data line. For the time interval of the data read-out, if 0 is applied, the delay circuit determines, how long IZ1990 will hold the data line on the LOW level, interlocking 1, generated by the master. If the data bit is equal to 1, IZ1990 will leave the time interval of the data read-out unaltered.

#### TIME CHART OF READ-OUT / WRITING

## Writing 1

# Writing 0

#### Read-out

Figure 2 – Procedures of writing / read-out

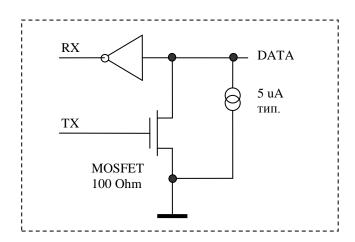

#### **EQUIVALENT CIRCUIT IZ1990**

Equivalent circuit 1-Wire of port IC IZ1990 is listed in Figure 3.

Figure 3 - Equivalent circuit 1-Wire of port IZ1990.

#### LIMIT MODE

| Parameter                       | Symbol           | Value         | Unit |

|---------------------------------|------------------|---------------|------|

| Voltage at pins relative to GND |                  | - 0.5 ÷ + 7.0 | V    |

| Operating temperature           | T <sub>por</sub> | - 40 ÷ + 85   | °C   |

| Limit temperature               | T <sub>stg</sub> | - 55 ÷ + 125  | °C   |

# **ELECTRIC PARAMETERS** ( \* Vpup = $2.8 \div 6.0 \text{ V}$ , T=- $40 \div +85$ )

| Parameter                  | Symbol          | Measurement<br>Mode     | Min  | Туре | Max      | Unit |

|----------------------------|-----------------|-------------------------|------|------|----------|------|

| Input voltage of logic "1" | $V_{IH}$        |                         | 2.2  |      | Vpup+0.3 | V    |

| Input voltage of logic "0" | V <sub>IL</sub> |                         | -0.3 |      | +0.8     | V    |

| Low level output voltage   | $V_{OL}$        | I <sub>OUT</sub> = 4 mA |      |      | 0.4      | V    |

| High level output voltage  | V <sub>OH</sub> |                         |      | Vpup | 6.0      | V    |

Note: Vpup is voltage level on the external pull-up resistor.

# **DYNAMIC PARAMETERS** ( \* Vpup = $2.8 \div 6.0 \text{ V}$ , T =- $40 \div +85$ )

| Parameter                             | Symbol               | Min | Туре | Max | Unit |

|---------------------------------------|----------------------|-----|------|-----|------|

| Duration of time interval             | t <sub>SLOT</sub>    | 60  |      | 120 | us   |

| Low level duration in writing 1       | t <sub>LOW1</sub>    | 1   |      | 15  | us   |

| Low level duration in writing 0       | t <sub>LOW0</sub>    | 60  |      | 120 | us   |

| Interval of valid data in read-out    | t <sub>RDV</sub>     |     | 15   |     | us   |

| Time for vacating the bus             | t <sub>RELEASE</sub> | 0   | 15   | 45  | us   |

| Time for presetting data for read-out | t <sub>SU</sub>      |     |      | 1   | us   |

| Restoration time                      | t <sub>REC</sub>     | 1   |      |     | us   |

| High level duration in reset          | t <sub>RSTH</sub>    | 480 |      |     | us   |

| Low level in reset                    | t <sub>RSTL</sub>    | 480 |      |     | us   |

| High level of availability pulse      | t <sub>PDH</sub>     | 15  |      | 60  | us   |

| Low level of availability pulse       | t <sub>PDL</sub>     | 60  |      | 240 | us   |

#### **CONTACT PADS DESCRIPTION**

| Pad N | Symbol | Description |

|-------|--------|-------------|

| 01    | GND    | Common pin  |

| 02    | TEST1  | Test pin    |

| 03    | TEST2  | Test pin    |

| 04    | DATA   | Data pin    |