## **JMF612**

### **SATAII To Flash Controller Datasheet**

Document No.: 61X-00002 / Revision: 1.04 / Issue Date: 09-12-2009

#### **JMicron Technology Corporation**

1F, No. 13, Innovation Road 1, Science-Based Industrial Park,

Hsinchu, Taiwan 300, R.O.C.

Tel: 886-3-5797389 Fax: 886-3-5799566

Website: http://www.jmicron.com

Copyright © 2009, JMicron Technology Corp. All Rights Reserved.

Printed in Taiwan 2009

JMicron and the JMicron Logo are trademarks of JMicron Technology Corporation in Taiwan and/or other countries.

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use implantation or other life supports application where malfunction may result in injury or death to persons. The information contained in this document does not affect or change JMicron's product specification or warranties. Nothing in this document shall operate as an express or implied license or environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will JMicron be liable for damages arising directly or indirectly from any use of the information contained in this document.

For more information on JMicron products, please visit the JMicron web site at <a href="http://www.JMicron.com">http://www.JMicron.com</a> or send e-mail to <a href="mailto-sales@jmicron.com">sales@jmicron.com</a>. For product application support, please send e-mail to <a href="mailto-fae@jmicron.com">fae@jmicron.com</a>.

**JMicron Technology Corporation**

1F, No.13, Innovation Road 1, Science-Based Industrial Park, Hsinchu, Taiwan 300, R.O.C.

Tel: 886-3-5797389 Fax: 886-3-5799566

Revision1.04 i Document No.:61X-00002

#### **Revision History**

| Revision | Effect Date |           | Author                               |                         |  |  |

|----------|-------------|-----------|--------------------------------------|-------------------------|--|--|

|          |             | Reference | Description of the Change            | Author                  |  |  |

| 1.01     | 06-26-2009  |           | Draft release.                       | M                       |  |  |

| 1.02     | 06-29-2009  |           | Electrical Characteristics modified. | M                       |  |  |

| 1.03     | 08-31-2009  |           | 10.4\10.5 modify.                    | M                       |  |  |

| 1.04     | 09-12-2009  |           | Delete Flash 2K page.                | $\mathcal{I}_{\Lambda}$ |  |  |

|          |             |           |                                      |                         |  |  |

Revision1.04 ii Document No.:61X-00002

#### **Table of Contents**

| Re  | vision Historyi                           |

|-----|-------------------------------------------|

| Та  | ble of Contentsii                         |

|     |                                           |

| Fig | gure Listv                                |

| Та  | ble List                                  |

|     |                                           |

| 1   | General Description                       |

| 2   | Features1                                 |

|     | 2.1 Compliance                            |

|     | 2.2 SATAI\II.                             |

|     |                                           |

|     | 2.3 CPU                                   |

|     |                                           |

|     | 2.5 SDRAM                                 |

|     | 2.6 SYSTEM                                |

|     | 2.7 Firmware                              |

|     |                                           |

| 3   | Block Diagram3                            |

|     |                                           |

| -   | Total Capacity                            |

| 5   | Package Pin Out (TFBGA 281 ball)          |

| /   |                                           |

| 6   | Package Outline Drawing (TFBGA 281 ball)5 |

| \   |                                           |

| 7   | Pin Descriptions8                         |

|     | 7.1 Pin type definition                   |

|     | 7.2 Pin definition                        |

|     |                                           |

| 8   | ECC Descriptions                          |

Revision1.04 iii Document No.:61X-00002

| 9  | SAT  | A Interface                                                                    | .16  |

|----|------|--------------------------------------------------------------------------------|------|

|    | 9.1  | Out of bank signaling                                                          | . 16 |

|    | 9.2  | COMRESET                                                                       | . 17 |

|    | 9.3  | COMINI                                                                         | . 19 |

|    | 9.4  | Power on sequence timing diagram                                               | . 21 |

|    | 9.5  | ATA command register                                                           | . 23 |

| 10 | Elec | trical Characteristics                                                         | .33  |

|    | 10.1 | Absolute Maximum Rating                                                        | . 33 |

|    | 10.2 | Recommended Power Supply Operation Conditions and Temperature                  | . 33 |

|    | 10.3 | Recommended External Clock Source Conditions                                   | . 34 |

|    | 10.4 | Power Supply DC Characteristics (SATA Idle mode and power saving mode disable) | . 34 |

|    | 10.5 | Power Supply DC Characteristics (SATA Active mode)                             | . 34 |

|    | 10.6 | I/O DC Characteristics                                                         | . 34 |

|    |      |                                                                                |      |

|    |      |                                                                                |      |

#### **Figure List**

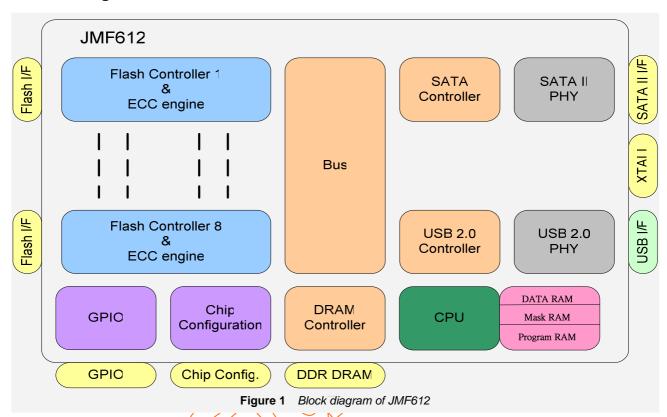

| Figure 1  | Block diagram of JMF612                                | 3 |

|-----------|--------------------------------------------------------|---|

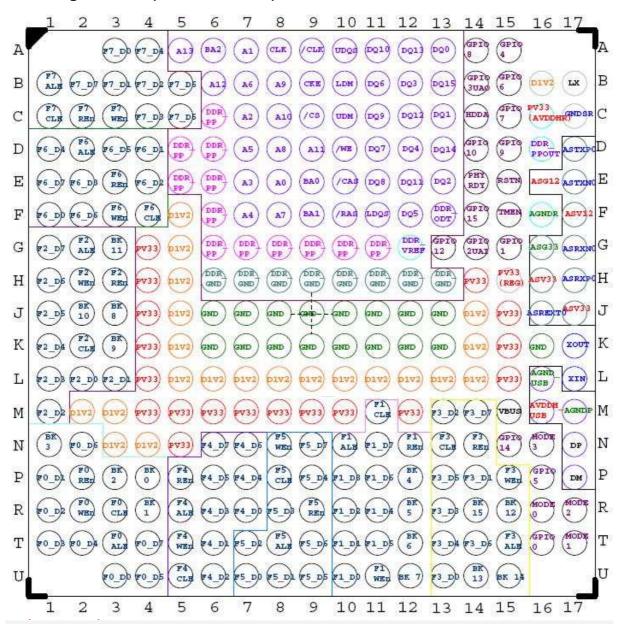

| Figure 2  | Package ball assignment of JMF612                      |   |

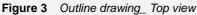

| Figure 3  | Outline drawing_ Top view                              | 5 |

| Figure 4  | Outline drawing_ Bottom view                           | 6 |

| Figure 5  | Outline drawing_ Side view                             | 7 |

| Figure 6  | Outline drawing_ symbol                                | 7 |

| Figure 7  | Allocation for ECC algorithm BCH in NAND Flash10       | 6 |

| Figure 8  | OOB signals17                                          | 7 |

| Figure 9  | Comreset sequence                                      | 3 |

| Figure 10 | Cominit sequence                                       | 0 |

| Figure 11 | Power on sequence2                                     | 1 |

|           | Table List                                             |   |

| Table 1   | Fotal capacity table                                   | 3 |

|           | Pin type definition table                              |   |

| Table 3   | Pin definition table                                   | 3 |

| Table 4   | QOB signal times                                       | 7 |

| Table 5   | Command table2                                         | 3 |

| Table 6 I | dentify device information default value24             | 1 |

| Table 7   | dentify device information default value (continued)25 | 5 |

| Table 8   | Features register value and settable operating mode32  | 2 |

#### 1 General Description

JMF612 is a single chip, supports external SDRAM, SATA II to NAND flash interface. It is native design to provide higher bandwidth for flash memory access.

JMF612 can support the maximum read and write speed to drive the limit of flash memory. JMF612 has the best supporting to the latest NAND flash memory, including Samsung, Toshiba, Hynix, Micron and IM Flash. It also provides the embedded hardware error correction code (ECC), wear leveling, and bad block management technology in this chip. In order to resolve compatibility issue, JMF612 provides the on line firmware upgrade ability.

JMF612 provides embedded processor, internal masked ROM, data SRAM, SATA link/transport layer, SATA PHY. Data swap between different interfaces can be done very efficiency by DMA without CPU involvement. Based on the efficient architecture, the JMF612 can provide the best performance.

#### 2 Features

#### 2.1 Compliance

- Compliant with Universal Serial Bus Specification Revision 2.0.

- Compliant with USB Mass Storage Class specification version 1.0.

- Compliant with Serial ATA International Organization; Serial ATA Revision 2.6.

#### 2.2 SATAI\II

Supports 1-port 1.5/3.0Gbps SATA I/II interface.

#### 2.3 CPU

- Embedded data buffer.

- 32bits Embedded processor.

- 32 KBytes Embedded masked program ROM.

- 128 KBytes Embedded system RAM.

#### 2.4 Flash

- Support maximum 16CE's Flash per channel.

- Support 5x/4x/3x nm Flash.

- Enhanced endurance by dynamic/static wear-leveling.

Revision1.04 1 Document No.:61X-00002

- Supports 4K/8K bytes page size.

- Supports dynamic power management.

- SMART (Self-Monitoring, Analysis and Reporting Technology).

- Data integrity under power-cycling.

- Supports online SATA/USB firmware update.

- Supports 8 bits Flash interface.

- Supports BCH 16/24 bits ECC.

#### **2.5 SDRAM**

- Supports DDR/DDR2

- Support 128Mbits to 2Gbits

#### 2.6 SYSTEM

- Integrated 1-USB2.0 port, 1-SATA II port and 8-channels Flash controller.

- LED indicator for USB2.0 and SATA read/write access.

- LED indicator for USB2.0 and SATA PHY link up.

- Provides 14 GPIO pins for customer.

- Provides UART and JTAG for 8/W debugging.

- Built-in power-up self-test (BIST):

- Manual and automatic self-diagnostics.

- Provides voltage low detect interrupt.

- 281-ball TFBGA package

#### 2.7 Firmware

- Support NCQ on this controller.

- Support LBA24 & LBA48 on this controller.

- Support 1 to 8 banks selected free.

- Support 2 to 8 channels selected free.

#### 3 Block Diagram

#### 4 Total Capacity

Table 1 Total capacity table

| density/per flash    | Support CE<br>pins/per flash | maximum flash<br>number | Total capacity |

|----------------------|------------------------------|-------------------------|----------------|

| 1G x 8 Bits (8Gb)    | 1 CE pin                     | 32                      | 32G Bytes      |

| 2G x 8 Bits (16Gb)   | 1 CE/ 2 CE pin               | 32                      | 64G Bytes      |

| 4G x 8 Bits (32Gb)   | 1 CE/ 2 CE pin               | 32                      | 128G Bytes     |

| 8G x 8 Bits (64Gb)   | 2 CE pin                     | 32                      | 256G Bytes     |

| 16G x 8 Bits (128Gb) | 4 CE pin                     | 32                      | 512G Bytes     |

Revision1.04 3 Document No.:61X-00002

#### 5 Package Pin Out (TFBGA 281 ball)

Figure 2 Package ball assignment of JMF612

Revision1.04 4 Document No.:61X-00002

#### 6 Package Outline Drawing (TFBGA 281 ball)

#### TOP VIEW

Revision1.04 5 Document No.:61X-00002

#### BOTTOM VIEW

Figure 4 Outline drawing\_ Bottom view

Revision1.04 6 Document No.:61X-00002

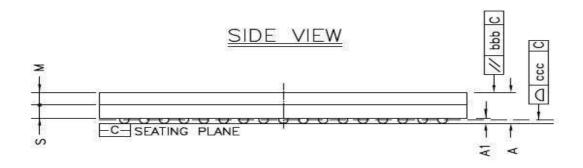

Figure 5 Outline drawing\_ Side view

|                              |     | Symbol        | Common Dimensions |  |

|------------------------------|-----|---------------|-------------------|--|

| Package :                    |     | LFBGA         |                   |  |

| Body Size:                   | E   | 12.000        |                   |  |

| Body Size.                   | Y   | D             | 12.000            |  |

| Ball Pitch :                 | ×   | eE            | 0.650             |  |

| bull Fitch .                 | Y   | eD            | 0.650             |  |

| Total Thickness :            |     | Α             | 1.400 MAX.        |  |

| Mold Thickness :             | -   | м             | 0.530 Ref.        |  |

| Substrate Thickness :        |     | s             | 0.560 Ref.        |  |

| Ball Diameter :              |     | 21            | 0.300             |  |

| Stand Off :                  | A1  | 0.160 ~ 0.260 |                   |  |

| Ball Width :                 | ь   | 0.270 ~ 0.370 |                   |  |

| Package Edge Tolerance :     | aga | 0.150         |                   |  |

| Mold Flatness :              |     | bbb           | 0.200             |  |

| Coplanarity:                 |     | ccc           | 0.080             |  |

| Ball Offset (Package) :      | ddd | 0.150         |                   |  |

| Ball Offset (Ball) :         | eee | 0.080         |                   |  |

| Ball Count :                 | n   | 281           |                   |  |

| E Dur Coult During           | X   | E1            | 10.400            |  |

| Edge Ball Center to Center : | Y   | D1            | 10.400            |  |

Figure 6 Outline drawing\_ symbol

Revision1.04 7 Document No.:61X-00002

#### 7 Pin Descriptions

#### 7.1 Pin type definition

**Table 2** Pin type definition table

| Pin Type | Definition                             |                                                                   |

|----------|----------------------------------------|-------------------------------------------------------------------|

| Α        | Analog                                 |                                                                   |

| D        | Digital                                |                                                                   |

| 1        | Input                                  |                                                                   |

| 0        | Output                                 |                                                                   |

| Ю        | Bi-directional                         | $\langle \rangle \langle \rangle \langle \rangle \langle \rangle$ |

| IL       | Internal week pull-low (Typical 75KΩ)  |                                                                   |

| IH       | Internal week pull-high (Typical 75KΩ) |                                                                   |

#### 7.2 Pin definition

Table 3 Pin definition table

| Signal Name | Ball No.                  | Туре                                              | Description                                                   |

|-------------|---------------------------|---------------------------------------------------|---------------------------------------------------------------|

| F0_[D0~D7]  | U3,P1,R1,T                | 10                                                | Flash data input/output                                       |

|             | 1,T2,U4N2,                | $\langle \rangle \langle \langle \rangle \rangle$ | The VO pins are used to output command, address, data and to  |

|             | T4 \                      | $\overline{}$                                     | input data during read operations.                            |

| F1_[D0~D7]  | U10,T10,R1                | > 10 <                                            | Flash data input/output                                       |

|             | 0,P10,R11,                | \\\ '                                             | The I/O pins are used to output command, address, data and to |

|             | T11,P11 <mark>,</mark> N1 |                                                   | input data during read operations.                            |

|             | (1 \ (                    |                                                   | <u> </u>                                                      |

| F2_[D0~D7]  | L2,L3,M1,L                | 10                                                | Flash data input/output                                       |

|             | 1,K1,J1H1,                | / ~                                               | The I/O pins are used to output command, address, data and to |

|             | G1\                       |                                                   | input data during read operations.                            |

| F3_[D0~D7]  | U13,P14,M                 | Ю                                                 | Flash data input/output                                       |

|             | 13,R13,T13                |                                                   | The I/O pins are used to output command, address, data and to |

|             | ,P13,T14,M                |                                                   | input data during read operations.                            |

|             | 14                        |                                                   |                                                               |

| F4_[D0~D7]  | R7,T6,U6,R                | 10                                                | Flash data input/output                                       |

|             | 6,P7,P6,N7,               |                                                   | The I/O pins are used to output command, address, data and to |

|             | N6                        |                                                   | input data during read operations.                            |

| F5_[D0~D7]  | U7,U8,T7,R                | 10                                                | Flash data input/output                                       |

|             | 8,P9,U9,T9,               |                                                   | The I/O pins are used to output command, address, data and to |

|             | N9                        |                                                   | input data during read operations.                            |

Revision1.04 8 Document No.:61X-00002

| Signal Name | Ball No.                                                                    | Туре | Description                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                             |      | · ·                                                                                                                                                                                                                                 |

| F6_[D0~D7]  | F1,D4,E4,E<br>2,D1,D3F2,<br>E1                                              | Ю    | Flash data input/output The I/O pins are used to output command, address, data and to input data during read operations.                                                                                                            |

| F7_[D0~D7]  | A3,B3,B4,C<br>4,A4,C5B5,<br>B2                                              | Ю    | Flash data input/output The I/O pins are used to output command, address, data and to input data during read operations.                                                                                                            |

| [F0~F7]_WEn | R2,U11,H2,<br>P15,T5,N8,<br>F3,C3                                           | 0    | Write Enable The WEn output controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WEn pulse                                                                                             |

| [F0~F7]_ALE | T3,N10,G2,<br>T15,R5,T8,<br>D2,B1                                           | 0    | Address Latch Enable  The ALE output controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WEn with ALE high.                                                     |

| [F0~F7]_CLE | R3,M11,K2,<br>N13,U5,P8,<br>F4,C1                                           | 0    | Command Latch Enable  The CLE output controls the activating path for commands sent to the command registers. When active high, commands are latched into the command register through the I/O ports on the edge of the WEn signal. |

| [F0~F7]_REn | P2,N12,H3,<br>N14,P5,R9,<br>E3,C2                                           | 0    | Read Enable The REn output is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of REn which also increments the internal column address counter by one.     |

| BK_[0n~15n] | P4,R4,P3,N<br>1,P12,R12,<br>T12,U12,J3<br>,K3,J2,G3,<br>R15,U14,U<br>15,R14 |      | Bank Selector The BKn output is the device selection control. When the device is in the Busy state, BKn high is ignored, and the device does not return to standby mode in program or erase operation.                              |

| GPIO0       | 716                                                                         | DIO  | General purpose I/O,                                                                                                                                                                                                                |

| GPI01       | G15                                                                         | DIO  | For normal function can be configured by customer.  General purpose I/O,                                                                                                                                                            |

|             |                                                                             |      | For normal function can be configured by customer.                                                                                                                                                                                  |

| GPIO2/UAI   | G14                                                                         | DIO  | General purpose I/O,                                                                                                                                                                                                                |

| 27/22/1/42  | 544                                                                         | DIO  | RS232 debug port.                                                                                                                                                                                                                   |

| GPIO3/UAO   | B14                                                                         | DIO  | General purpose I/O,                                                                                                                                                                                                                |

|             |                                                                             |      | RS232 debug port.                                                                                                                                                                                                                   |

| GPIO4       | A15                                                                         | DIO  | General purpose I/O,(F/W setting)                                                                                                                                                                                                   |

|             |                                                                             |      | 0: Run SATA 1.5Gbps.<br>1: Run SATA 3.0Gbps.                                                                                                                                                                                        |

Revision1.04 9 Document No.:61X-00002

| Ciamal Nama        | Dell No               | T       | Description                                                |

|--------------------|-----------------------|---------|------------------------------------------------------------|

| Signal Name        | Ball No.              | Туре    | Description                                                |

| GPIO5              | P16                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | 0: Load firmware code from flash to program memory.        |

|                    | _                     |         | 1: Load firmware code from host to program memory.         |

| GPIO6              | B15                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO7              | C15                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO8              | A14                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO9              | D15                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO10             | D14                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO12             | G13                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO14             | N15                   | DIO     | General purpose I/O,                                       |

|                    |                       |         | Can be configured by customer firmware.                    |

| GPIO15             | F14                   | DIO     | General purpose I/O,                                       |

| 0.1010             |                       | 2.0     |                                                            |

| DM                 | P17                   | ANO     | Can be configured by customer firmware.  USB Bus D Signal. |

| DP                 | N17 (                 | AIQ     | USB Bus D+ Signal.                                         |

| VBUS               | M15                   | ( Y)    | USB Cable Power Detector.                                  |

|                    |                       |         | The 51K and 100K resistances should be connected to divide |

| 10115 1105         |                       | / /     | the 5V cable power into 3.3V.                              |

| AGND_USB           | L16                   | AI \    | USB Analog Ground.                                         |

| AGNDP<br>AVDDH USB | M17<br>M16            | Al      | USB Analog Ground. USB Analog 3.3V Power Supply.           |

| TMEn               | F15                   | DIH     | Test Mode Enable, (internal pull-H)                        |

|                    | $ ( \ \ ), \ \rangle$ | <b></b> | This pin is reserved for IC mass production testing.       |

|                    | $\bigcup$             |         | Always Keep this pin to logic "1" in normal operation.     |

| MODE[3:0]          | N16,R17,T1            | IL      | Chip Operation Mode Selection.(internal 0000)              |

|                    | 7,R16                 |         | Ball B4 A3 B5 A4                                           |

| RSTn               | E15                   | DIH     | 0 0 0 0 System Global Reset Input.                         |

| 1.0111             |                       | ווט     | Active-low to reset the entire chip.                       |

|                    |                       |         | An external 10msec RC should be connected to this pin.     |

| HDDA               | C14                   | DO      | SATA Hard Disk Active.(GPIO21)                             |

|                    |                       |         | Can be configured by customer firmware.                    |

| PHYRDY             | E14                   | DO      | PHYRDY of SATA/USB output.                                 |

| XTALI              | L17                   | Al      | Crystal input pad                                          |

|                    |                       |         | It is connected to a 30MHz crystal.                        |

Revision1.04 10 Document No.:61X-00002

| Signal Name  | Ball No.       | Туре        | Description                                                            |

|--------------|----------------|-------------|------------------------------------------------------------------------|

|              |                |             | · ·                                                                    |

| XTALO        | K17            | AO          | Crystal output pad                                                     |

| ASV33        | 1140 147       | Λ1          | It is connected to a crystal.                                          |

| ASG33        | H16,J17<br>G16 | Al          | SATA Analog 3.3V Power Supply.                                         |

| ASREXTO      | J16            | AI<br>AI    | SATA Analog Ground.  External Reference Resistance.                    |

| ASKEATU      | 316            | Ai          | A $12K\Omega\pm1\%$ external resistor should be connected to this pin. |

| ASRXP0       | H17            | Al          | Serial ATA RX+ signal.                                                 |

| ASINAFU      | 1117           |             | A 10nF CAP. should be connected between this pin and SATA              |

|              |                |             | connector.                                                             |

| ASRXN0       | G17            | Al          | Serial ATA RX- signal.                                                 |

|              | 0              | ,           | A 10nF CAP. should be connected between this pin and SATA              |

|              |                |             | connector.                                                             |

| ASV12        | F17            | Al          | SATA Analog 1.2V Power Supply.                                         |

|              |                |             | This power could be sourced from internal 1.2V voltage regulator       |

|              |                |             | through AVREG pin.                                                     |

| ASG12        | E16            | Al          | SATA Analog Ground.                                                    |

| ASTXN0       | E17            | AO          | Serial ATA TX- signal                                                  |

|              |                |             | A 10nF CAP. should be connected between this pin and SATA              |

|              |                |             | connector.                                                             |

| ASTXP0       | D17            | AO          | Serial ATA TX+ signal.                                                 |

|              |                |             | A 10nF CAP should be connected between this pin and SATA               |

|              |                |             | connector.                                                             |

| LX           | B17            | AO          | Switching Regulator output.                                            |

| GNDSR        | C17            | AI          | Switching regulator ground                                             |

| PV33(REG)    | H15 (          | Al          | Switching regulator 3.3V power supply                                  |

| DDR PPOUT    | D16            | AO          | DDR regulator output                                                   |

| AGNDR        | F16            | AI          | DDR regulator ground                                                   |

| PV33(AVDDHR) | C16            | AI          | DDR regulator 3.3v power supply                                        |

| A0           | <b>€</b> 8     | 0           | Address inputs: Provide the row address for ACTIVE                     |

| A1           | AZ             |             | commands,                                                              |

| A2 /         | C7             | $\setminus$ | and the column address and auto precharge bit                          |

| A3           | E7             | <b>/</b>    | (A10) for READ/WRITE commands, to select one location                  |

| A4 /         | F7             |             | out of the memory array in the respective bank. A10 sampled            |

| A5           | D7             |             | during a PRECHARGE command determines whether                          |

| A6           | B7             |             | the PRECHARGE applies to one bank (A10 LOW, bank                       |

| A7           | F8             |             | selected                                                               |

| A8           | D8             |             | by BA[2:0]) or all banks (A10 HIGH). The address                       |

| A9           | B8             | ]           | inputs also provide the op-code during a LOAD MODE command.            |

| A10          | C8             |             | Command.                                                               |

| A11          | D9             |             |                                                                        |

| A12          | B6             |             |                                                                        |

| A13          | A5             |             |                                                                        |

| BA0          | E9             | 0           | Bank address inputs: BA[2:0] define to which bank an                   |

| BA1          | F9             |             | ACTIVE, READ, WRITE, or PRECHARGE command is being                     |

Revision1.04 11 Document No.:61X-00002

| Signal Name | Ball No.   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA2         | A6         |      | applied. BA[2:0] define which mode register, including MR, EMR, EMR(2), and EMR(3), is loaded during the LOAD MODE command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CK          | A8         | 0    | Clock: CK and CK# are differential clock inputs. All address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CK#         | А9         |      | and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#.  Output data (DQ and DQS/DQS#) is referenced to the crossings of CK and CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CKE         | В9         | 0    | Clock enable: CKE (registered HIGH) activates and CKE (registered LOW) deactivates clocking circuitry on the DDR2 SDRAM. The specific circuitry that is enabled/disabled is dependent on the DDR2 SDRAM configuration and operating mode. CKE LOW provides precharge powerdown and SELF REFRESH operation (all banks idle), or ACTIVATE power-down (row active in any bank). CKE is synchronous for power-down entry, power-down exit, output disable, and for self refresh entry. CKE is asynchronous for SELF REFRESH exit. Input buffers (excluding CK, CK#, CKE, and ODT) are disabled during power-down. Input buffers (excluding CKE) are disabled during self refresh. CKE is an SSTL 18 input but will detect a LVCMOS LOW level once Vdd is applied during first power-up. After Vref has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper SELF REFRESH operation, Vref must be maintained. |

| CS#         | C9         | 0    | Chip select: CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered high. CS# provides for external bank selection on systems with multiple ranks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |            |      | CS# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDM         | B10<br>C10 | 0    | Input data mask: DM is an input mask signal for write data. Input data is masked when DM is concurrently sampled HIGH during a WRITE access. DM is sampled on both edges of DQS. Although DM balls are input-only, the DM loading is designed to match that of DQ and DQS balls. LDM is DM for lower byte DQ0-DQ7 and UDM is DM for upper byte DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Revision1.04 12 Document No.:61X-00002

| Signal Name | Ball No.   | Туре                | Description                                                                                               |

|-------------|------------|---------------------|-----------------------------------------------------------------------------------------------------------|

| ODT         | F13        |                     | On-die termination: ODT (registered HIGH) enables                                                         |

|             |            |                     | termination                                                                                               |

|             |            |                     | resistance internal to the DDR2 SDRAM. When                                                               |

|             |            |                     | enabled, ODT is only applied to each of the following balls: DQ0-DQ15, LDM, UDM, LDQS, LDQS#, UDQS, and   |

|             |            |                     | UDQS# for the x16; DQ0–DQ7, DQS, DQS#, RDQS, RDQS#,                                                       |

|             |            |                     | and DM for the x8; DQ0–DQ3, DQS, DQS#, and DM for                                                         |

|             |            |                     | the x4. The ODT input will be ignored if disabled via the                                                 |

|             |            |                     | LOAD MODE command.                                                                                        |

| RAS#        | F10        | 0                   | Command inputs: RAS#, CAS#, and WE# (along with                                                           |

| CAS#        | E10        |                     | CS#) define the command being entered.                                                                    |

| WE#         | D10        |                     |                                                                                                           |

| DQ0         | A13        | Ю                   | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ1         | C13        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ2         | E13        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ3         | B12        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ4         | D12        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ5<br>DQ6  | F12        |                     | Data input/output: Bidirectional data bus for x16.  Data input/output: Bidirectional data bus for x16.    |

| DQ6<br>DQ7  | B11<br>D11 |                     | Data input/output: Bidirectional data bus for x16.  Data input/output: Bidirectional data bus for x16.    |

| DQ7         | E11        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ9         | C11        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ10        | A11        | _                   | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ11        | E12        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ12        | C12 /      |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ13        | A12        |                     | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ14        | D13        | $\rangle$ $\langle$ | Data input/output: Bidirectional data bus for x16.                                                        |

| DQ15        | B13        | \\\                 | Data input/output: Bidirectional data bus for x16.                                                        |

| LDQS        | F11        | 10                  | Data strobe for lower byte: Output with read data, input                                                  |

|             | ( )        |                     | with write data for source synchronous operation.                                                         |

|             |            |                     | Edge-aligned with read data, center-aligned with write                                                    |

|             | $\sim$     |                     | data. LDQS# is only used when differential data strobe                                                    |

| lunas       | ( ) ( )    | 10                  | mode is enabled via the LOAD MODE command.                                                                |

| UDQS        | A10        | Ю                   | Data strobe for upper byte: Output with read data, input                                                  |

|             |            |                     | with write data for source synchronous operation.  Edge-aligned with read data, center-aligned with write |

|             |            |                     | data. UDQS# is only used when differential data strobe                                                    |

|             |            |                     | mode is enabled via the LOAD MODE command.                                                                |

| PV33        | G4         | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | H4         | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | H14        | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | J4         | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | J15        | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | K4         | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

| PV33        | K15        | DI                  | I/O Pad 3.3V Power Supply.                                                                                |

Revision1.04 13 Document No.:61X-00002

| Signal Name  | Ball No.   | Туре     | Description                            |

|--------------|------------|----------|----------------------------------------|

| PV33         | L4         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | L15        | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M4         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M5         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M6         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M7         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M8         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M9         | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M10        | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | M12        | DI       | I/O Pad 3.3V Power Supply.             |

| PV33         | N5         | DI       | I/O Pad 3.3V Power Supply.             |

| GND          | J6         | DI       | Ground.                                |

| GND          | J7         | DI       | Ground.                                |

| GND          | J8         | DI       | Ground.                                |

| GND          | J9         | DI       | Ground.                                |

| GND          | J10        | DI       | Ground.                                |

| GND          | J11        | DI       | Ground.                                |

| GND          | J12        | DI       | Ground.                                |

| GND          | J13        | DI       | Ground.                                |

| GND          | K6         | DI       | Ground                                 |

| GND          | K7         | DI       | Ground.                                |

| GND          | K8         | DI       | Ground.                                |

| GND          | K9         | DI       | Ground.                                |

| GND          | K10        | 101/     | Ground.                                |

| GND          | K11 (      | DI       | Ground.                                |

| GND          | K12        | DI       | Ground.                                |

| GND          | K13        | DI \     | Ground.                                |

| GND          | K16        | DI       | Ground.                                |

| DV12         | F5\        | pi /     | 1.2V Power Supply.                     |

| DV12         | <b>G</b> 5 | DI       | 1.2V Power Supply.                     |

| DV12         | H5/        | DI       | 1.2V Power Supply.                     |

| DV12         | J5         | DI       | 1.2V Power Supply.                     |

| DV12         | J14        | DI       | 1.2V Power Supply.                     |

| DV12         | K5         | DI       | 1.2V Power Supply.                     |

| DV12         | K14        | DI       | 1.2V Power Supply.                     |

| DV12<br>DV12 | L5<br>L6   | DI       | 1.2V Power Supply                      |

|              |            | DI       | 1.2V Power Supply                      |

| DV12<br>DV12 | L7<br>L8   | DI       | 1.2V Power Supply.  1.2V Power Supply. |

| DV12<br>DV12 | L8<br>L9   | DI<br>DI | 1.2V Power Supply.  1.2V Power Supply. |

| DV12<br>DV12 | L10        | DI       | 1.2V Power Supply.  1.2V Power Supply. |

| DV12         | L10        | DI       | 1.2V Power Supply.  1.2V Power Supply. |

| DV12<br>DV12 | L11        | DI       | 1.2V Power Supply.  1.2V Power Supply. |

| DV12         | L12        | DI       | 1.2V Power Supply.                     |

| DVIZ         | LIJ        | וט       | 1.2v rowel Supply.                     |

Revision1.04 14 Document No.:61X-00002

| Signal Name | Ball No. | Туре | Description                    |

|-------------|----------|------|--------------------------------|

| DV12        | L14      | DI   | 1.2V Power Supply.             |

| DV12        | M2       | DI   | 1.2V Power Supply.             |

| DV12        | М3       | DI   | 1.2V Power Supply.             |

| DV12        | N3       | DI   | 1.2V Power Supply.             |

| DV12        | N4       | DI   | 1.2V Power Supply.             |

| DV12        | B16      | DI   | 1.2V Power Supply.             |

| DDR_PP      | C6       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | D5       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | D6       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | E5       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | E6       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | F6       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G6       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G7       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G8       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G9       | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G10      | DI   | DDR PAD 1.8V Power Supply      |

| DDR_PP      | G11      | DI   | DDR PAD 1.8V Power Supply      |

| DDR_VREF    | G12      | DI   | DDR PAD 0.9V reference voltage |

| DDR_GND     | H6       | DI   | Ground for DDR PAD             |

| DDR_GND     | H7       | DI   | Ground for DDR PAD             |

| DDR_GND     | H8       | DI   | Ground for DDR PAD             |

| DDR_GND     | H9       | DI/\ | Ground for DDR PAD             |

| DDR_GND     | H10      | DI   | Ground for DDR PAD             |

| DDR_GND     | H11      | DI ( | Ground for DDR PAD             |

| DDR_GND     | H12      | DI > | Ground for DDR PAD             |

| DDR_GND     | H13      | V IQ | Ground for DDR PAD             |

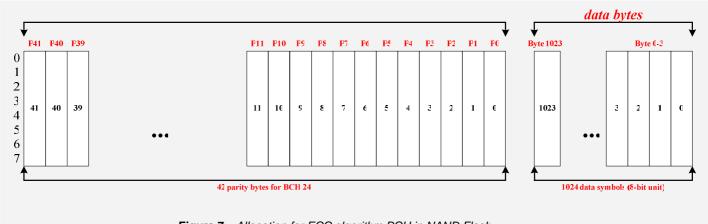

#### 8 ECC Descriptions

Please refer to FIG. 4 that is a diagram illustrating an allocating method of a spare area in each page of a NAND flash memory, where in the specific ECC algorithm utilizes a Bose, Chaudhuri and Hocquengham (BCH) ECC algorithm. When a BCH 16 ECC algorithm encodes the data in the NAND flash memory, the parity code generated in the encoding process may occupy 28 bytes of the spare area in each page. When a BCH 24 ECC algorithm encodes the data in the NAND flash memory, the parity code generated in the encoding process may occupy 42 bytes of the spare area in each page.

When a BCH 16 algorithm decodes the data in the NAND flash memory, the data can be decoded correctly if the error bit happened in two sector (1024Bytes) is 16. When a BCH 24 algorithm decodes the

Revision1.04 15 Document No.:61X-00002

data in the NAND flash memory, the data can be decoded correctly if the error bit happened in two sector is 24.

Figure 7 Allocation for ECC algorithm BCH in NAND Flash

#### 9 SATA Interface

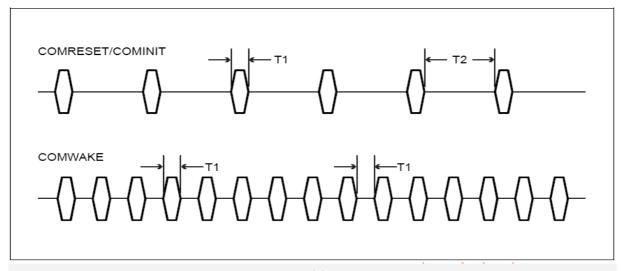

#### 9.1 Out of bank signaling

There shall be three Out Of Band (OOB) signals used/detected by the Phy: COMRESET, COMINIT, and COMWAKE. COMINIT, COMRESET and COMWAKE OOB signaling shall be achieved by transmission of either a burst of four Gen1 ALIGNe primitives or a burst composed of four Gen1 Dwords with each Dword composed of four D24.3 characters, each burst having duration of 160 Uloob. Each burst is followed by idle periods (at common mode levels), having durations as depicted in Figure 5 and Table 2.

Revision1.04 16 Document No.:61X-00002

Figure 8 OOB signals

| Table 4  | OOB signal times    |

|----------|---------------------|

| I GOIC T | OOD digital tillioo |

| Time | Value                                    |

|------|------------------------------------------|

| T1   | 160 Ul <sub>oob</sub> (106.7 ns nominal) |

| T2   | 480 Ul <sub>oob</sub> (320 ns nominal)   |

#### 9.2 COMRESET

COMRESET always originates from the host controller, and forces a hardware reset in the device. It is indicated by transmitting bursts of data separated by an idle bus condition. The OOB COMRESET signal shall consist of no less than six data bursts, including inter-burst temporal spacing.

The COMRESET signal shall be:

1) Sustained/continued uninterrupted as long as the system hard reset is asserted, or 2) Started during the system hardware reset and ended some time after the negation of system hardware reset, or 3) Transmitted immediately following the negation of the system hardware reset signal.

The host controller shall ignore any signal received from the device from the assertion of the hardware reset signal until the COMRESET signal is transmitted. Each burst shall be 160 Gen1 UI's long (106.7 ns) and each inter-burst idle state shall be 480 Gen1 UI's long (320 ns). A COMRESET detector looksfor four consecutive bursts with 320 ns spacing (nominal). Any spacing less than 175 ns or greater

Revision1.04 17 Document No.:61X-00002

than 525 ns shall invalidate the COMRESET detector output. The COMRESET interface signal to the Phy layer shall initiate the Reset sequence shown in Figure 6 below. The interface shall be held inactive for at least 525 ns after the last burst to ensure far-end detector detects the negation properly.

Figure 9 Comreset sequence

#### Description:

- 1. Host/device are powered and operating normally with some form of active communication.

- 2. Some condition in the host causes the host to issue COMRESET

- 3. Host releases COMRESET. Once the condition causing the COMRESET is released, the host releases the COMRESET signal and puts the bus in a quiescent condition.

- 4. Device issues COMINIT When the device detects the release of COMRESET, it responds with a COMINIT. This is also the entry point if the device is late starting. The device may initiate communications at any time by issuing a COMINIT.

- 5. Host calibrates and issues a COMWAKE.

Revision1.04 18 Document No.:61X-00002

- 6. Device responds The device detects the COMWAKE sequence on its RX pair and calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGNP Dwords have been sent for 54.6us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGNP primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGNP Dwords at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device enters an error state.

- 7. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGNP. This ensures interoperability with multi-generational and synchronous designs. If no ALIGNP is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence repeating indefinitely until told to stop by the Application layer.

- 8. Device locks the device locks to the ALIGN sequence and, when ready, sends SYNCP indicating it is ready to start normal operation.

- 9. Upon receipt of three back-to-back non-ALIGNP primitives, the communication link is established and normal operation may begin.

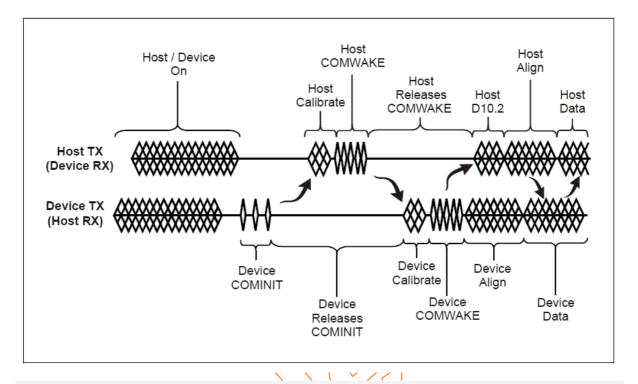

#### 9.3 COMINI

COMINIT always originates from the drive and requests a communication initialization. It is electrically identical to the COMRESET signal except that it originates from the device and is sent to the host. It is used by the device to request a reset from the host in accordance to the sequence shown in Figure 7, below:

Revision1.04 19 Document No.:61X-00002

Figure 10 Cominit sequence

#### Description:

- 1. Host/device are powered and operating normally with some form of active communication.

- 2. Some condition in the device causes the device to issues a COMINIT

- 3. Host calibrates and issues a COMWAKE

- 4. Device responds The device detects the COMWAKE sequence on its RX pair and calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGN Dwords have been sent for 54.6 us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGN primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGN Dwords at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device enters an error state.

- 5. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see

Revision1.04 20 Document No.:61X-00002

section 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6 us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGN<sub>P</sub>. This ensures interoperability with multi-generational and synchronous designs. If no ALIGN<sub>P</sub> is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence – repeating indefinitely until told to stop by the Application layer.

- 6. Device locks the device locks to the ALIGN sequence and, when ready, sends SYNCP indicating it is ready to start normal operation.

- 7. Upon receipt of three back-to-back non-ALIGN<sub>P</sub> primitives, the communication link is established and normal operation may begin.

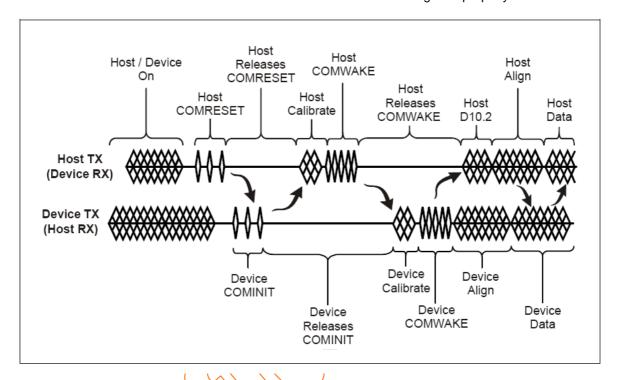

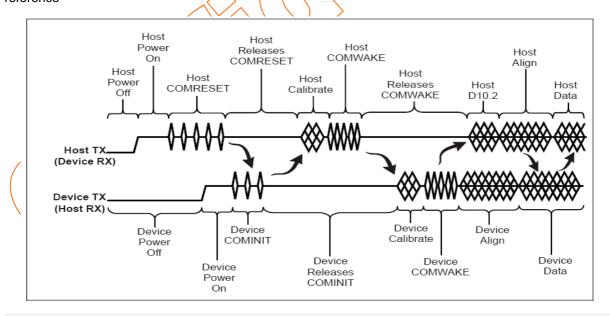

#### 9.4 Power on sequence timing diagram

The following timing diagrams and descriptions are provided for clarity and are informative. The state diagrams provided in section 8.4 comprise the normative behavior specification and is the ultimate reference

Figure 11 Power on sequence

Description:

Revision1.04 21 Document No.:61X-00002

- Host/device power-off Host and device power-off.

- 2. Power is applied Host side signal conditioning pulls TX and RX pairs to neutral state (common mode voltage).

- 3. Host issues COMRESET

- 4. Host releases COMRESET. Once the power-on reset is released, the host releases the COMRESET signal and puts the bus in a quiescent condition.

- 5. Device issues COMINIT When the device detects the release of COMRESET, it responds with a COMINIT. This is also the entry point if the device is late starting. The device may initiate communications at any time by issuing a COMINIT.

- 6. Host calibrates and issues a COMWAKE.

- 7. Device responds The device detects the COMWAKE sequence on its RX pair and calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGN<sub>P</sub> primitives have been sent for 54.6 us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGN<sub>P</sub> primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGN<sub>P</sub> primitives at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device shall enter an error state.

- 8. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6 us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGN<sub>P</sub>. This insures interoperability with multi-generational and synchronous designs. If no ALIGN<sub>P</sub> is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence repeating indefinitely until told to stop by the Application layer.

- 9. Device locks the device locks to the ALIGN sequence and, when ready, sends the SYNC<sub>P</sub> primitive indicating it is ready to start normal operation.

- 10.Upon receipt of three back-to-back non-ALIGN<sub>P</sub> primitives, the communication link is established and normal operation may begin.

Revision1.04 22 Document No.:61X-00002

#### 9.5 ATA command register

This table with the following paragraphs summarizes the ATA command set.

Table 5 Command table

| Command Name                 | Codo       | PARAMETERS USED |    |            |            |            |                     |  |

|------------------------------|------------|-----------------|----|------------|------------|------------|---------------------|--|

| Command Name                 | Code       | sc              | SN | CY         | DR         | HD         | FT                  |  |

| CHECK POWER MODE             | E5h        | Х               | Х  | Х          | 0          | x          | X                   |  |

| EXECUTE DIAGNOSTICS          | 90h        | Х               | Х  | Х          | 0          | Х          | X                   |  |

| FLUSH CACHE                  | E7h        | Х               | Х  | Х          | 0          | 0          | X                   |  |

| IDENTIFY DEVICE              | ECh        | Х               | Х  | X          | \ <u>\</u> | \x/        | $\langle x \rangle$ |  |

| IDLE                         | E3h        | 0               | Х  | ×          | /0         | X          | X                   |  |

| IDLE IMMEDIATE               | E1h        | Х               | Х  | ×          | 0          | X          | Х                   |  |

| INITIALIZE DEVICE PARAMETERS | 91h        | 0               | X  | X          | 0          | <b>)</b> 0 | Х                   |  |

| READ DMA                     | C8h or C9h | 0               | 0  | 6          | O          | 0          | Х                   |  |

| READ MULTIPLE                | C4h        | 0               | 9  | 6          | 0          | 0          | Х                   |  |

| READ SECTOR(S)               | 20h or 21h | ( 0 (           | 0  | <b>√</b> 0 | 0          | 0          | Х                   |  |

| READ VERIFY SECTOR(S)        | 40h or 41h | 6               |    | 0          | 0          | 0          | Х                   |  |

| RECALIBRATE                  | 10h        | -X              | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY DISABLE PASSWORD    | F6h        | <b>X</b>        | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY ERASE PREPARE       | F3h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY ERASE UNIT          | F4b        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY FREEZE LOCK         | F5h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY SET PASSWORD        | F1h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SECURITY UNLOCK              | F2h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SEEK                         | 7xh        | Х               | Х  | 0          | 0          | 0          | Х                   |  |

| SET FEATURES                 | EFh        | 0               | Х  | Х          | 0          | Х          | 0                   |  |

| SET MULTIPLE MODE            | C6h        | 0               | Х  | Х          | 0          | Х          | Х                   |  |

| SLEEP                        | E6h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| SMART                        | B0h        | Х               | Х  | 0          | 0          | Х          | 0                   |  |

| STANDBY                      | E2h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| STANDBY IMMEDIATE            | E0h        | Х               | Х  | Х          | 0          | Х          | Х                   |  |

| WRITE DMA                    | CAh or CBh | 0               | 0  | 0          | 0          | 0          | Х                   |  |

Revision1.04 23 Document No.:61X-00002

| WRITE MULTIPLE  | C5h        | 0 | 0 | 0 | 0 | 0 | Х |

|-----------------|------------|---|---|---|---|---|---|

| WRITE SECTOR(S) | 30h or 31h | 0 | 0 | 0 | 0 | 0 | Х |

#### Note:

O = Valid, X = Don't care

SC = Sector Count Register

SN = Sector Number Register

CY = Cylinder Low/High Register

DR = DEVICE SELECT Bit (DEVICE/HEAD Register Bit 4)

HD = HEAD SELECT Bit (DEVICE/HEAD Register Bit 3-0)

FT = Features Register

#### ATA COMMAND SPECIFICATIONS

#### **CHECK POWER MODE (E5h)**

The host can use this command to determine the current power management mode.

#### **EXECUTE DIAGNOSITICS (90h)**

This command performs the internal diagnostic tests implemented by the drive. See ERROR register for dianostic codes.

#### **FLUSH CACHE (E7h)**

This command is used by the host to request the device to flush the write cache. If there is data in the write cache, that data shall be written to the media. The BSY bit shall remain set to one until all data has been successfully written or an error occurs.

#### IDENTIFY DEVICE (ECh)

This commands read out 512Bytes of drive parameter information. Parameter Information consists of the arrangement and value as shown in the following table. This command enables the host to veceive the Identify Drive Information from the device.

Table 6 Identify device information default value

| Word | Value | F/V | Description |                                               |  |

|------|-------|-----|-------------|-----------------------------------------------|--|

|      |       |     | Genera      | al configuration bit-significant information: |  |

|      |       | F   | 15          | 0 = ATA device                                |  |

| 0    | 0040h | Х   | 14-8        | Retired                                       |  |

|      |       | F   | 7           | 1 = removable media device                    |  |

|      |       | Х   | 6           | Obsolete                                      |  |

Revision1.04 24 Document No.:61X-00002

|   |       | Х | 5-3   | Retired                 |

|---|-------|---|-------|-------------------------|

|   |       | F | 2     | Reserved                |

|   |       | Х | 1     | Retired                 |

|   |       | F | 0     | Reserved                |

| 1 | XXXXh | Х | Numbe | er of logical cylinders |

#### Table 7 Identify device information default value (continued)

| Word  | Value    | F/V  | Description                                                             |

|-------|----------|------|-------------------------------------------------------------------------|

|       |          | 170  | Description                                                             |

| 2     | C837h    | V    | Specific configuration                                                  |

| 3     | 00XXh    | Х    | Number of logical heads                                                 |

| 4-5   | XXXXh    | Х    | Retired                                                                 |

| 6     | XXXXh    | Х    | Number of logical sector per logical track                              |

| 7-8   | XXXXh    | V    | Reserved for assignment by the CompactFlash_Association                 |

| 9     | 000Eh    | Х    | Retired                                                                 |

| 10-19 | XXXXh    | F    | Serial number (20 ASCII characters)                                     |

| 20-21 | XXXXh    | Х    | Retired                                                                 |

| 22    | 003Fh    | Х    | Obsolete                                                                |

| 23-26 | XXXXh    | F    | Firmware revision (8 ASCII characters)                                  |

| 27-46 | XXXXh    | F    | Model number (40 ASCII, characters)                                     |

|       |          | F    | 1\$-8 80h                                                               |

| 47    | 8000h    | F    | 7-0 00h = Reserved                                                      |

|       |          | F    | 01h = Maximum number of 1 sectors on READ/WRITE MULTIPLE commands       |