## **TOSHIBA**

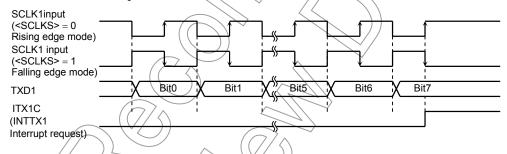

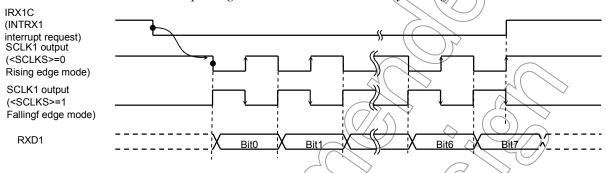

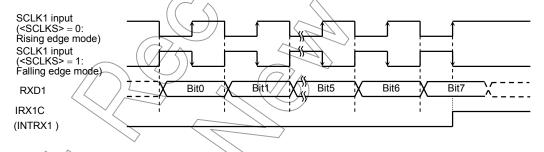

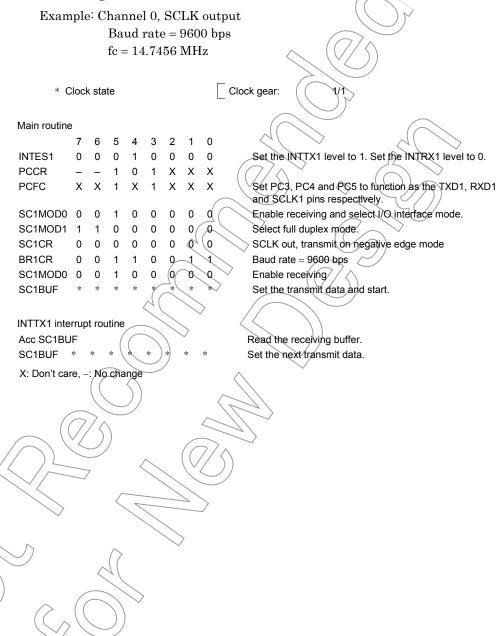

TOSHIBA Original CMOS 16-Bit Microcontroller

TLCS-900/L1 Series

TMP91C016FG JTMP91C016S

TOSHIBA CORPORATION

Semiconductor Company

### **Preface**

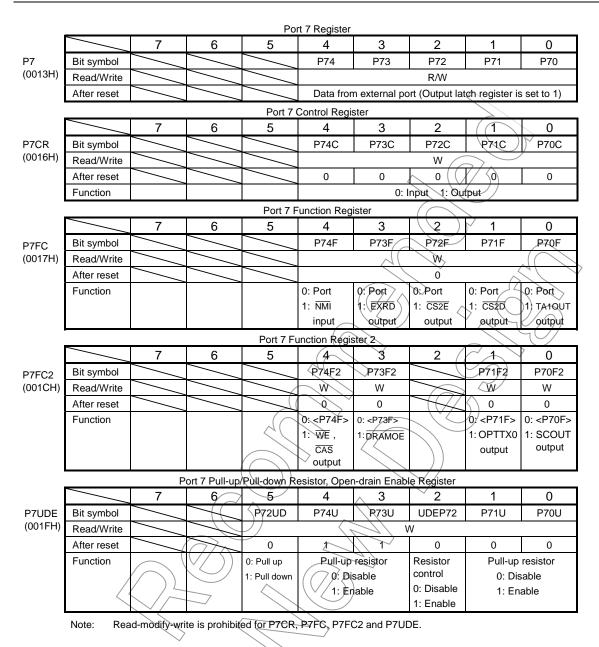

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

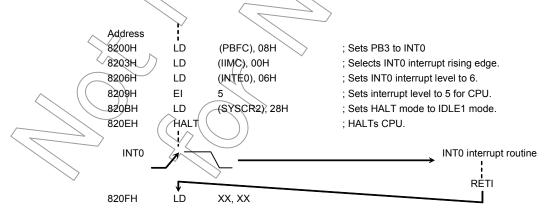

## \*\*CAUTION\*\* How to release the HALT mode

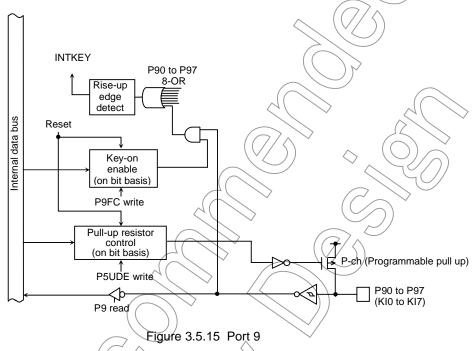

Usually, interrupts can release all halts status. However, the interrupts = (NMI, INTO to INT3, INTRTC, INTALM0 to INTALM4, INTKEY, INTVLD0 to INTVLD2), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 5 clocks of  $f_{FPH}$ ) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# CMOS 16-Bit Microcontrollers TMP91C016FG/JTMP91C016S

#### Outline and Features

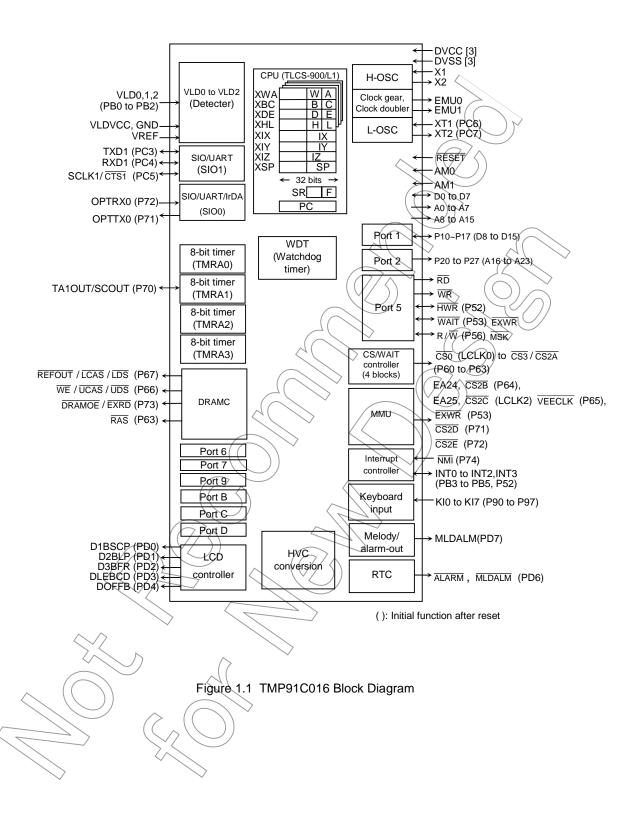

TMP91C016 is a high-speed 16-bit microcontroller designed for the control of various mid- to large-scale equipment.

TMP91C016FG comes in a 100-pin flat package. JTMP91C016S is a 100-pad-chip product. Listed below are the features.

- (1) High-speed 16-bit CPU (900/L1 CPU)

- Instruction mnemonics are upward compatible with TLCS-90/900

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

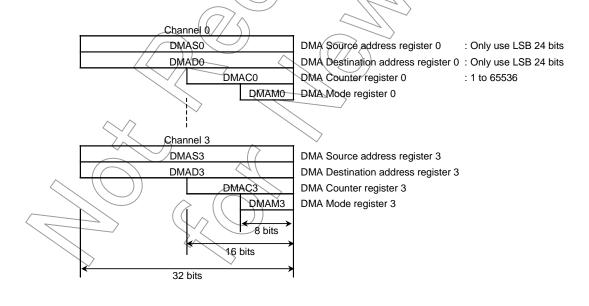

- Micro DMA: 4 channels (592ns/ 2bytes at 27MHz)

- (2) Minimum instruction execution time: 148 ns (at 27 MHz)

#### RESTRICTIONS ON PRODUCT USE

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations

that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses

occurring as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

91C016-1 2008-02-20

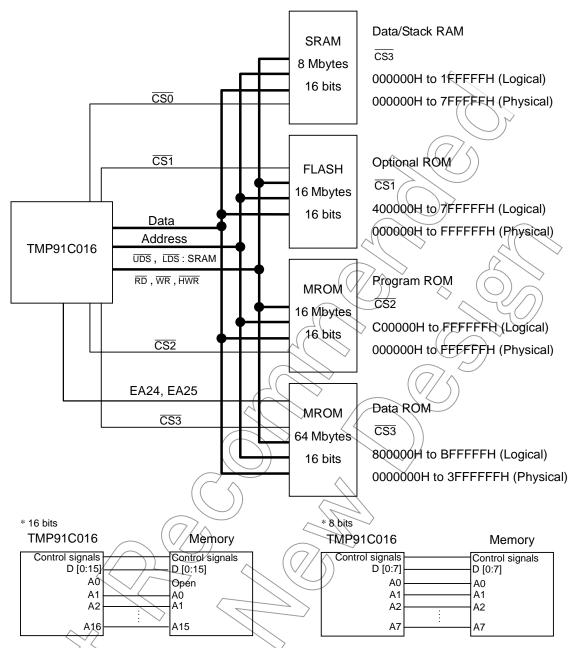

- (3) Built-in RAM: None Built-in ROM: None

- (4) External memory expansion

- Expandable up to 105 Mbytes (Shared program/data area)

- Can simultaneously support 8-/16-bit width external data bus: Dynamic data bus sizing

- Separate bus system

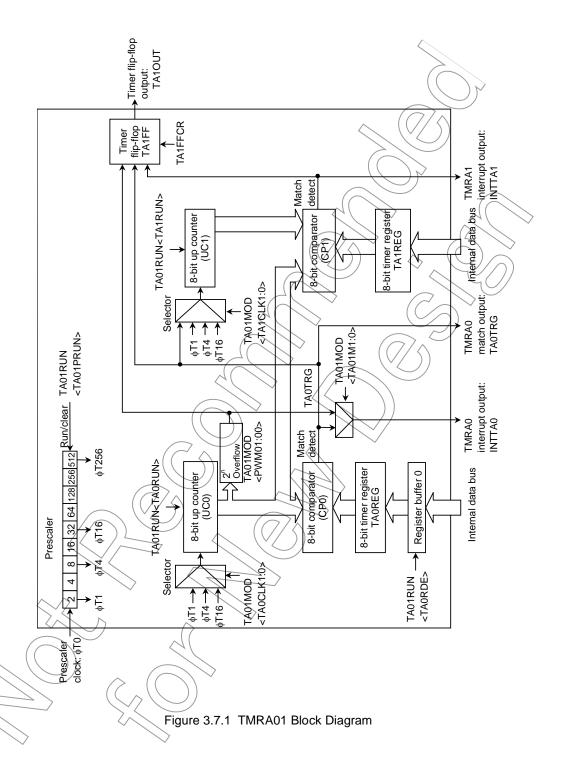

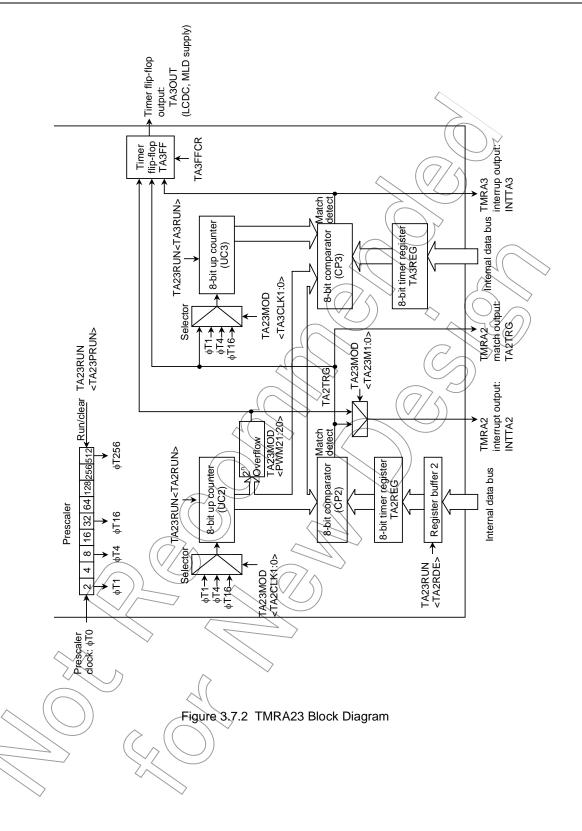

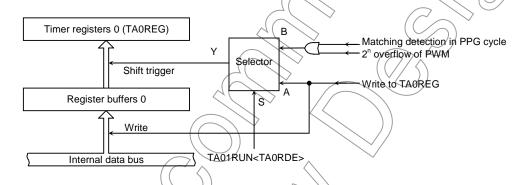

- (5) 8-bit timers: 4 channels

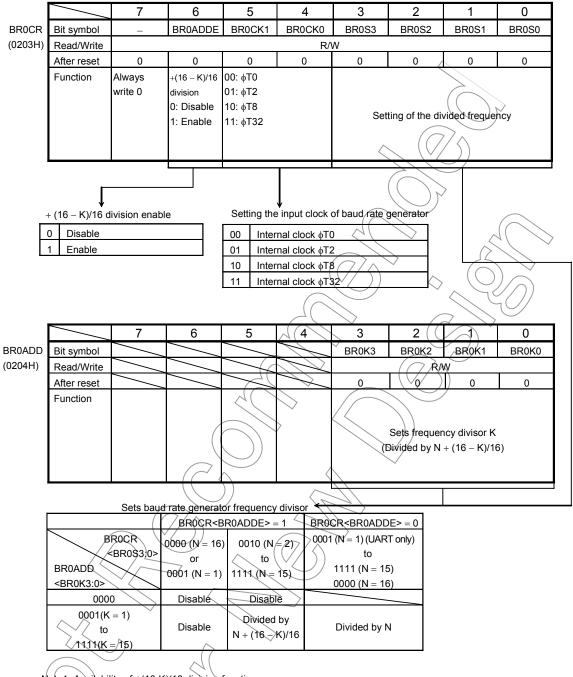

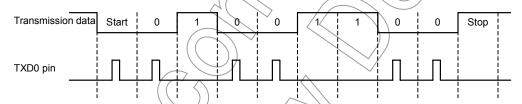

- (6) General-purpose serial interface: 2 channels

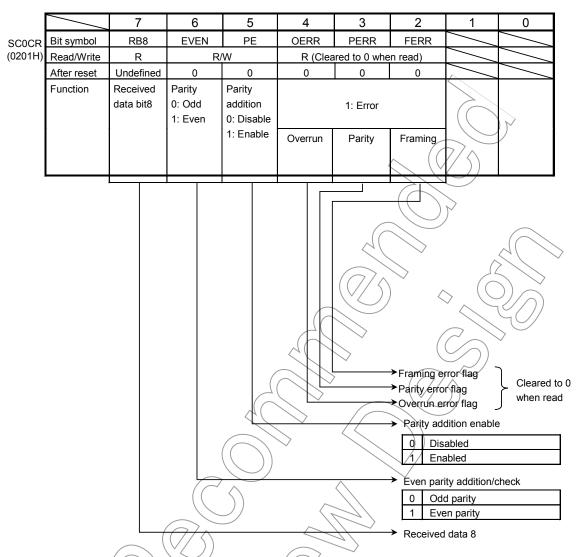

#### Channel 0

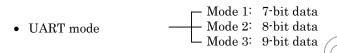

- UART mode

- IrDA Ver. 1.0 (115.2 kbps) mode selectable

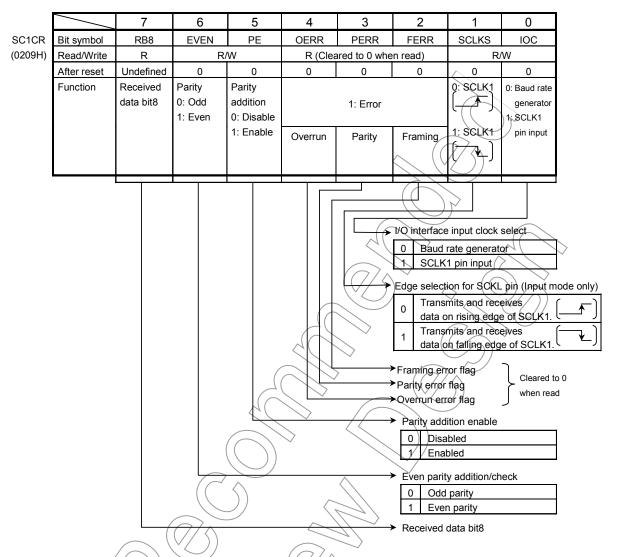

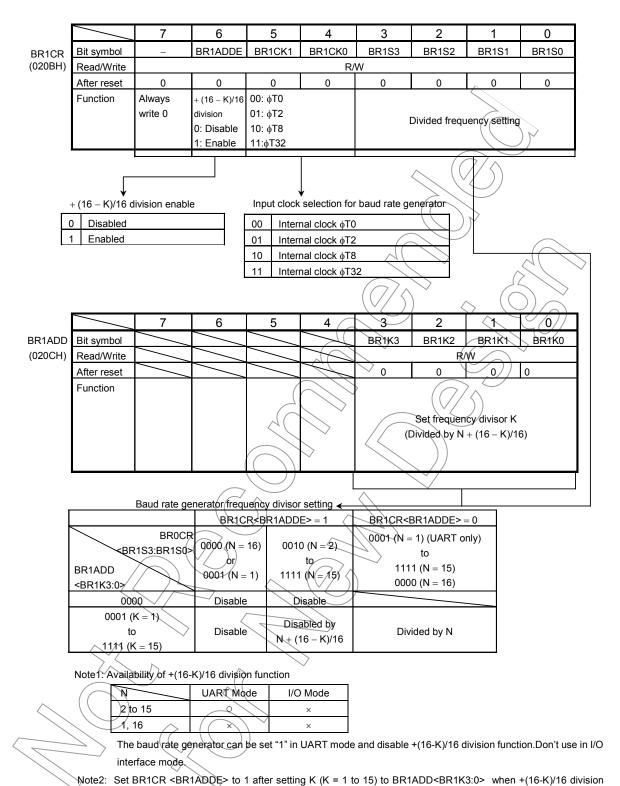

#### Channel 1

- UART mode

- Synchronous mode selectable

- (7) LCD controller

- Adapt to both Shift register type and Built-in RAM type LCD driver

- (8) Timer for real time clock (RTC)

- Based on TC8521A

- (9) Key-on wakeup (Interrupt key input)

- (10) Watchdog timer

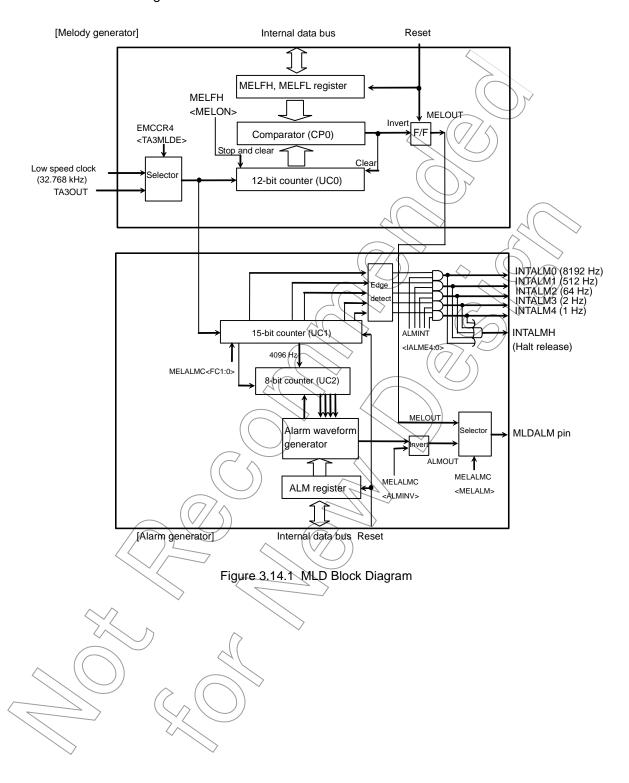

- (11) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

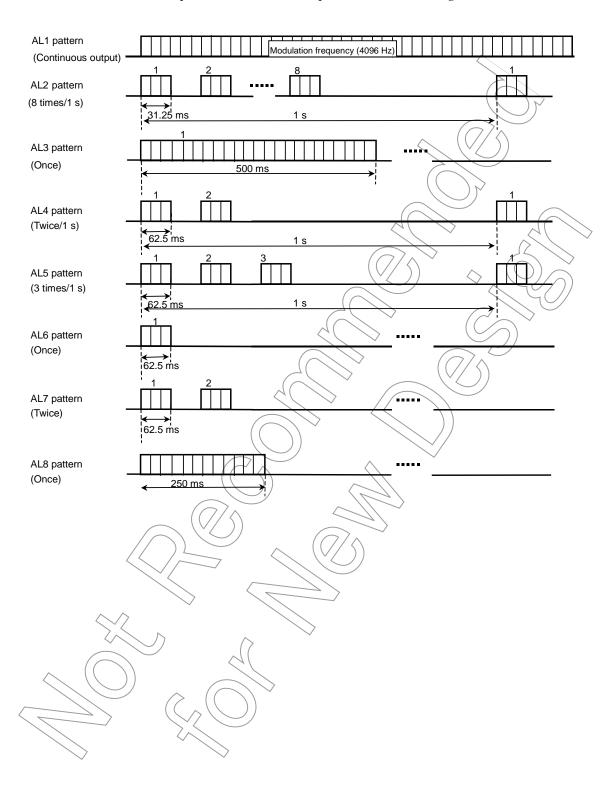

- Alarm: Output of the 8 kinds of alarm pattern

- Output of the 5 kinds of interval interrupt

- (12) Chip select/wait controller 4 channels

- (13) MMU

- Expandable up to 105 Mbytes (4 local area/8 bank method)

- (14) Display data reciprocal conversion function between the vertical and horizontal (8 × 8)

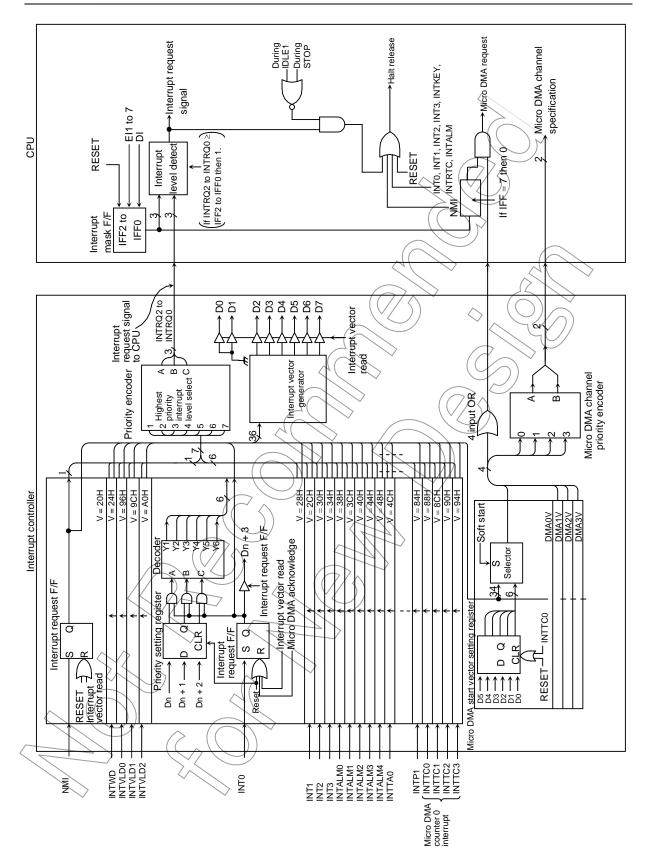

- (15) Interrupts: 40 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 25 internal interrupts 7 priority levels are selectable

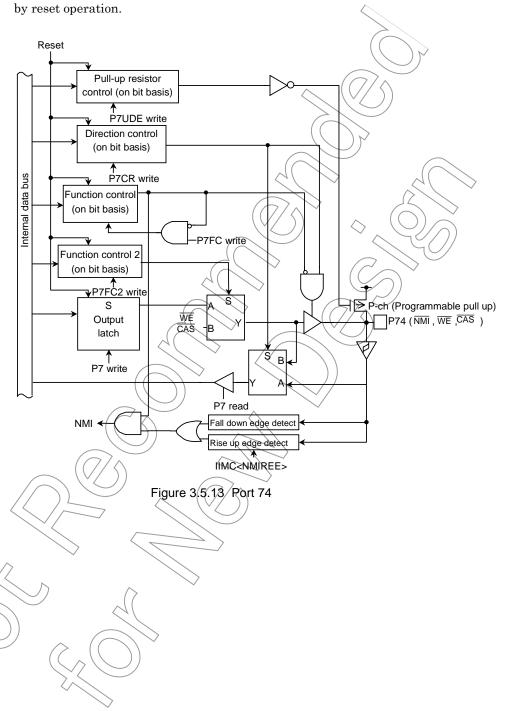

- 9 external interrupts: 7 priority levels are selectable

(among 4 interrupts are selectable edge mode)

- (16) Input/output ports: 31 pins (at External 16-bit data bus memory)

- (17) Standby function

Three HALT modes: IDLE2 (Programmable), IDLE1 and STOP

- (18) DRAM controller

- \overline{2CAS} mode

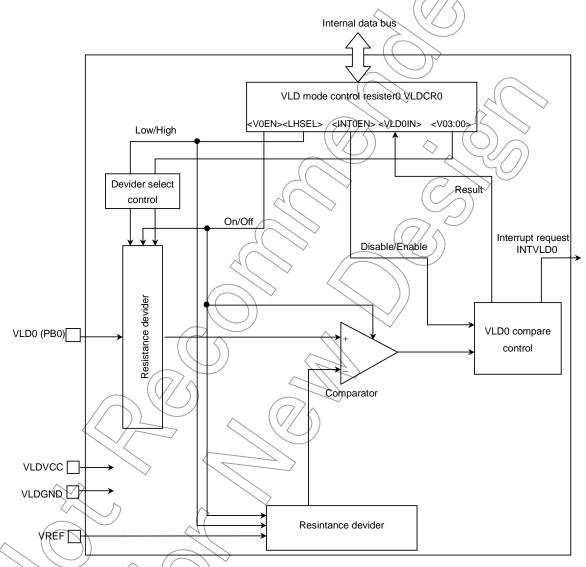

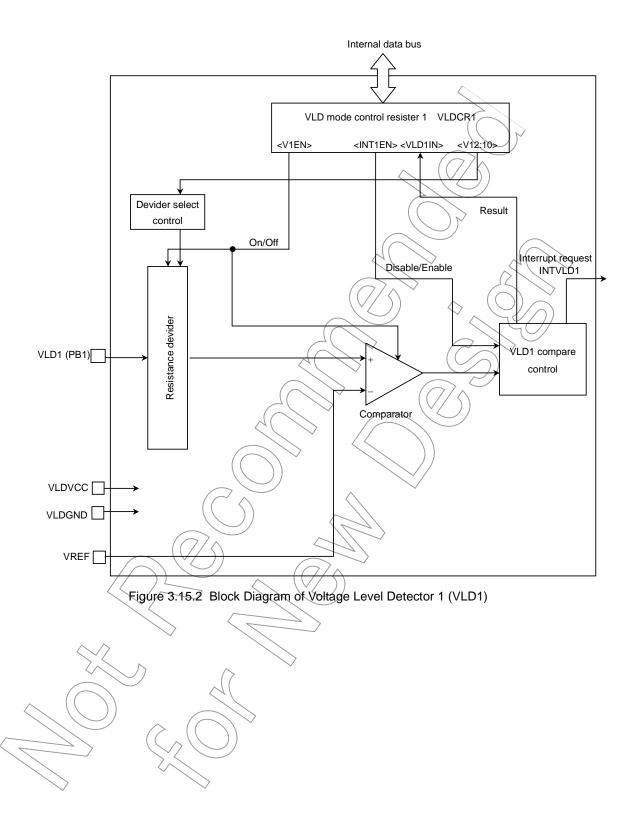

- (19) Voltage compare circuit: 3 channels

91C016-2 2008-02-20

#### (20) Triple-clock controller

- Clock doubler (DFM) circuit is inside

- Clock gear function: Select a high-frequency clock fc/1 to fc/16

- Slow mode (fs = 32.768 kHz)

#### (21) Operating voltage

- VCC = 2.7 V to 3.6 V (fc max = 27 MHz)

- VCC = 1.8 V to 3.6 V (fc max = 10 MHz)

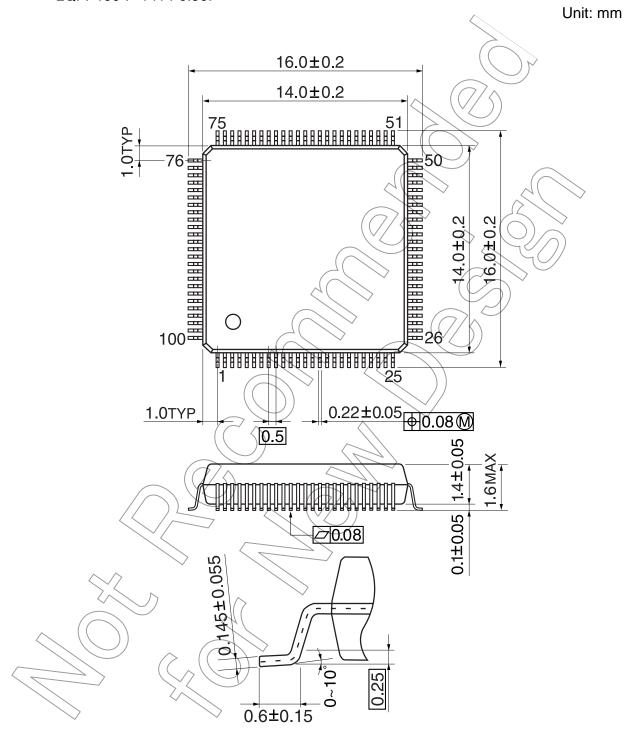

## (22) Package

• 100-pin QFP: LQFP100-P-1414-0.50F

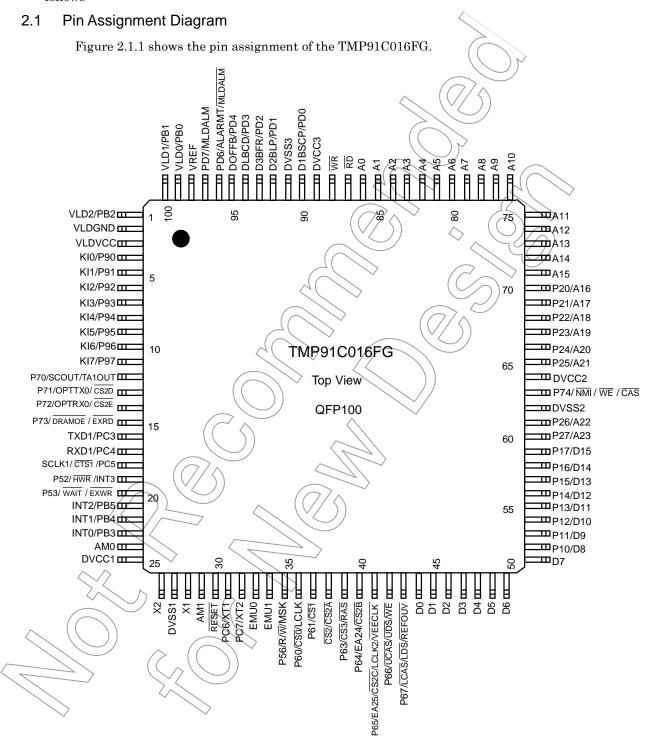

## 2. Pin Assignment and Pin Functions

The assignment of input/output pins for the TMP91C016, their names and functions are as follows:

Figure 2.1.1 Pin Assignment Diagram (100-pin QFP)

## 2.1.1 Pad Layout

Table 2.1.1 PAD Layout

(Chip size 4.38 mm  $\times$  4.43 mm)

Unit: µm

| (Criip si | Ze 4.36 IIIII × 4 | +.43 111111)   |         |             |          |         |                  |                 |          |         | Onit. µm |

|-----------|-------------------|----------------|---------|-------------|----------|---------|------------------|-----------------|----------|---------|----------|

| Pin<br>No | Name              | X Point        | Y Point | Pin<br>No   | Name     | X Point | Y Point          | Pin<br>No       | Name     | X Point | Y Point  |

| 1         | PB2               | -2057          | 1531    | 35          | P56      | -239    | -2082            | 69              | P21      | 2053    | 850      |

| 2         | VLDGND            | -2057          | 1417    | 36          | P60      | -125    | -2082            | 70              | P20      | 2053    | 964      |

| 3         | VLDVCC            | -2057          | 1303    | 37          | P61      | -11     | -2082            | 71 (            | (/A15    | 2053    | 1078     |

| 4         | P90               | -2057          | 990     | 38          | P62      | 103     | -2082            | 72              | A14      | 2053    | 1192     |

| 5         | P91               | -2057          | 876     | 39          | P63      | 217     | -2082            | 73              | A13      | 2053    | 1306     |

| 6         | P92               | -2057          | 762     | 40          | P64      | 331     | -2082            | 74_             | ) X A12  | 2053    | 1420     |

| 7         | P93               | -2057          | 648     | 41          | P65      | 479     | -2082            | 75              | A11      | 2053    | 1534     |

| 8         | P94               | -2057          | 534     | 42          | P66      | 593     | -2082            | 76>             | A10      | 1503    | 2082     |

| 9         | P95               | -2057          | 420     | 43          | P67      | 707     | -2082            | <del>\</del> 77 | A9       | 1389    | 2082     |

| 10        | P96               | -2057          | 306     | 44          | D0       | 821 (   | -2082            | 78              | _ A8 ( ( | 1275    | 2082     |

| 11        | P97               | -2057          | 192     | 45          | D1       | 935     | -2082            | 79              | ĄZ       | (1160)  | 2082     |

| 12        | P70               | -2057          | 55      | 46          | D2       | 1049    | -2082            | 80              | A6       | 1046    | 2082     |

| 13        | P71               | -2057          | -59     | 47          | D3       | 1163    | -2082            | 81              | A5       | 932     | 2082     |

| 14        | P72               | -2057          | -174    | 48          | D4       | 1277    | -2082            | 82              | (A4)     | 818     | 2082     |

| 15        | P73               | -2057          | -290    | 49          | D5       | 1391    | -2082            | 83              | A3       | 704     | 2082     |

| 16        | PC3               | -2057          | -404    | 50          | D6       | 1505    | -2082            | 84/             | A2       | 590     | 2082     |

| 17        | PC4               | -2057          | -521    | 51          | (D7      | 2053    | <del>-1534</del> | 85              | A1       | 476     | 2082     |

| 18        | PC5               | -2057          | -638    | 52          | P10      | 2053 <  | _1420            | 86              | A0       | 362     | 2082     |

| 19        | P52               | -2057          | -755    | 53          | P11      | 2053    | -1306            | 87              | RD       | 248     | 2082     |

| 20        | P53               | -2057          | -870    | 54          | P12      | 2053    | -1192            | 88              | WR       | 134     | 2082     |

| 21        | PB5               | -2057          | -991 /  | 55 <        | )<br>P13 | 2053    | -1078            | 89              | DVCC3    | 20      | 2082     |

| 22        | PB4               | -2057          | -1105   | <b>56</b> ) | ) P14    | 2053    | <del>-</del> 964 | 90              | PD0      | -180    | 2082     |

| 23        | PB3               | -2057          | -1219   | 57          | P15      | 2053    | <b>-8</b> 50     | 91              | DVSS3    | -294    | 2082     |

| 24        | AM0               | -2057          | -1333   | 58          | P16      | 2053    | <del>-736</del>  | 92              | PD1      | -408    | 2082     |

| 25        | DVCC1             | /-2057         | -1447   | <b>/</b> 59 | P17 (    | 2053    | -606             | 93              | PD2      | -522    | 2082     |

| 26        | X2 <              | <u>_1507</u> / | -2082   | 60          | R27 \    | 2053    | -450             | 94              | PD3      | -638    | 2082     |

| 27        | DVSS1             | -1342          | -2082   | 61_         | P26      | 2053    | -295             | 95              | PD4      | -752    | 2082     |

| 28        | X1                | -1176          | 2082    | 62          | DVSS2    | 2053    | -140             | 96              | PD6      | -866    | 2082     |

| 29        | AM1               | -1060          | -2082   | 63          | P74      | 2053    | 17               | 97              | PD7      | -980    | 2082     |

| 30        | RESET             | -946           | -2082   | 64          | DVCC2    | 2053    | 171              | 98              | VREF     | -1274   | 2082     |

| 31        | PC6               | -831           | -2082   | 65          | P25      | 2053    | 326              | 99              | PB0      | -1388   | 2082     |

| 32        | PC7               | -583           | -2082   | 66          | P24      | 2053    | 482              | 100             | PB1      | -1506   | 2082     |

| 33        | EMUO              | -467<br>^      | -2082   | 67          | > P23    | 2053    | 622              |                 |          |         |          |

| 34        | EMU1              | -353           | -2082   | 68          | P22      | 2053    | 736              |                 |          |         |          |

|           |                   |                |         |             |          |         |                  |                 |          |         |          |

## 2.2 Pin Names and Functions

The names of the input/output pins and their functions are described below.

| Pin Name         | Number of Pins | I/O       | Functions                                                                                                |

|------------------|----------------|-----------|----------------------------------------------------------------------------------------------------------|

| D0 to D7         | 8              | I/O       | Data (Lower): Bits 0 to 7 of data bus                                                                    |

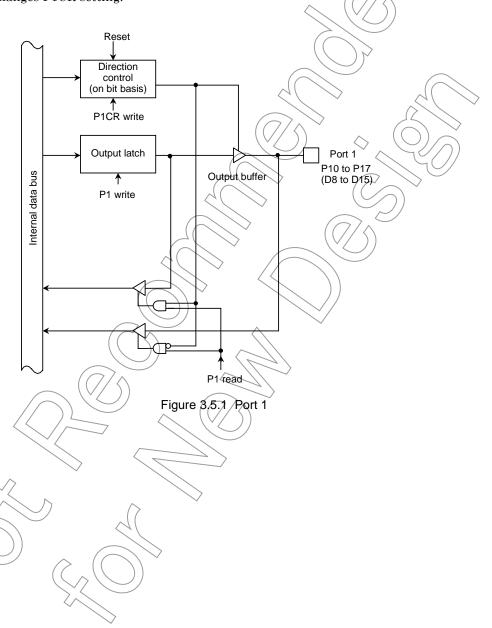

| P10 to P17       | 8              | I/O       | Port 1: I/O port that allows I/O to be selected at the bit-level (When used to the external 8-bit bus)   |

| D8 to D15        |                | I/O       | Data (Upper): Bits 8 to15 of data/bus                                                                    |

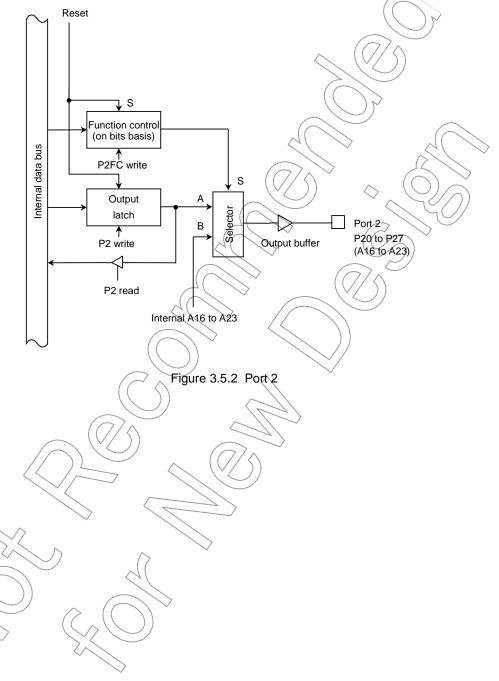

| P20 to P27       | 8              | Output    | Port 2: Output port                                                                                      |

| A16 to A23       |                | Output    | Address: Bits 16 to 23 of address bus                                                                    |

| A8 to A15        | 8              | Output    | Address: Bits 8 to 15 of address bus                                                                     |

| A0 to A7         | 8              | Output    | Address: Bits 0 to 7 of address bus                                                                      |

| RD               | 1              | Output    | Read: Strobe signal for reading external memory. P5 <rde>=0, output RD when reading internal area.</rde> |

| WR               | 1              | Output    | Write: Strobe signal for writing data to pins D0 to D7                                                   |

| P52              | 1              | I/O       | Port 52: I/O port (with pull-up resistor)                                                                |

| HWR              |                | Output    | High Write: Strobe signal for writing data to pins D8 to D15                                             |

| ĪNT3             |                | Input     | Interrupt request pin 3. Interrupt request pin with programmable rising/falling edge                     |

| P53              | 1              | I/O       | Port 53: I/Q port (with pull-up resistor)                                                                |

| WAIT             |                | Input     | Wait: Pin used to request CPU bus wait ((1 + N) WAIT mode)                                               |

| EXWR             |                | Output    | Ex write: Strobe signal for writing data for RAM                                                         |

| P56              | 1              | I/O       | Port-56; I/O port (with pull-up resistor)                                                                |

| $R/\overline{W}$ |                | Output    | Read/write: 1 represents read or dummy cycle; 0 represents write cycle.                                  |

| MSK              |                | Input     | Request VEECLK clock for external LCD-driver.                                                            |

| P60              | 1              | 1/0       | Port 69; 1/O port (with pull-up resistor)                                                                |

| CS0              |                | Output (  | Chip select 0: Outputs 0 when address is within specified address area.                                  |

| LCLK0            |                | Output    | Lcd CLK: Command controll C/S for S/R type lcdd.                                                         |

| P61              | 1              | I/Ø       | Port 61: I/O port (with pull-up resistor)                                                                |

| CS1              |                | Output    | Chip select 1: Outputs 0 when address is within specified address area                                   |

| CS2              | 1              | Output    | Chip select 2: Outputs 0 when address is within specified address area                                   |

| CS2A             |                | Output    | Expand chip select: 2A: Outputs 0 when address is within specified address area                          |

| P63              | /1             | 1/0       | Port 63: I/O port (with pull-up resistor)                                                                |

| CS3              |                | Output    | Chip select 3: Outputs 0 when address is within specified address area                                   |

| RAS              |                | Output    | Row address strobe: RAS strobe row address area for DRAM                                                 |

| P64              | 1              | 1/0       | Port 64 VO port (with pull-up resistor)                                                                  |

| EA24             |                | Output    | Chip select 24: Outputs 0 when address is within specified address area                                  |

| <u>CS2B</u>      |                | Output    | Expand chip select 2B: Outputs 0 when address is within specified address area                           |

| P65              | (1)            | 1/0       | Port 65: I/O port (with pull-up resistor)                                                                |

| EA25             |                | Outpût\   | Chip select 25: Outputs 0 when address is within specified address area                                  |

| CS2C (           |                | Output    | Expand chip select 2C: Outputs 0 when address is within specified address                                |

|                  |                |           | area                                                                                                     |

| LCLK2            |                | Output )  | Lcd CLK: Command controll C/S for S/R type lcdd.                                                         |

| VEECLK           |                | // Output | Pomp-up CLK for external LCD driver                                                                      |

| P66              | 1 4            | 1/0       | Port 66: I/O port (with pull-up resistor)                                                                |

| UCAS             |                | Output    | Upper column address strobe: Upper CAS strobe for 2CAS type DRAM.                                        |

| UDS              |                | Output    | Upper data enable strobe                                                                                 |

| WE               |                | Output    | Write strobe for DRAM (only 8-bit access)                                                                |

| P67              | 1              | I/O       | Port 67: I/O port (with pull-up resistor)                                                                |

| <b>LCAS</b>      |                | Output    | Lower column address strobe: Upper CAS strobe for 2CAS type DRAM.                                        |

| LDS              |                | Output    | Lower data enable strobe                                                                                 |

| REFOUT           |                | Output    | Refresh cycle state singanl for DRAM (only 8-bit access)                                                 |

| Pin Name     | Number of Pins | I/O        | Functions                                                                                                       |

|--------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------|

| P70          | 1              | I/O        | Port 70: I/O port (with pull-up resistor)                                                                       |

| SCOUT        |                | Output     | System clock output: Selectable fFPH or fs                                                                      |

| TA1OUT       |                | Output     | 8-bit timer output: Timer 0 or timer 1 out                                                                      |

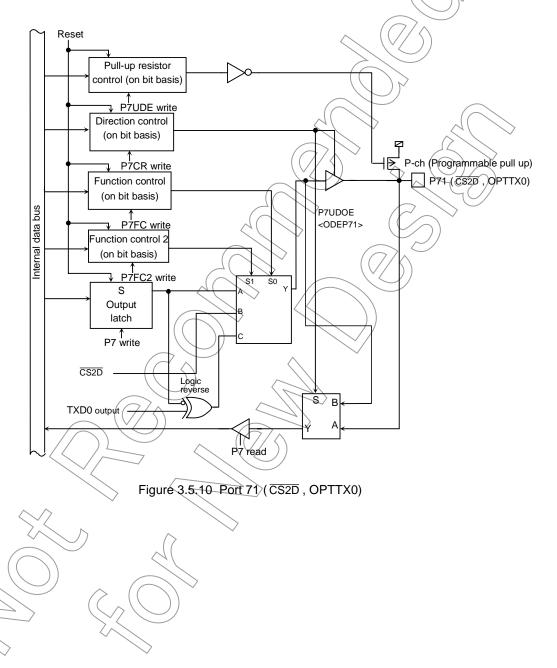

| P71          | 1              | I/O        | Port 71: I/O port (with pull-up resistor)                                                                       |

| OPTTX0       |                | Output     | SIO0 trance port                                                                                                |

| CS2D         |                | Output     | Expond chip select 2D: Outputs 0 when address is within specified address area                                  |

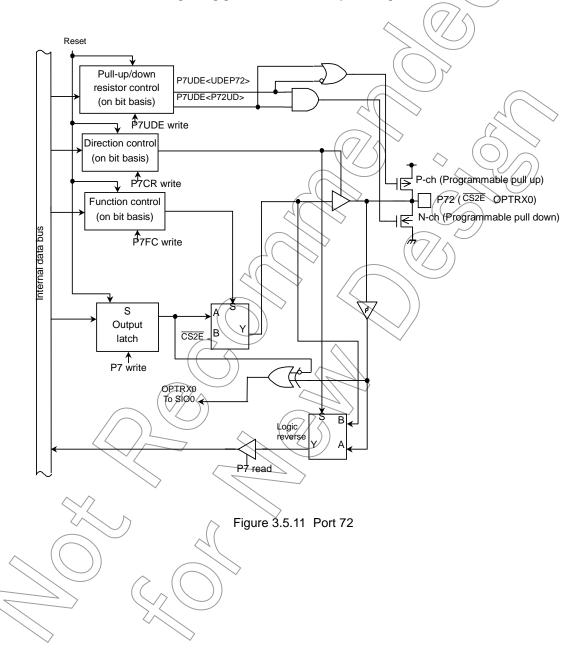

| P72          | 1              | I/O        | Port 72: I/O port (Shummit input, with pull-up/pull-down resistor)                                              |

| OPTRX0       |                | Input      | SIO0 receive port                                                                                               |

| CS2E         |                | Output     | Expond chip select 2E: Outputs 0 when address is within specified address area                                  |

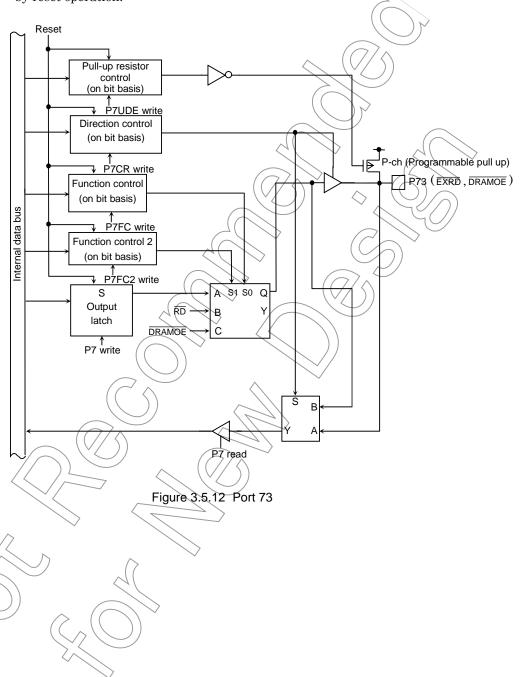

| P73          | 1              | I/O        | Port 73: I/O port (with pull-up resistor)                                                                       |

| DRAMOE       |                | Output     | DRAMOE: Strobe signal for reading external DRAM                                                                 |

| EXRD         |                | Output     | External read: Strobe signal for reading external memory                                                        |

| P74          | 1              | I/O        | Port 74: I/O port (with pull-up resistor)                                                                       |

| NMI          |                | Input      | Non-maskable interrupt request pin:                                                                             |

|              |                |            | Interrupt request pin with programmable falling edge level or with both edge levels programmable                |

| WE           |                | Output     | Strobe signal for writing data for DRAM (only 26AS)                                                             |

| CAS          |                | Output     | Coulmn address strobe: Outputs 0 when address is within specified DRAM column address area (only 8 bits access) |

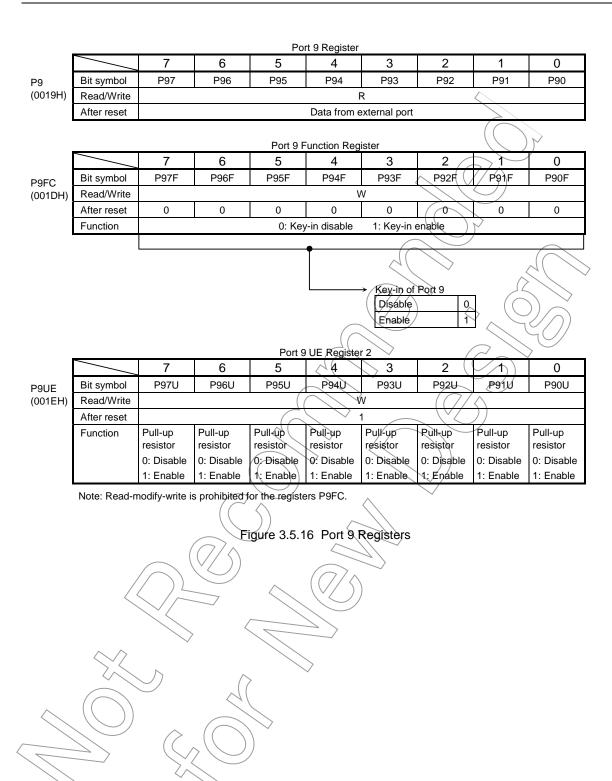

| P90 to P97   | 8              | Input      | Port: 90 to 97 port; Pin used to input ports                                                                    |

| KI0 to KI7   |                | Input      | Key input 0 to 7: Pin used of key on wake-up 0 to 7                                                             |

|              |                |            | (Schmitt input, with pull-up resistor)                                                                          |

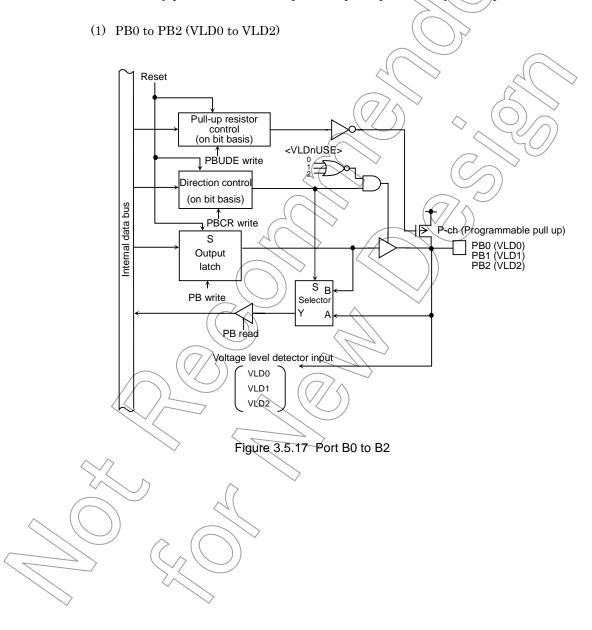

| PB0          | 1              | I/O        | Port B0: I/O port (with pull-up resistor)                                                                       |

| VLD0         |                | Input      | Voltage level detector 0: For main battery, Interrupt request with edge, too                                    |

| PB1          | 1              | 1/0 ((     | Port B1: I/O port (with pull-up resistor)                                                                       |

| VLD1         |                | Input      | Voltage level detector 1: For back up battery, Interrupt request with edge, too                                 |

| PB2          | 1              | 1/0/       | Port B2: I/O port (with pull-up resistor)                                                                       |

| VLD2         |                | Input      | Voltage level detector 2: For micon battery, Interrupt request with edge, too                                   |

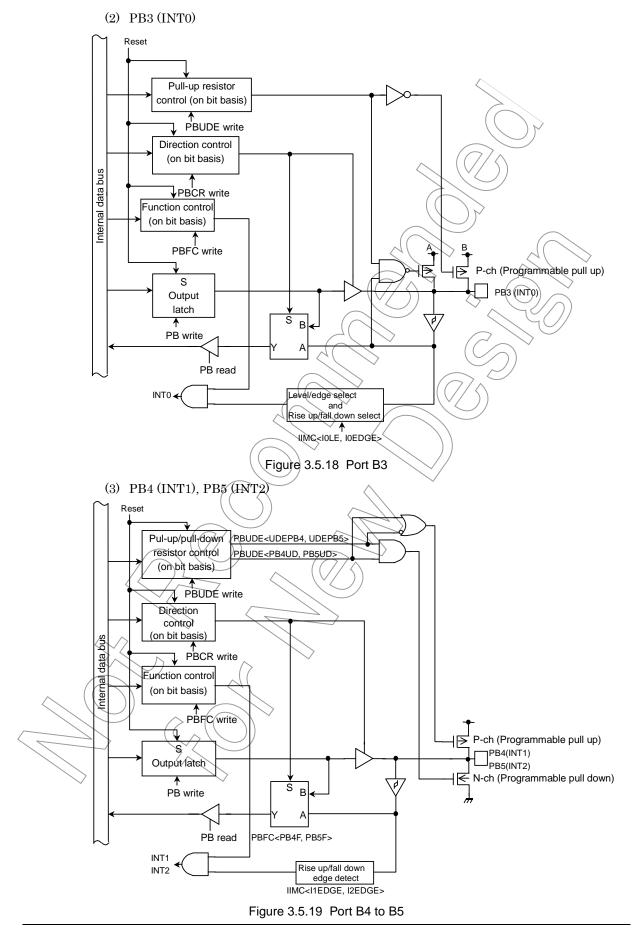

| PB3          | 1              | 1/0        | Port B3: I/O port (Schmitt input, with pull-up resistor)                                                        |

| INT0         |                | Input      | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge                      |

| PB4 to PB5   | //2            | 1/0        | Port B4 to B5: //O port (Schmitt input, with pull-down resistor)                                                |

| INT1 to INT2 |                | Input      | Interrupt request pin 1 to 2: Interrupt request pin with programmable rising/falling edge                       |

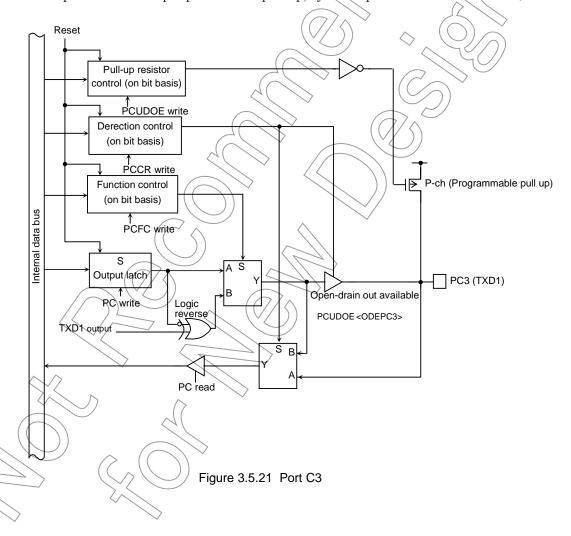

| PC3          | 1              | / 1/0 /    | Port C3: I/O port (with pull-up resistor)                                                                       |

| TXD1         |                | Output     | Serial 1 send data: Open-drain output pin by programmable                                                       |

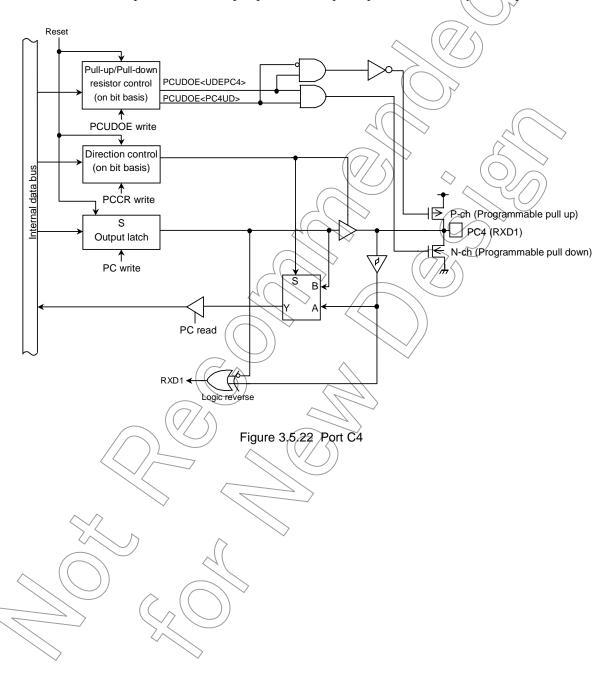

| PC4          | 1              | I/O        | Port C4: I/O port (Schmitt input, with pull-up/pull-down resistor)                                              |

| RXD1         |                | Input      | Serial 1 recive data                                                                                            |

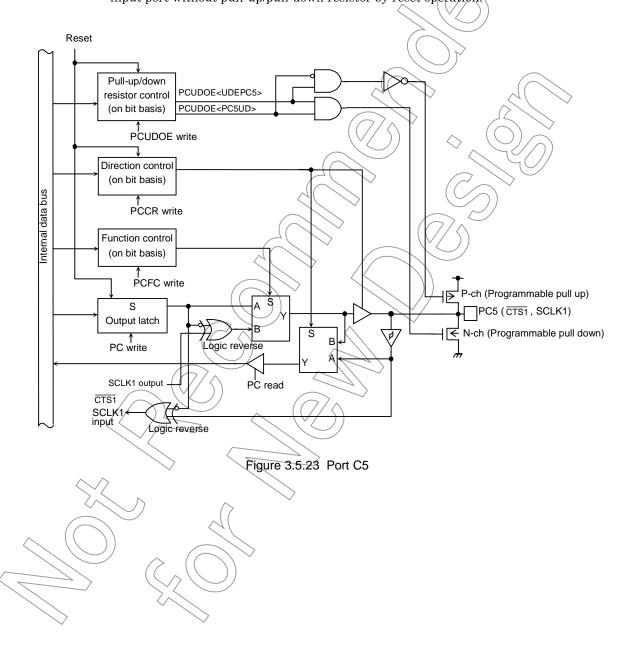

| PC5          | (1)            | 1/0        | Port C5: I/O port (Schmitt input, with pull-up/pull-down resistor)                                              |

| SCLK1        |                | 1/0        | Serial clock I/O 1                                                                                              |

| ह्यंडम \     | //             | Input      | Clear to send                                                                                                   |

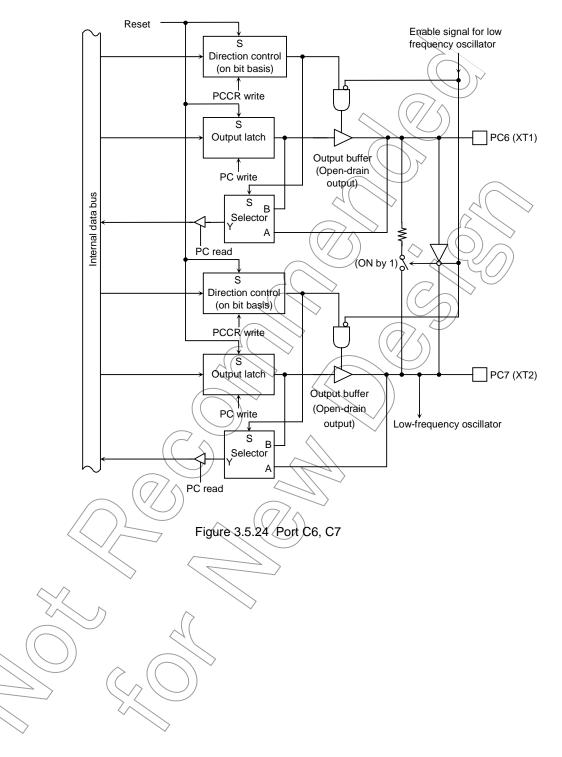

| PC6          | 1 /            | > ((I/O // | Port C6: I/O port (Open-drain output)                                                                           |

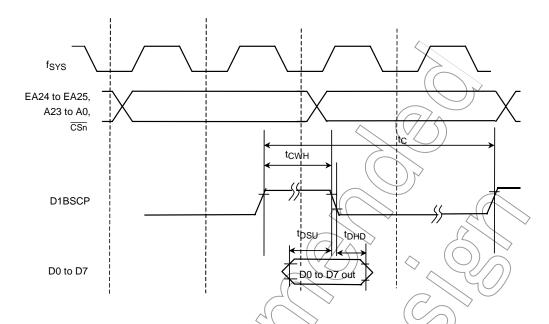

| XT1          |                | /> \Input  | Low-frequency oscillator connection pins                                                                        |

| PCZ          | 1 }            | 1/0        | Port C7: I/O port (Open-drain output)                                                                           |

| XT2          |                | Qutput     | Low-frequency oscillator connection pins                                                                        |

| Pin Name   | Number of Pins | I/O    | Functions                                                                  |

|------------|----------------|--------|----------------------------------------------------------------------------|

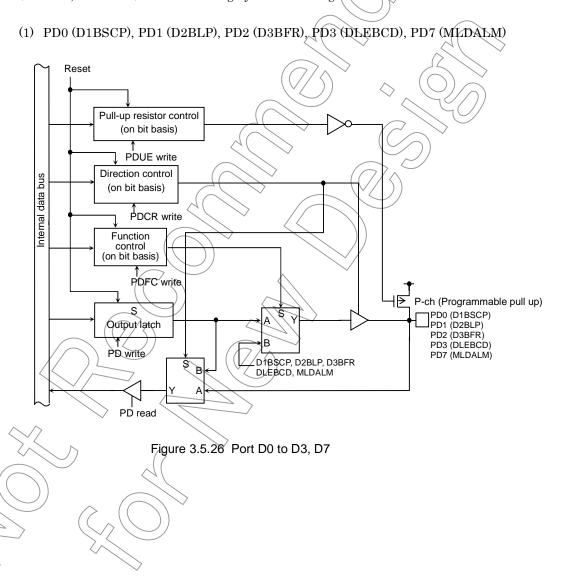

| PD0        | 1              | I/O    | Port D0: I/O port (with pull-up resistor)                                  |

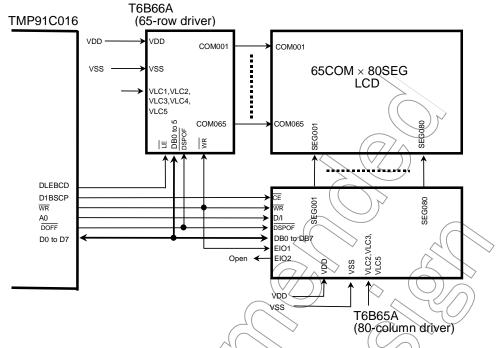

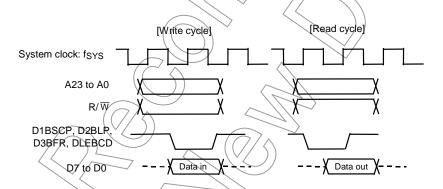

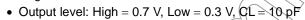

| D1BSCP     |                | Output | LCD driver output pin                                                      |

| PD1        | 1              | I/O    | Port D1: I/O port (with pull-up resistor)                                  |

| D2BLP      |                | Output | LCD driver output pin                                                      |

| PD2        | 1              | I/O    | Port D2: I/O port (with pull-up resistor)                                  |

| D3BFR      |                | Output | LCD driver output pin                                                      |

| PD3        | 1              | I/O    | Port D3: I/O port (with pull-up resistor)                                  |

| DLEBCD     |                | Output | LCD driver output pin                                                      |

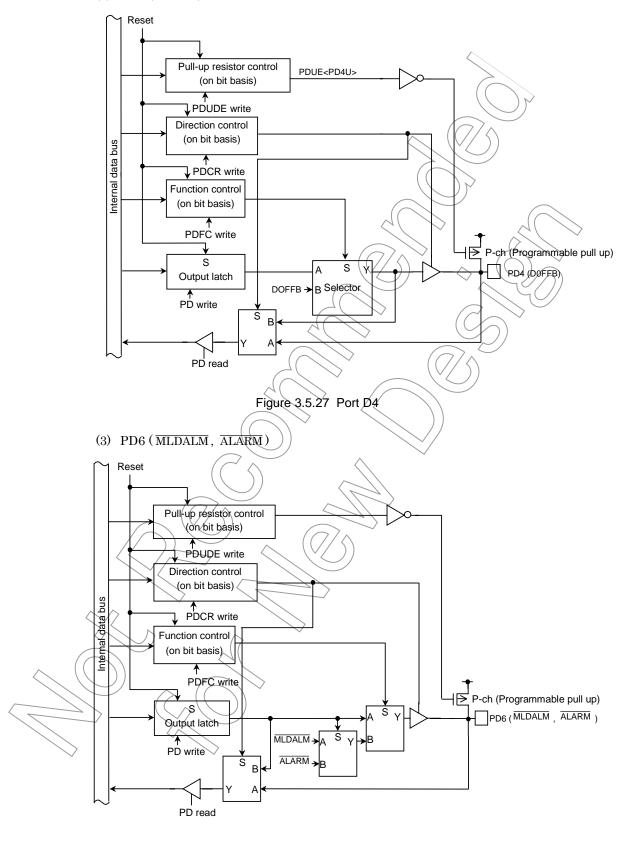

| PD4        | 1              | I/O    | Port D4: I/Ot port (with pull-up resistor)                                 |

| DOFFB      |                | Output | LCD driver output pin                                                      |

| PD6        | 1              | I/O    | Port D6: I/O port (with pull-up resistor)                                  |

| ALARM      |                | Output | RTC alarm output pin                                                       |

| MLDALM     |                | Output | Logical invert for Melody/alarm output pin                                 |

| PD7        | 1              | I/O    | Port D7: I/O port (with pull-up resistor)                                  |

| MLDALM     |                | Output | Melody/alarm output pin / /                                                |

| AM0 to AM1 | 2              | Input  | Operate mode:                                                              |

|            |                |        | Fixed to AM1 = 0, AM0 = 1-16-bit external bus or 8-/16-bit dynamic sizing. |

|            |                |        | Fixed to AM1=0, AM0=0,8-bit external bus fixed.                            |

| EMU0       | 1              | Output | Open pin                                                                   |

| EMU1       | 1              | Output | Open pin                                                                   |

| RESET      | 1              | Input  | Reset: Initializes TMP91C016. (with pull-up resistor)                      |

| VREF       | 1              | Input  | Power supply pin for Low-frequency oscillator, RTC and VLD.                |

| VLDVCC     | 1              |        | For VLD power supply pin                                                   |

| VLDVSS     | 1              |        | For VLD: GND pins (0,V) (All pins should be connected with GND (0 V).)     |

| X1/X2      | 2              |        | High-frequency oscillator connection pins                                  |

| DVCC       | 3              | ( (    | Power supply pins (All Vcc pins should be connected with the power         |

|            |                |        | Supply pin).                                                               |

| DVSS       | 3              |        | GND pins (0 V) (All pins should be connected with GND (0V).)               |

## 3. Operation

This following describes block by block the functions and operation of the TMP91C016.

Notes and restrictions for eatch book are outlined in 6. "Points of Note and Restrictions" at the end of this manual.

#### 3.1 CPU

The TMP91C016 incorporates a high-performance 16-bit CPU (The 900/L1) CPU). For CPU operation, see the TLCS-900/L1 CPU.

The following describe the unique function of the CPU used in the TMP91C016; these functions are not covered in the TLCS-900/L1 CPU section.

#### 3.1.1 Reset

When resetting the TMP91C016 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then set the RESET input to low level at least for 10 system clocks (12 µs at 27 MHz).

Thus when turn on the switch, be set to the power supply voltage is within the operating voltage range, and that the internal high frequency oscillator has stabilized. Then hold the RESET input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock mode fsys is set to fc/32 (=  $fc/16 \times 1/2$ ).

When the reset is accept, the CPU:

Sets as follows the program counter (PC) in accordance with the reset vector stored at address FFFF00H to FFFF02H:

PC<0:7>

Value at FFFF00H address

PC<15:8>

Value at FFFF01H address

PC<23:16>

Value at FFFF02H address

- Sets the stack pointer (XSP) to 100H.

- Sets bits <1FF2:0> of the status register (SR) to 111 (Sets the interrupt level mask register to level 7).

- Sets the <MAX> bit of the status register (SR) to 1 (Max mode).

(Note: As this product does not support Min mode, do not write a 0 to the <MAX>)

• Clears bits <RFP2:0> of the status register (SR) to 000 (Sets the register bank to

When reset is released, the CPU starts executing instructions in accordance with the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports, and other pins as follows.

- Initializes the internal I/O registers.

- Sets the port pins, including the pins that also act as internal I/O, to general purpose input or output port mode.

Note: The CPU internal register (except to PC, SR, XSP) and internal RAM data do not change by resetting.

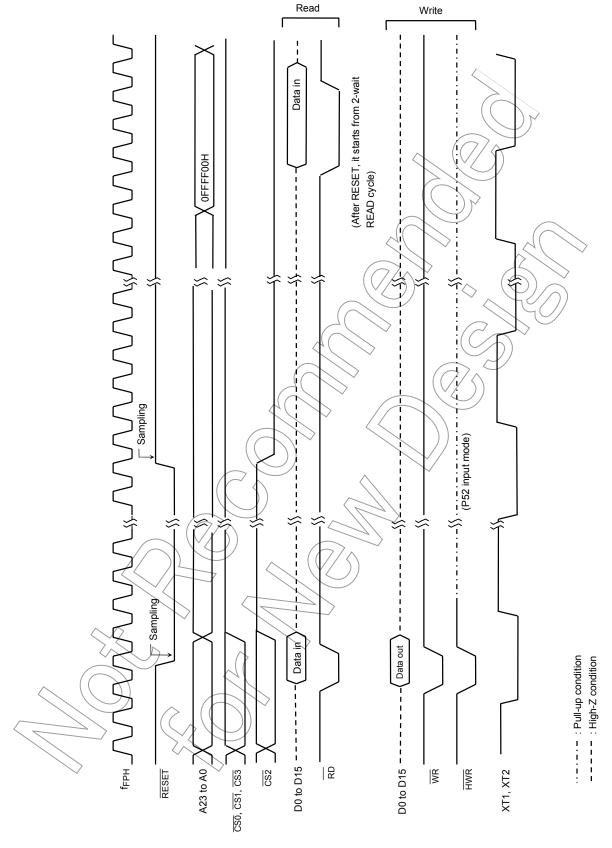

Figure 3.1.1 is a reset timing chart of the TMP91C016.

Figure 3.1.1 TMP91C016 Reset Timing Chart

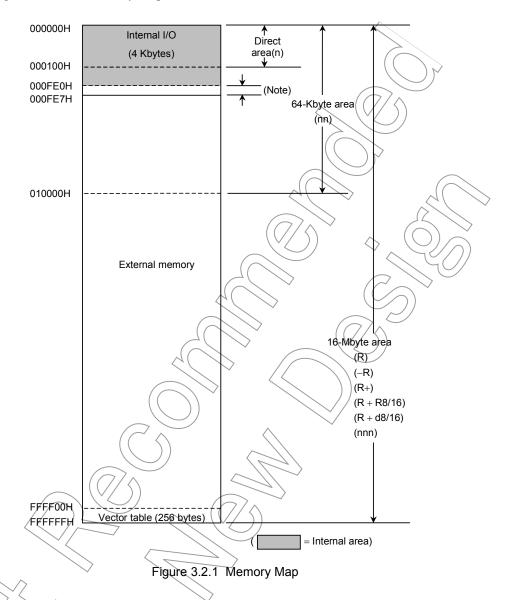

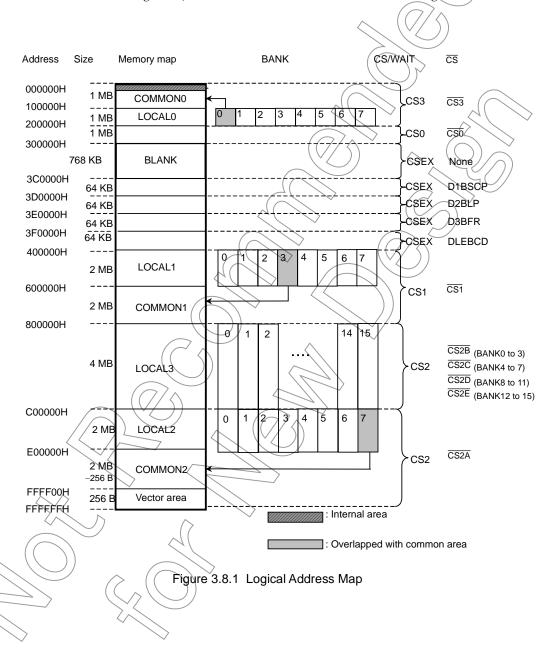

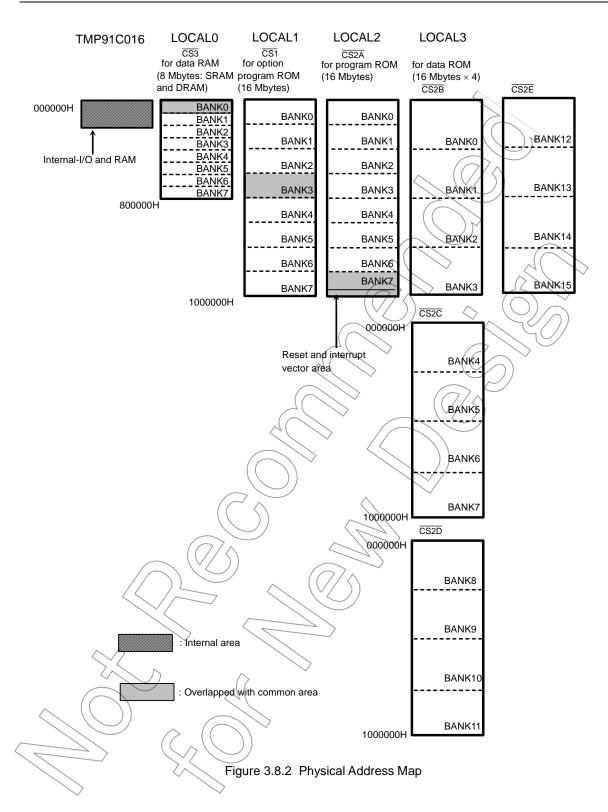

## 3.2 Memory Map

Figure 3.2.1 is a memory map of the TMP91C016.

Note: Address 000FE0H to 00FE7H are assigned for the external memory area of built-in RAM type LCD driver.

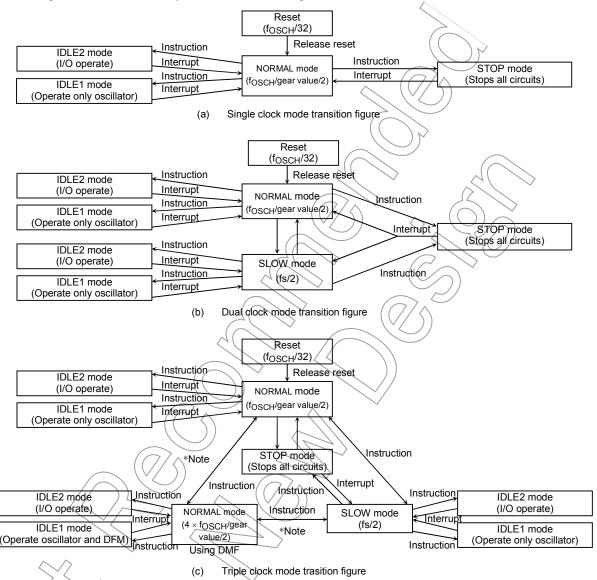

## 3.3 Triple Clock Function and Standby Function

TMP91C016 contains (1) clock gear, (2) clock doubler (DFM), (3) standby controller and (4) noise-reduction circuit. It is used for low-power, low-noise systems.

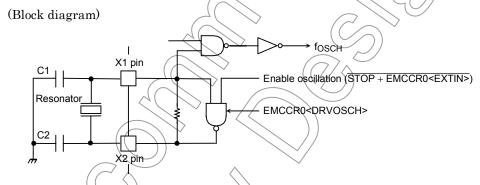

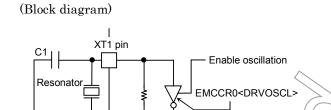

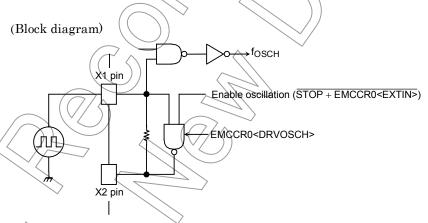

The clock operating modes are as follows: (a) Single clock mode (X1, X2 pins only), (b) Dual clock mode (X1, X2, XT1 and XT2 pins) and (c) Triple clock mode (the X1, X2, XT1 and XT2 pins and DFM).

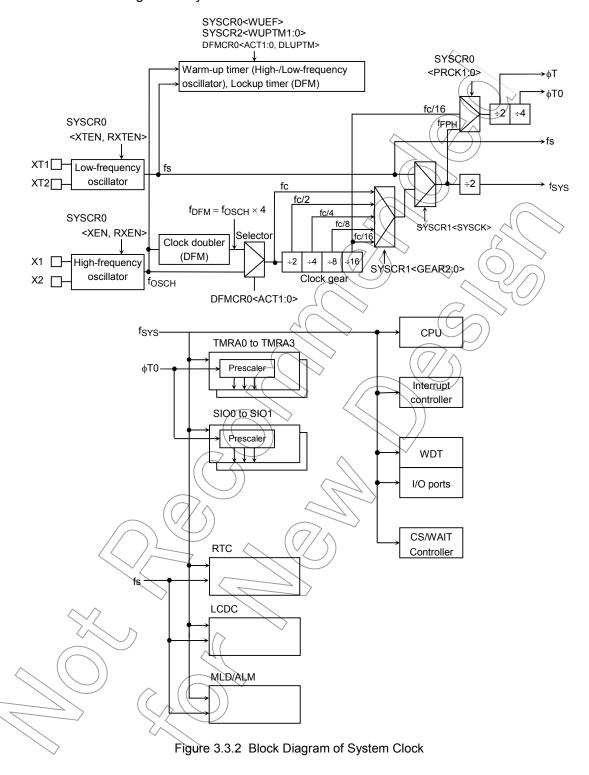

Figure 3.3.1 shows the system clock block diagrams.

Note 1: It's prohiibited to control DFM in SLOW mode when shifting from SLOW mode to NORMAL mode with use of DFM. (IDFM Start up/Stop/Change Write to DFMCR0<ACT1:0> register)

Note 2: If you shift from NORMAL mode with use of DFM to NORMAL mode, the above two instructions should be separated into two procedures as below. Change CPU clock → Stop DFM circuit.

Note 3: It's prohibited to shift from NORMAL mode with use of DFM to STOP mode directly. You should set NORMAL mode once, and then shift to STOP mode. (You should stop high frequency oscillator after you stop DFM.)

Figure 3.3.1 System Clock Block Diagram

The clock frequency input from the X1 and X2 pins is called fc, and the clock frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is called the system clock  $f_{FPH}$ . The system clock  $f_{SYS}$  is defined as the divided clock of  $f_{FPH}$ , and one cycle of  $f_{SYS}$  is regret to as one state.

### 3.3.1 Block Diagram of System Clock

#### 3.3.2 SFRs

|         |             | 7       | 6                                                                 | 5                                                                                                          | 4                                           | 3                                                                        | 2                                                                                                      | 1                                                                     | 0                                                                                                        |

|---------|-------------|---------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| SYSCR0  | Bit symbol  | XEN     | XTEN                                                              | RXEN                                                                                                       | RXTEN                                       | RSYSCK                                                                   | WUEF                                                                                                   | PRCK1                                                                 | PRCK0                                                                                                    |

| (00E0H) | Read/Write  |         |                                                                   |                                                                                                            | R/                                          | W                                                                        | •                                                                                                      |                                                                       |                                                                                                          |

|         | After reset | 1       | 1                                                                 | 1                                                                                                          | 0                                           | 0                                                                        | 0                                                                                                      | 20                                                                    | 0                                                                                                        |

|         | Function    | 0: Stop | Low-<br>frequency<br>oscillator (fs)<br>0: Stop<br>1: Oscillation | High-<br>frequency<br>oscillator (fc)<br>after release<br>of STOP<br>mode<br>0: Stop<br>1: Oscillation     | after release<br>of STOP<br>mode<br>0: Stop | Selects clock<br>after release<br>of STOP<br>mode<br>0: fc<br>1: fs      | Warm-up timer  0: Write Don't care 1: Write start timer 0: Read end Warm up 1: Read Do not end warm up | Select presca<br>00.1FPH<br>01: Reserved<br>10: fc/16<br>11: Reserved | ler clock                                                                                                |

|         |             | 7       | 6                                                                 | 5                                                                                                          | 4                                           | 3                                                                        | 2                                                                                                      | 1 $\Diamond$                                                          | \\Q\ \                                                                                                   |

| SYSCR1  | Bit symbol  |         |                                                                   |                                                                                                            |                                             | SYSCK                                                                    | GEAR2                                                                                                  | GEAR1                                                                 | GEAR0                                                                                                    |

| (00E1H) | Read/Write  |         |                                                                   |                                                                                                            |                                             | $(\vee \angle)$                                                          | Ŕ                                                                                                      | w (                                                                   |                                                                                                          |

|         | After reset |         |                                                                   |                                                                                                            | $\sim$                                      | 0                                                                        | 1                                                                                                      | (a)                                                                   | _( ø/                                                                                                    |

|         | Function    |         |                                                                   |                                                                                                            |                                             | Select<br>system clock<br>0: fc<br>1: fs                                 | 000: fc<br>001: fc/2<br>010: fc/4<br>011: fc/8<br>100: fc/16<br>101: (Reserve<br>110: (Reserve         | ed)                                                                   | 7                                                                                                        |

|         |             | 7       | 6                                                                 | 5                                                                                                          | √ 4                                         | \3                                                                       | )2)                                                                                                    | 1                                                                     | 0                                                                                                        |

| SYSCR2  | Bit symbol  |         | SCOSEL                                                            | WUPTM1                                                                                                     | WUPTM0                                      | HALTM                                                                    | HALTM0                                                                                                 | SELDRV                                                                | DRVE                                                                                                     |

| (00E2H) | Read/Write  |         | R/W-                                                              | RW                                                                                                         | R/W                                         | R/W                                                                      | √R/W                                                                                                   | R/W                                                                   | R/W                                                                                                      |

|         | After reset |         | 0                                                                 |                                                                                                            | 0                                           | 1                                                                        | 1                                                                                                      | 0                                                                     | 0                                                                                                        |

|         | Function    |         | 0: fs                                                             | Warm-up time<br>00: Reserved<br>01: 2 <sup>8</sup> /inputted<br>10: 2 <sup>14</sup><br>11: 2 <sup>16</sup> | /                                           | HALT mode<br>00: Reserved<br>01: STOP mo<br>10: IDLE1 mo<br>11: IDLE2 mo | de                                                                                                     | <drve><br/>mode<br/>select<br/>0: STOP<br/>1: IDLE1</drve>            | Pin state<br>control in<br>STOP/IDLE1<br>mode<br>0: I/O off<br>1: Remains<br>the state<br>before<br>HALT |

| VLDCTL  | Bit symbol  |         |                                                                   |                                                                                                            |                                             | XT1VSEL                                                                  | VLD2VSE                                                                                                | VLD1VSE                                                               | VLD0VSE                                                                                                  |

| (0449H) | Read/Write  |         |                                                                   |                                                                                                            |                                             | W                                                                        | R/W                                                                                                    | R/W                                                                   | R/W                                                                                                      |

|         | After reset | /       |                                                                   |                                                                                                            |                                             | 0                                                                        | 0                                                                                                      | 0                                                                     | 0                                                                                                        |

|         | Function    |         |                                                                   |                                                                                                            |                                             | 0: Vcc<br>operation<br>1: Vref<br>operation                              | 0: VLD don't<br>use<br>1: VLD use                                                                      | 0: VLD don't<br>use<br>1: VLD use                                     | 0: VLD don't<br>use<br>1: VLD use                                                                        |

Note1: SYSCR1 bit7:4>,SYSCR2 bit7> are read as undefined value.

Note2: By reset, low-frequency oscillator become to enable condition.

Figure 3.3.3 SFR for System Clock

| Symbol   | Name        | Address |    | 7                                                            |      | 6           | 5           | 4                         | 3        | 2                           | 1     | 0   |

|----------|-------------|---------|----|--------------------------------------------------------------|------|-------------|-------------|---------------------------|----------|-----------------------------|-------|-----|

|          |             |         |    | ACT1                                                         |      | ACT0        | DLUPFG      | DLUPTM                    |          |                             |       |     |

|          |             |         |    | R/W                                                          |      | R/W         | R           | R/W                       |          |                             |       |     |

|          | DFM         |         |    | 0                                                            |      | 0           | 0           | 0                         |          | f                           |       |     |

| DFMCR0   | Control     | E8H     |    | DFM                                                          | LUP  | Select fFPH | Lockup      | Lockup time               |          | 7                           |       |     |

| Di Morto | Register 0  |         | 00 | STOP                                                         | STOP | fosch       | status flag | 0: 2 <sup>12</sup> /foscH |          |                             |       |     |

|          | , regions c | ,       | 01 | RUN                                                          | RUN  | fosch       | 0: End      | 1: 2 <sup>10</sup> /fosch |          |                             | J ) ~ |     |

|          |             |         | 10 | RUN                                                          | STOP | fDFM        | 1: Not end  |                           |          |                             |       |     |

|          |             |         | 11 | RUN                                                          | STOP | fosch       |             |                           | $\wedge$ | $(//\langle \cdot \rangle)$ |       |     |

|          |             |         |    | D7                                                           |      | D6          | D5          | D4                        | D3       | D2/                         | D1    | D0  |

|          | DFM         |         |    | R/W                                                          |      | R/W         | R/W         | R/W                       | R/W      | R/W                         | R/W   | R/W |

| DFMCR1   | Control     | E9H     |    | 0                                                            |      | 0           | 0           | 1                         | 6        | ) 1/0                       | 1     | 1   |

| DIWORT   | Register 1  | L311    |    |                                                              |      |             |             | DFM r                     | evision  |                             |       |     |

|          | Register 1  |         |    | Input frequency 4 to 6.75 MHz (at 2.7 V to 3.6 V): Write 0BH |      |             |             |                           |          |                             |       |     |

|          |             |         |    | Input frequency 2 to 2.5 MHz (at 2.0 ± 10%): Write 1BH       |      |             |             |                           |          | $\rightarrow$               |       |     |

Figure 3.3.4 SFR for DFM

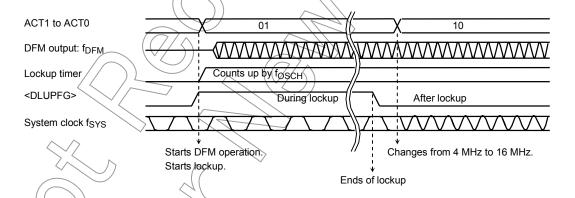

#### Limitation point on the use of DFM

1. It's prohibited to execute DFM enable/disable control in the SLOW mode (fs) (write to DFMCR0<ACT1:0> = "10"). You should control DFM in the NORMAL mode.

2. If you stop DFM operation during using DFM (DFMCR0<ACT1:0>= "10"), you shouldn't executions should be separated into two procedures as showing below.

LD (DFMCR0), C0H

; Change the clock f<sub>DFM</sub> to f<sub>OSCH</sub>

LD (DFMCR0), 00H

; DFM stop

3. If you stop high frequency oscillator during using DFM (DFMCR0<ACT1:0> = "10"), you should stop DFM before you stop high frequency oscillator.

Please refer to 3.35 "Clock Doubler (DFM)" for the details.

|                   |             | 7            | 6                                                                                                                | 5               | 4             | 3         | 2              | 1                 | 0             |  |  |  |  |

|-------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-----------|----------------|-------------------|---------------|--|--|--|--|

| EMCCR0            | Bit symbol  | PROTECT      | _                                                                                                                | _               | -             | -         | EXTIN          | DRVOSCH           | DRVOSCL       |  |  |  |  |

| (00E3H)           | Read/Write  | R            | R/W                                                                                                              | R/W             | R/W           | R/W       | R/W            | R/W               | R/W           |  |  |  |  |

|                   | After reset | 0            | 0                                                                                                                | 1               | 0             | 0         | 0              | <u>( 1</u>        | 1             |  |  |  |  |

|                   | Function    | Protect flag | Always                                                                                                           | Always          | Always        | Always    | 1: External    | fc oscillator     | fs oscillator |  |  |  |  |

|                   |             | 0: OFF       | Write "0"                                                                                                        | Write "1"       | Write "0"     | Write "0" | clock          | drivability       | drivability   |  |  |  |  |

|                   |             | 1: ON        |                                                                                                                  |                 |               |           |                | 1: Normal         | 1. Normal     |  |  |  |  |

|                   |             |              |                                                                                                                  |                 |               |           |                | 0: Weak           | 0: Weak       |  |  |  |  |

| EMCCR1            | Bit symbol  |              |                                                                                                                  |                 |               |           | $\sim$ (()     | // \              |               |  |  |  |  |

| (00E4H)           | Read/Write  |              | Switching the protect ON/OFF by write to following 1st key, 2nd key                                              |                 |               |           |                |                   |               |  |  |  |  |

|                   | After reset |              | 1st key: EMCCR1 = 5AH, EMCCR2 = A5H in succession write                                                          |                 |               |           |                |                   |               |  |  |  |  |

|                   | Function    |              | 1st key: EMCCR1 = 5AH, EMCCR2 = A5H in succession write  2nd key: EMCCR1 = A5H, EMCCR2 = 5AH in succession write |                 |               |           |                |                   |               |  |  |  |  |

| EMCCR2<br>(00E5H) | Bit symbol  |              |                                                                                                                  |                 |               |           |                |                   |               |  |  |  |  |

|                   | Read/Write  |              |                                                                                                                  |                 |               |           |                |                   |               |  |  |  |  |

|                   | After reset |              |                                                                                                                  |                 |               |           |                |                   |               |  |  |  |  |

|                   | Function    |              |                                                                                                                  |                 |               |           |                |                   |               |  |  |  |  |

| EMCCR3            | Bit symbol  |              | ENFROM                                                                                                           | ENDROM          | ENPROM        |           | FFLAG          | DFLAG             | PFLAG         |  |  |  |  |

| (00E6H)           | Read/Write  |              | R/W                                                                                                              | R/W             | R/W (         | Ž         | R/W            | R/W               | /R/W)         |  |  |  |  |

|                   | After reset |              | 0                                                                                                                | 0               | 0 (           | $\sim$    | 0              | 0                 | $\sqrt{0}$    |  |  |  |  |

|                   | Function    |              | CS1A area                                                                                                        | CS2B-2G         | CS2A area     |           | CS1A write     | CS2B-2G           | CS2A write    |  |  |  |  |

|                   |             |              | detect                                                                                                           | area detect     | detect        |           | operation (    | write             | operation     |  |  |  |  |

|                   |             |              | control                                                                                                          | control         | control       | ~         | flag           | operation<br>flag | flag          |  |  |  |  |

|                   |             |              | 0: Disable                                                                                                       | 0: Disable      | 0: Disable    |           | (O)            | \(\)              |               |  |  |  |  |

|                   |             |              | 1: Enable                                                                                                        | 1: Enable       | 1: Enable     |           | When readin    | g) )              |               |  |  |  |  |

|                   |             |              |                                                                                                                  | $\mathcal{A}()$ |               |           | 0: Not writter |                   |               |  |  |  |  |

|                   |             |              |                                                                                                                  |                 | ,             | //        | 1: Written     |                   |               |  |  |  |  |

|                   |             |              |                                                                                                                  |                 | $\rightarrow$ |           | When writing   |                   |               |  |  |  |  |

|                   |             |              |                                                                                                                  |                 |               |           | 0: Clear flag  | 1                 |               |  |  |  |  |

| EMCCR4            | Bit symbol  |              |                                                                                                                  | $\mathcal{Y}$   |               | *         | $\int_{0}^{1}$ | TA3MLDE           | TA3LCDE       |  |  |  |  |

| (00E7H)           | Read/Write  |              | $\mathcal{A}$                                                                                                    |                 |               |           |                | R/W               | R/W           |  |  |  |  |

|                   | After reset |              | $\mathcal{A}$                                                                                                    | $\nearrow$      | 4             | 11/       |                | 0                 | 0             |  |  |  |  |

|                   | Function    | /            |                                                                                                                  |                 |               |           |                | MLD CLK:          | LCD CLK:      |  |  |  |  |

|                   |             |              | (// {\                                                                                                           |                 |               | 7/        |                | 0: 32 kHz         | 0: 32 kHz     |  |  |  |  |

|                   |             |              |                                                                                                                  |                 |               | >         |                | 1: TA3            | 1: TA3        |  |  |  |  |

Note1: In case restarting the oscillator in the stop oscillation state (e.g. Restart the oscillator in STOP mode), set EMCCR0<PRVOSCH>, <DRVOSCL>="1"

Note2: When VCC=2V $\pm$ 10%, set EMCCR0<DRVOSCH> to "1".

#### 3.3.3 System Clock Controller

The system clock controller generates the system clock signal (fsys) for the CPU core and internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency (fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs, SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator, and SYSCR1<GEAR0:2> sets the high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4, fc/8 or fc/16). These functions can reduce the power consumption of the equipment in which the device is installed.

The combination of settings  $\langle XEN \rangle = 1$ ,  $\langle XTEN \rangle = 0$ ,  $\langle SYSCK \rangle = 0$  and  $\langle GEAR0:2 \rangle = 100$  will cause the system clock (fsys) to be set to fc/32 (fc/16 × 1/2) after a Reset.

For example, fsys is set to 0.84 MHz when the 27-MHz oscillator is connected to the X1 and X2 pins. And TMP91C016 has another power terminal: VREF except DVCC, this VREF power terminal supply to low-frequency oscillator operation and reference voltage for VLD operation. That can controll low-frequency oscillator's power DVCC or VREF by VLDCTL<XTVSEL>.

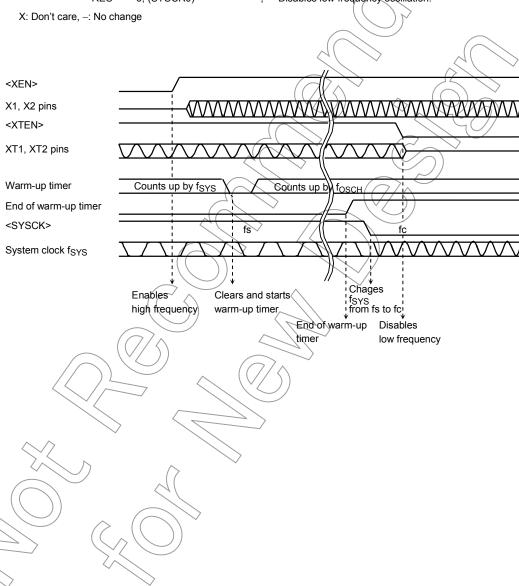

#### (1) Switching from NORMAL mode to SLOW mode

When the resonator is connected to the X1 and X2 pins, or to the XT1 and XT2 pins, the warm-up timer can be used to change the operation frequency after stable oscillation has been attained.

The warm-up time can be selected using SYSCR2<WUPTM0:1>.

This warm-up timer can be programmed to start and stop as shown in the following examples 1 and 2.

Table 3.3.1 shows the warm up time.

Note 1: When using an oscillator (other than a resonator) with stable oscillation, a warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

Table 3.3.1 Warm-up Times

| Warm-up Time<br>SYSCR2<br><wuptm1:0></wuptm1:0> | Change to NORMAL Mode | Change to<br>SLOW Mode |

|-------------------------------------------------|-----------------------|------------------------|

| 01 (28/frequency)                               | 9.0 μs                | 7.8 ms                 |

| 10 (2 <sup>14</sup> /frequency)                 | 0.607 ms              | 500 ms                 |

| 11 (2 <sup>16</sup> /frequency)                 | 2,427 ms              | 2000 ms                |

at foscH= 27 MHz, fs = 32.768 kHz

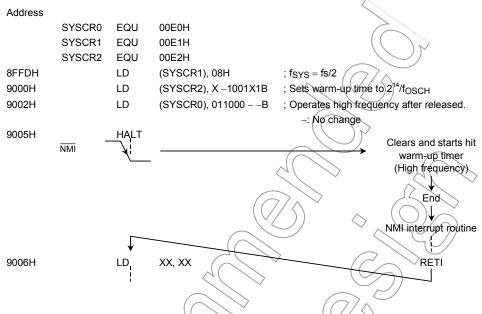

Example 1: Setting the clock

Changing from high frequency (fc) to low frequency (fs).

| 0 0                        |                                       | 1 1 1 1                                                                                                                                                                                                                                                    |

|----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCR0<br>SYSCR1<br>SYSCR2 | EQU<br>EQU<br>EQU<br>LD               | 00E0H<br>00E1H<br>00E2H<br>(SYSCR2), X-11X-B ; Sets warm-up time to 2 <sup>16</sup> /fs.                                                                                                                                                                   |

| WUP:                       | SET<br>SET<br>BIT<br>JR<br>SET<br>RES | 6, (SYSCR0) ; Enables low-frequency oscillation. 2, (SYSCR0) ; Clears and starts warm-up timer. 2, (SYSCR0) ; Detects stopping of warm-up timer. 3, (SYSCR1) ; Changes f <sub>SYS</sub> from fc. to fs. 7, (SYSCR0) ; Disables high-frequency oscillation. |

| X: Don't care,             | -: No chan                            |                                                                                                                                                                                                                                                            |

|                            |                                       |                                                                                                                                                                                                                                                            |

| <xen></xen>                |                                       |                                                                                                                                                                                                                                                            |

| X1, X2 pins                |                                       |                                                                                                                                                                                                                                                            |

| <xten></xten>              |                                       |                                                                                                                                                                                                                                                            |

| XT1, XT2 pins              | 3                                     |                                                                                                                                                                                                                                                            |

| Warm-up time               | er                                    | Counts up by f <sub>SYS</sub> Counts up by fs                                                                                                                                                                                                              |

| End of warm-               | up timer                              |                                                                                                                                                                                                                                                            |

| <sysck></sysck>            |                                       | fc                                                                                                                                                                                                                                                         |

| System clock               | f <sub>SYS</sub>                      |                                                                                                                                                                                                                                                            |

|                            |                                       |                                                                                                                                                                                                                                                            |

|                            |                                       | Enables Clears and starts Chages f <sub>SYS</sub> Disables f <sub>SYS</sub> bight frequency                                                                                                                                                                |

|                            |                                       |                                                                                                                                                                                                                                                            |

|                            |                                       | End of warm-up timer                                                                                                                                                                                                                                       |

|                            | _ ((                                  |                                                                                                                                                                                                                                                            |

|                            | ) $)$ $)$                             |                                                                                                                                                                                                                                                            |

|                            | //_                                   |                                                                                                                                                                                                                                                            |

|                            |                                       |                                                                                                                                                                                                                                                            |

| $\langle \rangle \rangle$  |                                       |                                                                                                                                                                                                                                                            |

|                            |                                       |                                                                                                                                                                                                                                                            |

|                            |                                       |                                                                                                                                                                                                                                                            |

|                            | $\wedge$                              |                                                                                                                                                                                                                                                            |

| 2>                         |                                       |                                                                                                                                                                                                                                                            |

| _                          | 1/2                                   |                                                                                                                                                                                                                                                            |

| \                          |                                       |                                                                                                                                                                                                                                                            |

Example 2: Setting the clock

Changing from low frequency (fs) to high frequency (fc).

| 01/0000        | FOLI      | 005011            |                                             |

|----------------|-----------|-------------------|---------------------------------------------|

| SYSCR0         | EQU       | 00E0H             |                                             |

| SYSCR1         | EQU       | 00E1H             |                                             |

| SYSCR2         | EQU       | 00E2H             |                                             |

|                | LD        | (SYSCR2), X-10X-B | ; Sets warm-up time to 2 <sup>14</sup> /fc. |

|                | SET       | 7, (SYSCR0)       | ; Enables high-frequency oscillation.       |

|                | SET       | 2, (SYSCR0)       | ; Clears and starts warm-up timer.          |

| WUP:           | BIT       | 2, (SYSCR0)       | ; } Detects stopping of warm-up/timer.      |

|                | JR        | NZ, WUP           | ; J Detects stopping of waiting times.      |

|                | RES       | 3, (SYSCR1)       | ; Changes f <sub>SYS</sub> from fs to fc.   |

|                | RES       | 6, (SYSCR0)       | ; Disables low-frequency oscillation.       |

| X: Don't care, | -: No cha | nge               |                                             |

#### (2) Clock gear controller

When the high-frequency clock fc is selected by setting SYSCR1<SYSCK> = 0, fFPH is set according to the contents of the clock gear select register SYSCR1<GEAR0:2> to either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of fFPH reduces power consumption.

Example 3: Changing to a high-frequency gear

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0000B ; Changes f<sub>SYS</sub> to fc/2. LD (SYSCR1), XXXX0100B ; Changes f<sub>SYS</sub> to fc/32

X: Don't care

(High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2:0> register. It is necessary the warm-up time until changing after writing the register value.

There is the possibility that the instruction next to the clock gear changing instruction is executed by the clock gear before changing. To execute the instruction next to the clock gear switching instruction by the clock gear after changing, input the dummy instruction as follows (Instruction to execute the write cycle).

#### Example:

SYSCR1

EQU 00E1H

LD (SYSCR1), XXXX0001B ; Changes f<sub>SYS</sub> to fc/4.

LD (DUMMY), 00H ; Dummy instruction

Instruction to be executed after clock gear has changed

#### (3) Internal clock terminal out function

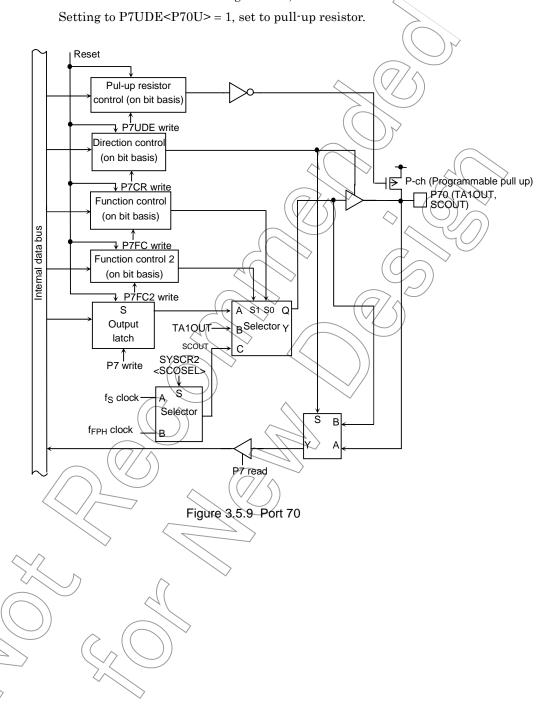

It can out internal clock (fFPH or fs) from P70 (TA1OUT, SCOUT).

P70 pin function is set to SCOUT output by the following bit setting.

P7CR < P70F > 1, P7FC < P70F > 0, P7FC < P70F > 0

Output clock select

: Refer to SYSCR2<SCOSED> bit setting

Table 3.3.2 SCOUT Output Condition

|   | HALT Mode             | NORMAL Mode          |              | HALT Mode  |           |

|---|-----------------------|----------------------|--------------|------------|-----------|

|   | SCOUT Select          | SLOW Mode            | IDLE2 Mode   | IDEL1 Mode | STOP Mode |

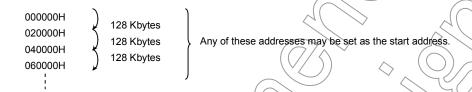

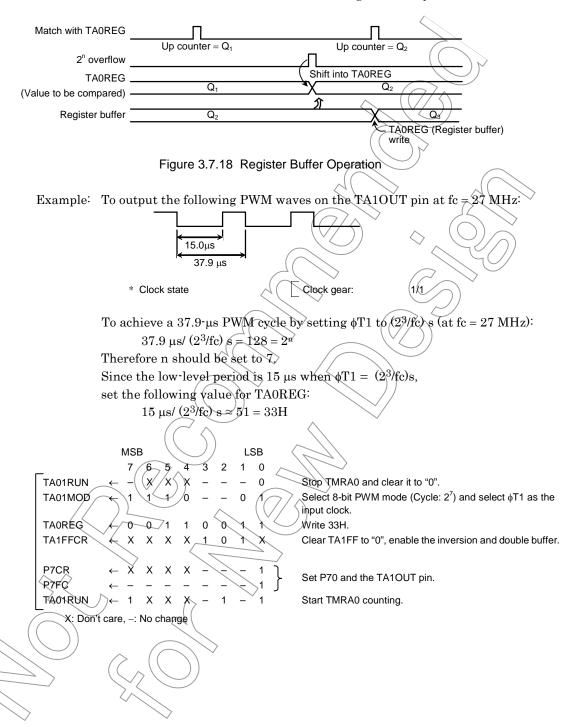

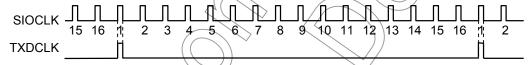

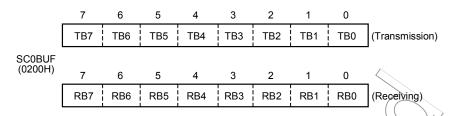

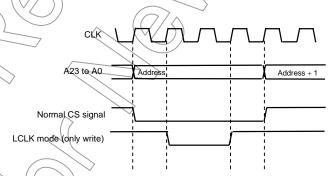

| Ţ | <scosel> = 0</scosel> |                      | fs clock out |            |           |