#### 4-Switch Buck-Boost

### **Charger Controller with I2C Interface**

Preliminary Specifications Subject to Change without Notice

### **DESCRIPTION**

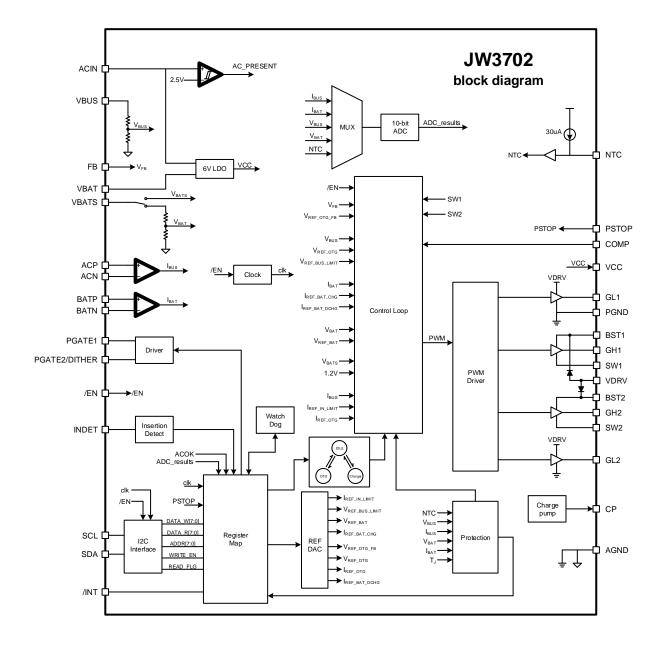

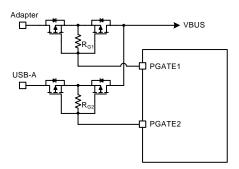

The JW®3702 is a synchronous 4-switch buck-boost controller capable of charging 1-4 cell Li-ion batteries with high light load efficiency and fast transient response. It can charge the battery from a wide range of input sources, such as USB adapter, high voltage USB PD sources and traditional adapters.

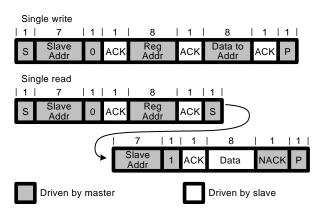

The JW3702 supports I2C serial communication interface to program a lot of parameters of the chip, offering a flexible solution for battery charging applications. An internal 10-bit ADC is provided to monitor the bus voltage, bus current, battery voltage, battery current and NTC resistor voltage, so user can monitor the system status in real time.

The device also supports OTG function to deliver power from battery to other portable devices through USB port. And the OTG voltage and current limit can be programmed by I2C interface.

The JW3702 guarantees robustness with battery/ OTG over-voltage protection, bus/ battery under-voltage protection, OTG/ battery over-current protection, charging timeout, watchdog and thermal shutdown.

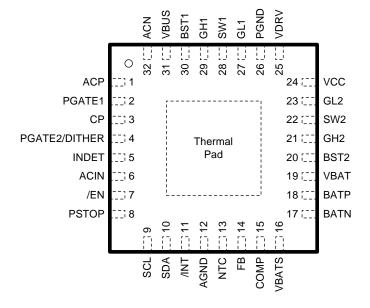

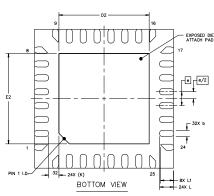

The JW3702 is available in QFN4X4-32 package.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Inc.

#### **FEATURES**

- Up to 28V breakdown voltage

- 3.0V to 24V input voltage range

- 2.4V to 24V OTG output voltage range

- Support 1-4 cell batteries charging and discharging

- 150kHz to 500kHz programmable switching frequency

- I2C interface supported

- Integrate 10-bit ADC to monitor bus voltage, bus current, battery voltage, battery current and NTC resistor voltage

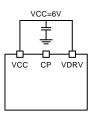

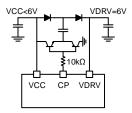

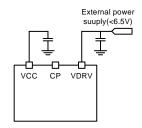

- Integrate charge pump circuit to provide 6V drive voltage even with single cell application

- Safety

- battery/OTG over-voltage protection

- bus/battery under-voltage protection

- OTG/battery over-current protection

- charging timeout

- watchdog protection

- thermal shutdown

- Ultra-low quiescent current: 12uA (typical)

- Package: QFN4X4-32

#### **APPLICATIONS**

- Power bank

- USB Type-C PD

- USB-HUB

- Portable devices with rechargeable battery

- Industrial applications

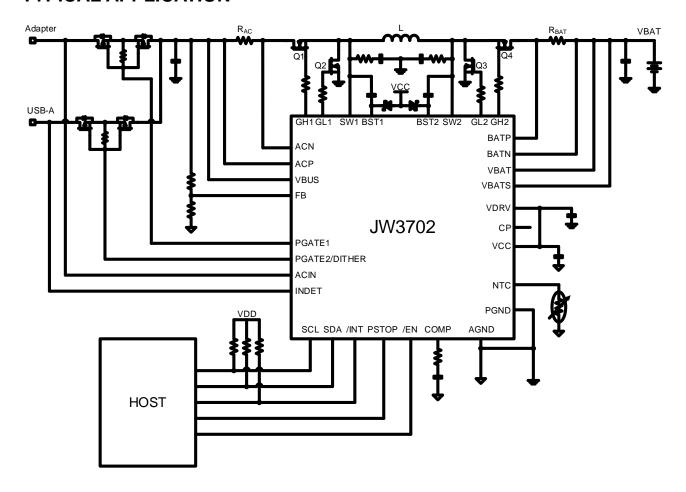

### **TYPICAL APPLICATION**

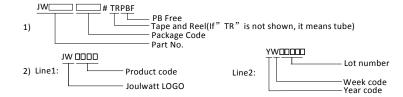

#### ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE   | TOP MARKING <sup>2)</sup> |

|----------------------|-----------|---------------------------|

| NA/2702OFAIK#TDDDF   | OFNAVA 22 | JW3702                    |

| JW3702QFNK#TRPBF     | QFN4X4-32 | YW□□□□                    |

#### Note:

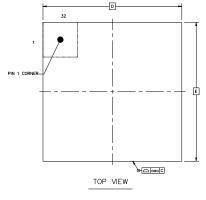

### **PIN CONFIGURATION**

#### **TOP VIEW**

## **ABSOLUTE MAXIMUM RATING<sup>1)</sup>**

| INDET, ACIN, VBUS, ACP, ACN, VBAT, BATP, BATN, FB, VBATS | 0.3V to 28V                                                                  |

|----------------------------------------------------------|------------------------------------------------------------------------------|

| SW1, SW2                                                 | 2.0V to 28V                                                                  |

| /EN, PSTOP, PGATE1, PGATE2/DITHER                        | 0.3V to 28V                                                                  |

| BST1, BST2, GH1, GH2                                     | 0.3V to 34V                                                                  |

| BST1-SW1, BST2-SW2                                       | 0.3V to 7V                                                                   |

| All Other Pins                                           |                                                                              |

| Junction Temperature <sup>2)3)</sup>                     | 40°C to 150°C                                                                |

| Lead Temperature                                         | 260°C                                                                        |

| ESD Susceptibility (Human Body Model)                    | ±2kV                                                                         |

| RECOMMENDED OPERATING CONDITIONS                         |                                                                              |

| Input Voltage VBUS                                       | 3.0V to 24V                                                                  |

| Battery Voltage VBAT                                     | 3.0V to 24V                                                                  |

| Operation Junction Temp (T <sub>J</sub> )                | 40°C to +125°C                                                               |

| THERMAL PERFORMANCE <sup>4)</sup>                        | $	heta_{\!\scriptscriptstyle J\!A} \qquad 	heta_{\!\scriptscriptstyle J\!c}$ |

| QFN4X4-32                                                |                                                                              |

#### Note:

- 1) Exceeding these ratings may damage the device.

- 2) The JW3702 guarantees robust performance from -40°C to 150°C junction temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

- 3) The JW3702 includes thermal protection that is intended to protect the device in overload conditions. Thermal protection is active when junction temperature exceeds the maximum operating junction temperature. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 4) Measured on JESD51-7, 4-layer PCB.

### **ELECTRICAL CHARACTERISTICS**

| VBUS=10V, TA=25°C, unless otherwise stated |                       |                                                       |      |      |      |       |

|--------------------------------------------|-----------------------|-------------------------------------------------------|------|------|------|-------|

| Item                                       | Symbol                | Condition                                             | Min. | Тур. | Max. | Units |

| Power supply                               |                       |                                                       |      |      |      |       |

| Operation input voltage                    | V <sub>IN</sub>       |                                                       | 3.0  |      | 24   | V     |

| VBUS under-voltage lockout                 | V                     | V <sub>BUS</sub> rising                               |      | 3.0  |      | V     |

| threshold                                  | V <sub>BUS_UVLO</sub> | V <sub>BUS</sub> falling                              |      | 2.5  |      | V     |

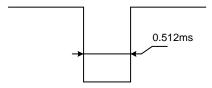

| VBUS_UVLO deglitch time                    | <b></b>               | V <sub>BUS</sub> rising to recover from VBUS_UVLO     |      | 250  |      | ms    |

| VB03_0VLO degilicii time                   | tbus_uvlo_deg         | V <sub>BUS</sub> falling to trigger VBUS_UVLO         |      | 8    |      | ms    |

| AC_PRESENT threshold                       | V <sub>AC_PRE</sub>   | V <sub>ACIN</sub> rising                              |      | 3.0  |      | V     |

| AC_PRESENT tillesiloid                     | V AC_PRE              | V <sub>ACIN</sub> falling                             |      | 2.5  |      | V     |

| AC DDECENT de alitab time                  | tac_pre_deg           | V <sub>ACIN</sub> rising to set AC_PRESENT bit        |      | 250  |      | ms    |

| AC_PRESENT deglitch time                   |                       | V <sub>ACIN</sub> falling to clear AC_PRESENT bit     |      | 8    |      | ms    |

| Battery under-voltage lockout              | V                     | V <sub>BAT</sub> rising, BATUVP_SEL=0b                |      | 3.0  |      | V     |

| threshold                                  | V <sub>BAT_UVLO</sub> | V <sub>BAT</sub> falling, BATUVP_SEL=0b               |      | 2.5  |      | V     |

| VDAT LIVI O do clitale tica o              | tbat_uvlo_deg         | V <sub>BAT</sub> rising to recover from VBAT_UVLO     |      | 20   |      | ms    |

| VBAT_UVLO deglitch time                    |                       | V <sub>BAT</sub> falling to trigger VBAT_UVLO         |      | 200  |      | ms    |

| VCC output voltage                         | Vcc                   | /EN=L, V <sub>BUS</sub> =10V, I <sub>VCC</sub> =0A    | 5.9  | 6.0  | 6.1  | V     |

| VCC output current limit                   | Ivcc                  | /EN=L, V <sub>BUS</sub> =10V                          |      | 30   |      | mA    |

| Quiescent current into VBUS                | IQ_VBUS               | /EN=L, PSTOP=H,<br>AD_START=0, VBUS=10V               |      | 115  |      | μA    |

| Quiescent current into VBAT                | Iq_vbat               | /EN=L, PSTOP=H,<br>AD_START=0, VBAT=24V,<br>VBUS open |      | 35   |      | μА    |

| Shutdown current into VBAT                 | I <sub>SD_VBAT</sub>  | /EN=H, VBAT=24V, VBUS open                            |      | 12   |      | μA    |

| Charge mode                                |                       |                                                       |      |      |      |       |

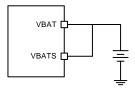

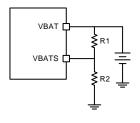

| Battery voltage regulation range           | $V_{BAT}$             |                                                       | 2.4  |      | 24   | V     |

| Battery voltage regulation accuracy                                             | V <sub>BAT_ACC</sub>     | VBAT_FB_SEL=0b, as percentage of the value set in | -0.5  |      | 0.5   | %  |

|---------------------------------------------------------------------------------|--------------------------|---------------------------------------------------|-------|------|-------|----|

| VBATS reference voltage for external setting                                    | VBATS                    | VBAT_SET register  VBAT_FB_SEL=1b                 | 1.194 | 1.2  | 1.206 | V  |

| The maximum compensation voltage when battery impedance compensation is enabled | Vсомр_мах                |                                                   |       | 125  |       | mV |

| Input voltage regulation range in charge mode                                   | VINDPM                   |                                                   | 3.0   |      | 24    | V  |

|                                                                                 |                          | VBUS_SCALE=0b,                                    |       | 5    |       | V  |

|                                                                                 |                          | VINDPM_H=00h,<br>VINDPM_L=FAh,                    | -2    |      | 2     | %  |

|                                                                                 |                          | VBUS_SCALE=0b,                                    |       | 10   |       | ٧  |

| Input voltage regulation                                                        | VINDPM_ACC               | VINDPM_H=01h,<br>VINDPM_L=F4h                     | -2    |      | 2     | %  |

| accuracy in charge mode                                                         |                          | VBUS_SCALE=1b,                                    |       | 10   |       | V  |

|                                                                                 |                          | VINDPM_H=00h,<br>VINDPM_L=FAh                     | -2    |      | 2     | %  |

|                                                                                 |                          | VBUS_SCALE=1b,                                    |       | 20   |       | V  |

|                                                                                 |                          | VINDPM_H=01h,<br>VINDPM_L=F4h                     | -2    |      | 2     | %  |

| Input current limit range in charge mode                                        | lin                      | R <sub>AC</sub> =10mΩ                             | 0     |      | 12750 | mA |

|                                                                                 |                          | R <sub>AC</sub> =10mΩ, IBUS_SCALE=0b,             |       | 2000 |       | mA |

|                                                                                 |                          | IIN_LIMIT=50h                                     | -5    |      | 5     | %  |

|                                                                                 |                          | R <sub>AC</sub> =10mΩ, IBUS_SCALE=0b,             |       | 4000 |       | mA |

| Input current limit accuracy in                                                 | I <sub>IN_ACC</sub>      | IIN_LIMIT=A0h                                     | -5    |      | 5     | %  |

| charge mode                                                                     | IIN_ACC                  | $R_{AC}$ =10m $\Omega$ , IBUS_SCALE=1b,           |       | 4000 |       | mA |

|                                                                                 |                          | IIN_LIMIT=50h                                     | -5    |      | 5     | %  |

|                                                                                 |                          | R <sub>AC</sub> =10mΩ, IBUS_SCALE=1b,             |       | 6000 |       | mA |

|                                                                                 |                          | IIN_LIMIT=78h                                     | -5    |      | 5     | %  |

| Battery current limit range in charge mode                                      | I <sub>BAT_CHG</sub>     | R <sub>BAT</sub> =10mΩ                            | 0     |      | 12750 | mA |

| D. (1 ) (1 )                                                                    |                          | R <sub>BAT</sub> =10mΩ, IBAT_SCALE=0b             |       | 2000 |       | mA |

| Battery current limit accuracy in charge mode                                   | I <sub>BAT_CHG_ACC</sub> | IBAT_CHG=50h                                      | -5    |      | 5     | %  |

| in sharge mode                                                                  |                          | R <sub>BAT</sub> =10mΩ, IBAT_SCALE=0b             |       | 4000 |       | mA |

This document contains information of a product under development.

Joulwatt reserves the right to change this product without notice.

|                                          |                      | IBAT_CHG=A0h                                            | -5  |      | 5  | %    |

|------------------------------------------|----------------------|---------------------------------------------------------|-----|------|----|------|

|                                          |                      | R <sub>BAT</sub> =10mΩ, IBAT_SCALE=1b                   |     | 4000 |    | mA   |

|                                          |                      | IBAT_CHG=50h                                            | -5  |      | 5  | %    |

|                                          |                      | R <sub>BAT</sub> =10mΩ, IBAT_SCALE=1b                   |     | 6000 |    | mA   |

|                                          |                      | IBAT_CHG=78h                                            | -5  |      | 5  | %    |

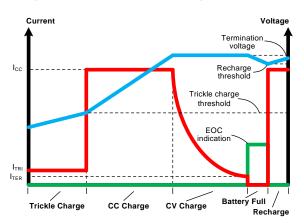

|                                          |                      | VTRICKLE_TH=0b, as                                      |     |      |    |      |

|                                          |                      | percentage of the setting                               |     | 70   |    | %    |

| Trialda abarras threahald                | $V_{TRI}$            | battery voltage                                         |     |      |    |      |

| Trickle charge threshold                 | VIRI                 | VTRICKLE_TH=1b, as                                      |     |      |    |      |

|                                          |                      | percentage of the setting                               |     | 60   |    | %    |

|                                          |                      | battery voltage                                         |     |      |    |      |

| Deglitch time to get out of trickle mode | ttri_deg             | V <sub>BAT</sub> rising to exceed V <sub>TRI</sub>      |     | 30   |    | ms   |

|                                          |                      | ICHG_SEL=0b, as percentage                              |     |      |    |      |

|                                          |                      | of the value set in IIN_LIMIT                           |     | 10   |    | %    |

| Titalda as a da abanca assessa t         | Itri<br>Iter         | register.                                               |     |      |    |      |

| Trickle mode charge current              |                      | ICHG_SEL=1b, as percentage                              |     |      |    |      |

|                                          |                      | of the value set in IBAT_CHG                            |     | 10   |    | %    |

|                                          |                      | register.                                               |     |      |    |      |

|                                          |                      | ITERM_SET=000b                                          |     | 100  |    | mA   |

| Charge termination current               |                      | ITERM_SET=010b                                          |     | 200  |    | mA   |

|                                          |                      | ITERM_SET=110b                                          |     | 400  |    | mA   |

| Battery full charge deglitch time        | t <sub>FULL</sub>    |                                                         |     | 5    |    | s    |

| Battery re-charge threshold              | VRECHG               | As percentage of the battery voltage regulation target. |     | 95   |    | %    |

| Battery re-charge deglitch time          | trechg               |                                                         |     | 30   |    | ms   |

| The stands of the                        |                      | $R_{AC}=10m\Omega,\ R_{BAT}=10m\Omega,$                 |     |      |    |      |

| The step length of charge                | ISTEP_CHG            | IBUS_SCALE=1b,                                          |     | 50   |    | mA   |

| current increase                         |                      | IBAT_SACLE=1b                                           |     |      |    |      |

| The step time of charge current increase | tstep_chg            |                                                         |     | 2    |    | ms   |

| CONTENT INCIGASE                         |                      | EN_OTG=0b, VBUS>VBUS_UVLO,                              |     |      |    |      |

| Deglitch time to start charging          | tous ses             | from PSTOP=L to converter                               |     | 50   |    | ms   |

|                                          | t <sub>CHG_DEG</sub> | starting switching.                                     |     |      |    | 1113 |

| OTG mode                                 |                      | otarting ownering.                                      |     |      |    |      |

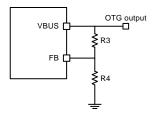

| Output voltage regulation                |                      |                                                         |     |      |    |      |

| range                                    | Vотg                 |                                                         | 2.4 |      | 24 | V    |

| J -                                      |                      |                                                         |     |      |    |      |

| Output voltage regulation accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |                           |                                            |       |      |       |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|--------------------------------------------|-------|------|-------|------|

| Output voltage regulation accuracy         Vote_Acc         VOTG_FB_SEL=0b, VOTG_L=EEh         15         V           Votage FB_SEL=1b, VOTG_H=00h, VOTG_L=EEh         -2         2         %           Votage FB_SEL=1b, VOTG_H=00h, VOTG_L=FAh         -2         2         %           FB reference voltage for external setting         Votage FB_SEL=1b, VOTG_FB_H=02h, VOTG_FB_H=02h, VOTG_FB_H=02h, VOTG_FB_L=58h         1.178         1.2         1.222         V           Output current limit range in discharge mode         Iord         Rac=10mΩ         0         12750         mA           Rax=10mΩ         0         12750         mA           Battery current limit accuracy in discharge mode         IBAT_DCHG=50h         -5         5         5         %           Battery current limit accuracy in discharge mode         IBAT_DCHG=50h         -5         5         %         %           Battery current limit accuracy in discharge mode         IBAT_DCHG=50h         -5         5         %         %           Battery current limit accuracy in discharge mode         IBAT_DCHG=50h         -5         5         %           Battery current limit accuracy in discharge mode         IBAT_DCHG=50h         -5         5         %           Rax=10mΩ, IBAT_SCALE=1b, IBAT_DCHG=50h         -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |                           | VOTG_FB_SEL=0b,                            |       | 5    |       | V    |

| Accuracy   VOTG_H=02h, VOTG_L=EEh   -2   2   %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                           | VOTG_H=00h, VOTG_L=FAh                     | -2    |      | 2     | %    |

| VOTG_H=02h, VOTG_L=EEh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Output voltage regulation                   | .,                        | VOTG_FB_SEL=0b,                            |       | 15   |       | V    |

| VOTG_H=00h, VOTG_L=FAh   -2   2   9   9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | accuracy                                    | Votg_acc                  | VOTG_H=02h, VOTG_L=EEh                     | -2    |      | 2     | %    |

| VOTG_H=00h, VOTG_L=FAh   -2   2   %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                           | VOTG_FB_SEL=1b,                            |       | 10   |       | V    |

| FB reference voltage for external setting  VFB  VOTG_FB_H=02h, VOTG_FB_L=58h  1.178  1.2  1.222  V  VOTG_FB_L=58h  Output current limit range in discharge mode  Rac=10mΩ  Rac=10mΩ  Rac=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=1b, BAT_DCHG=78h  The step length of output voltage increase  VSTEP_OTG  VSTEP_OTG  VBUS_SACLE=0b  20  mV  Protection  VBAT rising, as percentage of the value set in VBAT_SET register  VBAT falling, as percentage of the value set in VBAT_SET  register  VBAT falling, as percentage of the value set in VBAT_SET  register  VBAT falling, as percentage of the value set in VBAT_SET  102  VSTEP_OTG  VBAT falling, as percentage of the value set in VBAT_SET  register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |                           |                                            | -2    |      | 2     | %    |

| FB reference voltage for external setting  VFB  VOTG_FB_H=02h, VOTG_FB_L=58h  1.178  1.2  1.222  V  VOTG_FB_L=58h  Output current limit range in discharge mode  Rac=10mΩ  Rac=10mΩ  Rac=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=0b, BAT_DCHG=50h  Reat=10mΩ, BAT_SCALE=1b, BAT_DCHG=78h  The step length of output voltage increase  VSTEP_OTG  VSTEP_OTG  VBUS_SACLE=0b  20  mV  Protection  VBAT rising, as percentage of the value set in VBAT_SET register  VBAT falling, as percentage of the value set in VBAT_SET  register  VBAT falling, as percentage of the value set in VBAT_SET  register  VBAT falling, as percentage of the value set in VBAT_SET  102  VSTEP_OTG  VBAT falling, as percentage of the value set in VBAT_SET  register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |                           | VOTG_FB_SEL=1b,                            |       |      |       |      |

| VOTG_FB_L=58h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                           | $V_{FB}$                  | VOTG_FB_H=02h,                             | 1.178 | 1.2  | 1.222 | V    |

| Battery current limit accuracy in discharge mode   Iams   Rac=10mΩ   0   12750   mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | external setting                            |                           | VOTG_FB_L=58h                              |       |      |       |      |

| Rax1=10mΩ,   BAT_SCALE=0b,   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_6A0h   BAT_SCALE=0b,   BAT_DCHG_6A0h   BAT_DCHG_6A0h   BAT_SCALE=1b,   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   BAT_DCHG_50h   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output current limit range in               | lote                      | R <sub>40</sub> =10mO                      | 0     |      | 12750 | mΔ   |

| Battery current limit accuracy in discharge mode   Hart_DCHG_ACC   Hart_DCH                                                                                                                                                                                                                                                                                                                                                 | discharge mode                              | IOIG                      | TVAC - TOTTIS2                             | · ·   |      | 12730 | ША   |

| Battery current limit accuracy in discharge mode   IBAT_DCHG_50h   RBAT_BCHG_50h   RBAT_BCHG_50h   RBAT_BCHG_50h   RBAT_BCHG_50h   RBAT_DCHG_50h   RBAT_BCHG_50h   RBAT_BCH                                                                                                                                                                                                                                                                                                                                                 |                                             |                           | ·                                          |       | 2000 |       | mA   |

| Rate   10mΩ,   18AT_SCALE = 0b,   18AT_DCHG_ACC   18AT_DCHG_E = 0b,   18AT_DCHG_E =                                                                                                                                                                                                                                                                                                                                                 |                                             |                           |                                            | -5    |      | 5     | %    |

| Battery current limit accuracy in discharge mode   Battery current limit accuracy   Bat                                                                                                                                                                                                                                                                                                                                                 |                                             |                           |                                            |       |      |       |      |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |                           |                                            |       | 4000 |       | mA   |

| in discharge mode $\begin{bmatrix} BaT\_DCHG\_ACC \\ EBAT\_DCHG\_ACC \\ BAT\_DCHG\_ACC \\ EBAT\_SCALE=1b, \\ IBAT\_DCHG=50h \\ RBAT=10m\Omega, \\ IBAT\_SCALE=1b, \\ IBAT\_DCHG=78h \\ \end{bmatrix} = 5 \\ 5 \\ \%$ The step length of output voltage increase $\begin{bmatrix} V_{STEP\_OTG} \\ V_{STEP\_OTG} \end{bmatrix} = \begin{bmatrix} V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \end{bmatrix} = \begin{bmatrix} V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \\ V_{BUS\_SACLE=0b} \end{bmatrix} = \begin{bmatrix} V_{BUS\_SACLE=0b} \\ V_{BUS\_SA$ | Dottom, ourrant limit accuracy              | I <sub>BAT_DCHG_ACC</sub> | ·                                          | -5    |      | 5     | %    |

| IBAT_SCALE=1b,   IBAT_DCHG=50h   -5   5   %     RBAT=10mΩ,   G000   mA     RBAT_SCALE=1b,   IBAT_SCALE=1b,   IBAT_DCHG=78h   -5   5   %     The step length of output voltage increase   VSTEP_OTG   VBUS_SACLE=0b   20   mV     The step time of output voltage increase   The step time of output voltage increase   The step time of output voltage increase   EN_OTG=1b, VBUS <vbus_uvlo, %="" 104="" as="" converter="" g000="" in="" ma="" ma<="" of="" percentage="" protection="" pstop="L" rbat="10mΩ," rising,="" set="" starting="" switching.="" td="" the="" to="" town="" value="" vbat="" vbat_set=""  =""><td>-</td><td></td><td></td><td>4000</td><td></td><td>mΛ</td></vbus_uvlo,>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                           |                           |                                            |       | 4000 |       | mΛ   |

| IBAT_DCHG=50h   -5   5   %     RBAT=10mΩ,   BAT_SCALE=1b,   IBAT_DCHG=78h   -5   5   %     The step length of output voltage increase   VSTEP_OTG   VBUS_SACLE=0b   20   mV     The step time of output voltage increase   The step time of output voltage increase   STEP_OTG   EN_OTG=1b, VBUS_VBUS_UVLO,   TOWN                                                                                                                                                                                                                                                                                                                                                  | in dioditargo modo                          |                           |                                            |       | 4000 |       | IIIA |

| IBAT_SCALE=1b, IBAT_DCHG=78h  The step length of output voltage increase  The step time of output voltage increase  The step time of output voltage increase  The step time of output voltage increase <sup>5)</sup> Deglitch time to start OTG <sup>5)</sup> The step time of output tooltage increase <sup>5)</sup> EN_OTG=1b, V_Bus <v_bus_uvlo, %="" %<="" 102="" 104="" as="" converter="" engister="" falling,="" from="" in="" of="" percentage="" protection="" pstop="L" rising,="" set="" starting="" switching.="" td="" the="" to="" value="" vbat="" vbat_set=""><td></td><td></td><td>-5</td><td></td><td>5</td><td>%</td></v_bus_uvlo,>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |                           |                                            | -5    |      | 5     | %    |

| The step length of output voltage increase  The step time of output voltage increase  The step time of output voltage increase  The step time of output voltage increases  EN_OTG=1b, VBUS_VBUS_UVLO, from PSTOP=L to converter starting switching.  Protection  VBAT rising, as percentage of the value set in VBAT_SET register  VBAT falling, as percentage of the value set in VBAT_SET 102 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                           | R <sub>BAT</sub> =10mΩ,                    |       | 6000 |       | mA   |

| The step length of output voltage increase  The step time of output voltage volt                                                                                                                                                                                                                                                                                                                                              |                                             |                           | IBAT_SCALE=1b,                             | _     |      | _     | 0/   |

| Voltage increase  The step time of output voltage increase <sup>5)</sup> Deglitch time to start OTG <sup>5)</sup> Protection  VBUS_SACLE=0b  VBUS_SACLE=0b  100  µs  EN_OTG=1b, VBUS <vbus_uvlo, %="" 100="" 104="" 105="" 106="" 107="" 108="" 109="" as="" converter="" falling,="" from="" in="" of="" output="" percentage="" pstop="L" pushing="" rising,="" set="" starting="" step="" switching.="" td="" tegister="" temporal="" the="" time="" to="" value="" vbat="" vbat_set="" vbat_set<="" wbat=""><td></td><td>IBAT_DCHG=78h</td><td>-5</td><td></td><td>5</td><td>%</td></vbus_uvlo,>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |                           | IBAT_DCHG=78h                              | -5    |      | 5     | %    |

| The step time of output voltage increase   The step time of output voltage increase <sup>5)</sup> EN_OTG=1b, V_BUS <v_bus_uvlo, %="" %<="" 102="" 104="" as="" converter="" falling,="" from="" in="" of="" percentage="" protection="" pstop="L" register="" rising,="" set="" starting="" switching.="" td="" the="" to="" value="" vbat="" vbat_set=""><td>The step length of output</td><td>Veter ota</td><td>VBUS SACLE=0b</td><td></td><td>20</td><td></td><td>mV</td></v_bus_uvlo,>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The step length of output                   | Veter ota                 | VBUS SACLE=0b                              |       | 20   |       | mV   |

| voltage increase <sup>5)</sup> tstep_otg  EN_OTG=1b, V_Bus <v_bus_uvlo, %="" %<="" 102="" 104="" as="" converter="" falling,="" from="" in="" of="" percentage="" protection="" pstop="L" rising,="" set="" starting="" switching.="" td="" the="" to="" value="" vbat="" vbat_set=""><td>-</td><td>10121 _010</td><td>7200_0.1022 00</td><td></td><td></td><td></td><td></td></v_bus_uvlo,>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                           | 10121 _010                | 7200_0.1022 00                             |       |      |       |      |

| Deglitch time to start OTG <sup>5)</sup> The starting switching.  Protection  Very constant of the value set in VBAT_SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ·                                           | tstep_otg                 |                                            |       | 100  |       | μs   |

| Deglitch time to start OTG <sup>5)</sup> tcHG_DEG  from PSTOP=L to converter starting switching.  Protection  VBAT rising, as percentage of the value set in VBAT_SET  VBAT falling, as percentage of the value set in VBAT_SET  104  %  register  VBAT falling, as percentage of the value set in VBAT_SET  102  %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | voltage increase <sup>5)</sup>              |                           | EN OTO 45 V                                |       |      |       |      |

| Starting switching.  Protection  VBAT rising, as percentage of the value set in VBAT_SET 104 % register  VBAT falling, as percentage of the value set in VBAT_SET 102 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Doglitch time to start OTG5)                | tous are                  |                                            |       | 7    |       | me   |