1A, Low-Dropout High-PSRR, Low-Noise, LDO

### **DESCRIPTION**

JWQ7821 is a 1A high accuracy, low noise, high PSRR linear regulator with 200mV maximum dropout voltage. JWQ7821 supports input voltage ranges from 2.2 V to 5.5 V and adjustable output voltage range from 0.8 V to 5V.

Low noise, high PSRR and high current capability makes JWQ7821 ideal power supply for noise sensitive applications, such as VCO, PLL, ADC and CMOS sensor. Accurate output voltage tolerance and excellent transient response ensures JWQ7821 optimal power supply for processors and digital loads, such as ASIC, FPGA, CPLD and DSP.

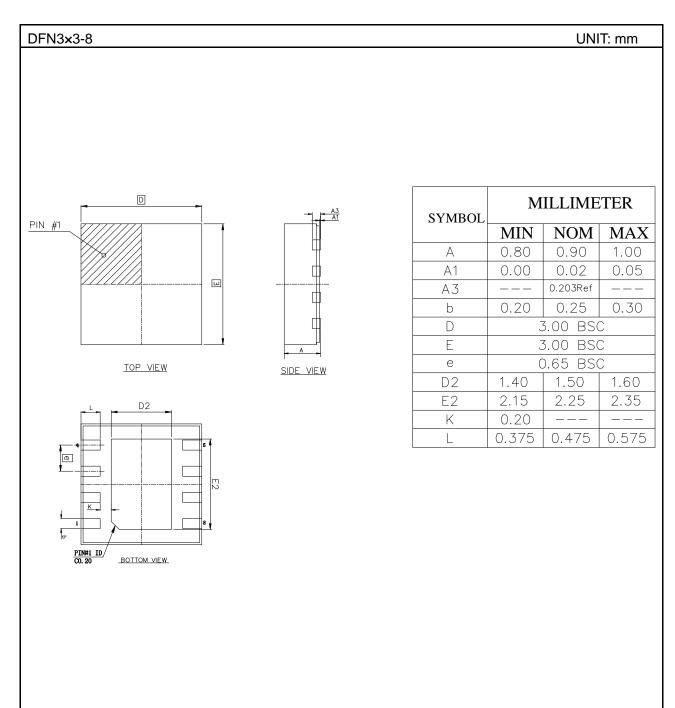

JWQ7821 provides 3mm×3mm DFN-8 package with guaranteed operating junction temperature range (T<sub>J</sub>) from -40°C to +125°C.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of Joulwatt technology Inc Co.,Ltd.

#### **FEATURES**

- AEC-Q100 Grade1 Qualified

- Input Voltage Range 2.2V to 5.5V

- Output Voltage Range 0.8V to 5V

- Low Dropout: 200mV Maximum at 1A

- High PSRR

- 78dB at 1kHz

- 42dB at 100kHz

- 30dB at 1MHz

- 3% Accuracy over Line Regulation, Load Regulation and Operating Temperature Range

- 35.6uV<sub>RMS</sub> Output Noise (100Hz 100kHz)

- Stable with 4.7µF Ceramic Output Capacitors

- Over Temperature and Overcurrent Protection

- Offer DFN3x3-8 Package

#### **APPLICATIONS**

- Automotive ADAS Domain Control Unit

- Automotive Body Control Unit

- Automotive Telematics Control Unit

- Automotive Infotainment and Cluster system

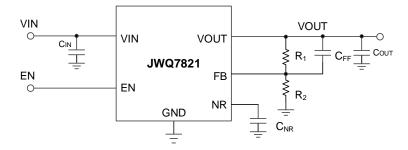

#### TYPICAL APPLICATION

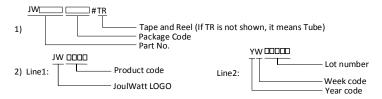

### **ORDER INFORMATION**

| DEVICE1)       | PACKAGE   | TOP MARKING2) | ENVIRONMENTAL3) |

|----------------|-----------|---------------|-----------------|

| JWQ7821DFNA#TR | DFN3x3-8  | JWQ7821       | Groon           |

| JWQ/821DFNA#TK | DEINOXO-0 | YW□□□□□       | Green           |

#### Notes:

3) All JoulWatt products are packaged with Pb-free and Halogen-free materials and compliant to RoHS standards.

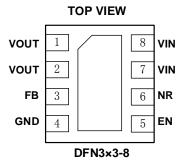

## **PIN CONFIGURATION**

# ABSOLUTE MAXIMUM RATING<sup>1)</sup>

| VIN, EN,OUT Pin                                | 0.3V to 7V    |

|------------------------------------------------|---------------|

| Other Pins                                     | 0.3V to 7V    |

| Junction Temperature <sup>2)</sup>             | 150°C         |

| Lead Temperature                               | 260°C         |

| Storage Temperature Range                      | 65°C to 150°C |

| ESD Susceptibility (Human Body Model)          | ±2kV          |

| ESD Susceptibility (Charged Device Model)      | ±1kV          |

| MSL                                            | MSL1          |

| Continuous Power Dissipation(TA=+25°C)DFN3×3-8 | 2.6W          |

## **RECOMMENDED OPERATING CONDITIONS<sup>3)</sup>**

| Input Voltage VIN                 | 2.2                               | V to 5.5V      |

|-----------------------------------|-----------------------------------|----------------|

| Output Voltage VOUT               | 0                                 | .8V to 5V      |

| Output Current                    |                                   | . 0A to 1A     |

| Junction Temperature Range        | 40°C                              | to 125°C       |

| THERMAL PERFORMANCE <sup>4)</sup> | $	heta_{\scriptscriptstyle J\!A}$ | $	heta_{J\!c}$ |

| DFN3X3-8                          | . 38                              | 6°C/W          |

#### Note:

- 2) The JWQ7821 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB

<sup>1)</sup> Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at other conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}=V_{OUT(NOM)}+0.5V$  or 2.2V,  $V_{EN}=2V$ ,  $I_{OUT}=1mA$ ,  $C_{IN}=10\mu F$ ,  $C_{OUT}=10\mu F$ ,  $C_{NR}=10nF$ ,  $T_{J}=-40$  °C to 125 °C, Unless otherwise stated.

| Item                                       | Symbol                                 | Cond                                                                       | litions                       | Min.     | Тур.  | Max. | Unit              |

|--------------------------------------------|----------------------------------------|----------------------------------------------------------------------------|-------------------------------|----------|-------|------|-------------------|

| Input Voltage                              | V <sub>IN</sub>                        | T <sub>A</sub> =25°C                                                       |                               | 2.2      |       | 5.5  | V                 |

| Undervoltage Lockout                       | UVLO                                   | VIN rising                                                                 |                               | 1.86     | 2     | 2.2  | V                 |

| Undervoltage Lockout<br>Hysteresis         | UVLO <sub>HYST</sub>                   | VIN falling                                                                |                               |          | 200   |      | mV                |

|                                            |                                        | V <sub>IN</sub> =(V <sub>OUT(NOM)</sub>                                    | +1V) to 5.5V                  |          |       |      |                   |

| Output Voltage Accuracy                    | riangleVout                            | Iout=100mA to                                                              | I <sub>OUT</sub> =100mA to 1A |          |       | 3%   | Vouт              |

|                                            |                                        | V <sub>IN</sub> ≥2.2V                                                      |                               | <u> </u> |       |      |                   |

| Line Regulation                            | $\triangle V_{OUT} \triangle V_{IN}$   | VIN=(VOUT(NOM)                                                             | +1V) to 5.5V                  |          | 150   |      | μV/V              |

|                                            |                                        | I <sub>OUT</sub> =100mA                                                    |                               |          |       |      |                   |

| Load Regulation                            | $\triangle V_{OUT}/\triangle I_{LAOD}$ | I <sub>OUT</sub> =100mA to                                                 | 1A                            |          | 2     |      | μV/mA             |

| Load Current                               | Iload                                  |                                                                            |                               | 0        |       | 1    | Α                 |

| Maximum Output Current                     | ILOAD_MAX                              |                                                                            |                               | 1        |       |      | Α                 |

| Ground Current                             | ΙQ                                     | I <sub>OUT</sub> =1mA                                                      |                               |          | 350   |      | μA                |

| Cround Current                             | iq                                     | I <sub>OUT</sub> =1A                                                       |                               |          | 700   | 1200 | μπ                |

| Shutdown Current (I <sub>GND</sub> )       | ls                                     | V <sub>EN</sub> =0.4V, R <sub>LOAD</sub> =1kΩ                              |                               |          |       | 2.5  | μΑ                |

|                                            |                                        | V <sub>IN</sub> ≥2.2V, I <sub>OUT</sub> =500mA                             |                               |          |       | 100  | mV                |

| Dropout Voltage <sup>5)</sup>              | V <sub>DO</sub>                        | V <sub>IN</sub> ≥2.5V, I <sub>OUT</sub> =750mA                             |                               |          |       | 150  |                   |

|                                            |                                        | V <sub>IN</sub> ≥2.5V, I <sub>OUT</sub> =1A                                |                               |          |       | 200  |                   |

| Current Limit                              | IcL                                    | T <sub>A</sub> =25°C                                                       |                               | 1.1      | 1.5   | 2    | Α                 |

| Feedback Pin Current                       | I <sub>FB</sub>                        | V <sub>IN</sub> =5.5V, V <sub>FB</sub> =0.8V                               |                               |          |       | 1    | μA                |

|                                            | PSRR                                   | V <sub>IN</sub> =4.3V<br>V <sub>OUT</sub> =3.3V<br>I <sub>OUT</sub> =750mA | f=100Hz                       |          | 70    |      | dB                |

| D 0 1 D : ::                               |                                        |                                                                            | f=1kHz                        |          | 78    |      |                   |

| Power-Supply Rejection Ratio <sup>6)</sup> |                                        |                                                                            | f=10kHz                       |          | 70    |      |                   |

| Kalio <sup>-7</sup>                        |                                        |                                                                            | f=100kHz                      |          | 42    |      |                   |

|                                            |                                        |                                                                            | f=1MHz                        |          | 30    |      |                   |

|                                            |                                        | BW=100Hz to                                                                | 100kHz                        |          |       |      |                   |

| Output Noise Voltage <sup>6)</sup>         | V <sub>NO</sub>                        | $V_{IN}=3.8V$ , $V_{OUT}=3.3V$                                             |                               |          | 35.6  |      | μV <sub>RMS</sub> |

|                                            |                                        | I <sub>OUT</sub> =100mA,C <sub>NR</sub> =C <sub>FF</sub> =470nF            |                               |          |       |      |                   |

| High Input Threshold                       | VENH                                   | V <sub>IN</sub> =2.2V to 5.5V, EN rising                                   |                               | 1.2      |       |      | V                 |

| Low Input Threshold                        | V <sub>ENL</sub>                       | V <sub>IN</sub> =2.2V to 5.5V, EN falling                                  |                               |          |       | 0.4  | V                 |

| EN Lookage Correct                         | len_lkg                                | V <sub>EN</sub> =5.5V, V <sub>IN</sub> =5.5V                               |                               |          |       | 1    | μA                |

| EN Leakage Current                         |                                        | V <sub>EN</sub> =0V, V <sub>IN</sub> =5.5V                                 |                               |          | 0.001 |      |                   |

|                                            |                                        | V <sub>OUT(NOM)</sub> =3.3V,                                               |                               |          |       |      |                   |

| Rising Time                                | $T_R$                                  | Vout=0%~90%Vout(NOM),                                                      |                               |          | 33    |      | ms                |

|                                            |                                        | $C_{OUT}=10\mu F$ , $R_{LOAD}=3.3$ kohm,                                   |                               |          |       |      |                   |

$V_{IN}=V_{OUT(NOM)}+0.5V$  or 2.2V,  $V_{EN}=2V$ ,  $I_{OUT}=1$ mA,  $C_{IN}=10\mu$ F,  $C_{OUT}=10\mu$ F,  $C_{NR}=10$ nF,  $T_{J}=-40$  °C to 125 °C, Unless otherwise stated.

| Item                                      | Symbol                | Conditions             | Min. | Тур. | Max. | Unit |

|-------------------------------------------|-----------------------|------------------------|------|------|------|------|

|                                           |                       | C <sub>NR</sub> =470nF |      |      |      |      |

| Thermal Shutdown <sup>6)</sup>            | T <sub>TSD</sub>      |                        |      | 160  |      | °C   |

| Thermal Shutdown Hysteresis <sup>6)</sup> | T <sub>TSD_HYST</sub> |                        |      | 20   |      | °C   |

#### Note:

- 5) Dropout voltage is the voltage difference between input and output at which the output voltage drops to 100mV below its nominal value.

- 6) Guaranteed by design.

## **PIN DESCRIPTION**

| Pin<br>DFN3X3-8 | Name | Description                                                                         |  |  |

|-----------------|------|-------------------------------------------------------------------------------------|--|--|

| 1               | VOUT | Output of the regulator A 4 7uE or larger output conneiter is recommended           |  |  |

| 2               | VOOT | Output of the regulator. A 4.7µF or larger output capacitor is recommended          |  |  |

| 3               | FB   | Feedback pin. Connected to error amplifier. The FB reference voltage is 0.8V        |  |  |

| 4               | GND  | Ground                                                                              |  |  |

|                 |      | Enable pin. Active high. Driving this pin to logic high enables the device; driving |  |  |

| 5               | EN   | this pin to logic low disables the device. If enable functionality is not required, |  |  |

|                 |      | this pin must be connected to VIN.                                                  |  |  |

|                 |      | Noise-reduction and soft-start pin. Connecting an external capacitor between        |  |  |

|                 |      | this pin and ground reduces reference voltage noise and also enables the            |  |  |

| 6 NR            |      | soft-start function. Although not required, a 10nF or larger capacitor is           |  |  |

|                 |      | recommended to be connected from NR/SS to GND (as close to the pin as               |  |  |

|                 |      | possible) to maximize ac performance.                                               |  |  |

| 7               |      | Input supply voltage pin. A 2.2µF or larger ceramic capacitor from IN to ground     |  |  |

| 8               | VIN  | is required to reduce the impedance of the input supply. Place the input            |  |  |

| 0               |      | capacitor as close to the input as possible.                                        |  |  |

| Evposed Red     |      | The exposed pad should be connected to a large ground plane to maximize             |  |  |

| Exposed Pad     | -    | thermal performance.                                                                |  |  |

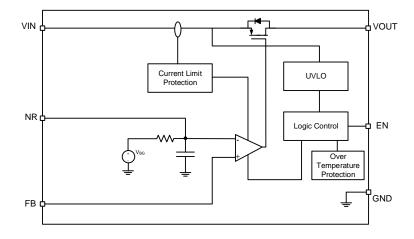

## **BLOCK DIAGRAM**

#### TYPICAL PERFORMANCE CHARACTERISTICS

At  $V_{Onom} = 3.3 \text{ V}$ ,  $V_{IN} = V_{Onom} + 0.5 \text{ V}$  or 2.2 V (whichever is greater),  $I_{O} = 100 \text{ mA}$ ,  $V_{(EN)} = V_{IN}$ ,  $C_{(IN)} = 2.2 \mu F$ ,  $C_{(OUT)} = 4.7 \mu F$ ,

and  $C_{(NR)}$  = 0.01  $\mu F$ ,  $T_A$ =25  $^{\circ}C$ , unless otherwise noted

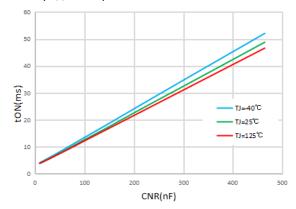

Turn-on time(EN high to 90%Vout) vs.CNR

$V_{IN}$ =4.3V, $V_{OUT}$ =3.3V,  $C_{FF}$ =NC

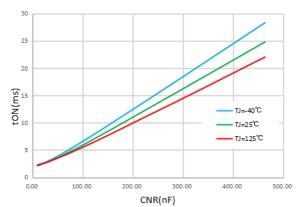

Rising time (10%Vout to 90%Vout) vs.CNR  $\,$

$V_{IN}$ =4.3V, $V_{OUT}$ =3.3V,  $C_{FF}$ =10nF

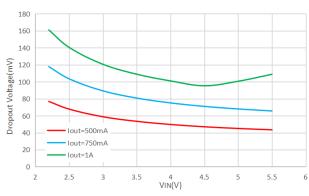

#### Dropout voltage vs Input voltage

T<sub>A</sub>=25 ℃

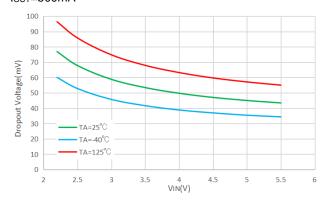

Dropout voltage vs Load current

I<sub>OUT</sub>=500mA

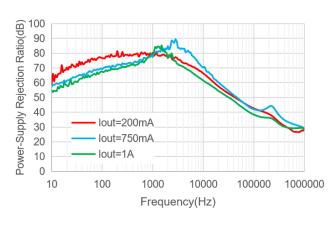

#### **PSRR vs Frequency**

$V_{\text{OUT}} = V_{\text{IN}} - 1V, C_{\text{IN}} = 0F, C_{\text{OUT}} = 10 \mu F, C_{\text{NR}} = 470 nF, C_{\text{FF}} = 470 nF$

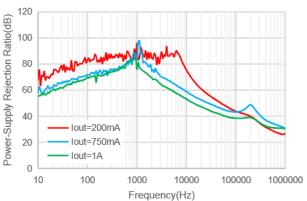

PSRR vs Frequency

$V_{OUT}=V_{IN}-0.5V$ ,  $C_{IN}=0F$ ,  $C_{OUT}=10\mu F$ ,  $C_{NR}=470nF$ ,  $C_{FF}=470nF$

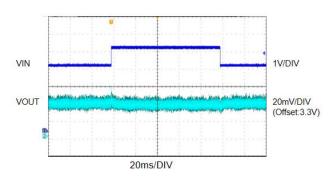

# Line transient

## $\ensuremath{\text{V}_{\text{IN}}}\text{=}3.8\ensuremath{\text{V}}$ to 4.8V to 3.8V, $\ensuremath{\text{I}_{\text{OUT}}}\text{=}500\ensuremath{\text{mA}}$

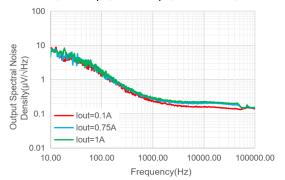

#### Output spectral noise density vs Frequency

$V_{\text{OUT}} = V_{\text{IN}} - 0.5 V, C_{\text{IN}} = 10 \mu F, C_{\text{OUT}} = 10 \mu F, C_{\text{NR}} = 470 nF, C_{\text{FF}} = 470 nF$

#### **FUNCTIONAL DESCRIPTION**

The JWQ7821 is a low noise, low quiescent current linear regulator. The input voltage range is from 2.2V to 5.5V, and the output current is up to 1A. The minimum required output capacitance for stable operation is 4.7µF effective capacitance after consideration of the temperature and voltage coefficient of the capacitor.

#### **Output Transistor**

The JWQ7821 builds in a P-MOSFET output transistor which provides a low switch-on resistance for low dropout voltage applications.

#### **Error Amplifier**

The Error Amplifier (EA) compares the internal reference voltage  $V_{\text{REF}}$  with the output feedback voltage  $V_{\text{FB}}$  through the internal divider. Output of the error amplifier (EA) is used to control the gate voltage of P-MOSFET and ensures that the device provides good line and load regulation at output voltage.

#### **Enable**

The device is active when EN pin is set to high. For proper operation, this pin must be terminated and must not be left floating. With EN pin set to low, the device enters shutdown mode with less than 1uA current consumption.

#### **Current Limit Protection**

JWQ7821 provides current limit function to prevent the device from damages during the over load or shorted-circuit condition. The current is detected by a sensing transistor, which monitors and controls the pass transistor's gate voltage, limiting the output current to 1.1A (TYP.). The PMOS pass transistor dissipates ( $V_{\text{IN}} - V_{\text{OUT}}$ ) ×  $I_{\text{LIMIT}}$  until thermal shutdown is triggered and the device turns off. When the device cools, the internal thermal shutdown circuit turns the device back on. If the fault condition continues, the device cycles between current limit and thermal shutdown.

#### **Low Output Noise**

Any internal noise at the JWQ7821 reference voltage is reduced by a first order low-pass RC filter before it is passed to the output buffer stage. The low-pass RC filter has a -3dB cut-off frequency of approximate 0.1Hz.

#### Transient Response

As with any regulator, increasing the size of the output capacitor reduces overshoot and undershoot magnitude but increases the duration of the transient response. Using a larger noise-reduction capacitor  $C_{NR}$ , bypass capacitor  $C_{FF}$ , or both types of capacitors can improve line transient performance

#### **Thermal Protection**

When the temperature of the JWQ7821 rises above  $T_{TSD}$ , it is forced into thermal shut-down. When the junction temperature cools to approximately  $T_{TSD}$ - $T_{TSD\_HYST}$  the output circuitry is again enabled.

#### APPLACATION INFORMATION

The JWQ7821 is a new generation LDO regulators that use innovative circuitry to achieve wide bandwidth and high loop gain, resulting in extremely high PSRR (over a 1-MHz range) at very low headroom (VIN – VOUT). A noise reduction capacitor (CNR) at the NR pin and a bypass capacitor (CFF) bypass noise generated by the bandgap reference to improve PSRR, while a quick-start circuit fast-charges the noise reduction capacitor. This regulator offers sub-bandgap output voltages, current limit, and thermal protection, and is fully specified from –40°C to 125°C.

#### **Dropout Voltage**

The JWQ7821 uses a PMOS pass transistor to achieve low dropout. When (VIN – VOUT) is less than the dropout voltage (VDO), the PMOS pass device is in its linear region of operation and the input-to-output resistance is the RDS(ON) of the PMOS pass element. VDO scales approximately with output current because the PMOS device in dropout behaves the same way as a resistor.

#### Input and Output Capacitor Selection

The JWQ7821 is designed to support low ESR (Equivalent Series Resistance) ceramic capacitors. It is recommended to use ceramic capacitors with X7R, X5R, and COG-rated ceramic capacitors to get good capacitive stability across different temperatures.

A 4.7 $\mu$ F or greater output ceramic capacitor is suggested to ensure stability. Input capacitance is selected to minimize transient input drop during load current steps. For general applications, an input capacitor of at least 2.2 $\mu$ F is highly recommended for minimal input impedance. If the trace inductance between the

JWQ7821 input pin and power supply is high, a fast load transient can cause VIN voltage level ringing above the absolute maximum voltage rating which damages the device. Adding more input capacitors is available to restrict the ringing and keep it below the device absolute maximum ratings.

#### **Output Voltage Setting**

For the JWQ7821, the voltage on the FB pin sets the output voltage and is determined by the values of R1 and R2. The values of R1 and R2 can be calculated for any voltage using the formula given in Equation:

$$Vout = \frac{R1 + R2}{R2} \times 0.8$$

Using lower values for R1 and R2 is recommended to reduces the noise injected from the FB pin. Note that R1 is connected from VOUT pin to FB pin, and R2 is connected from FB to GND.

#### **Output Noise**

In general, the dominant noise source is from the internal bandgap for most LDOs. If a noise reduction capacitor (CNR) is used with the JWQ7821, the bandgap does not contribute significantly to noise. Instead, noise is dominated by the output resistor divider and the error amplifier input. If a bypass capacitor (CFF) across the high-side feedback resistor (R1) is used with the JWQ7821 in addition to CNR, noise from these other sources can also be significantly reduced.

#### **Adjustable Rise Time**

The rise time of JWQ7821 can be adjusted individually by CFF(connected between VOUT

pin and FB pin) and CNR(connected between NR/SS and GND pins). The approximate rise time of VOUT measured on a typical device at VOUT = 3.3V is shown in table 1.

Table 1:

|                                       | Rising time,Tr(ms)10%-90% of VOUT, |      |           |  |  |

|---------------------------------------|------------------------------------|------|-----------|--|--|

| CND                                   | COUT=4.7µF,CIN=2.2µF,              |      |           |  |  |

|                                       | CNR Typical values at 25°C,        |      |           |  |  |

| (nF) VIN=4.3V,VOUT=3.3V,RLoad=3.3kohr |                                    |      |           |  |  |

|                                       | CFF=NC CFF=10nF CFF=4              |      | CFF=470nF |  |  |

| 0                                     | 2.1                                | 2.24 | 33.7      |  |  |

| 10                                    | 2.37                               | 2.58 | 34.4      |  |  |

| 100                                   | 6.8                                | 7.24 | 37.8      |  |  |

| 470                                   | 30.3                               | 30.6 | 53.8      |  |  |

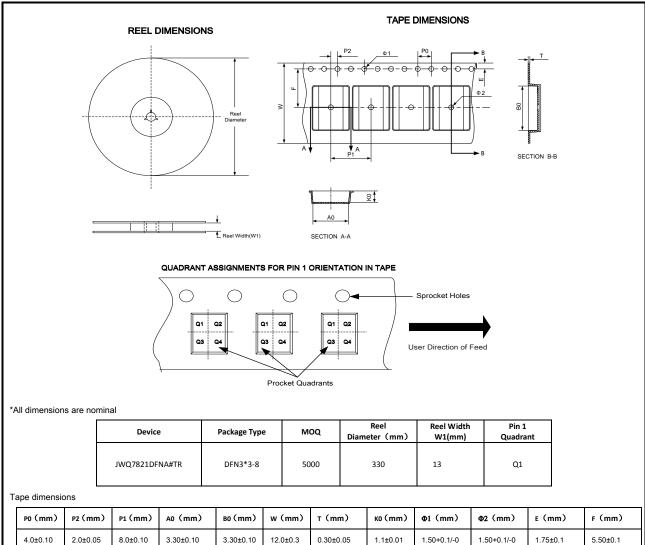

### TAPE AND REEL INFORMATION

TAPE AND REEL BOX DIMENSIONS

| Device         | Package Type | MOQ  | Length(mm) | Width(mm) | Height(mm) |

|----------------|--------------|------|------------|-----------|------------|

| JWQ7821DFNA#TR | DFN3*3-8     | 5000 | 340        | 358       | 50         |

### **PACKAGE OUTLINE**

#### IMPORTANT NOTICE

Joulwatt Technology Co.,Ltd reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Co.,Ltd does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- JOULWATT TECHNOLOGY CO.,LTD PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, SAFETY INFORMATION AND OTHER RESOURCES, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

Copyright © 2022 JoulWatt

All rights are reserved by Joulwatt Technology Co.,Ltd