## **Document Title**

512Kx36-bit, 1Mx18-bit QDR<sup>™</sup> SRAM

## **Revision History**

| <u>Rev. No.</u> | History                                                             |                                                                                           |                                                                                 |              |                                 |                    | Draft Date     | <u>Remark</u> |

|-----------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------|---------------------------------|--------------------|----------------|---------------|

| 0.0             | 1. Initial d                                                        | ocument.                                                                                  |                                                                                 |              |                                 |                    | April 30, 2001 | Advance       |

| 0.1             | W (4<br><u>R (8</u> /<br>BWo                                        | 3,4 PIN NAI<br>A) : from Re<br>A) : <u>from</u> W<br>(7B),BW1(7A<br>from Re<br>27 STATE D | ead Control F<br>rit <u>e C</u> ontrol <u>F</u><br>a),BW2(5A),B<br>ad Control F |              | May, 13, 2001                   | Advance            |                |               |

| 0.2             | BW2                                                                 |                                                                                           | RUTH TABL<br>s for  W <u>R</u> ITE<br>YTEs( K↑ )                                |              | May, 26, 2001<br>June, 11, 2001 | Advance<br>Advance |                |               |

| 0.3             | 1. 1.8V I/C<br>1) Page<br>2) Page<br>3) Page<br>4) Page<br>2. Amend | D supply volt<br>2 FEATURE<br>3,4 PIN NAI<br>10, OPERA<br>11 AC TES                       | age addition<br>ES<br>ME VDDQ<br>TING CONT<br>T CONTITIC                        |              |                                 |                    |                |               |

| 0.4             | 1. lcc, lsb<br>2. 1.8V Vo                                           | addition<br>ddq addition                                                                  |                                                                                 |              |                                 |                    | Sep, 03, 2001  | Advance       |

| 0.5             | 1. Reserve                                                          | ed pin for hig                                                                            | gh density na                                                                   | ame change f | from NC to                      | Vss/SA             | Nov, 30, 2001  | Preliminary   |

| 0.6             | 1. Release                                                          | e lcc.                                                                                    |                                                                                 |              |                                 |                    | May, 22. 2002  | Preliminary   |

|                 | part #                                                              | x                                                                                         | 18                                                                              | x            | 36                              | _                  |                |               |

|                 |                                                                     | From                                                                                      | То                                                                              | From         | То                              | _                  |                |               |

|                 | -20                                                                 | 500                                                                                       | 520                                                                             | 530          | 600                             | _                  |                |               |

|                 | -16<br>-13                                                          | -                                                                                         | -                                                                               | 490          | 550<br>490                      | _                  |                |               |

|                 | -13                                                                 | -                                                                                         | -                                                                               | 460          | 490                             | _                  |                |               |

| 1.0             |                                                                     | PEC release                                                                               |                                                                                 |              |                                 |                    | July, 03. 2002 | Final         |

2. Modify thermal resistance

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

## 512Kx36-bit, 1Mx18-bit QDR™ SRAM

#### FEATURES

- 2.5V+0.1V/-0.1V Power Supply.

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/-0.1V for 1.8V I/O.

- Separate independent read and write data ports with concurrent read and write operation.

- HSTL I/O.

- Full data coherency, providing most current data .

- Synchronous pipeline read with self timed late write.

- Registered address, control and data input/output.

- DDR(Double Data Rate) Interface on read and write ports.

- Fixed 4-bit burst for both read and write operation.

- Clock-stop supports to reduce current.

- Two input clocks(K and K) for accurate DDR timing at clock rising edges only.

- Two input clocks for output data(C and C) to minimize clock-skew and flight-time mismatches.

- Single address bus.

- Byte writable function.

- Sepatate read/write control  $pin(\overline{R} \text{ and } \overline{W})$

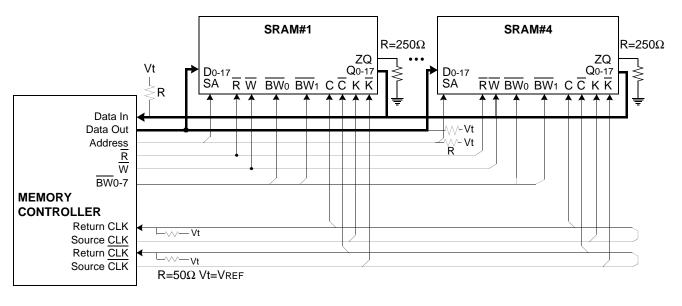

- Simple depth expansion with no data contention.

- Programmable output impedance.

- JTAG 1149.1 compatible test access port.

- 165FBGA(11x15 ball aray FBGA) with body size of 13x15mm

| Organization | Part<br>Number  | Cycle<br>Time | Access<br>Time | Unit |

|--------------|-----------------|---------------|----------------|------|

|              | K7Q163654A-FC20 | 5.0           | 2.2            | ns   |

| X36          | K7Q163654A-FC16 | 6.0           | 2.5            | ns   |

| 7.50         | K7Q163654A-FC13 | 7.5           | 3.0            | ns   |

|              | K7Q163654A-FC10 | 10.0          | 3.0            | ns   |

|              | K7Q161854A-FC20 | 5.0           | 2.2            | ns   |

| X18          | K7Q161854A-FC16 | 6.0           | 2.5            | ns   |

| X10          | K7Q161854A-FC13 | 7.5           | 3.0            | ns   |

|              | K7Q161854A-FC10 | 10.0          | 3.0            | ns   |

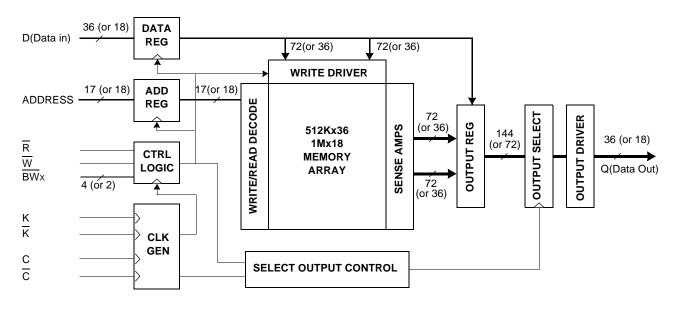

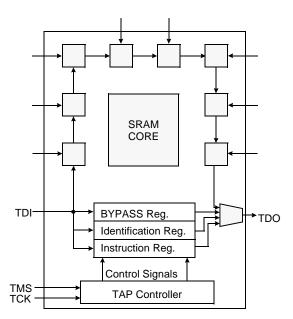

## FUNCTIONAL BLOCK DIAGRAM

Notes: 1. Numbers in ( ) are for x18 device.

QDR SRAM and Quad Data Rate comprise a new family of products developed by Cypress, Hitachi, IDT, Micron, NEC and Samsung technology.

#### PIN CONFIGURATIONS(TOP VIEW) K7Q161854A(1Mx18)

|   | 1   | 2       | 3      | 4    | 5   | 6   | 7               | 8    | 9    | 10      | 11  |

|---|-----|---------|--------|------|-----|-----|-----------------|------|------|---------|-----|

| Α | NC  | Vss/SA* | NC/SA* | W    | BW1 | ĸ   | NC              | R    | SA   | Vss/SA* | NC  |

| В | NC  | Q9      | D9     | SA   | NC  | К   | BW <sub>0</sub> | SA   | NC   | NC      | Q8  |

| с | NC  | NC      | D10    | Vss  | SA  | NC  | SA              | Vss  | NC   | Q7      | D8  |

| D | NC  | D11     | Q10    | Vss  | Vss | Vss | Vss             | Vss  | NC   | NC      | D7  |

| Е | NC  | NC      | Q11    | Vddq | Vss | Vss | Vss             | Vddq | NC   | D6      | Q6  |

| F | NC  | Q12     | D12    | Vddq | Vdd | Vss | Vdd             | Vddq | NC   | NC      | Q5  |

| G | NC  | D13     | Q13    | Vddq | Vdd | Vss | Vdd             | Vddq | NC   | NC      | D5  |

| н | NC  | Vref    | Vddq   | Vddq | Vdd | Vss | Vdd             | Vddq | Vddq | Vref    | ZQ  |

| J | NC  | NC      | D14    | Vddq | Vdd | Vss | Vdd             | Vddq | NC   | Q4      | D4  |

| к | NC  | NC      | Q14    | Vddq | Vdd | Vss | Vdd             | Vddq | NC   | D3      | Q3  |

| L | NC  | Q15     | D15    | Vddq | Vss | Vss | Vss             | Vddq | NC   | NC      | Q2  |

| м | NC  | NC      | D16    | Vss  | Vss | Vss | Vss             | Vss  | NC   | Q1      | D2  |

| N | NC  | D17     | Q16    | Vss  | SA  | SA  | SA              | Vss  | NC   | NC      | D1  |

| Р | NC  | NC      | Q17    | SA   | SA  | С   | SA              | SA   | NC   | D0      | Q0  |

| R | TDO | тск     | SA     | SA   | SA  | C   | SA              | SA   | SA   | TMS     | TDI |

Notes: 1.\* Checked pins are reserved for higher density address, i.e. 3A for 32Mb, 10A for 64Mb and 2A for 128Mb. 2. BW₀ controls write to D0:D8 and BW₁ controls write to D9:D17.

#### **PIN NAME**

| SYMBOL   | PIN NUMBERS                                                                                                                                                                                                            | DESCRIPTION                        | NOTES |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------|

| К, К     | 6B, 6A                                                                                                                                                                                                                 | Input Clock                        |       |

| C, C     | 6P, 6R                                                                                                                                                                                                                 | Input Clocks for Output data       | 1     |

| SA       | 9A,4B,8B,5C,7C,5N-7N,4P,5P,7P,8P,3R-5R,7R-9R                                                                                                                                                                           | Address Inputs                     |       |

| D0-17    | 10P,11N,11M,10K,11J,11G,10E,11D,11C,3B,3C,2D,<br>3F,2G,3J,3L,3M,2N                                                                                                                                                     | Data Inputs                        |       |

| Q0-17    | 11P,10M,11L,11K,10J,11F,11E,10C,11B,2B,3D,3E,<br>2F,3G,3K,2L,3N,3P                                                                                                                                                     | Data Outputs                       |       |

| W        | 4A                                                                                                                                                                                                                     | Write Control                      |       |

| R        | 8A                                                                                                                                                                                                                     | Read Control                       |       |

| BW0, BW1 | 7B, 5A                                                                                                                                                                                                                 | Byte Write Control                 |       |

| Vref     | 2H,10H                                                                                                                                                                                                                 | Input Reference Voltage            |       |

| ZQ       | 11H                                                                                                                                                                                                                    | Output Driver Impedance Control    | 2     |

| Vdd      | 5F,7F,5G,7G,5H,7H,5J,7J,5K,7K                                                                                                                                                                                          | Power Supply ( 2.5V )              |       |

| Vddq     | 4E,8E,4F,8F,4G,8G,3H,4H,8H,9H,4J,8J,4K,8K,4L,8L                                                                                                                                                                        | Output Power Supply (1.5V or 1.8V) |       |

| Vss      | 2A,10A,4C,8C,4D-8D,5E-7E,<br>6F,6G,6H,6J,6K,5L-7L,4M-8M,4N,8N                                                                                                                                                          | Ground                             |       |

| TMS      | 10R                                                                                                                                                                                                                    | JTAG Test Mode Select              |       |

| TDI      | 11R                                                                                                                                                                                                                    | JTAG Test Data Input               |       |

| ТСК      | 2R                                                                                                                                                                                                                     | JTAG Test Clock                    |       |

| TDO      | 1R                                                                                                                                                                                                                     | JTAG Test Data Output              |       |

| NC       | 1A,3A,7A,11A,1B,5B,9B,10B,1C,2C,6C,9C,1D,9D,10D,         No Connect           1E,2E,9E,1F,9F,10F,1G,9G,10G,1H,1J,2J,9J,1K,2K,         No Connect           9J,1L,9L,10L,1M,2M,9M,1N,9N,10N,1P,2P,9P         No Connect |                                    | 3     |

**Notes:** 1. C,  $\overline{C}$ , K or  $\overline{K}$  cannot be set to VREF voltage.

2. When ZQ pin is directly connected to VDD output impedance is set to minimum value and it cannot be connected to ground or left unconnected. 3. Not connected to chip pad internally.

|   | 1   | 2       | 3      | 4    | 5               | 6   | 7               | 8    | 9      | 10      | 11  |

|---|-----|---------|--------|------|-----------------|-----|-----------------|------|--------|---------|-----|

| Α | NC  | Vss/SA* | NC/SA* | W    | BW <sub>2</sub> | ĸ   | BW <sub>1</sub> | R    | NC/SA* | Vss/SA* | NC  |

| В | Q27 | Q18     | D18    | SA   | BW3             | К   | BW <sub>0</sub> | SA   | D17    | Q17     | Q8  |

| С | D27 | Q28     | D19    | Vss  | SA              | NC  | SA              | Vss  | D16    | Q7      | D8  |

| D | D28 | D20     | Q19    | Vss  | Vss             | Vss | Vss             | Vss  | Q16    | D15     | D7  |

| Е | Q29 | D29     | Q20    | Vddq | Vss             | Vss | Vss             | Vddq | Q15    | D6      | Q6  |

| F | Q30 | Q21     | D21    | Vddq | Vdd             | Vss | Vdd             | Vddq | D14    | Q14     | Q5  |

| G | D30 | D22     | Q22    | Vddq | Vdd             | Vss | Vdd             | Vddq | Q13    | D13     | D5  |

| н | NC  | Vref    | Vddq   | Vddq | Vdd             | Vss | Vdd             | Vddq | Vddq   | Vref    | ZQ  |

| J | D31 | Q31     | D23    | Vddq | Vdd             | Vss | Vdd             | Vddq | D12    | Q4      | D4  |

| к | Q32 | D32     | Q23    | Vddq | Vdd             | Vss | Vdd             | Vddq | Q12    | D3      | Q3  |

| L | Q33 | Q24     | D24    | Vddq | Vss             | Vss | Vss             | Vddq | D11    | Q11     | Q2  |

| м | D33 | Q34     | D25    | Vss  | Vss             | Vss | Vss             | Vss  | D10    | Q1      | D2  |

| N | D34 | D26     | Q25    | Vss  | SA              | SA  | SA              | Vss  | Q10    | D9      | D1  |

| Р | Q35 | D35     | Q26    | SA   | SA              | С   | SA              | SA   | Q9     | D0      | Q0  |

| R | TDO | тск     | SA     | SA   | SA              | C   | SA              | SA   | SA     | TMS     | TDI |

Notes: 1. \* Checked pins are reserved for higher density address, i.e. <u>9A</u> for 32Mb, 3A for 64Mb, 10A for <u>128</u>Mb and 2A for 256Mb. 2. BW<sub>0</sub> controls write to D0:D8, BW<sub>1</sub> controls write to D9:D17, BW<sub>2</sub> controls write to D18:D26 and BW<sub>3</sub> controls write to D27:D35.

#### **PIN NAME**

| SYMBOL                                                                       | PIN NUMBERS                                                                                                                   | DESCRIPTION                                           | NOTES |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|

| К, К                                                                         | 6B, 6A                                                                                                                        | Input Clock                                           |       |

| C, C                                                                         | 6P, 6R                                                                                                                        | Input Clocks for Output data                          | 1     |

| SA                                                                           | 4B,8B,5C,7C,5N-7N,4P,5P,7P,8P,3R-5R,7R-9R                                                                                     | Address Inputs                                        |       |

| D0-35                                                                        | 10P,11N,11M,10K,11J,11G,10E,11D,11C,10N,9M,9L<br>9J,10G,9F,10D,9C,9B,3B,3C,2D,3F,2G,3J,3L,3M,2N<br>1C,1D,2E,1G,1J,2K,1M,1N,2P | G,9F,10D,9C,9B,3B,3C,2D,3F,2G,3J,3L,3M,2N Data Inputs |       |

| Q0-35                                                                        | 11P,10M,11L,11K,10J,11F,11E,10C,11B,9P,9N,10L<br>9K,9G,10F,9E,9D,10B,2B,3D,3E,2F,3G,3K,2L,3N<br>3P,1B,2C,1E,1F,2J,1K,1L,2M,1P | Data Outputs                                          |       |

| W                                                                            | 4A                                                                                                                            | Write Control Pin                                     |       |

| R                                                                            | 8A                                                                                                                            | Read Control Pin                                      |       |

| $\overline{BW}_{0}, \overline{BW}_{1}, \overline{BW}_{2}, \overline{BW}_{3}$ | 7B,7A,5A,5B                                                                                                                   | Byte Write Control Pin                                |       |

| Vref                                                                         | 2H,10H                                                                                                                        | Input Reference Voltage                               |       |

| ZQ                                                                           | 11H                                                                                                                           | Output Driver Impedance Control                       | 2     |

| Vdd                                                                          | 5F,7F,5G,7G,5H,7H,5J,7J,5K,7K                                                                                                 | Power Supply ( 2.5V )                                 |       |

| Vddq                                                                         | 4E,8E,4F,8F,4G,8G,3H,4H,8H,9H,4J,8J,4K,8K,4L,8L                                                                               | Output Power Supply( 1.5V or 1.8V )                   |       |

| Vss                                                                          | 2A,10A,4C,8C,4D-8D,5E-7E,<br>6F,6G,6H,6J,6K,5L-7L,                                                                            | Ground                                                |       |

| TMS                                                                          | 10R                                                                                                                           | JTAG Test Mode Select                                 |       |

| TDI                                                                          | 11R                                                                                                                           | JTAG Test Data Input                                  |       |

| TCK                                                                          | 2R                                                                                                                            | JTAG Test Clock                                       |       |

| TDO                                                                          | 1R                                                                                                                            | JTAG Test Data Output                                 |       |

| NC                                                                           | 1A,3A,9A,11A,6C,1H                                                                                                            | No Connect                                            | 3     |

Notes: 1. C, C, K or K cannot be set to VREF voltage. 2. When ZQ pin is directly connected to VDD output impedance is set to minimum value and it cannot be connected to ground or left unconnected. 3. Not connected to chip pad internally.

#### **GENERAL DESCRIPTION**

The K7Q163654A and K7Q161854A are 18,874,368-bits QDR(Quad Data Rate) Synchronous Pipelined Burst SRAMs. They are organized as 524,288 words by 36bits for K7Q163654A and 1,048,576 words by 18 bits for K7Q161854A.

The QDR operation is possible by supporting DDR read and write operations through separate data output and input ports with the same cycle. Memory bandwidth is maxmized as data can be transfered into sram on every rising edge of K and  $\overline{K}$ , and transfered out of sram on every rising edge of C and  $\overline{C}$ . And totally independent read and write ports eliminate the need for high speed bus turn around.

Address for read and write are latched on alternate rising edges of the input clock K. Data inputs, and all control signals are synchronized to the input clock ( K or  $\overline{K}$  ). Normally data outputs are synchronized to output clocks ( C and  $\overline{C}$  ), but when C and  $\overline{C}$  are tied high, the data outputs are synchronized to the input clocks ( K and  $\overline{K}$  ). Common address bus is used to access address both for read and write operations.

The internal burst counter is fiexd to 4-bit sequential for both read and write operations, reguiring tow full clock bus cycles. Any request that attempts to interrupt a burst operation in progress is ignored. Synchronous pipeline read and late write enable high speed operations. Simple depth expansion is accomplished by using R and W for port selection. Byte write operation is supported with BWo and BW1 (BW2 and BW3) pins. IEEE 1149.1 serial boundary scan (JTAG) simplifies monitoring package pads attachment status with system.

The K7Q163654A and K7Q161854A are implemented with SAMSUNG's high performance 6T CMOS technology and is available in 165pin FBGA packages. Multiple power and ground pins minimize ground bounce.

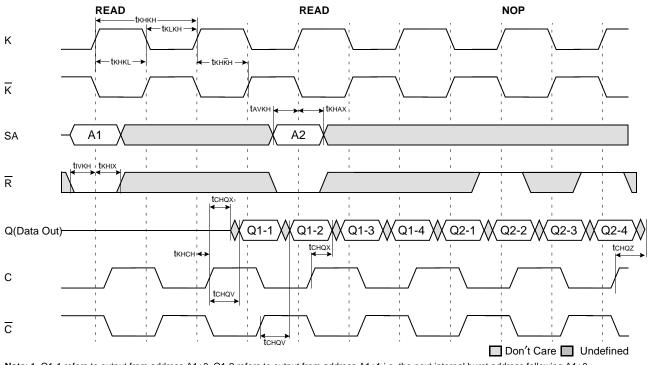

#### **Read Operations**

Read cycles are initiated by activating  $\overline{R}$  at the rising edge of the positive input clock K. Address is presented and stored in the read address register synchronized with K clock.

For 4-bit burst DDR operation, it will access four 36-bit or 18-bit data words with each read command. The first pipelined data is transfered out of the device triggered by C clock following next K clock rising edge. Next burst data is triggered by the rising edge of following  $\overline{C}$  clock rising edge. The process continues until all four data are transfered.

Continuous read operations are initiated with K clock rising edge. And pipelined data are transferred out of device on every rising edge of both C and  $\overline{C}$  clocks. In case C and  $\overline{C}$  tied to high, output data are triggered by K and K instead of C and  $\overline{C}$ .

When the  $\overline{R}$  is disabled after a read operation, the K7Q163654A and K7Q161854A will first complete burst read operation before entering into deselect mode at the next K clock rising edge. Then output drivers disabled automatically to high impedance state.

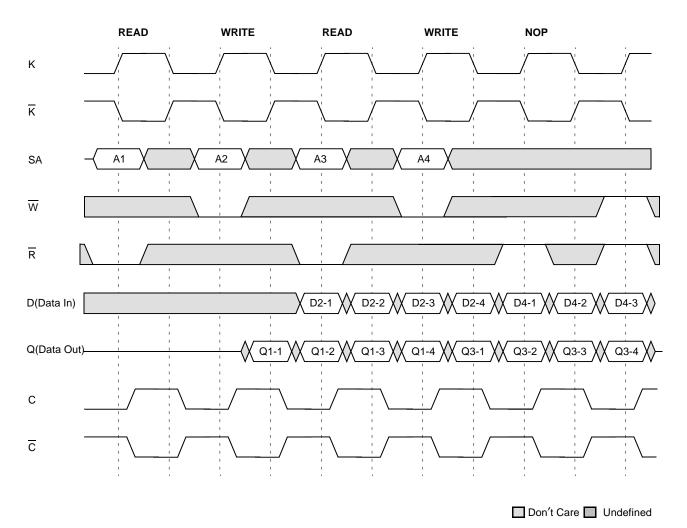

#### Write Operations

Write cycles are initiated by activating  $\overline{W}$  at the rising edge of the positive input clock K. Address is presented and stored in the write address register synchronized with K clock.

For 4-bit burst DDR operation, it will write four 36-bit or 18-bit data words with each write command. The first "late" data is transfered and registered in to the device synchronous with next K clock rising edge. Next burst data is transfered and registered synchronous with following  $\overline{K}$  clock rising edge. The process continues until all four data are transfered and registered.

Continuous write operations are initated with K rising edge. And "late writed" data is presented to the device on every rising edge of both K and  $\overline{K}$  clocks.

The device disregards input data presented on the same cycle  $\overline{W}$  disabled. When the  $\overline{W}$  is disabled after a read operation, the K7Q163654A and K7Q161854A will first complete burst read operation before entering into deselect mode at the next K clock rising edge.

The K7Q163654A and K7Q161854A support byte write operations. With activating  $\overline{BW_0}$  or  $\overline{BW_1}$  ( $\overline{BW_2}$  or  $\overline{BW_3}$ ) in write cycle, only one byte of input data is presented. In K7Q161854A,  $\overline{BW_0}$  controls write operation to D0:D8,  $\overline{BW_1}$  controls write operation to D9:D17. And in K7Q163654A  $\overline{BW_2}$  controls write operation to D18:D26,  $\overline{BW_3}$  controls write operation to D27:D35.

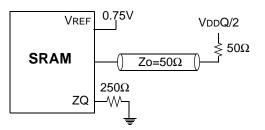

#### Programmable Impedance Output Buffer Operation

The designer can program the SRAM's output buffer impedance by terminating the ZQ pin to Vss through a precision resistor(RQ). The value of RQ (within 15%) is five times the output impedance desired.

For example,  $250\Omega$  resistor will give an output impedance of  $50\Omega$ . Impedance updates occur early in cycles that do not activate the outputs, such as deselect cycles. In all cases impedance updates are transparent to the user and do not produce access time "push-outs" or other anomalous behavior in the SRAM.

There are no power up requirements for the SRAM. However, to guarantee optimum output driver impedance after power up, the SRAM needs 1024 non-read cycles.

## **Single Clock Mode**

The K7Q163654A and K7Q161854A can be used with the single clock pair K and K. In this mode, C and  $\overline{C}$  must be tied high during power up and this single clock pair control both the input and output registers. C and  $\overline{C}$  cannot be tied high during operation. System flight time and clock skew could not be compensated in single clock mode.

#### **Depth Expansion**

Separate input and output ports enables easy depth expansion. Each port can be selected and deselected independently and read and write operation do not affect each other. Before chip deselected, all read and write pending operations are completed.

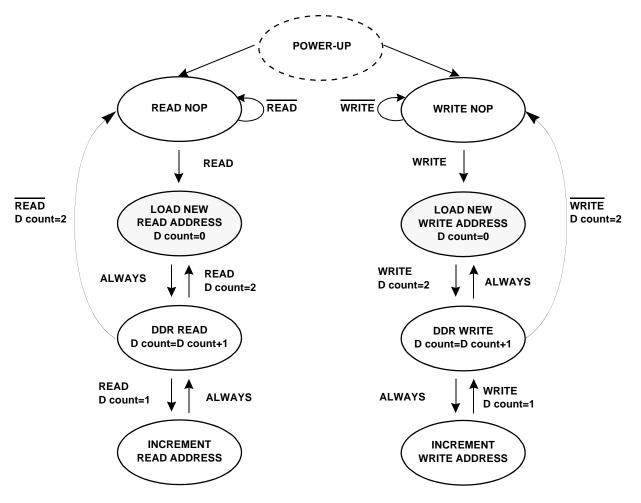

#### STATE DIAGRAM

Notes: 1. Internal burst counter is fixed as 2-bit linear, i.e. when first address is A0+0, next internal burst address is A0+1.

2. "READ" refers to read active status with  $\overline{R}$ =Low, "READ" refers to read inactive status with  $\overline{R}$ =high. "WRITE" and "WRITE" are the same case. 3. Read and write state machine can be active simultaneously.

4. State machine control timing sequence is controlled by K.

## **TRUTH TABLES**

#### SYNCHRONOUS TRUTH TABLE

| к       | R | w | D                 |                   |                  |                   |                   | C                         | 2<br>A            |                   | OPERATION    |  |

|---------|---|---|-------------------|-------------------|------------------|-------------------|-------------------|---------------------------|-------------------|-------------------|--------------|--|

| ĸ       | n |   | D(A1)             | D(A2)             | D(A3)            | D(A4)             | Q(A1)             | Q(A2)                     | Q(A3)             | Q(A4)             | OFERATION    |  |

| Stopped | х | х | Previous<br>state | Previous<br>state | Previous state   | Previous<br>state | Previous state    | Previous<br>state         | Previous state    | Previous<br>state | Clock Stop   |  |

| ↑       | Н | Н | Х                 | Х                 | Х                | Х                 | High-Z            | High-Z                    | High-Z            | High-Z            | No Operation |  |

| Ŷ       | L | х | х                 | х                 | х                | х                 | Douт<br>at C(t+1) | <u>D</u> о∪т<br>at C(t+1) | Dout<br>at C(t+2) | Do∪⊤<br>at C(t+2) | Read         |  |

| Ŷ       | Н | L | Din<br>at K(t+1)  | Din<br>at K(t+1)  | Din<br>at K(t+2) | Din<br>at K(t+2)  | х                 | х                         | х                 | х                 | Write        |  |

Notes: 1. X means "Don't Care".

2. The rising edge of clock is symbolized by (  $\uparrow$  ).

3. Before enter into clock stop status, all pending read and write operations will be completed.

#### WRITE TRUTH TABLE(x18)

| к          | ĸ          | w | BW <sub>0</sub> | BW1 | OPERATION                                           |

|------------|------------|---|-----------------|-----|-----------------------------------------------------|

| $\uparrow$ |            | н | х               | х   | READ/NOP                                            |

|            | $\uparrow$ | Н | Х               | х   | READ/NOP                                            |

| $\uparrow$ |            | L | L               | L   | WRITE ALL BYTEs ( K <sup>↑</sup> )                  |

|            | $\uparrow$ | L | L               | L   | WRITE ALL BYTES ( $\overline{\mathbf{K}}$ )         |

| $\uparrow$ |            | L | L               | Н   | WRITE BYTE 0 ( K <sup>↑</sup> )                     |

|            | $\uparrow$ | L | L               | Н   | WRITE BYTE 0 ( $\overline{\mathbf{K}}^{\uparrow}$ ) |

| $\uparrow$ |            | L | н               | L   | WRITE BYTE 1 ( K↑ )                                 |

|            | $\uparrow$ | L | н               | L   | WRITE BYTE 1 ( $\overline{\mathbf{K}}$ )            |

| $\uparrow$ |            | L | н               | Н   | WRITE NOTHING ( K↑ )                                |

|            | ↑          | L | Н               | Н   | WRITE NOTHING ( $\overline{\mathbf{K}}$ )           |

Notes: 1. X means "Don't Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(  $\uparrow$  ).

#### WRITE TRUTH TABLE(x36)

| к          | ĸ | w | BW <sub>0</sub> | BW1 | BW <sub>2</sub> | BW <sub>3</sub> | OPERATION                                            |

|------------|---|---|-----------------|-----|-----------------|-----------------|------------------------------------------------------|

| 1          |   | Н | Х               | Х   | Х               | Х               | READ/NOP                                             |

|            | Ŷ | Н | Х               | Х   | Х               | Х               | READ/NOP                                             |

| ↑          |   | L | L               | L   | L               | L               | WRITE ALL BYTEs ( K <sup>↑</sup> )                   |

|            | Ŷ | L | L               | L   | L               | L               | WRITE ALL BYTES ( $\overline{K}^{\uparrow}$ )        |

| $\uparrow$ |   | L | L               | Н   | Н               | Н               | WRITE BYTE 0 ( K <sup>↑</sup> )                      |

|            | Ŷ | L | L               | Н   | Н               | Н               | WRITE BYTE 0 ( $\overline{K}\uparrow$ )              |

| $\uparrow$ |   | L | н               | L   | Н               | Н               | WRITE BYTE 1 ( K <sup>↑</sup> )                      |

|            | ↑ | L | н               | L   | Н               | Н               | WRITE BYTE 1 ( $\overline{K}\uparrow$ )              |

| ↑          |   | L | н               | Н   | L               | L               | WRITE BYTE 2 and BYTE 3 ( K $\uparrow$ )             |

|            | ↑ | L | н               | Н   | L               | L               | WRITE BYTE 2 and BYTE 3 ( $\overline{K}\uparrow$ )   |

| ↑          |   | L | н               | Н   | Н               | Н               | WRITE NOTHING ( K <sup>↑</sup> )                     |

|            | ↑ | L | Н               | Н   | Н               | Н               | WRITE NOTHING ( $\overline{\mathbf{K}}^{\uparrow}$ ) |

Notes: 1. X means "Don't Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(  $\uparrow$  ).

### **ABSOLUTE MAXIMUM RATINGS\***

| PARAMETER                              | SYMBOL | RATING          | UNIT |

|----------------------------------------|--------|-----------------|------|

| Voltage on VDD Supply Relative to Vss  | Vdd    | -0.5 to 3.6     | V    |

| Voltage on VDDQ Supply Relative to Vss | Vddq   | -0.5 to VDD     | V    |

| Voltage on Input Pin Relative to Vss   | Vin    | -0.5 to VDD+0.3 | V    |

| Power Dissipation                      | PD     | 1.8             | W    |

| Storage Temperature                    | Тѕтс   | -65 to 150      | °C   |

| Operating Temperature                  | Topr   | 0 to 70         | °C   |

| Storage Temperature Range Under Bias   | TBIAS  | -10 to 85       | °C   |

\*Note: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VDDQ must not exceed VDD during normal operation.

# DC ELECTRICAL CHARACTERISTICS(VDD=2.5V ±0.1V, TA=0°C to +70°C) PARAMETER SYMBOL TEST CONDITIONS MIN

| PARAMETER                     | SYMBOL | TEST CONDITIONS                                                         |     | MIN      | MAX      | UNIT | NOTES |

|-------------------------------|--------|-------------------------------------------------------------------------|-----|----------|----------|------|-------|

| Input Leakage Current         | ١L     | VDD=Max ; VIN=Vss to VDDQ                                               |     | -2       | +2       | μΑ   |       |

| Output Leakage Current        | Iol    | Output Disabled,                                                        |     | -2       | +2       | μΑ   |       |

|                               |        |                                                                         | -20 | -        | 520      |      |       |

| Operating Current (x18) : DDR | lcc    | VDD=Max , IOUT=0mA                                                      | -16 | -        | 460      | mA   | 1,5   |

| Operating Current (XTO) . DDK | ICC    | Cycle Time ≥ tкнкн Min                                                  | -13 | -        | 430      |      |       |

|                               |        |                                                                         | -10 | -        | 390      |      |       |

|                               |        |                                                                         | -20 | -        | 600      |      |       |

| Operating Current (x36) : DDR | lcc    | VDD=Max , IOUT=0mA                                                      | -16 | -        | 550      | mA   | 1,5   |

| Operating Current (x50) . DDR | 100    | Cycle Time ≥ tкнкн Min                                                  | -13 | -        | 490      |      |       |

|                               |        |                                                                         | -10 | -        | 420      |      |       |

|                               |        |                                                                         | -20 | -        | 200      | mA   | 1,6   |

| Standby Current(NOD) + DDD    | ISB1   | Device deselected, IOUT=0mA, f=Max,                                     | -16 | -        | 190      |      |       |

| Standby Current(NOP) : DDR    | ISB1   | All Inputs $\leq 0.2 \text{V} \text{ or } \geq \text{VDD-}0.2 \text{V}$ | -13 | -        | 180      |      |       |

|                               |        |                                                                         | -10 | -        | 170      |      |       |

| Output High Voltage           | Voh1   |                                                                         |     | Vddq/2   | Vddq     | V    | 2,7   |

| Output Low Voltage            | Vol1   |                                                                         |     | Vss      | Vddq/2   | V    | 3,7   |

| Output High Voltage           | Voh2   | Iон=-1.0mA                                                              |     | VDDQ-0.2 | Vddq     | V    | 4     |

| Output Low Voltage            | Vol2   | IOL=1.0mA                                                               |     | Vss      | 0.2      | V    | 4     |

| Input Low Voltage             | VIL    |                                                                         |     | -0.3     | Vref-0.1 | V    | 8,9   |

| Input High Voltage            | Viн    |                                                                         |     | Vref+0.1 | Vddq+0.3 | V    | 8,10  |

Notes: 1. Minimum cycle. IOUT=0mA.

2.  $|I_{OH}| = (V_{DDQ}/2)/(RQ/5) \pm 15\%$  @Voh=VDDQ/2 for  $175\Omega \le RQ \le 350\Omega$ .

3.  $|I_{OL}| = (V_{DDQ}/2)/(RQ/5) \pm 15\%$  @Vol=VDDQ/2 for  $175\Omega \le RQ \le 350\Omega$ .

4. Minimum Impedance Mode when ZQ pin is connected to Vss.

5. Operating current is calculated with 50% read cycles and 50% write cycles.

6. Standby Current is only after all pending read and write burst opeactions are completed.

7. Programmable Impedance Mode.

8. These are DC test criteria. DC design criteria is VREF±50mV. The AC VIH/VIL levels are defined separately for measuring

timing parameters.

9. VIL (Min)DC=-0.3V, VIL (Min)AC=-1.5V(pulse width  $\leq$  3ns).

10. VIH (Max)DC=VDDQ+0.3, VIH (Max)AC=VDDQ+0.85V(pulse width  $\leq$  3ns).

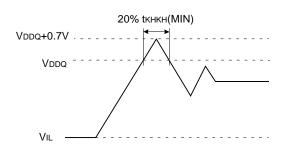

## **Overershoot Timing**

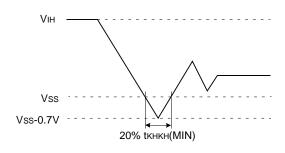

## **Undershoot Timing**

Note: For power-up, VIH  $\leq$  VDDQ+0.3V and VDD  $\leq$  2.4V and VDDQ  $\leq$  1.4V for  $~t\leq$  200ms

#### **OPERATING CONDITIONS** $(0^{\circ}C \le TA \le 70^{\circ}C)$

| PARAMETER         | SYMBOL | MIN  | MAX  | UNIT |

|-------------------|--------|------|------|------|

| Supply Voltage    | Vdd    | 2.4  | 2.6  | V    |

| Supply voltage    | Vddq   | 1.4  | 1.9  | V    |

| Reference Voltage | Vref   | 0.68 | 0.95 | V    |

| Ground            | Vss    | 0    | 0    | V    |

#### AC TIMING CHARACTERISTICS (VDD=2.5V±0.1V, TA=0°C to +70°C)

| PARAMETER                                                                                                                                         | SYMBOL        | -:  | 20   | -   | 16  | -   | 13  | -   | 10  | UNITS | NOTES |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|------|-----|-----|-----|-----|-----|-----|-------|-------|

| PARAMETER                                                                                                                                         | SYMBOL        | MIN | MAX  | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NUTES |

| Clock                                                                                                                                             | lock          |     |      |     |     |     |     |     |     |       |       |

| Clock Cycle Time(K, $\overline{K}$ , C, $\overline{C}$ )                                                                                          | tкнкн         | 5   |      | 6   |     | 7.5 |     | 10  |     | ns    |       |

| Clock HIGH time (K, $\overline{K}$ , C, $\overline{C}$ )                                                                                          | tĸнĸ∟         | 2.0 |      | 2.4 |     | 3.0 |     | 3.5 |     | ns    |       |

| Clock LOW time (K, $\overline{K}$ , C, $\overline{C}$ )                                                                                           | tк∟кн         | 2.0 |      | 2.4 |     | 3.0 |     | 3.5 |     | ns    |       |

| Clock to $\overline{\text{clock}}$ (K <sup>↑</sup> $\rightarrow \overline{K}^{\uparrow}$ , C <sup>↑</sup> $\rightarrow \overline{C}^{\uparrow}$ ) | tкнкн         | 2.2 | 2.75 | 2.7 | 3.3 | 3.4 | 4.1 | 4.6 | 5.4 | ns    |       |

| Clock to data clock $(K^{\uparrow} \rightarrow C^{\uparrow}, \overline{K}^{\uparrow} \rightarrow \overline{C}^{\uparrow})$                        | tкнсн         | 0.0 | 1.7  | 0.0 | 2.0 | 0.0 | 2.5 | 0.0 | 3.0 | ns    |       |

| Output Times                                                                                                                                      |               |     |      |     |     |     |     |     |     |       |       |

| C, C High to Output Valid                                                                                                                         | <b>t</b> CHQV |     | 2.2  |     | 2.5 |     | 3.0 |     | 3.0 | ns    | 3     |

| C, $\overline{C}$ High to Output hold                                                                                                             | <b>t</b> CHQX | 1.0 |      | 1.2 |     | 1.2 |     | 1.2 |     | ns    | 3     |

| C High to Output High-Z                                                                                                                           | <b>t</b> CHQZ |     | 2.2  |     | 2.5 |     | 3.0 |     | 3.0 | ns    | 3     |

| C High to Output Low-Z                                                                                                                            | tCHQX1        | 1.0 |      | 1.2 |     | 1.2 |     | 1.2 |     | ns    | 3     |

| Setup Times                                                                                                                                       |               |     |      |     |     |     |     |     |     |       |       |

| Address valid to K rising edge                                                                                                                    | tavкн         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | ns    |       |

| Control inputs valid to K rising edge                                                                                                             | tı∨ĸн         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | ns    | 2     |

| Data-in valid to K, $\overline{K}$ rising edge                                                                                                    | tdvкн         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | ns    |       |

| Hold Times                                                                                                                                        |               |     |      |     |     |     |     |     |     | 1     |       |

| K rising edge to address hold                                                                                                                     | tкнах         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | v     |       |

| K rising edge to control inputs hold                                                                                                              | tкніх         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | ns    |       |

| K, $\overline{K}$ rising edge to data-in hold                                                                                                     | tкнdх         | 0.6 |      | 0.7 |     | 0.8 |     | 1.0 |     | ns    |       |

Notes: 1. All address inputs must meet the specified setup and hold times for all latching clock edges.

2. Control signals are R, W,BW0,BW1 and (BW2, BW3, also for x36)

3. If C,C are tied high, K,K become the references for C,C timing parameters.

4. To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ. The specs as shown do not imply bus contention beacuse tCHQX1 is a MIN parameter that is worst case at totally different test conditions (20, 0, 0, 0) then total ways to the specific test conditions and the specific test conditions are total ways to the specific test conditions. (0°C, 2.6V) than tCHQZ, which is a MAX parameter(worst case at 70°C, 2.4V)

It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

## **AC TEST CONDITIONS**

| Parameter                     | Symbol  | Value     | Unit |

|-------------------------------|---------|-----------|------|

| Core Power Supply Voltage     | Vdd     | 2.4~2.6   | V    |

| Output Power Supply Voltage   | Vddq    | 1.4~1.9   | V    |

| Input High/Low Level          | VIH/VIL | 1.25/0.25 | V    |

| Input Reference Level         | Vref    | 0.75      | V    |

| Input Rise/Fall Time          | Tr/Tf   | 0.3/0.3   | ns   |

| Output Timing Reference Level |         | Vddq/2    | V    |

Note: Parameters are tested with RQ=250 $\Omega$

## AC TEST OUTPUT LOAD

#### **PIN CAPACITANCE**

| PRMETER                           | SYMBOL | TESTCONDITION | MIN | MAX | Unit | NOTES |

|-----------------------------------|--------|---------------|-----|-----|------|-------|

| Address Control Input Capacitance | CIN    | VIN=0V        | 4   | 5   | pF   |       |

| Input and Output Capacitance      | Соит   | Vout=0V       | 6   | 7   | pF   |       |

| Clock Capacitance                 | CCLK   | -             | 5   | 6   | pF   |       |

Note: 1. Parameters are tested with RQ=250 $\Omega$  and VDDQ=1.5V.

2. Periodically sampled and not 100% tested.

#### THERMAL RESISTANCE

| PRMETER             | SYMBOL | ТҮР  | Unit | NOTES |

|---------------------|--------|------|------|-------|

| Junction to Ambient | ALθ    | 24.0 | °C/W |       |

| Junction to Case    | θJC    | 2.8  | °C/W |       |

| Junction to Pins    | θјв    | 5.5  | °C/W |       |

Note: Junction temperature is a function of on-chip power dissipation, package thermal impedance, mounting site temperature and mounting site thermal impedance. T<sub>J</sub>=T<sub>A</sub> + P<sub>D</sub> x θ<sub>JA</sub>

## **APPLICATION INFORMATION**

1Mx18

### TIMING WAVE FORMS OF READ AND NOP

Note: 1. Q1-1 refers to output from address A1+0, Q1-2 refers to output from address A1+1 i.e. the next internal burst address following A1+0. 2. Outputs are disabled one cycle after a NOP.

#### WRITE WRITE NOP tкнкн -tĸlkh Κ -tкнкL tкнкн → ĸ **t**AVKH **t**KHAX ◄ SA A1 A2 tĸнıx tĸнı> W D(Data In) D2-2 D1-2 D2-1 D1-1 D1-3 D1-4 D2-3 D2-4 **∢**→ tdvkh **€**кнох Don't Care Undefined

## TIMING WAVE FORMS OF WRITE AND NOP

Note: 1. D1-1 refers to input to address A1+0, D1-2 refers to input to address A1+1, i.e the next internal burst address following A1+0.

## TIMING WAVE FORMS OF READ, WRITE AND NOP

Note: 1. Q1-1 refers to output from address A1+0, Q1-2 refers to output from address A1+1 i.e. the next internal burst address following A1+0. 2. Outputs are disabled one cycle after a NOP.

3. If address A3=A2, data Q3-1=D2-1, data Q3-2=D2-2, data Q3-3=D2-3, data Q3-4=D2-4. Write data is forwarded immediately as read results.

4. BWx assumed active

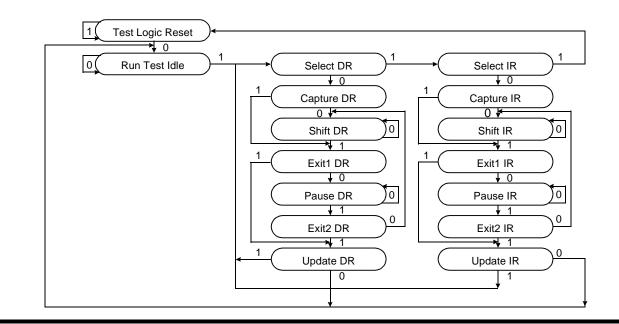

## IEEE 1149.1 TEST ACCESS PORT AND BOUNDARY SCAN-JTAG

This part contains an IEEE standard 1149.1 Compatible Test Access Port(TAP). The package pads are monitored by the Serial Scan circuitry when in test mode. This is to support connectivity testing during manufacturing and system diagnostics. Internal data is not driven out of the SRAM under JTAG control. In conformance with IEEE 1149.1, the SRAM contains a TAP controller, Instruction Register, Bypass Register and ID register. The TAP controller has a standard 16-state machine that resets internally upon power-up, therefore, TRST signal is not required. It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfacing with normal operation of the SRAM, TCK must be tied to Vss to preclude mid level input. TMS and TDI are designed so an undriven input will produce a response identical to the application of a logic 1, and may be left unconnected. But they may also be tied to VDD through a resistor. TDO should be left unconnected.

#### **JTAG Block Diagram**

**TAP Controller State Diagram**

## **JTAG Instruction Coding**

| IR2 | IR1 | IR0 | Instruction | TDO Output              | Notes |  |

|-----|-----|-----|-------------|-------------------------|-------|--|

| 0   | 0   | 0   | EXTEST      | Boundary Scan Register  | 1     |  |

| 0   | 0   | 1   | IDCODE      | Identification Register | 3     |  |

| 0   | 1   | 0   | SAMPLE-Z    | Boundary Scan Register  | 2     |  |

| 0   | 1   | 1   | BYPASS      | Bypass Register         | 4     |  |

| 1   | 0   | 0   | SAMPLE      | Boundary Scan Register  | 5     |  |

| 1   | 0   | 1   | RESERVED    | Do Not Use              | 6     |  |

| 1   | 1   | 0   | BYPASS      | Bypass Register         | 4     |  |

| 1   | 1   | 1   | BYPASS      | Bypass Register         | 4     |  |

NOTE :

- 1. Places DQs in Hi-Z in order to sample all input data regardless of other SRAM inputs. This instruction is not IEEE 1149.1 compliant.

- 2. Places DQs in Hi-Z in order to sample all input data regardless of other SRAM inputs.

- 3. TDI is sampled as an input to the first ID register to allow for the serial shift of the external TDI data.

- Bypass register is initiated to Vss when BYPASS instruction is invoked. The Bypass Register also holds serially loaded TDI when exiting the Shift DR states.

- 5. SAMPLE instruction dose not places DQs in Hi-Z.

- 6. This instruction is reserved for future use.

#### SCAN REGISTER DEFINITION

| Part    | Instruction Register | ruction Register Bypass Register |         | Boundary Scan |

|---------|----------------------|----------------------------------|---------|---------------|

| 1Mx18   | 3 bits               | 1 bits                           | 32 bits | 107 bits      |

| 512Kx36 | 3 bits               | 1 bits                           | 32 bits | 107 bits      |

#### **ID REGISTER DEFINITION**

| Part    | Revision Number<br>(31:28) | Part Configuration (27:18) | Vendor Definition<br>(17:12) | Samsung JEDEC Code<br>(11: 1) | Start Bit(0) |

|---------|----------------------------|----------------------------|------------------------------|-------------------------------|--------------|

| 1Mx18   | 0000                       | 01000 00011                | XXXXXX                       | 00001001110                   | 1            |

| 512Kx36 | 0000                       | 00111 00100                | XXXXXX                       | 00001001110                   | 1            |

## **BOUNDARY SCAN EXIT ORDER**

| BIT | PIN ID | BIT | PIN ID | BIT | PIN ID |

|-----|--------|-----|--------|-----|--------|

| 1   | 6R     | 37  | 10D    | 73  | 2C     |

| 2   | 6P     | 38  | 9E     | 74  | 3E     |

| 3   | 6N     | 39  | 10C    | 75  | 2D     |

| 4   | 7P     | 40  | 11D    | 76  | 2E     |

| 5   | 7N     | 41  | 90     | 77  | 1E     |

| 6   | 7R     | 42  | 9D     | 78  | 2F     |

| 7   | 8R     | 43  | 11B    | 79  | 3F     |

| 8   | 8P     | 44  | 11C    | 80  | 1G     |

| 9   | 9R     | 45  | 9B     | 81  | 1F     |

| 10  | 11P    | 46  | 10B    | 82  | 3G     |

| 11  | 10P    | 47  | 11A    | 83  | 2G     |

| 12  | 10N    | 48  | 10A    | 84  | 1J     |

| 13  | 9P     | 49  | 9A     | 85  | 2J     |

| 14  | 10M    | 50  | 8B     | 86  | ЗK     |

| 15  | 11N    | 51  | 7C     | 87  | 3J     |

| 16  | 9M     | 52  | 6C     | 88  | 2K     |

| 17  | 9N     | 53  | 8A     | 89  | 1K     |

| 18  | 11L    | 54  | 7A     | 90  | 2L     |

| 19  | 11M    | 55  | 7B     | 91  | 3L     |

| 20  | 9L     | 56  | 6B     | 92  | 1M     |

| 21  | 10L    | 57  | 6A     | 93  | 1L     |

| 22  | 11K    | 58  | 5B     | 94  | 3N     |

| 23  | 10K    | 59  | 5A     | 95  | 3M     |

| 24  | 9J     | 60  | 4A     | 96  | 1N     |

| 25  | 9K     | 61  | 5C     | 97  | 2M     |

| 26  | 10J    | 62  | 4B     | 98  | 3P     |

| 27  | 11J    | 63  | 3A     | 99  | 2N     |

| 28  | 11H    | 64  | 2A     | 100 | 2P     |

| 29  | 10G    | 65  | 1A     | 101 | 1P     |

| 30  | 9G     | 66  | 2B     | 102 | 3R     |

| 31  | 11F    | 67  | 3B     | 103 | 4R     |

| 32  | 11G    | 68  | 1C     | 104 | 4P     |

| 33  | 9F     | 69  | 1B     | 105 | 5P     |

| 34  | 10F    | 70  | 3D     | 106 | 5N     |

| 35  | 11E    | 71  | 3C     | 107 | 5R     |

| 36  | 10E    | 72  | 1D     | J   |        |

Note: 1. NC pins are read as "X" ( i.e. don't care.)

### JTAG DC OPERATING CONDITIONS

| Parameter                     | Symbol | Min  | Тур | Max     | Unit | Note |

|-------------------------------|--------|------|-----|---------|------|------|

| Power Supply Voltage          | Vdd    | 2.4  | 2.5 | 2.6     | V    |      |

| Input High Level              | Vін    | 1.7  | -   | Vdd+0.3 | V    |      |

| Input Low Level               | VIL    | -0.3 | -   | 0.7     | V    |      |

| Output High Voltage(Iон=-2mA) | Vон    | 2.0  | -   | Vdd     | V    |      |

| Output Low Voltage(IoL=2mA)   | Vol    | Vss  | -   | 0.4     | V    |      |

$\ensuremath{\textit{Note}}\xspace$  1. The input level of SRAM pin is to follow the SRAM DC specification.

## JTAG AC TEST CONDITIONS

| Parameter                               | Symbol  | Min     | Unit | Note |

|-----------------------------------------|---------|---------|------|------|

| Input High/Low Level                    | VIH/VIL | 2.5/0.0 | V    |      |

| Input Rise/Fall Time                    | TR/TF   | 1.0/1.0 | ns   |      |

| Input and Output Timing Reference Level |         | 1.25    | V    | 1    |

Note: 1. See SRAM AC test output load on page 11.

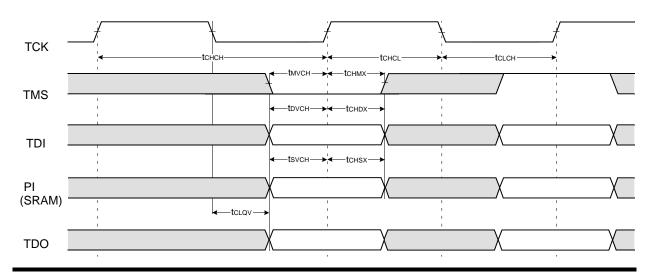

#### **JTAG AC Characteristics**

| Parameter                 | Symbol        | Min | Max | Unit | Note |

|---------------------------|---------------|-----|-----|------|------|

| TCK Cycle Time            | tснсн         | 50  | -   | ns   |      |

| TCK High Pulse Width      | <b>t</b> CHCL | 20  | -   | ns   |      |

| TCK Low Pulse Width       | <b>t</b> CLCH | 20  | -   | ns   |      |

| TMS Input Setup Time      | tмvсн         | 5   | -   | ns   |      |

| TMS Input Hold Time       | tснмх         | 5   | -   | ns   |      |

| TDI Input Setup Time      | <b>t</b> DVCH | 5   | -   | ns   |      |

| TDI Input Hold Time       | <b>t</b> CHDX | 5   | -   | ns   |      |

| SRAM Input Setup Time     | <b>t</b> SVCH | 5   | -   | ns   |      |

| SRAM Input Hold Time      | tCHSX         | 5   | -   | ns   |      |

| Clock Low to Output Valid | <b>t</b> CLQV | 0   | 10  | ns   |      |

#### JTAG TIMING DIAGRAM

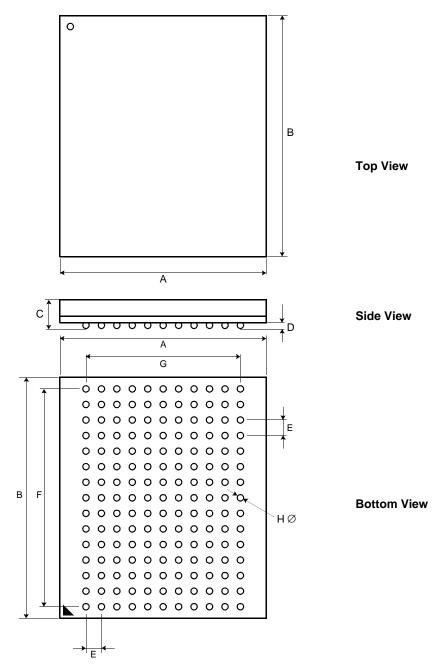

## **165 FBGA PACKAGE DIMENSIONS**

13mm x 15mm Body, 1.0mm Bump Pitch, 11x15 Ball Array

| Symbol | Value         | Units | Note | Symbol | Value         | Units | Note |

|--------|---------------|-------|------|--------|---------------|-------|------|

| А      | $13\pm0.1$    | mm    |      | E      | 1.0           | mm    |      |

| В      | $15\pm0.1$    | mm    |      | F      | 14.0          | mm    |      |

| С      | $1.3\pm0.1$   | mm    |      | G      | 10.0          | mm    |      |

| D      | $0.35\pm0.05$ | mm    |      | н      | $0.45\pm0.05$ | mm    |      |