Rev. 1.4, Jul. 2012 KLMxGxFE4B-B001

## **Samsung e·MMC Product family** e.MMC 4.5 Specification compatibility

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2012 Samsung Electronics Co., Ltd. All rights reserved.

## SAMSUNG ELECTRONICS

## **Revision History**

| Revision No.        | History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Draft Date    | <u>Remark</u> | <u>Editor</u> |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|

| 0.0                 | 1. Initial issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Sep. 29, 2011 | Target        | S.M.Lee       |

| 0.5                 | <ol> <li>Engineering Sample</li> <li>64GB is deleted</li> <li>Discard Time is added in Table 10</li> <li>Init time is changed to 3sec which is the value after partition setting in Table 44</li> <li>Extended CSD Register values are changed in Chapter 7.4         <ul> <li>HPI_FEATURES is changed from 0x03 to 0x01</li> <li>DATA_TAG_SUPPORT is changed from 0x00 to 0x01</li> <li>INI_TIMEOUT_AP is changed from 0x0A to 0x1E</li> <li>TRIM_MULT is changed from 0x0A to 0x11</li> <li>SEC_ERASE_MULT is changed from 0x0A to 0x11</li> <li>ACC_SIZE is changed from 0x05 to 0x07</li> <li>OUT_OF_INTERRUPT_TIME is changed from 0x01 to 0x02</li> </ul> </li> <li>Time Parameters are changed in Table 60         <ul> <li>Initialization time is divided into 'Normal' and 'After partition setting'</li> <li>Write timeout is changed from 10ms to 15ms</li> <li>Secure Erase timeout is changed from 300ms to 55cc</li> <li>Trim timeout is changed from 300ms to 350ms</li> </ul> </li> </ol> | Dec. 16, 2011 | Preliminary   | S.M.Lee       |

| 1.0                 | <ul> <li>Discard timeout is deleted</li> <li>1. Customer Sample</li> <li>2. 16GB is deleted</li> <li>3. Maximum enhanced partition size is changed in Table 47</li> <li>4. Performance is updated with measured value in Table 54</li> <li>5. Extended CSD Register values are changed in Chapter 7.4</li> <li>HC_WP_GRP_SIZE is changed from 0x40 to 0x50</li> <li>MAX_ENH_SIZE_MULT is changed from 0x1D1 to 0x174</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Jan. 16, 2012 | Final         | S.M.Lee       |

| 1.1                 | 1. Read Timeout Typo is corrected in Table 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Feb. 09 ,2012 | Final         | S.M.Lee       |

| WV <sup>1,2</sup> W | 1. Typo of default Boot Area Partition size is corrected in Chapter 6.1.1.1<br>[512KB -> 2,048KB]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mar. 12, 2012 | Final         | S.M.Lee       |

| 1.3                 | <ol> <li>1. 16GB and 64GB products are added</li> <li>2. 'Dual Data Rate mode is supported' is added in Chapter 2.0</li> <li>3. List of interruptible command is changed in Table 28</li> <li>4. Information of Wear Leveling is deleted in Chapter 6.1.4</li> <li>5. Information of 'End of Life Management' is deleted in Chapter 6.1.7</li> <li>6. Information of Smart Report is deleted in Chapter 6.2</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | May. 11, 2012 | Final         | S.M.Lee       |

| 1.4                 | <ol> <li>Maximum Enhanced Partition Size of 16GB is changed in Table 46</li> <li>User Density Size of 16GB is changed in Table 47</li> <li>Extended CSD Register values are changed in Chapter 7.4         <ul> <li>SEC_COUNT of 16GB is changed from 0x1D5A000 to 0x1D1F000</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jul.20, 2012  | Final         | S.M.Lee       |

SEC\_COUNT of 16GB is changed from 0x1D5A000 to 0x1D1F000

MAX\_ENH\_SIZE\_MULT of 16GB is changed from 0xBB to 0xBA

## Revision History Appendix(0.5)

| Before(ver.0.0)                                                                                                                                                                                      |                                    |                   | After(ver.0.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Table 1] Product List                                                                                                                                                                                |                                    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

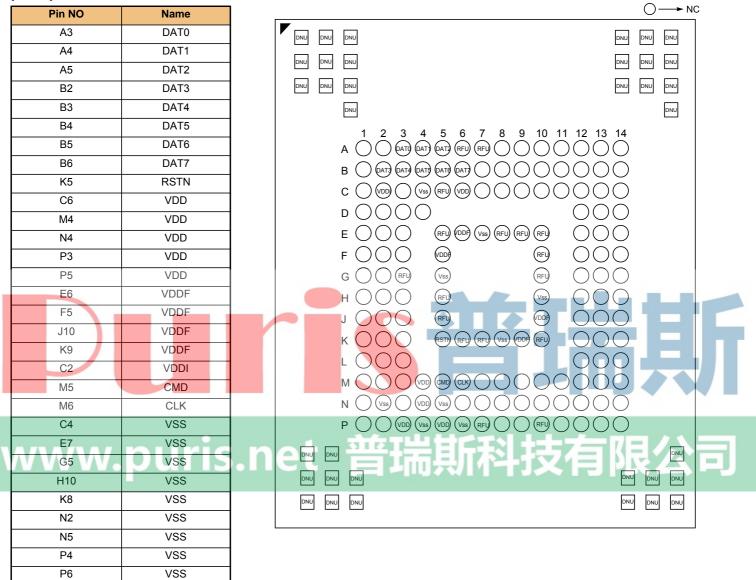

| Capacities e-MMC Part ID NAND Flash Type User Density (%) Power System                                                                                                                               | Package size                       | Pin Configuration | (Table 1) Product List<br>Capacities e-MMC Part ID NAND Flash Type User Density (%) Power System Package size Pin Configur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

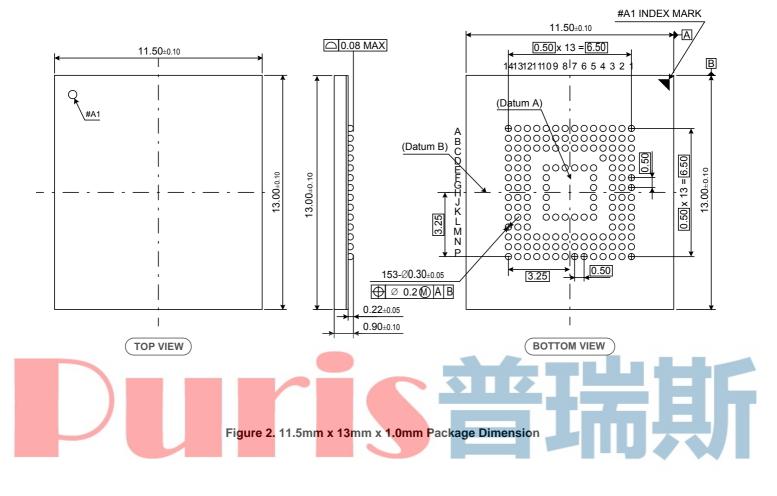

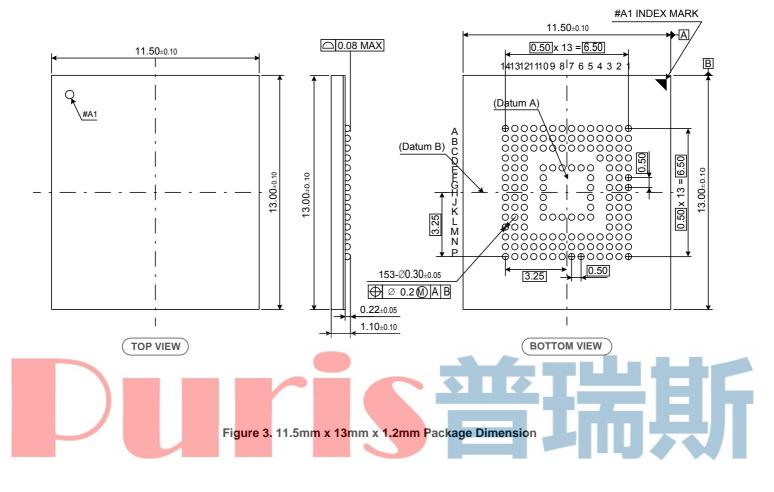

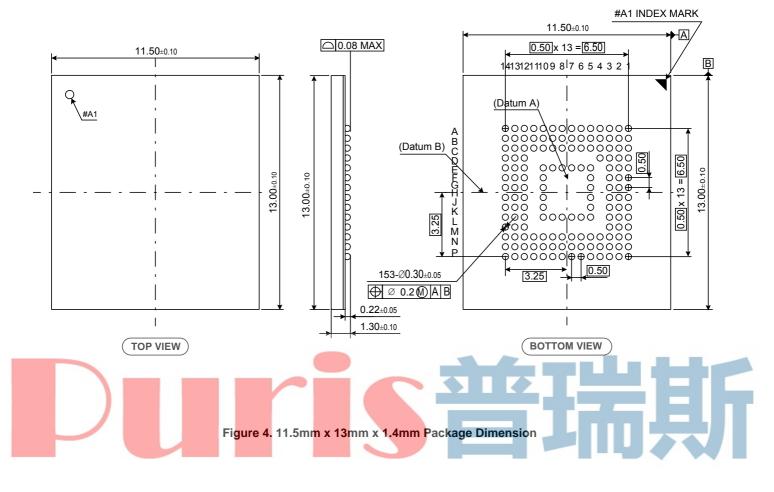

| 18GB KLMAG4FE4B-B001 32Gb MLC x 4 - Interface power : VD                                                                                                                                             | -                                  |                   | 18GB KLMAG4FE4B-8001 32Gb MLC x 4 - Interface power VDD 11.5mm x 13mm x 1.0mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| 32GB         KLMBG8FE4B-B001         32Gb MLC x 8         (1/10V ~ 1/96V or<br>2.7V ~ 3.6V)           64GB         KLMCGAFE4B-B001         32Gb MLC x 18         - Memory power: VD<br>(2.7V ~ 3.6V) | 11.5mm x 1.3mm x 1.2mm             |                   | 32GB KLMBG8FE4B-B001 32Gb MLC x 8 91.0% 2.7V ~ 3.6V)<br>- Memory power : VDDF<br>(2.7V ~ 3.6V)<br>- Memory power : VDDF<br>(2.7V ~ 3.6V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                      |                                    |                   | [Table 10] Discard Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                      |                                    |                   | Timing Factor Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                      |                                    |                   | Discard <sup>1)</sup> < 15ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| e                                                                                                                                                                                                    |                                    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

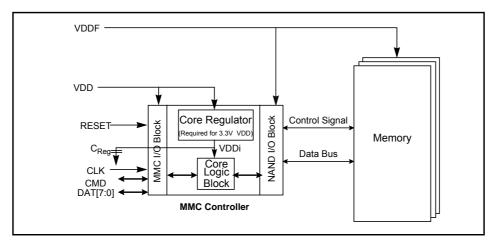

|                                                                                                                                                                                                      |                                    |                   | CLK MMMMMMMM<br>CMD $(M00^{+})$ |  |  |  |  |  |  |  |  |

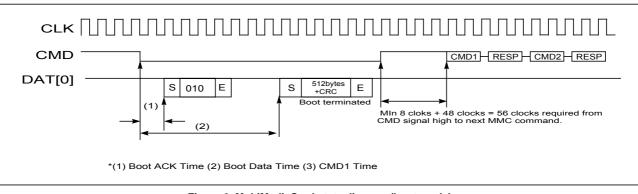

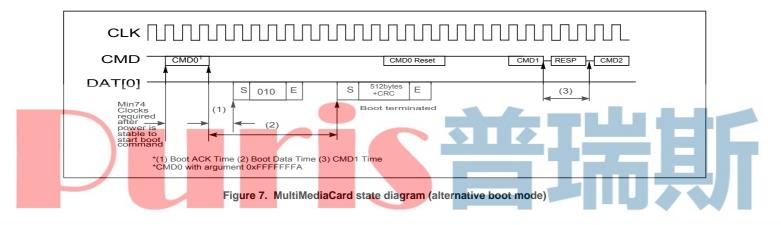

| Figure 7. MultiMediaCard state diagram (alternative bo                                                                                                                                               | ot mode)                           | j                 | Figure 7. MultiMediaCard state diagram (alternative boot mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| [Table 43] Boot ACK and Boot Data timing value and initialization time                                                                                                                               |                                    |                   | [Table 44] Boot ack, boot data and initialization Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Timing Factor<br>(1) Bodt ACK Time<br>(2) Bodt Data Time                                                                                                                                             | < 50 ms                            |                   | Timing Factor         Value           (1) Boot ACK Time         < 50 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| (3) Inibalization Time* * Definition of Initialization Time CND0 + CMD1 busy bit clearing time. For Initialization time after p                                                                      | < 200 ma                           |                   | (3) Icithalization Time <sup>19</sup> 3 sets<br>NOTE: 10 Icitatization Time Includes particip, Sease refer 20 VII_1112EQUT_AP In 7.4 Existenced CSD Register:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| in 7.4 Extended CSD Register.<br>Minimum function for reading boot data is initialized during boot time and after that full function is initi                                                        | alized during initialization time. |                   | 1) The initialization time includes particles setting. Joakse refer to INE_TUDE_OUT_AP in 7.4 Existence GSD Register.<br>Norms initialization time (without partition setting) is completed within fase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| [Table 58] Extended CSD Register                                                                                                                                                                     |                                    |                   | [Table 59] Extended CSD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Name Field Size (Bytes)                                                                                                                                                                              | CSD-slice                          | SD Value          | Name Field Size Cell CSD clice CSD Val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| HPI features HPI_FEATURES 1                                                                                                                                                                          | R [503]                            | 0x03              | HPI features HPI_FEATURES 1 R [503] 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Data Tag Support DATA_TAG_SUPPORT 1 1st initialization time after partitioning INI_TIMEOUT_AP 1                                                                                                      | R [499]<br>R [241]                 | 0x00<br>0x0A      | Data Tag Support         DATA_TAG_SUPPORT         1         R         [499]         0x01           1st initialization time after partitioning         INI_TIMEOUT_AP         1         R         [241]         0x1E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| TRIM Multiplier TRIM_MULT 1                                                                                                                                                                          | R [232]                            | 0x01              | TRIM Multiplier TRIM_MULT _ 1 R (232) 0/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Secure Erase Multiplier SEC_ERASE_MULT 1 Secure TRIM Multiplier SEC_TRIM_MULT 1                                                                                                                      | R [230]<br>R [229]                 | 0x0A<br>0x0A      | Secure Erase Multipler         SEC_ERASE_MULT         1         R         [230]         0x18           Secure TRIM Multipler         SEC_TRIM_MULT         1         R         [229]         0x11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Access size ACC_SIZE 1                                                                                                                                                                               | R [225]                            | 0x05              | Access size ACC_SIZE 1 R [225] 0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Out-of-interrupt busy timing OUT_OF_INTERRUPT_TIME 1                                                                                                                                                 | R [198]                            | 0x01              | Out-of-Interrupt busy timing OUT_OF_INTERRUPT_TIME 1 R [198] 0/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| [Table 59] Time Parameter                                                                                                                                                                            |                                    |                   | [Table 60] Time Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Timing Paramter                                                                                                                                                                                      | Max. Value                         | Unit              | Timing Paramter Max. Value Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Initialization Time (tINIT)                                                                                                                                                                          | 1                                  | s                 | Initialization Time (tINIT) Normal 1) 1 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Read Timeout                                                                                                                                                                                         | 100                                | ms                | After partition setting <sup>2)</sup> 3 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Write Timeout                                                                                                                                                                                        | 300                                | ms                | Read Timeout 100 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

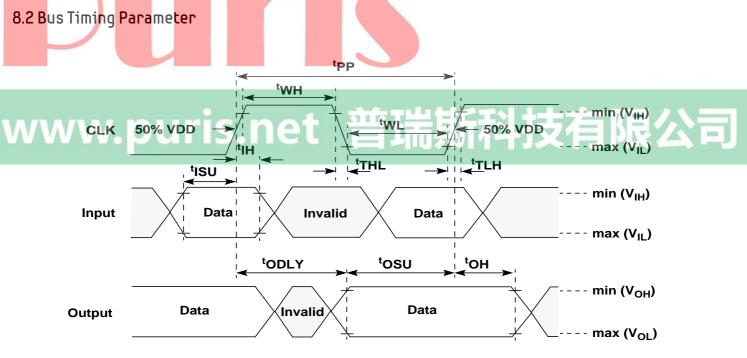

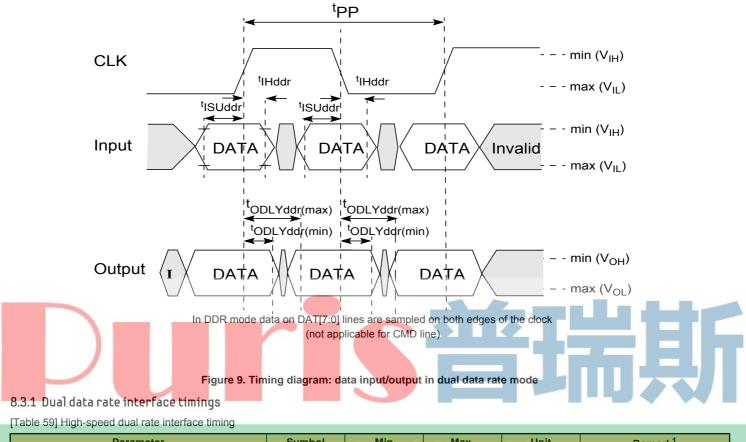

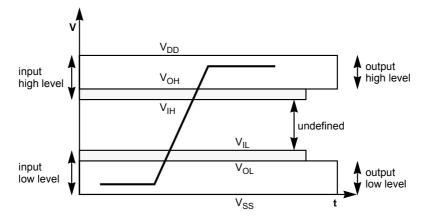

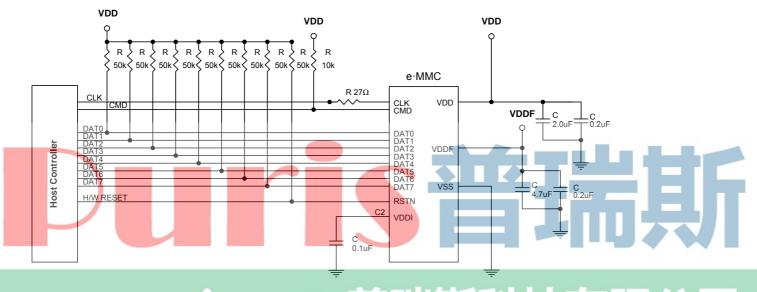

| Erase Timeout                                                                                                                                                                                        |                                    |                   | Write Timeout 350 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |