# 8K×8 Bit EEPROM with Latches and Auto-Write

## **FEATURES**

- Simple Byte Write

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- Enhanced Write Protection

- Single 5 volt Supply

- Byte Write: 10ms (max)—KM2864A 2ms (max)—KM2864AH

- Fast Access Time: 200ns

- Power: 50mA—Standby (max) 120mA-Operating (max)

- Two Line Control-Eliminates Bus Contention

- 10,000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

# GENERAL DESCRIPTION

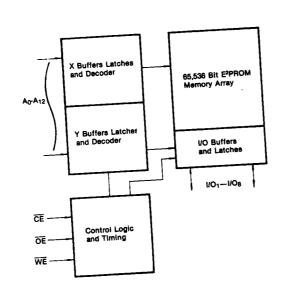

The KM2864A/AH is a 65,536 bit Electrically Erasable and Programmable Read-Only-Memory organized as 8,192 words by 8-bits. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM2864A/AH is very simple. The internally self-timed write cycle latches both address and data to provide a free system bus during the write period which is 10ms (max) for the KM2864A or 2ms (max) for the KM2864AH.

The KM2864A/AH features DATA Polling, a software scheme to detect the early completion of a write cycle without requiring the use of any additional external hardware. The KM2864A/AH is fabricated with the well defined floating gate NMOS technology using Fowler-Nordhelm tunneling for erasing and programming.

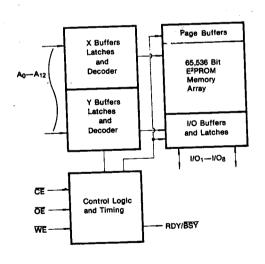

# FUNCTIONAL BLOCK DIAGRAM

| N.C. 1<br>A12 2<br>A7 3<br>A6 4<br>A5 5<br>A4 6<br>A3 7<br>A2 8<br>A1 9<br>A0 10<br>I/O1 11<br>I/O2 113<br>I/O3 113 | 28 Vcc<br>27 WE<br>28 N.C.<br>25 A8<br>24 A9<br>23 A11<br>22 OE<br>21 A10<br>20 CE<br>19 1/08<br>18 1/07<br>17 1/06<br>18 1/05 |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| VO2 12                                                                                                              | F-                                                                                                                             |

| 1/03 13                                                                                                             | -                                                                                                                              |

| Vss 14                                                                                                              | 15 1/04                                                                                                                        |

| Pin Name                        | Pin Function        |

|---------------------------------|---------------------|

| A <sub>0</sub> -A <sub>12</sub> | Address Inputs      |

| 1/01-1/08                       | Data Inputs/Outputs |

| CE                              | Chip Enable         |

| OE OE                           | Output Enable       |

| WE                              | Write Enable        |

| N.C.                            | No Connection       |

| Voc                             | Power (+5V)         |

| Vss                             | Ground              |

#### 2.3 Static RAM

|          |                | 9.3. +       | Speed | <b> </b><br> - | Current                 |                          | ŀ          |        |

|----------|----------------|--------------|-------|----------------|-------------------------|--------------------------|------------|--------|

| Capacity | Part Number    | Organization | (ns)  | Technology     | Active, mA<br>Typ (max) | Standby, µA<br>Typ (max) | Packages   | Remark |

|          | KM6816A-12     | 2K×8         | 120   | CMOS           | 20 (40)                 | 10 (50)                  | 24-Pin DIP | Now    |

| 16K bit  | KM6816A-15     | 2K×8         | 150   | CMOS           | 20 (40)                 | 10 (50)                  | 24-Pin DIP | Now    |

| IOK DIL  | KM6816AL-12    | 2K×8         | 120   | CMOS           | 20 (40)                 | 1 (10)                   | 24-Pin DIP | Now    |

|          | KM6816AL-15    | 2K×8         | 150   | CMOS           | 20 (40)                 | 1 (10)                   | 24-Pin DIP | Now    |

|          | KM6264-12      | 8K×8         | 120   | CMOS           | 35 (45)                 | (1mA)                    | 28-Pin DIP | Now    |

| 64K bit  | KM6264-15      | 8K×8         | 150   | CMOS           | 35 (45)                 | (1mA)                    | 28-Pin DIP | Now    |

| D4K DIL  | KM6264L-12     | 8K×8         | 120   | CMOS           | 35 (45)                 | 2 (0.1mA)                | 28-Pin DIP | Now    |

|          | KM6264L-15     | 8K×8         | 150   | CMOS           | 35 (45)                 | 2 (0.1mA)                | 28-Pin DIP | Now    |

|          | ††KM62256P-10  | 32K×8        | 100   | CMOS           | 30 (45)                 | (1mA)                    | 28-Pin DIP | TBA    |

|          | ††KM62256P-12  | 32K×8        | 120   | CMOS           | 30 (45)                 | (1mA)                    | 28-Pin DIP | TBA    |

| DEOK PR  | ††KM62256P-15  | 32K×8        | 150   | CMOS           | 30 (45)                 | (1mA)                    | 28-Pin DIP | TBA    |

| 256K bit | ††KM62256LP-10 | 32K×8        | 100   | CMOS           | 30 (45)                 | (4 μΑ)                   | 28-Pin DIP | TBA    |

|          | ††KM62256LP-12 | 32K×8        | 120   | CMOS           | 30 (45)                 | (4 μA)                   | 28-Pin DIP | TBA    |

|          | ††KM62256LP-15 | 32K×8        | 150   | CMOS           | 30 (45)                 | (4 μA)                   | 28-Pin DIP | TBA    |

## 2.4 EEPROM

| Capacity | Part Number  | Organization | Speed<br>(ns) | Technology | Write Cycle<br>Time (max)<br>(ms) | Features                                  | Packages   | Remark |

|----------|--------------|--------------|---------------|------------|-----------------------------------|-------------------------------------------|------------|--------|

|          | KM2816A-25   | 2K×8         | 250           | NMOS       | 10                                |                                           | 24-Pin DIP | Now    |

|          | KM2816A-30   | 2K×8         | 300           | NMOS       | 10                                | _                                         | 24-Pin DIP | Now    |

| 16K bit  | KM2816A-35   | 2K×8         | 350           | NMOS       | 10                                | _                                         | 24-Pin DIP | Now    |

| TOK DIL  | KM2817A-25   | 2K×8         | 250           | NMOS       | 10                                | Ready/Busy                                | 28-Pin DIP | Now    |

| t        | KM2817A-30   | 2K×8         | 300           | NMOS       | 10                                | Ready/Busy                                | 28-Pin DIP | Now    |

|          | KM2817A-35   | 2K×8         | 350           | NMOS       | 10                                | Ready/Busy                                | 28-Pin DIP | Now    |

| ·        | KM2864A-20   | 8K×8         | 200           | NMOS       | 10                                | Data Polling                              | 28-Pin DIP | Now    |

|          | KM2864A-25   | 8K×8         | 250           | NMOS       | 10                                | Data Polling                              | 28-Pin DIP | Now    |

|          | KM2864A-30   | 8K×8         | 300           | NMOS       | 10                                | Data Polling                              | 28-Pin DIP | Now    |

|          | KM2865A-20   | 8K×8         | 200           | NMOS       | 10                                | Data Polling,                             | 28-Pin DIP | Now    |

|          | KM2865A-25   | 8K×8         | 250           | NMOS       | 10                                | Ready/Busy<br>Data Polling,<br>Ready/Busy | 28-Pin DIP | Now    |

|          | KM2865A-30   | 8K×8         | 300           | NMOS       | 10                                | Data Polling,<br>Ready/Busy               | 28-Pin DIP | Now    |

|          | †KM2864AH-20 | 8K×8         | 200           | NMOS       | 2                                 | Data Polling                              | 28-Pin DIP | Now    |

| 64K bit  | †KM2864AH-25 | 8K×8         | 250           | NMOS       | 2<br>2<br>2<br>2                  | Data Polling                              | 28-Pin DIP | Now    |

|          | †KM2864AH-30 | 8K×8         | 300           | NMOS       | 2                                 | Data Polling                              | 28-Pin DIP | Now    |

|          | †KM2865AH-20 | 8K×8         | 200           | NMOS       | 2                                 | Data Polling,<br>Ready/Busy               | 28-Pin DiP | Now    |

|          | †KM2865AH-25 | 8K×8         | 250           | NMOS       | 2                                 | Data Polling,<br>Ready/Busy               | 28-Pin DIP | Now-   |

|          | †KM2865AH-30 | 8K×8         | 300           | NMOS       | 2                                 | Data Polling,<br>Ready/Busy               | 28-Pin DIP | Now    |

|          | ††KM28C64-15 | 8K×8         | 150           | CMOS       | 10                                | Data Polling,<br>Page Mode                | 28-Pin DIP | TBA    |

|          | ††KM28C64-20 | 8K×8         | 200           | CMOS       | 10                                | Data Polling,<br>Page Mode                | 28-Pin DiP | TBA    |

|          | ††KM28C64-25 | 8K×8         | 250           | CMOS       | 10                                | Data Polling,<br>Page Mode                | 28-Pin DIP | ТВА    |

† New Product

†† Under Development

TBA: To Be Announced

# 8K×8 Bit EEPROM with Latches and Auto-Write

### **FEATURES**

- Simple Byte Write

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- Ready/Busy Output Pin (KM2865A)

- Enhanced Write Protection

- Single 5 volt Supply

- Byte Write: 10ms (max)

- Fast Access Time: 200ns

- Power: 50mA—Standby (max)

120mA—Operating (max)

- Two Line Control-Eliminates Bus Contention

- NMOS Floating Gate Technology

- 10,000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

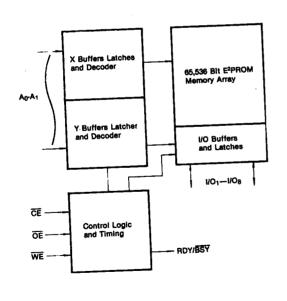

# FUNCTIONAL BLOCK DIAGRAM

## GENERAL DESCRIPTION

The KM2864A/65A is a 65,536 bit Electrically Erasable and Programmable Read-Only-Memory organized as 8,192 words by 8-bits. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM2884A/65A is very simple. The internally self-timed write cycle latches both address and data to provide a free system bus during the 10ms (max) write period.

The KM2864A features DATA Polling, which enables the E2PROM to signal the processor that a write operation is complete without requiring the use of any external hardware. The KM2865A is identical to the KM2864A and in addition has a Ready/Busy output on pin 1 which signals when the write operation is complete.

| Pin Name                        | Pin Function        |

|---------------------------------|---------------------|

| A <sub>0</sub> -A <sub>12</sub> | Address Inputs      |

| 1/01-1/08                       | Data inputs/Outputs |

| CE                              | Chip Enable         |

| ŌĒ                              | Output Enable       |

| WE                              | Write Enable        |

| RDY/BSY                         | Ready/Busy Output   |

| N.C.                            | No Connect          |

| V <sub>cc</sub>                 | Power (+5V)         |

| Vss                             | Ground              |

## 8K×8 Bit High Performance EEPROM with Latches and Auto-Write

#### **FEATURES**

- Simple Byte Write

- Fast Byte Write Time

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- Ready/Busy Output Pin (KM2865AH)

- Enhanced Write Protection

- Single 5 volt Supply

- Byte Write: 2ms (max)

- Fast Access Time: 200ns

- Power: 50mA—Standby (max)

120mA—Operating (max)

- Two Line Control-Eliminates Bus Contention

- NMOS Floating Gate Technology

- 10,000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

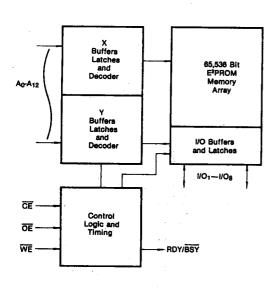

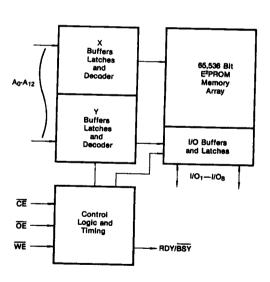

### **FUNCTIONAL BLOCK DIAGRAM**

#### **GENERAL DESCRIPTION**

The KM2884AH/65AH is a 65,536 bit Electrically Erasable and Programmable Read-Only-Memory organized as 8,192 words by 8-bits. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM2864AH/65AH is very simple. The internally self-timed write cycle latches both address and data to provide a free system bus during the 2ms (max) write period.

The KM2864AH features DATA Polling, which enables the E²PROM to signal the processor that a write operation is complete without requiring the use of any external hardware. The KM2865AH is identical to the KM2864AH and in addition has a Ready/Busy output on pin 1 which signals when the write operation is complete. For systems requiring faster byte write time the KM2864AH/65AH is specified at 2ms.

|                       |   | ~ ~ |                     |

|-----------------------|---|-----|---------------------|

| N.C or RDY/BSY        |   |     | 28 V <sub>CC</sub>  |

| A <sub>12</sub> 2     |   |     | 27 WE               |

| A7 3                  |   |     | 26 N.C.             |

| As 4                  |   |     | 25 A <sub>8</sub>   |

| As 5                  |   |     | 24 A9               |

| A4 [8]                |   |     | 23 A <sub>11</sub>  |

| A3 🔽                  |   |     | 22 CE               |

| A <sub>2</sub> 8      | : |     | 21 A <sub>10</sub>  |

| A1 9                  |   |     | 20 CE               |

| Ao 10                 |   |     | 19 1/08             |

| 1/01 11               |   |     | 18 1/07             |

| I/O <sub>2</sub> 12   |   |     | 17 I/O <sub>8</sub> |

| I/O <sub>3</sub> [13] |   |     | 16 1/05             |

| V88 14                |   |     | 15 I/O <sub>4</sub> |

|                       |   |     |                     |

| Pin Name                           | Pin Function        |

|------------------------------------|---------------------|

| A <sub>0</sub> -A <sub>12</sub>    | Address Inputs      |

| I/O <sub>1</sub> —I/O <sub>8</sub> | Data Inputs/Outputs |

| CE                                 | Chip Enable         |

| ŌĒ                                 | Output Enable       |

| WE                                 | Write Enable        |

| RDY/BSY                            | Ready/Busy Output   |

| N.C.                               | No Connect          |

| V <sub>oc</sub>                    | Power (+5V)         |

| Vss                                | Ground              |

## 8K×8 CMOS Electrically Eraseble PROM

#### **FEATURES**

1

- Simple Byte Write

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- -- Ready/Busy Output Pin (KM28C65)

- 32-byte page write: 5mS max

- Effective 150μS/byte write

- Enhanced Write Protection

- Single 5 volt Supply

- Fast Access Time: 150nS

- Power: 100 μA Standby (max)

30 mA Operating (max)

- Two Line Control-Eliminates Bus Contention

- 10.000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

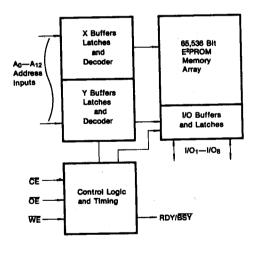

## **FUNCTIONAL BLOCK DIAGRAM**

## **GENERAL DESCRIPTION**

The KM28C64/C65 is a 8,192 × 8 bit electrically erasable and programable Read Only Memory. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM28C84/C85 is very simple. The internally self-timed write cycle latches both address bus during the 5mS (max) write period.

A 32-byte page write enables an entire chip written in 1.3 second.

The KM28C84/C85 features DATA-polling, which enables the EEPROM to signal the processor that a write operation is complete without requiring the use of any external hardware. Ready/Busy is a hardware scheme in which Pin 1 is used to signal the status of the write operation and is especially useful in interrupt driven systems.

The KM28C64/C65 is fabricated with the well defined floating gate CMOS technology using Fowler-Nordheim tunneling for erasing and programming.

| N.C. or<br>RDY/BSY 1<br>A12 2<br>A7 3<br>A6 4<br>A5 5<br>A4 6<br>A3 7<br>A2 8<br>A1 9<br>A0 10<br>I/O <sub>2</sub> 112<br>I/O <sub>2</sub> 112<br>I/O <sub>3</sub> 13 | KM28C64/<br>KM28C65 | 28 VCC<br>27 WE<br>28 N.C.<br>25 As<br>24 As<br>23 A11<br>22 OE<br>21 A10<br>20 CE<br>19 I/Os<br>10 I/Os<br>10 I/Os<br>10 I/Os |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub> 14                                                                                                                                                    |                     |                                                                                                                                |

| Pin Name                          | Pin Function        |

|-----------------------------------|---------------------|

| A <sub>0</sub> A <sub>12</sub>    | Address Inputs      |

| I/O <sub>1</sub> I/O <sub>8</sub> | Data Inputs/Outputs |

| CE                                | Chip Enable         |

| ŌĒ                                | Output Enable       |

| WE                                | Write Enable        |

| RDY/BSY                           | Ready/Busy Output   |

| N.C.                              | No Connect          |

| Vcc                               | + 5V                |

| V <sub>BS</sub>                   | Ground              |

## 8K × 8 CMOS Electrically Erasable PROM

### FEATURES

- Simple Byte Write

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- Ready/Busy Output Pin (KM28C65)

- 32-byte page write: 5ms max

Effective 150 µS/byte write

- Enhanced Write Protection

- Single 5 volt Supply

- Fast Access Time: 150ns

- Power: 100 μA Standby (max)

30 mA Operating (max)

- Two Line Control-Eliminates Bus Contention

- 10,000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

# FUNCTIONAL BLOCK DIAGRAM

## **GENERAL DESCRIPTION**

The KM28C64/C65 is a 8,192 × 8 bit electrically erasable and programmable Read Only Memory. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM28C64/C65 is very simple. The internally self-timed write cycle latches both address bus during the 5mS (max) write period.

A 32-byte page write enables an entire chip written in 1.3 second.

The KM28C64/C65 features DATA-polling, which enables the EEPROM to signal the processor that a write operation is complete without requiring the use of any external hardware. Ready/Busy is a hardware scheme in which Pin 1 is used to signal the status of the write operation and is especially useful in interrupt driven systems.

The KM28C64/C65 is fabricated with the well defined floating gate CMOS technology using Fowler-Nordheim tunneling for erasing and programming.

| Pin Name                       | Pin Function        |

|--------------------------------|---------------------|

| A <sub>0</sub> A <sub>12</sub> | Address Inputs      |

| 1/01-1/08                      | Data Inputs/Outputs |

| CE                             | Chip Enable         |

| ŌĒ                             | Output Enable       |

| WE                             | Write Enable        |

| RDY/BSY                        | Ready/Busy Output   |

| N.C.                           | No Connect          |

| V <sub>cc</sub>                | + 5V                |

| Vss                            | Ground              |

## 8K×8 Bit EEPROM with Latches and Auto-Write

#### **FEATURES**

- Simple Byte Write

- Fast Byte Write Time

- Single TTL Level Write Signal

- Latched Address and Data

- Automatic Internal Erase-before-Write

- Automatic Write Timing

- DATA Polling and Verification

- Ready/Busy Output Pin

- Enhanced Write Protection

- Single 5 volt Supply

- Byte Write: 10ms (max)—KM2865A

2ms (max)—KM2865AH

- Fast Access Time: 200ns

- Power: 50mA—Standby (max)

120mA—Operating (max)

- Two Line Control-Eliminates Bus Contention

- 10,000 Cycle Endurance

- JEDEC Byte-wide Memory Pinout

## FUNCTIONAL BLOCK DIAGRAM

## **GENERAL DESCRIPTION**

The KM2865A/AH is a 65,536 bit Electrically Erasable and Programmable Read-Only-Memory organized as 8,192 words by 8-bits. Its data can be modified using simple TTL level signals and a single 5 volt power supply.

Writing data into the KM2865A/AH is very simple. The internally self-timed write cycle latches both address and data to provide a free system bus during the write period which is 10ms (max) for the KM2865A or 2ms (max) for the KM2865AH.

The KM2865A/AH features two end of write detection schemes to provide maximum design flexibility white enhancing the system performance. DATA Polling is a software scheme to detect the early completion of a write cycle without using any additional hardware. Ready/Busy is a hardware scheme in which Pin 1 is used to signal the status of the write operation and is especially useful in interrupt driven systems.

The KM2865A/AH is fabricated with the well defined floating gate NMOS technology using Fowler-Nordheim tunneling for erasing and programming.

| A1 6 20 CE A0 10 19 1/08 1/01 11 18 1/07 1/02 12 177 1/06 1/03 13 18 1/05 | A12 2<br>A7 3<br>A6 4<br>A5 5<br>A4 6<br>A3 7<br>A2 8            | 28 V <sub>CC</sub> 27 WE 28 N.C. 25 As 24 As 23 At1 22 OE 21 At0                                                                                                                         |

|---------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss 14 15 I/O <sub>4</sub>                                                | A7 3 A6 4 A5 5 A4 6 A3 7 A2 8 A1 9 A0 10 1/01 11 1/02 12 1/03 13 | 28) N.C. 25) A <sub>8</sub> 24) A <sub>9</sub> 23) A <sub>11</sub> 22) OE 21) A <sub>10</sub> 20] CE 19] I/O <sub>8</sub> 18] I/O <sub>7</sub> 17] I/O <sub>6</sub> 18] I/O <sub>5</sub> |

| Pin Name                           | Pin Function        |

|------------------------------------|---------------------|

| A <sub>0</sub> -A <sub>12</sub>    | Address Inputs      |

| I/O <sub>1</sub> —I/O <sub>8</sub> | Data Inputs/Outputs |

| CE                                 | Chip Enable         |

| ŌĒ                                 | Output Enable       |

| WE                                 | Write Enable        |

| RDY/BSY                            | Ready/Busy Output   |

| N.C.                               | No Connection       |

| Vcc                                | Power (+5V)         |

| Vss                                | Ground              |