## **High Performance Non-Isolated Buck PFC Controller**

#### **FEATURES**

- Low Cost LED Driver Solution with Typical

Non-Isolated Buck PFC

- Quasi-Resonant Switching to Achieve >90%

Efficiency

- Accurate LED Output Current <±1% Control with Universal Input</li>

- Proprietary Constant On-time Control for PF>0.97

- Proprietary ZCD Method to Save Auxiliary

Winding Design

- Building-in Complete Protection:

- LED Open and Short Protection

- Cycle-by-Cycle Over Current Protection

- OVP for IC Bias Voltage

- Maximum and Minimum Switching Frequency Limit

- o Built-in Thermal Protection

- RoHS Compliant and Halogen Free

- I Available with SOT23-6 Package

#### **APPLICATIONS**

- **I** LED Driver Power Supplies

- I Commercial and Residential LED Fixtures

- Non isolated Applications E27, PAR30,

- I Offline LED Lights

- 5w-35w typical application.

#### **GENERAL DESCRIPTION**

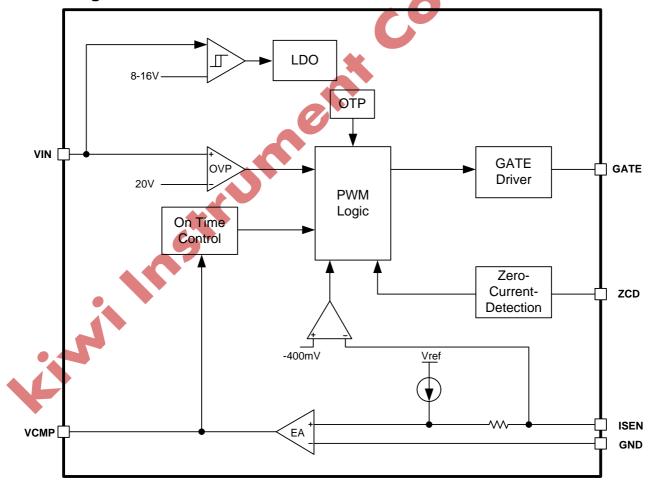

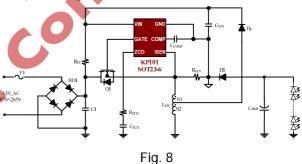

KP101 is a pulse-width modulated (PWM) controller with integrated high side floating gate driver. This switching mode power supply controller is intended for driving low to medium power single stage power factor corrected (PFC) LEDs. The devices operate in boundary mode and are suitable for buck topologies. Constant on-time boundary mode control scheme guarantees high power factor and low gate turn-on loss. Build-in gate control limits the switching frequency range from 16 kHz to 200 kHz, solving the audible noise and high switching loss issue inherited from boundary mode operation: the switching frequency will change with variation of line voltage, load voltage or load current.

The devices feature a gate driver, duty cycle limiter, error amplifier, PWM control circuitry and protection functions, as well as the proprietary zero cross detection (ZCD) technique required to implement a boundary mode switch power supply. The accurate output LED current is achieved by an average current feedback loop. The fault protection features include Under Voltage Lockout (UVLO), Over Current Protection (OCP), Over Voltage Protection (OVP) and thermal protection function (OTP). Moreover, for high efficiency, the device features low startup current enabling fast, low loss charging of the VIN capacitor.

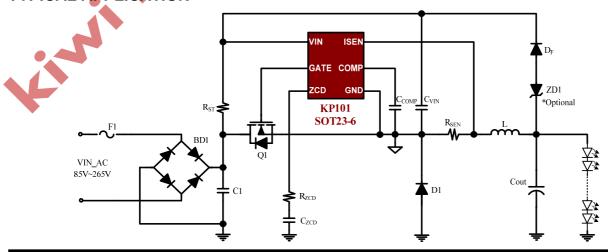

#### TYPICAL APPLICATION

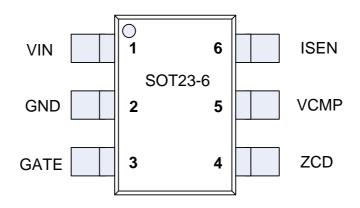

## **Pin Configuration**

## **Pin Description**

| Pin Num | Pin Name | I/O | Description                                                                                                                                                                                              |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VIN      | I   | Power Supply Pin of the Chip. The circuit starts to operate when VIN goes above 16V and turns off when VIN goes below 8V. After startup, the operating range is recommended to be from 10V to 18V.       |

| 2       | GND      | Р   | Ground of the Chip.                                                                                                                                                                                      |

| 3       | GATE     | 0   | Gate Driver for External MOSFET Switch.                                                                                                                                                                  |

| 4       | ZCD      | ı   | Zero-Current-Direction Pin. Typically a 2M ohm resistor and a 1pF capacitor are recommended to be connected between ZCD Pin and Power Ground of the LED output, which needs fine-tuned in actual design. |

| 5       | VCMP     | I   | Control loop Compensation Pin.                                                                                                                                                                           |

| 6       | ISEN     | I   | LED Current Sense Input Pin. Typical internal current reference threshold is -90mVand a resistor is used to sensing the averaged output current.                                                         |

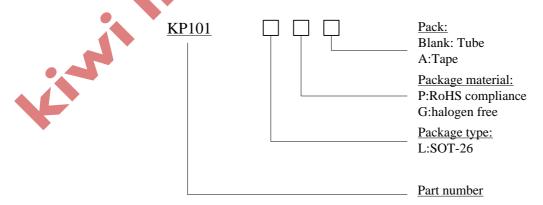

**Ordering Information**

| Part Number | Description                                |

|-------------|--------------------------------------------|

| KP101LGA    | SOT23-6, Halogen free in T&R, 3000Pcs/Reel |

## **Marking Information**

## SOT-26 Mark Spec

## **Block Diagram**

**Absolute Maximum Ratings** (Note 1)

| Rating                                       | Symbol | Value       | Unit |  |  |  |

|----------------------------------------------|--------|-------------|------|--|--|--|

| Supply Input Voltage                         | VIN    | 20.5        | V    |  |  |  |

| GATE Voltage                                 | GATE   | 14          | V    |  |  |  |

| ZCD Voltage                                  | ZCD    | 6           | V    |  |  |  |

| Compensation Voltage                         | VCMP   | 6           | V    |  |  |  |

| Current Sense Voltage                        | SENSE  | -0.350 to 6 | V    |  |  |  |

| Power dissipation, @ TA = 25°C SOT-23-6      | PD     | 0.350       | W    |  |  |  |

| Package Thermal Resistance SOT-23-6 (Note 2) | RθJA   | 255         | °C/W |  |  |  |

| Junction Temperature                         | TJ     | 150         | °C   |  |  |  |

| Lead Temperature (Soldering, 10 s)           | TL     | 260         | °C   |  |  |  |

| Storage Temperature Range                    | TSTG   | -65 to 150  | °C   |  |  |  |

| ESD Susceptibility (Note 3)                  |        |             |      |  |  |  |

| ESD Capability, HBM (Human Body Model)       | HBM    | 3500        | V    |  |  |  |

| ESD Capability, MM (Machine Model)           | MM     | 350         | V    |  |  |  |

**Recommended Operation Conditions** (Note 2)

| Rating                        | Symbol | Value      | Unit |

|-------------------------------|--------|------------|------|

| Supply Input Voltage          | VIN    | 10.2 to 20 | V    |

| Junction Temperature          | ŢJ     | -40 to 150 | °C   |

| Operating Ambient Temperature | OAT    | -40 to 125 | °C   |

## ELECTRICAL CHARACTERISTICS (Ta=25°C, unless otherwise noted)

| Parameter                                  | Symbol              | Test Conditions                             | Min | Тур  | Max | Unit |

|--------------------------------------------|---------------------|---------------------------------------------|-----|------|-----|------|

| Input Start-up voltage                     | Vin_on              | ~                                           |     | 16   |     | V    |

| Under Voltage<br>Lockout Threshold         | V <sub>IN_OFF</sub> |                                             | 1   | 8    | 1   | V    |

| Maximum Startup<br>Current                 | ST(MAX)             |                                             | 1   |      | 150 | uA   |

| Input Supply<br>Current                    | lcc                 | After Start-Up with switching, VCC = 15V    | 1   | 1    | 3   | mA   |

| Input Quiescent<br>Current                 | l <sub>ac</sub>     | After Start Up without switching, VCC = 15V | 1   | 100  | 1   | uA   |

| Input Over Voltage<br>Protection threshold | $V_{IN_{OV}}$       |                                             | 1   | 20   | 1   | V    |

| Current Sense<br>Reference Voltage         | $V_{I\_ref}$        |                                             |     | 90   |     | mV   |

| Maximum Switching Frequency                | f <sub>SW_MAX</sub> |                                             |     | 200  |     | kHz  |

| Minimum Switching Frequency                | F <sub>sw_MIN</sub> |                                             |     | 16   |     | kHz  |

| Over current protection level              | $V_{CP}$            |                                             |     | -400 |     | mV   |

# KP101 High Performance Non-Isolated Buck PFC Controller

| Minimum Turn-On<br>Time                  | t <sub>ON(MIN)</sub>                      |                    | <br>300         |     | ns |

|------------------------------------------|-------------------------------------------|--------------------|-----------------|-----|----|

| Maximum On Time                          | t <sub>on_max</sub>                       |                    | 13.6            |     | us |

| GATE Pin Voltage                         | $V_{\sf GATE}$                            |                    | <br>13.5        | -1  | <  |

| GATE Drive Rise<br>and Fall Time         | T <sub>R</sub> /T <sub>F</sub>            | 1.0nF Load at GATE | <br>            | 100 | ns |

| GATE Drive Source<br>/ Sink Peak Current | I <sub>Source</sub><br>/I <sub>Sink</sub> | 1.0nF Load at GATE | <br>0.5<br>/0.8 |     | А  |

| Thermal Shutdown<br>Temperature          | T <sub>SD</sub>                           |                    | 96              | 140 | °C |

| Thermal Shutdown<br>Hysteresis           | T <sub>SDH</sub>                          |                    | 80              |     | °C |

**Note1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

**Note2.** R<sub>BJA</sub> is measured in natural convection at  $T_A = 25^{\circ}C$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note3. Devices are ESD sensitive. Handling precaution is recommended.

Note4. The device is not guaranteed to function outside its operating conditions.

#### **OPERATION DESCRIPTION**

The KP101 is a high side buck type PWM LED driver controller for high performance non-isolated LED application. Its high side floating gate driver is used to control the buck converter via an external MOSFET and regulate the constant output current. The KP101 can achieve high accuracy LED output current via the average current feedback loop control and high power factor by the constant on time Active PFC control.

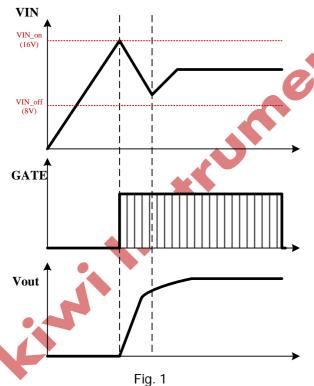

#### I Start-Up Operation

Before the operation, the VIN Cap is charged through the start-up resistor for KP101. When the VIN voltage reaches the threshold of  $V_{\text{IN\_ON}}$  (16V typically), the chip is enabled and GATE begins to switch; after that the VIN cap is to be discharged due to the increased operation current of the IC which will be continued until the VIN cap voltage is taken controlled by the built-up output voltage.

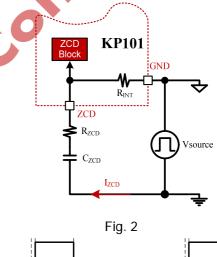

#### Quasi-Resonant Operation Mode

KP101 utilized the Quasi-Resonant Operation Mode to achieve high efficiency and better EMI performance compared with conventional PWM

#### Control.

Internally a resistor  $R_{\text{INT}}$  is connected between GND Pin and ZCD Pin which is used to sense the dynamic current flowing through the IC GND Pin and the Output Ground. Shown as Fig.2, a resistor and a capacitor are also needed to be connected between the ZCD Pin and the output Ground. When the inductor current reaches zero, the polarity of the voltage source  $V_{\text{source}}$  is changed from  $+V_F$  to  $-V_o$  which will cause a negative current flowing through the resistor of  $R_{\text{INT}}$  and ZCD Pin voltage starts to fall down. When the voltage of ZCD pin is lower than its internal threshold, the set signal will be triggered by its internal ZCD block and next cycle of GATE signal begins.

GATE

IL

VF

Vsource

Vsource

I<sub>ZCD</sub>

Fig. 3

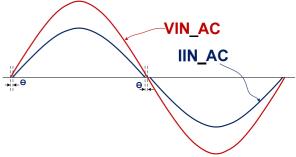

#### **Active Power Factor Correction**

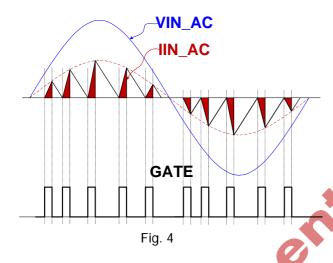

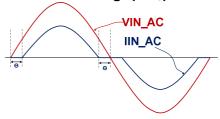

In KP101, the on time of GATE signal is controlled as a constant within a line cycle and the off time of GATE is controlled by the ZCD signal. By this method, the switching frequency varies with the real-time value of AC input voltage and the averaged input voltage becomes sinusoidal to achieve high PF value, which is shown in Fig.4. Normally a large capacitor, such as 100nF, is recommended to be connected to VCMP Pin to keep low bandwidth control loop for High PF.

#### **Setting Average Output Current**

The output current that flows through the LED string is set by an external resistor, RSEN, which is connected between the GND and ISEN Pin. The relationship between average output current, Io, and R<sub>SEN</sub> is shown below:

#### **LED Open Protection**

Normally the power supply of the chip is taken by the AC Line input through the start-up resistor at the beginning of system start and taken by the output voltage through the feedback diode after output voltage becomes high enough.

If the LED is opened, the output current will be charged into the output capacitor only which causes the output voltage and the IC VIN Pin rise up quickly. When the threshold of  $V_{\text{IN\_OV}}$  is triggered, internal logic and GATE signal is shut down. Then the system is latched and next startup is initialed only by re-plug the AC input.

Fig. 5

#### LED Short Protection

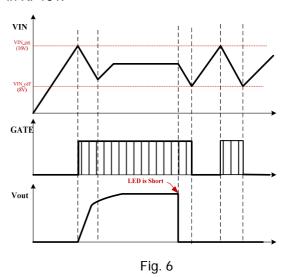

After the LED is short, the output voltage becomes too small to charge the VIN Capacitor and the VIN starts to fall down. When the threshold of  $V_{\text{IN OFF}}$  is triggered, GATE stops switching and VIN is recharged due to the decreased IC operation current through the start up resistor. When the threshold of V<sub>IN ON</sub> is triggered, the GATE starts to work again which will be repeat continuously until the fault condition is removed. By the function, the auto-recovery is realized for LED short Protection in KP101.

#### I Cycle by Cycle Current Limit (OCP)

To limit the peak inductor current value, an internal -400mV threshold is designed in KP101. After the turn on of GATE signal, the inductor current rises up and the ISEN Pin voltage starts to falls down. If the inductor current is too large to cause the ZCD Pin voltage to be lower than -400mV, the GATE will be blocked immediately and next switching cycle will be triggered by the ZCD signal.

#### I Minimum and Maximum Switching Frequency

For constant on time PFC control, the switching frequency varies with the real-time AC input. With the increase of the AC input, the switching frequency becomes smaller; with the decrease of the AC input, the switching frequency becomes larger. To avoid audio noise and decrease the requirement of the EMI filter design, the minimum and maximum switching frequency is limited as 20 kHz and 200 kHz internally in KP101.

#### I Thermal Shut Down

When the IC temperature is over 140 °C, the IC shuts down. Only when the IC temperature drops to 80 °C, the IC restarts to work again.

## COMPONENTS SELECTION FOR BUCK CONVERTER

#### I Start-Up Resistor (R<sub>ST</sub>)

Make sure the current flowing through the  $R_{ST}$  is larger than the IC start-up current  $I_{ST}$  (150uA typically).

$$R_{ST} < \frac{V_{in\_\min}}{I_{ST}}$$

Where:

$V_{in\_min}$ : the minimum peak value of AC input voltage. For universal input,  $V_{in\_min}$  is 120V.

#### I VIN Capacitor (C<sub>VIN</sub>)

To meet the requirement of the start-up time  $T_{\text{ST}}$  (from AC input added to IC starts to work), the VIN capacitor is recommended to be selected by the following equation:

$$C_{VIN} < \frac{(\frac{V_{in\_min}}{R_{ST}} - I_{ST}) \cdot T_{ST}}{V_{IN\_ON}}$$

Normally too much small value of  $C_{VIN}$  will cause too short start-up time. But too much small value of  $C_{VIN}$  will cause the first time start-up failed. If the capacitor of  $C_{VIN}$  is not big enough and secondary-start-up happens, go back to re-select the start-up resistor until the ideal start-up sequence is obtained.

#### I VCMP Capacitor (C<sub>CMP</sub>)

Generally a large enough capacitance of  $C_{\text{COMP}}$  is needed to achieve high power factor (100nF typically). Usually larger capacitance of  $C_{\text{COMP}}$  can provide bigger phase margin for the control loop which also make the start-up time larger at the same time.

#### I PFC Inductor Design(L<sub>PFC</sub>)

Fig. 7

For buck PFC converter, a dead conduction angle always exists when the real-time input voltage is smaller than the output voltage. Then the input power can only be transferred to the output within the conduction angle of  $\pi$ -2 $\Theta$ . According to the power balance rule, the PFC inductor can be calculated by the following equation:

$$L_{pFC} = \frac{V_o \cdot h}{2p \cdot F_{sw\_min} \cdot I_o} (\frac{p}{2} - \frac{V_o}{V_{in\_min}^2} \cdot \sqrt{V_{in\_min}^2 - V_o^2} - \arcsin(\frac{V_o}{V_{in\_min}}))$$

NATION OF STATE OF THE PROPERTY OF THE PROPE

V<sub>in\_min</sub>: The minimum peak value of AC input voltage. For universal input (85Vac-265Vac), V<sub>in min</sub> is 120V.

F<sub>sw\_min</sub>: The pre-set minimum switching frequency. 40 kHz is recommended for universal input and 80 kHz for narrow input.

Vo: The DC output voltage

I<sub>o</sub>: The averaged output LED current.

$\eta$  : The pre-set overall efficiency, 0.95 is recommended as typically value.

The peak current for the PFC inductor, Power MOSFET and Diode is:

$$I_{PK} = \frac{V_{in\_\min} - V_o}{F_{sw\_\min} \cdot L_{PFC}} \cdot (\frac{V_o}{V_{in\_\min}})$$

#### I Output Capacitor (Cout)

For PFC converter, two times of AC line frequency voltage ripple should be observed on the output capacitor which value is related to the output current  $I_o$ , peak to peak output voltage ripple  $\Delta\,V_o$ , AC line frequency  $f_{ac}$  and system efficiency  $\eta$ :

$$C_{out} = \frac{I_o}{h \cdot 4p \cdot f_{ac} \cdot \Delta V_o}$$

#### I MOSFET and Diode Selection

When the circuit is working with the maximum AC line input voltage, the voltage stress of the MOSFET and Diode is maximum; when the circuit is working with minimum AC line input voltage and full load condition, the current stress is maximum.

For MOSFET:

$$V_{DS\_MAX} = \sqrt{2} \cdot V_{in\_\max}$$

$$I_{DS\_MAX} = I_{PK}$$

For Diode:  $V_{DR\_MAX} = \sqrt{2} \cdot V_{in\_\max}$   $I_{DF\_MAX} = I_{PK}$

Where:

V<sub>in\_min</sub>: The maximum peak value of AC input voltage. For universal input (85Vac-265Vac), V<sub>in max</sub> is 265V.

# COMPONENTS SELECTION FOR BUCK/BOOST CONVERTER

For high voltage output application, the dead conduction angle will become very large which should greatly decrease the Power Factor Value and increase the THD. So for KP101, it's recommended to use buck/boost topology for output voltage >60V cases.

For the selection of  $R_{\text{st}}$ ,  $C_{\text{vin}}$ , and  $C_{\text{comp}}$ , the calculation method is the same with buck converter above.

## I PFC Inductor Design(L<sub>PFC</sub>)

Compared with buck converter, there's only a small dead conduction angle for buck/boost converter which is caused by the filter capacitor after the rectifier bridge diode and can be ignored during the circuit parameter calculation.

Fig. 9

The calculation of PFC inductance for buck/boost converter can be:

$$L_{PFC} = \frac{h}{2 \cdot F_{sw \text{ min}} \cdot P_O} \left( \frac{V_{in \text{-min}} \cdot V_o}{V_o + \sqrt{2} \cdot V_{in \text{-min}}} \right)^2$$

Where:

V<sub>in\_min</sub>: The minimum peak value of AC input voltage. For universal input (85Vac-265Vac), V<sub>in\_min</sub> is 85V.

F<sub>sw\_min</sub>: The pre-set minimum switching frequency. 40 kHz is recommended for universal input and 80 kHz for narrow input.

Vo: The DC output voltage

I<sub>o</sub>: The averaged output LED current.

$\eta$ : The pre-set overall efficiency, 0.95 is recommended as typically value.

The peak current for the PFC inductor, Power MOSFET and Diode is:

$$I_{PK} = L_{PFC} \cdot \frac{V_o}{(\sqrt{2} \cdot V_{in \min} + V_o) \cdot F_{sw \min}}$$

#### I MOSFET and Diode Selection

When the circuit is working with the maximum AC line input voltage, the voltage stress of the MOSFET and Diode is maximum; when the circuit is working with minimum AC line input voltage and full load condition, the current stress is maximum.

For MOSFET:

$$V_{DS\_MAX} = \sqrt{2} \cdot V_{in\_max} + V_o$$

$$I_{DS\_MAX} = I_{PK}$$

For Diode:

$$V_{DR\_MAX} = \sqrt{2} \cdot V_{in\_max} + V_o$$

$$I_{DF\_MAX} = I_{PK}$$

Where:

V<sub>in\_min</sub>: The maximum peak value of AC input voltage. For universal input (85Vac-265Vac), V<sub>in\_max</sub> is 265V.

#### I Output Capacitor (Cout)

For PFC converter, two times of AC line frequency voltage ripple should be observed on the output capacitor which value is related to the output current  $I_0$ , peak to peak output voltage ripple  $\Delta V_0$ ,

AC line frequency  $f_{ac}$  and system efficiency  $\eta$ :

$$C_{out} = \frac{I_o}{h \cdot 4p \cdot f_{ac} \cdot \Delta V_o}$$

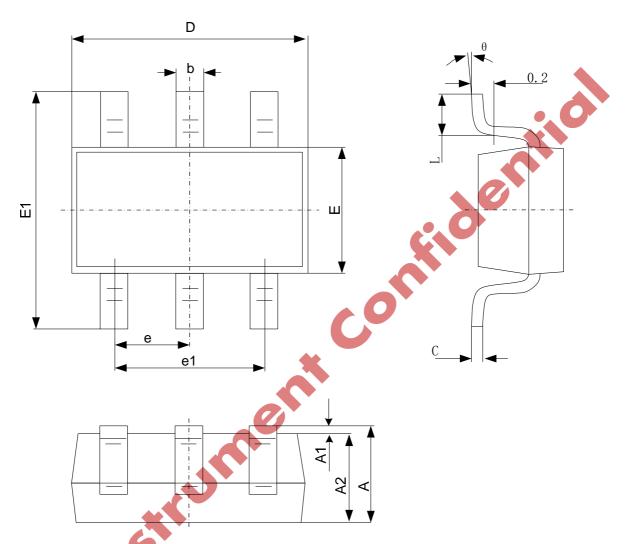

## **Package Dimension**

### **SOT23-6**

| Cumbal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| A      | 0.900        | 1.200         | 0.035                | 0.047 |  |

| A1     | 0.000        | 0.150         | 0.000                | 0.006 |  |

| A2     | 0.900        | 1.100         | 0.035                | 0.043 |  |

| b      | 0.300        | 0.500         | 0.012                | 0.020 |  |

| C      | 0.100        | 0.200         | 0.004                | 0.008 |  |

| D      | 2.800        | 3.020         | 0.110                | 0.119 |  |

| E      | 1.500        | 1.700         | 0.059                | 0.067 |  |

| E1     | 2.600        | 3.000         | 0.102                | 0.118 |  |

| е      | 0.950 (BSC)  |               | 0.037 (BSC)          |       |  |

| e1     | 1.800        | 2.000         | 0.071                | 0.079 |  |

| L      | 0.300        | 0.600         | 0.012                | 0.024 |  |

| θ      | 0°           | 8°            | 0°                   | 8°    |  |

#### **Kiwi Instruments Corporation**

**US** Headquarter 1772 Clear Lake Ave, STE 202 Milpitas, CA, 95035

Tel: (1) 408-475-6888 Fax: (1)408-905-6912

Email: marketing@kiwiinst.com

#### China office:

Marketing/Field Support B302-B303, University Creative Park, Xili Rd., Nanshan District, Shenzhen, P.R.C

Tel: (86)755-8204-2689 Fax: (86)755-82042192

Email: marketing@kiwiinst.com.cn