**Color Television Receiver**

Model: KS21TK305A

# **CONTENTS**

| I. IMPORTANT SERVICE SAFETY INFORMATION       | 3          |

|-----------------------------------------------|------------|

| II. ALIGNMENT PROCEDURES PLEASE READ BEFORE A | ATTEMPTING |

| SERVICE                                       | 5          |

| III. TV SPECIFICATION                         | 5          |

| IV. TV ADJUSTMENT                             | 7          |

| V. IC INFORMATION                             | 12         |

| 1. PHILIPS UOCIII CHIP (N603)                 | 12         |

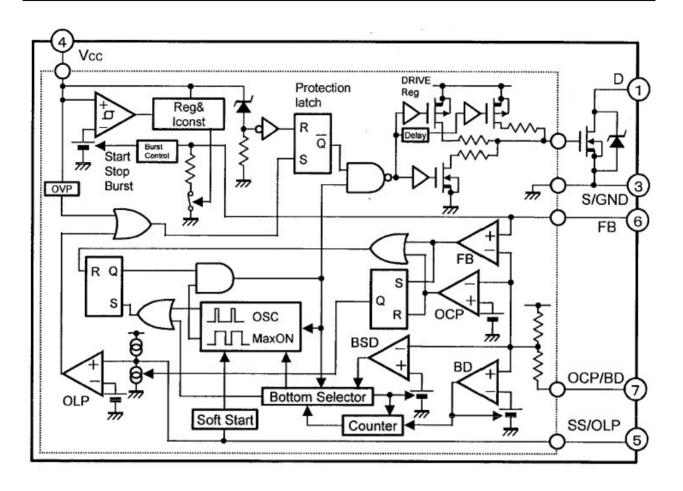

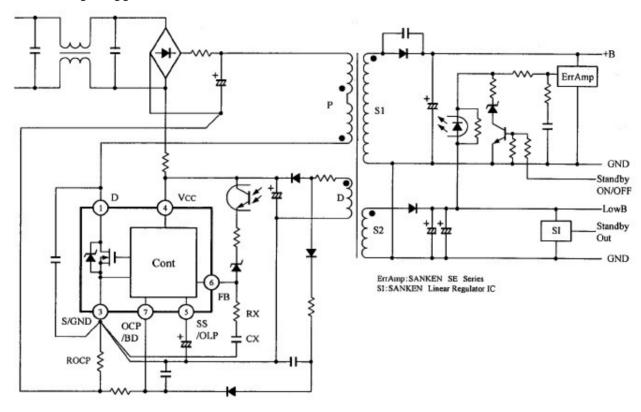

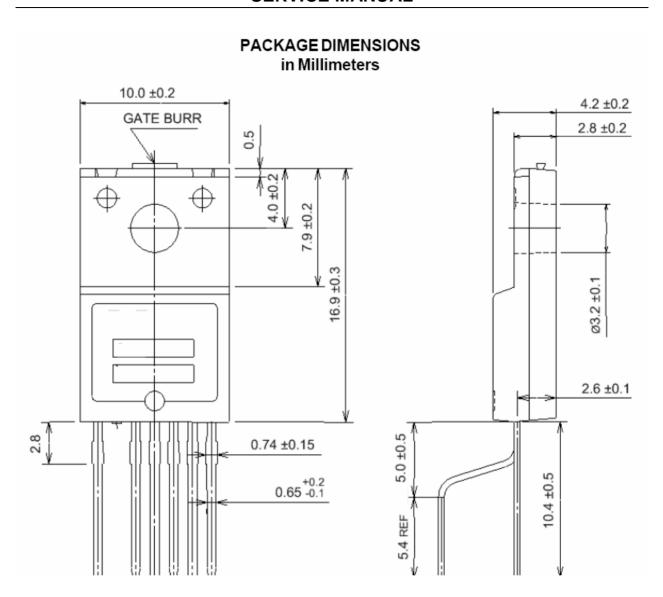

| 2. SWITCH POWER IC (N901)                     | 41         |

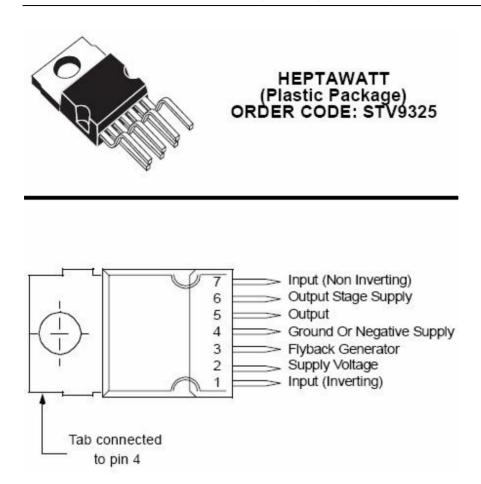

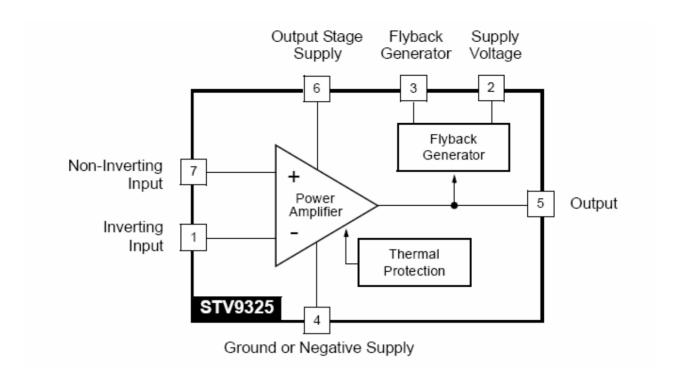

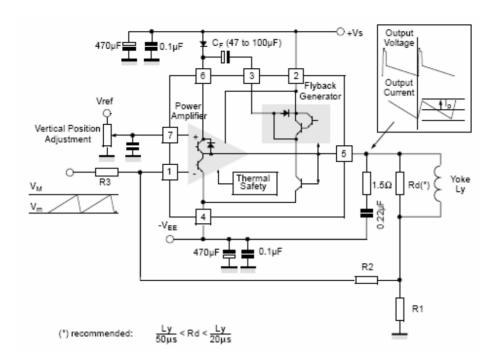

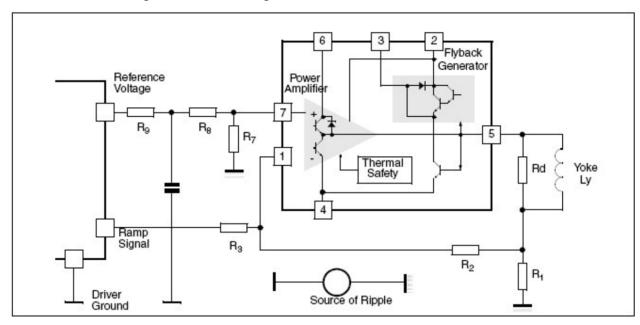

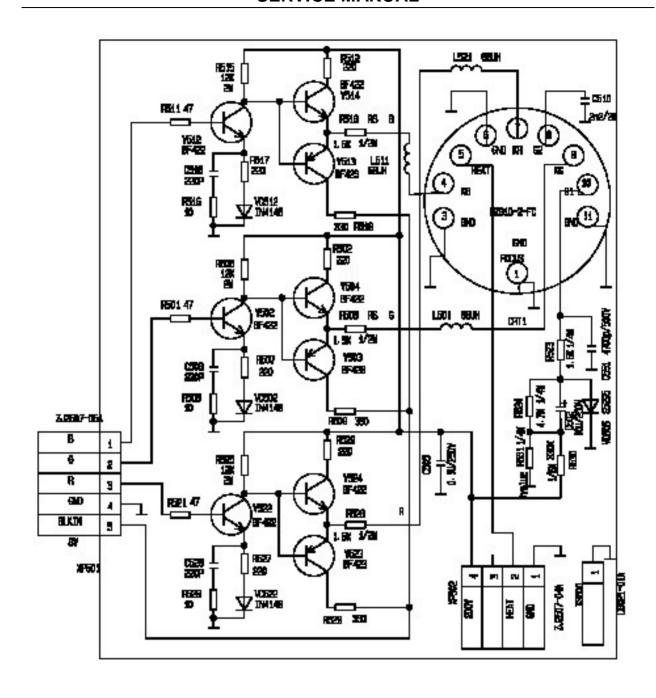

| 3. VERTICAL DEFLECTION BOOSTER (N401)         | 45         |

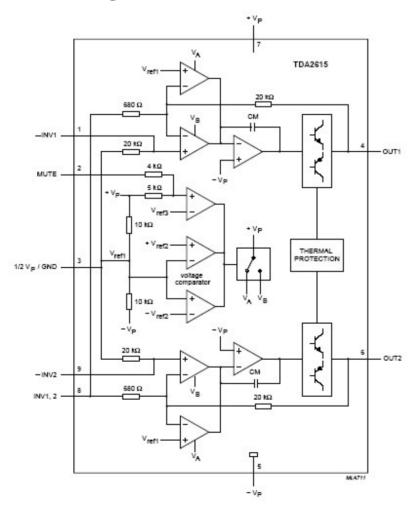

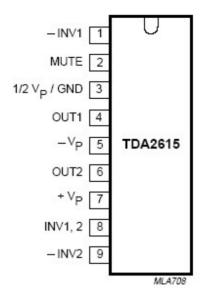

| 4. AUDIO POWER AMPLIFIER (N202)               | 49         |

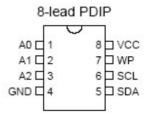

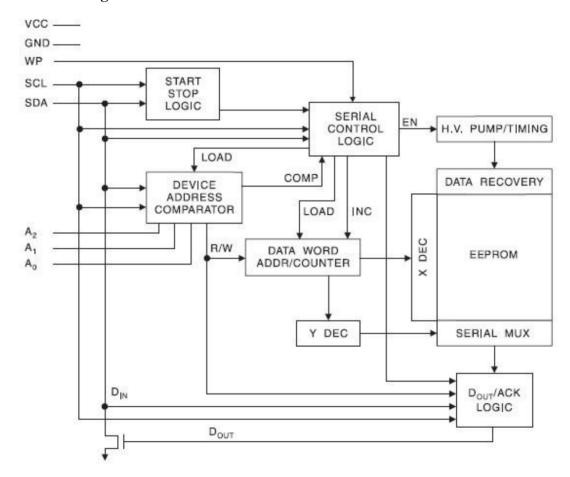

| 5. EEPROM 24C16 (N602)                        | 52         |

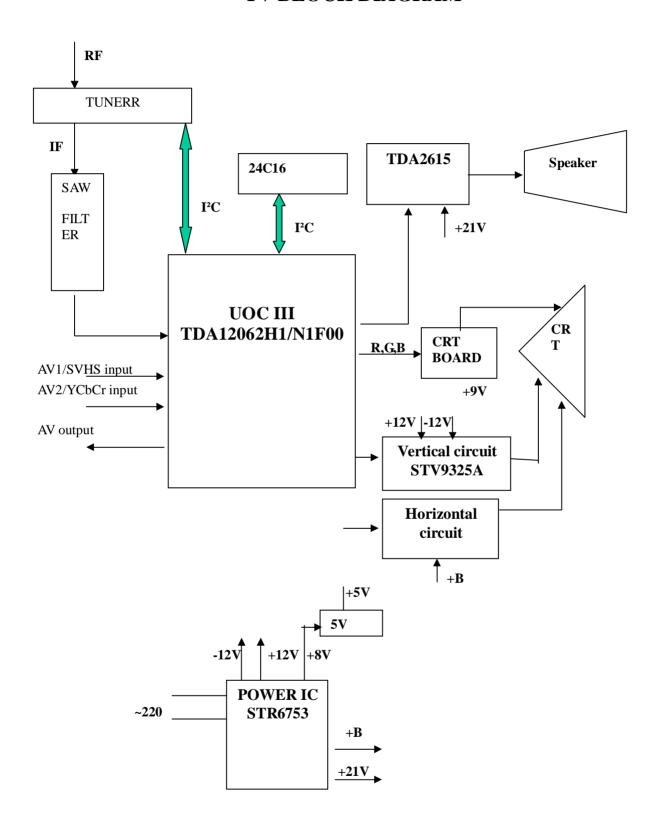

| VI. TV BLOCK DIAGRAM                          | 57         |

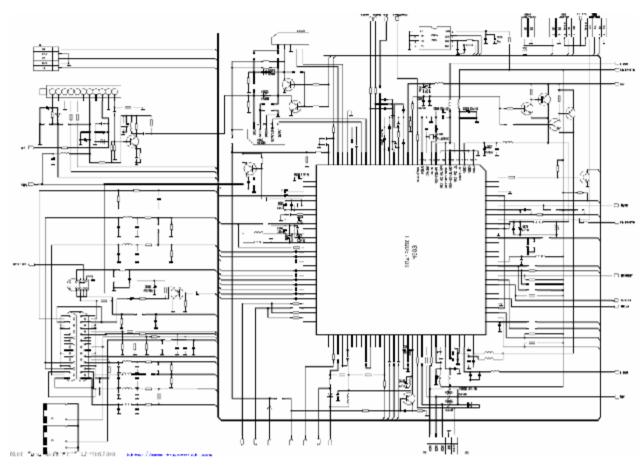

| Appendix 1: Schematic Circuit Diagram         | 58         |

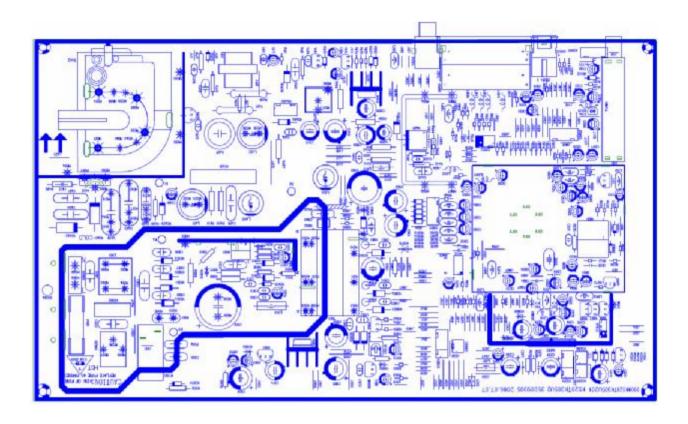

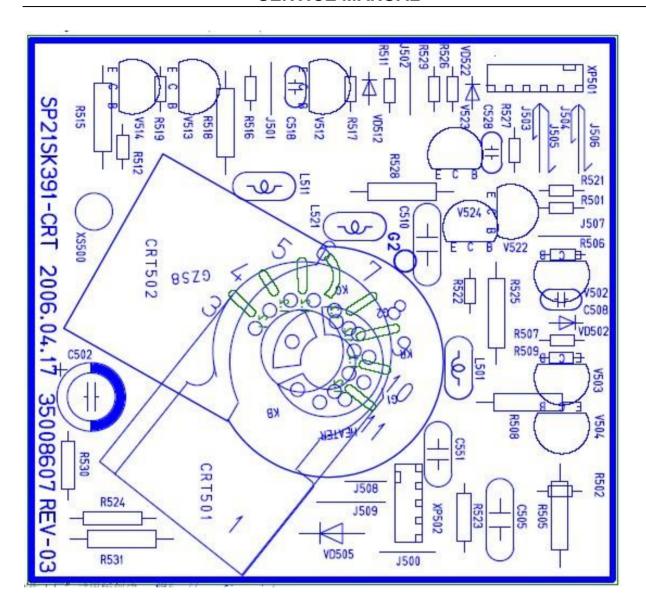

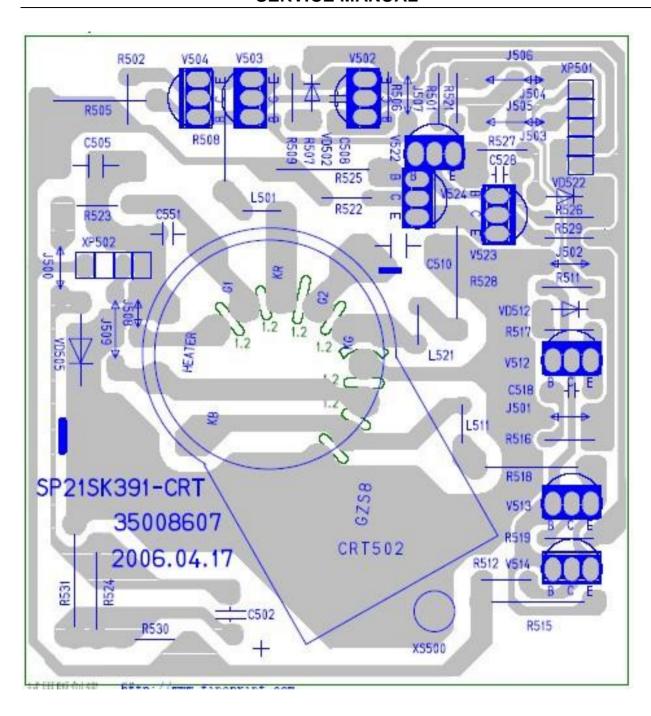

| Appendix 2: PCB Layout Diagram                | 59         |

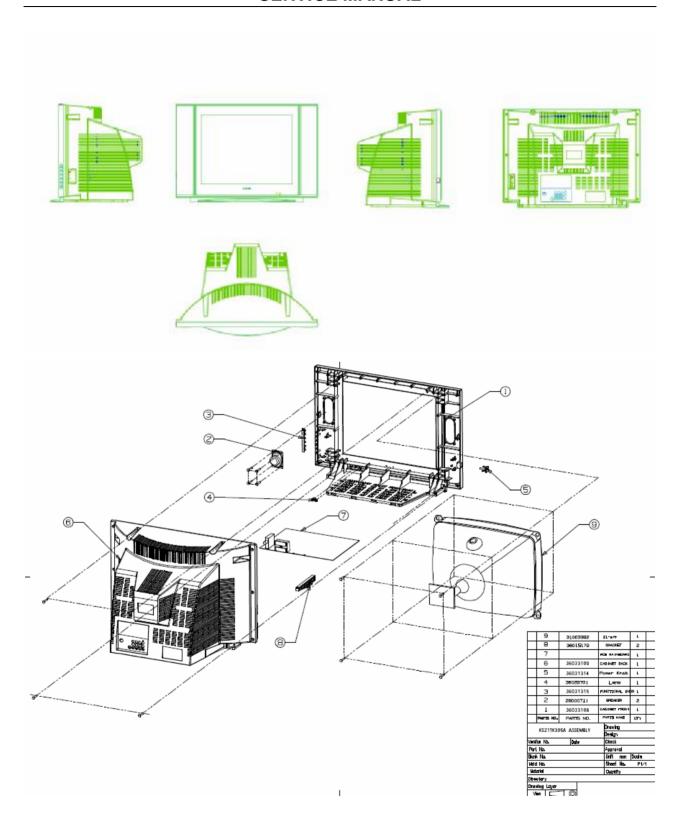

| Appendix 3: Exploded Views                    | 63         |

#### IMPORTANT SERVICE SAFETY INFORMATION

Operating the receiver outside of its cabinet or with its back removed involves a shock hazard. Work on these models should only be performed by those who are thoroughly familiar with precautions necessary when working on high voltage equipment.

Exercise care when servicing this chassis with power applied. Many B plus and high voltage RF terminals are exposed which, if carelessly contacted, can cause serious shock or result in damage to the chassis. Maintain interconnecting ground lead connections between chassis, escutcheon, picture tube dag and tuner when operating chassis.

These receivers have a "polarized" AC line cord. The AC plug is designed to fit into standard AC outlets in one direction only. The wide blade connects to the "ground side" and the narrow blade connects to the hot "side" of the AC line. This assures that the TV receiver is properly grounded to the house wiring. If an extension cord must be used, make sure it is of the "polarized" type.

Since the chassis of this receive is connected to one side of the AC supply during operation, service should not be attempted by anyone not familiar with the precautions necessary when working on these types of equipment.

When it is necessary to make measurements or tests with AC power applied to the receiver chassis, an Isolation Transformer must be used as a safety precaution and to prevent possible damage to transistors. The Isolation Transformer should be connected between the TV line cord plug and the AC power outlet.

Certain High voltage (HV) maybe cause X-ray radiation. Receivers should not be operated with HV levels exceeding the specified rating for their chassis type. Higher voltage may also increase the possibility of failure in the HV supply.

It is important to maintain specified values of all components in the horizontal and high voltage circuits and anywhere else in the receive that could cause a rise in high voltage, or operating supply voltages. No changes should be made the original design of the receiver.

Components shown in the shaded areas on the schematic diagram and/or identified by in the replacement parts list should be replaced only with exact factory recommended replacement parts. The use of unauthorized substitute parts man creats may create shock, fire, X-ray radiation, or other hazards.

To determine the presence of high voltage, use an accurate high impedance HV meter connected between the second anode lead and he CRT dag grounding device. When servicing the

High Voltage System remove static charges from it by connecting a 10K Ohm resistor in series Wan insulated wire(such as test probe) between the picture tube dag and 2nd anode lead(Have AC line cord disconnected from AC supply).

The picture tube use in this receiver employ integral implosion protection. Replace with a tube of the same type number for continued safety. Do not lift picture tube by the neck. Handle the picture tube only when wearing shatterproof goggles and after discharging the high voltage completely, Keep others without shatter proof goggles away.

Before returning the receiver to the user, perform the following safety checks:

- 1. Inspect all lead dress to make certain that leads are not pinched or that hardware is not lodged between the chassis and other metal parts in the receiver.

- 2. Replace all protective devices such as non-metallic control knobs, insulating fish-papers, cabinet backs, adjustment and compartment covers of shields, isolation resistor-capacitor networks, mechanical insulators etc.

- 3. To be sure that not shock hazard exists, a check for the presence of leakage current should be made at each exposed metal part having a return path to the chassis (antenna, cabinet metal, screw heads knobs and/or shafts, escutcheon, etc.) in the following manner.

Plug the AC line cord directly into a 110V/240V (or 180V/240V), AC receptacle. (Do not use an Isolation Transformer during these checks.) All checks must be repeated with the AC line cord plug connection reversed. (If necessary, a non-polarized adapter plug must be used only for the purpose of completing these checks.)

If available, measure the current using an accurate leakage current tester. Any reading of 0.35mA or more is excessive and indicates a potential shock hazard which must be corrected before returning the receiver to owner.

If a reliable leakage current tester is not available, this alternate method of measurement should be used. Using two clip leads, connect a 1500 Ohm, 10 watt resistor paralleled by a 0.15MF capacitor in series with a known earth ground, such as a water pipe or conduit and the metal part to be checked. Use a VTVM or VOM with 1000 Ohms per Volt, or higher, sensitivity to measure this AC voltage drop across the resistor,. Any reading of 0.35 volt RMS of more is excessive and indicates potential shock hazard which must be corrected before returning he receiver to the owner.

# ALIGNMENT PROCEDURES PLEASE READ BEFORE ATTEMPTING SERVICE

- 1. Use an Isolation Transformer when performing any service on this chassis.

- 2. Never disconnect any leads while receiver is in operation.

- 3. Disconnect all power before attempting an repairs.

- 4. Do not short any position of the circuit while the power is on.

- 5. For safety reasons, replacing any components should be according with identical replacement parts.

- 6. Before testing, warm up the TV for at least 30 minutes and demagnetize the CRT with an external degaussing coil.

- 7. When removing a PCB or related component, after unfastening or changing a wire, be sure to put the wire back in its original position.

- 8. Inferior silicon grease can damage IC's and transistors. When replacing IC's and transistors, use only specified silicon grease, Remove all old silicon when applying new silicon.

- 9. Before removing the anode cap, discharge drastically because it contains high voltage.

#### TV SPECIFICATION

#### 1. Ambient Conditions:

- 1.1 Ambient Temperatures:

- a. Operating:  $-10 \sim +40$  °C

- b. Storage: -15 ~ +45 °C

- 1.2 Humidity

- a. Operation: <80%

- b. Storage: <90%

- 1.3 Air Pressure: 86kpa ~ 106kpa

#### 2. General Specification

- 2.1 Main IC: PHILIPS UOCIII CHIP (TDA12060 or TDA12062)

- 2.2 TV Broadcasting System:

PAL DK/BG/I

SECAM DK/BG

2.3 Scanning Lines & Frequencies

525 lines/60Hz or 625 lines/50Hz

15.75KHz/15.625KHz

- 2.4 Color Sub-Carrier: 4.433MHz/3.579MHz

- 2.5 IF: Picture 38.9MHz Sound 5.5/6.5MHz

- 2.6 Power Consumption: 75W;

- 2.7 Power Supply: AC 110-240V 50Hz±10%

- 2.8 Audio Output Power (7%THD): 1.5W X 2;

- 2.9 Aerial Input Impedance: 75 Ω Unbalanced Din Jack Ant. Input

#### 3. Basic Features of Controller

- 3.1 Channel Tuning Method: Frequency Synthesizer

- 3.2 Presettable Program: 240 Programs

- 3.3 Tuning for VHF and UHF Bands: Auto Tuning/Manual Tuning

- 3.4 Picture and Sound Adjustment

Bright, Contrast, Color, Sharpness Control and Color Temperature Adjustment

TINT Control (NTSC only)

Volume Control (More controls can do in TV Model 21SL39 and 29F08)

3.5 OSD

General Features (Volume, Brightness, Contrast, Color, Program, Band, Auto Search, Manual

Tune, Muting, AV/TV, Child Lock and Sleep Timer)

AV Stereo

Russia and English Language

- 3.6 Sleep Timer: 5 -120 Minutes with 5 Minutes Increment

- 3.7 Auto Standby When No Broadcasting Signal: 5 minutes

- 3.8 Full Function Infrared Remote Control

- 3.9 Remote Effective Distance: 8m

#### 4. Construction of Front Panel

Main Power Switch

Remote Sensor

Standby Indicator

Menu Select

TV/AV Select

Program and Volume Up/Down

#### 5. TV's Terminals

75 Ω Aerial Terminal

- 3 AV Inputs

- 1 S-Video Input

- 1 Y/U/V Input

- 1 AV Output

#### 6. Other Informations

- 6.1 Magnetic Field:  $Bv = 0.3 \sim 0.65Gs$

- 6.2 Standard Colour Temperature: 9300K (X = 0.284, Y = 0.299)

#### TV ADJUSTMENT

#### **Test Equipment**

- 1. Oscilloscope

- 2. Multifunction meter (Internal resistance: DC $\geq$ 20k $\Omega$ /V AC $\geq$ 5k $\Omega$ /V )

- 3. High voltmeter: 35kV

- 4. Standard Signal Generator

- 5. Degaussing coil

#### Factory menu

Some adjustments must be performed in the Factory menu. You can enter the Factory menu in the following way:

1. Press the MENU button on the remote control then press the Q.VIEW button on the remote

control at least 5 times immediately.

- 2. Press the MENU buttons to select the desired Factory menu pages or press 0-9 number buttons to enter the Factory menu pages directly and then press the PROG+/- buttons to select the desired items.

- 3. Press the VOL+/- buttons to change the settings.

#### **B+ Adjustment**

Test Equipment: Multifunction meter

- 1. Operate the TV set with AC 110-240V(50/60Hz).

- 2. Receive Television broadcast signal, set PICTURE to Normal mode.

- 2. Connect the multifunction meter + lead to C960 and GND. Adjust the RP950 until the meter reading the proper DC value: B+=115±0.5Vdc.

#### High voltage check and filament voltage check

Test Equipment: High voltmeter

- 1. Make sure AC power supply and +B are within pointed range before calibrating high voltage.

- 2. Connect high voltmeter to anode (G4) of CRT.

- 3. Turn on the TV, set the BRIGHTNESS and CONTRAST to the minimum (zero beam current), swap to AV mode (No any signal applied).

- 4. High voltage please see the related model BOM.

- 5. Filament voltage measured by virtual value meter please see the related model BOM, usually within the range of 6.3±0.2Vrms.

#### Grid voltage adjustment

1. Enter into FAC3 and select VG2, then adjust potentiometer to IN/OUT flash on the screen.

VG2 XX Please see the related model BOM

VSD Brightness XX Please see the related model BOM

VSD XX Please see the related model BOM

2. Receive PHILIPS five circles pattern after settings finishing, set PICTURE to Normal mode.

#### RF AGC adjustment

- 1. Receive a 60dBµV gray scale signal(PAL or SECAM).

- 2. Enter Factory menu and select AGC TAKE OVER, then adjust it until the picture noise is just disappeared.

#### **FOCUS** adjustment

- 1. Receive five circles pattern, adjust the pattern to Normal mode.

- 2. Adjust focus potentiometer (horizontal output transformer) so that the center and four corners of pattern are the best focus.

# Horizontal scanning, vertical scanning and geometry correction adjustment (adjust with PAL/SECAM and NTSC signal separately)

1. Receive five circles pattern signal, enter into factory menu to call up FAC2.

**VERT SLOPE** 50(60) XX Adjust it so that horizontal midline of the pattern superpose with the black edge of the pattern.

**VERT SHIFT** 50(60) XX Adjust it so that the pattern midline superposes over CRT

geometric center.

**VERT AMPLE** 50(60) XX Adjust it so that the picture vertical reproduction display ratio

is more than 92%.

S CORR 50(60) XX Adjust it so that upper pane and bottom pan of the pattern are

the same as the middle pane.

**V.LIN.CTRL** 50(60) 0

V. LINEARITY 50 (60) XX Adjust vertical linear.

**VERT ZOOM** 50(60) 25 Adjust vertical amplitude (fixed value 25).

2. Call up FAC1

**EW WIDTH** 50 (60) XX Adjust it so that the picture horizontal reproduction display ratio is more than 92% (H- size adjustment).

**HOR.SHIFT** 50 (60) XX Adjust it so that the left half is symmetrical with the right half (H. CEN correction).

**EW PARABOLA** 50 (60) XX Adjust it so that parallelogram will be transformed to rectangle or trapezium (Receive cross hatch signal)(Parallelogram correction).

**TRAPEZIUM** 50 (60) XX Adjust it so that trapezium distortion is just disappeared (Receive cross hatch signal)(Trapezium).

**UC PARABOLA** 50(60) XX Adjust it so that upper corner (left and right) vertical line are straight line (Receive cross hatch signal)(Upper corner pincushion).

**LC PARABOLA** 50 (60) XX Adjust it so that bottom corner (left and right) vertical line are straight line (Receive cross hatch signal)(Bottom correction pincushion).

**HOR.BOW** 50 (60) XX Adjust it so that vertical line is the straight line.(Receive cross hatch signal) (Bow correction).

PARALLEL 50 (60) XX Adjust it so that left and right line are straight lines (Pincushion correction).

#### White balance adjustment (PAL or SECAM signal)

- 1. Enter into menu firstly and set COLOR mode to normal.(9300K)

- 2. Enter into AV mode and receive left black right white signal which with color sync signal.

- 3. Plug XS805, adjust it automatically with white balance adjustment software, enter into factory menu when adjustment is OK, then enter into FAC 6. FAC 7. FAC 8 menu to check the following data are consistent with data in computer.

Standard: Color temperature 9300K (X=0.284 Y=0.299) FAC 6

Cold color: Color temperature 12000K (X=0.272 Y=0.279) FAC 8

Warm color: Color temperature 6500K (X=0.313 Y=0.329) FAC 7

| FAC 6<br>ADJ content<br>X=0.284<br>Y=0.299 | value | FAC 7<br>ADJ Content<br>X=0.313<br>Y=0.329 | value | FAC 8<br>ADJ Content<br>X=0.272<br>Y=0.279 | value |

|--------------------------------------------|-------|--------------------------------------------|-------|--------------------------------------------|-------|

| BLOR-N                                     | XX    | BLOR-W                                     | XX    | BLOR-C                                     | XX    |

| BLOG-N | XX | BLOG-W | XX | BLOG-C | XX |

|--------|----|--------|----|--------|----|

| WPR-N  | XX | WPR-W  | XX | WPR-C  | XX |

| WPR-N  | XX | WPG-W  | XX | WPG-C  | XX |

| WPR-N  | XX | WPB-W  | XX | WPB-C  | XX |

# Other factory menu data

|                        |                  |               | TV Model |        |       |  |  |  |  |  |

|------------------------|------------------|---------------|----------|--------|-------|--|--|--|--|--|

| Factory menu           | Item             | 2108<br>21F08 | 1402     | 21SL39 | 29F08 |  |  |  |  |  |

|                        | TXT-ON           | 0             | 0        | 0      | 0     |  |  |  |  |  |

| Factoria               | Teletext lang    | 0             | 0        | 0      | 0     |  |  |  |  |  |

| Factory adjustment4    | Teletext E/W     | 0             | 0        | 0      | 0     |  |  |  |  |  |

| aujustillerit4         | Track. Mode      | 0             | 0        | 0      | 0     |  |  |  |  |  |

|                        | Sub Brightness   | 25            | 25       | 25     | 25    |  |  |  |  |  |

|                        | Main YVolume1    | 22            | 22       | 22     | 22    |  |  |  |  |  |

| Factory                | Main YVolume2    | 44            | 44       | 44     | 44    |  |  |  |  |  |

| adjustment5            | Main YVolume3    | 58            | 58       | 58     | 58    |  |  |  |  |  |

|                        | Main XVolume1    | 22            | 22       | 22     | 22    |  |  |  |  |  |

|                        | Main XVolume2    | 44            | 44       | 44     | 44    |  |  |  |  |  |

| Factory<br>adjustment6 | Max Brightness   | 47            | 47       | 47     | 47    |  |  |  |  |  |

|                        | Max Contrast     | 63            | 63       | 63     | 63    |  |  |  |  |  |

|                        | Max Colour       | 47            | 47       | 47     | 47    |  |  |  |  |  |

| Factory                | RGB              | 10            | 10       | 10     | 10    |  |  |  |  |  |

| adjustment7            | CL               | 4             | 2        | 4      | 8     |  |  |  |  |  |

|                        | RGB-IN           | 0             | 0        | 0      | 0     |  |  |  |  |  |

|                        | DVD1-IN          | 0             | 0        | 1      | 1     |  |  |  |  |  |

| Factory                | AV2-IN           | 0             | 0        | 1      | 1     |  |  |  |  |  |

| adjustment9            | AV3-IN           | 1             | 1        | 1      | 1     |  |  |  |  |  |

|                        | AV1S-IN          | 0             | 0        | 1      | 1     |  |  |  |  |  |

|                        | CBVS-OUT         | 1             | 1        | 1      | 1     |  |  |  |  |  |

|                        | IF               | 3             | 3        | 3      | 3     |  |  |  |  |  |

|                        | TUNER            | 0             | 0        | 0      | 0     |  |  |  |  |  |

| Factory                | HIGH GAIN        | 0             | 0        | 0      | 0     |  |  |  |  |  |

| adjustment10           | QSS              | 0             | 0        | 0      | 0     |  |  |  |  |  |

|                        | SECAM L          | 0             | 0        | 0      | 0     |  |  |  |  |  |

|                        | NTSC M           | 0             | 0        | 0      | 0     |  |  |  |  |  |

| Factory                | French Frequency | 0             | 0        | 0      | 0     |  |  |  |  |  |

| adjustment11         | Russia Frequency | 0  | 0  | 0  | 0  |

|----------------------|------------------|----|----|----|----|

|                      | Italy Frequency  | 0  | 0  | 0  | 0  |

|                      | Spain Frequency  | 0  | 0  | 0  | 0  |

|                      | Turkey Frequency | 0  | 0  | 0  | 0  |

|                      | German Frequency | 0  | 0  | 0  | 0  |

|                      | Poland Frequency | 0  | 0  | 0  | 0  |

|                      | OP Dyn.skin tone | 0  | 0  | 0  | 0  |

|                      | OP TRUSUR        | 0  | 0  | 0  | 0  |

| Factory              | OP Rotation      | 0  | 0  | 0  | 0  |

| adjustment12         | OP EQUAL         | 0  | 0  | 1  | 1  |

|                      | OP AUDIO CONFIG  | 0  | 0  | 1  | 1  |

|                      | OP BILING        | 0  | 0  | 0  | 0  |

| F .                  | Blackstretch     | 0  | 0  | 0  | 0  |

| Factory adjustment13 | Bluestretch      | 0  | 0  | 0  | 0  |

| aujustillerit 13     | HORIZOTAL OFFSET | 12 | 12 | 12 | 12 |

|                      | TIM-REM          | 1  | 1  | 1  | 1  |

| Factory              | TIM-SLP          | 1  | 1  | 1  | 1  |

| adjustment14         | PWR-REST         | 1  | 1  | 1  | 1  |

|                      | PWR-ONKEY        | 1  | 1  | 1  | 1  |

#### IC INFORMATION

#### 1. PHILIPS UOCIII CHIP (N603)

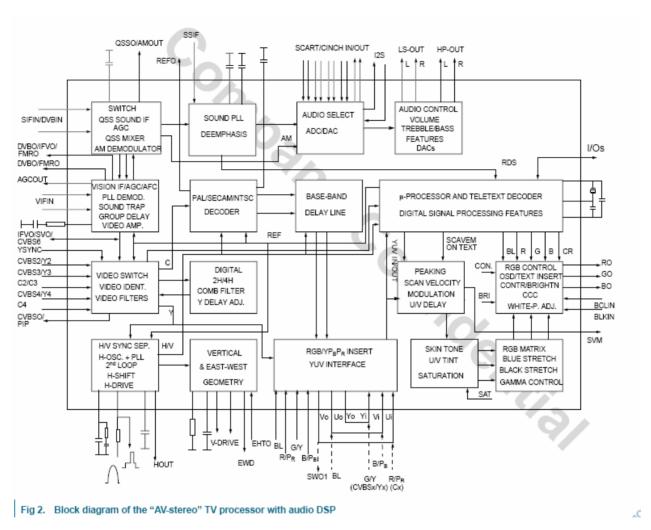

In this section mainly describe two ICs: TDA12060 and TDA12062, the TDA12060 is a AV Stereo without audio DSP chip, but the TDA12062 is a AV Stereo with audio DSP chip.

#### 1.1 General description

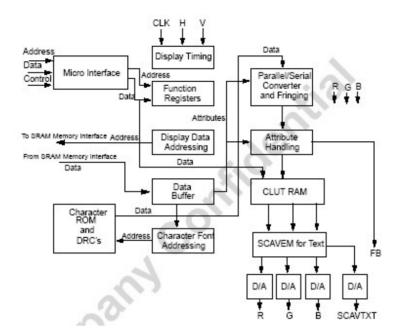

The UOCIII series combines the functions of a Video Signal Processor (VSP) together with a FLASH embedded TEXT/Control/Graphics -Controller (TCG -Controller) and US Closed Caption decoder. In addition the following functions can be added:

- Adaptive digital (4H/2H) PAL/NTSC comb filter

- Teletext decoder with 10 or 100 page text memory

- Multi-standard stereo decoder

- BTSC stereo decoder

- Digital sound processing circuit

- Digital video processing circuit

The UOCIII series consists of the following 3 basic concepts:

- Stereo versions. These versions contain the TV processor with a stereo audio selector, the TCG

-Controller, the multi-standard stereo or BTSC decoder, the digital sound processing circuit and the digital video processing circuit. Options are the adaptive digital PAL/NTSC comb filter and a teletext decoder with 10 or 100 page text memory.

- AV stereo versions. These versions contain the TV processor with stereo audio selector and the TCG -Controller. Options are the digital sound processing circuit, the digital video processing circuit, the adaptive digital PAL/NTSC comb filter and a teletext decoder with a 10 page text memory.

- Mono sound versions. These versions contain the TV processor with a selector for mono audio signals and the TCG -Controller. Options are the adaptive digital PAL/NTSC combfilter and a teletext decoder with 10 page text memory.

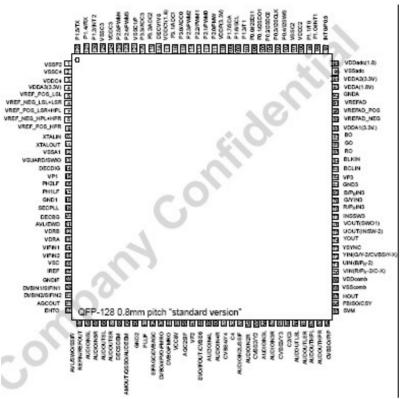

The ICs are mounted in a QFP-128 package and can be used in economy television receivers with 90  $_{\cdot}$  and 110  $_{\cdot}$  picture tubes. The package is according to the ROHS legislation, which also means that the package is lead-free. The ICs have supply voltages of 5V, 3.3V. Also an 1.8V supply is needed, but this can be simply derived by adding an emitter follower at a reference voltage from the device.

#### 1.2 Features

#### 1.2.1 Analogue Video Processing

- \* Multi-standard vision IF circuit with alignment-free PLL demodulator

- \* Internal (switchable) time-constant for the IF-AGC circuit

- \* Switchable group delay correction and sound trap (with switchable centre frequency) for the demodulated CVBS signal

- \* DVB/VSB IF circuit for preprocessing of digital TV signals.

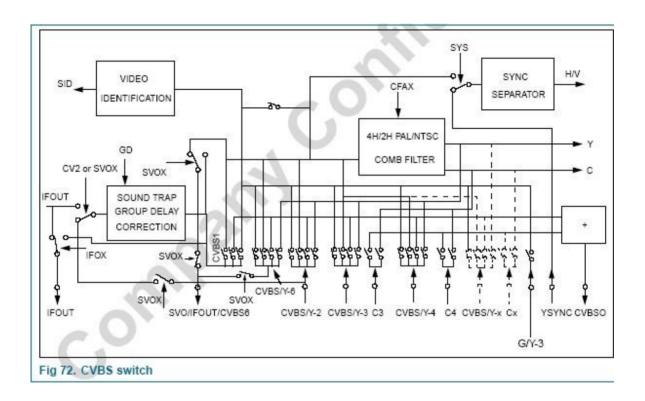

- \* Video switch with 3 external CVBS inputs and a CVBS output. All CVBS inputs can be used as Y-input for Y/C signals. However, only 2 Y/C sources can be selected because the circuit has 2 chroma inputs. It is possible to add an additional CVBS(Y)/C input (CVBS/YX and CX) when the YUV interface and the RGB/YPBPR input are not needed. It is also possible to insert a CVBS/Y

signal at the SVO/IFVOUT output.

- \* Automatic Y/C signal detector

- \* Integrated luminance delay line with adjustable delay time

- \* Picture improvement features with peaking (with switchable centre frequency, depeaking, variable positive/negative peak ratio, variable pre-/overshoot ratio and video dependent coring), dynamic skin tone control, gamma control and blue- and black stretching. All features are available for CVBS, Y/C and RGB/YPBPR signals.

- \* The effect of the various features can de demonstrated by means of a 'split screen' mode in which the features are activated in one half of the picture and switched off in the other half

- \* Switchable DC transfer ratio for the luminance signal

- \* Only one reference (24.576 MHz) crystal required for the TCG -Controller, and the colour decoder

- \* Multi-standard colour decoder with automatic search system and various "forced mode" possibilities

- \* Internal base-band delay line

- \* Indication of the Signal-to-Noise ratio of the incoming CVBS signal

- \* Linear RGB/YPBPR input with fast insertion.

- \* YUV interface. When this feature is not required some pins can be used as additional RGB/YPBPR input. It is also possible to use these pins for additional CVBS (or Y/C) input (CVBS/YX and CX).

- \* Tint control for external RGB/YPBPR signals

- \* Scan Velocity Modulation output. The SVM circuit is active for all the incoming CVBS, Y/C and RGB/YPBPR signals.

- \* RGB control circuit with 'Continuous Cathode Calibration', white point and black level off-set adjustment so that the colour temperature of the dark and the light parts of the screen can be chosen independently.

- \* Contrast reduction possibility during mixed-mode of OSD

- \* Adjustable 'wide blanking' of the RGB outputs

- \* Horizontal synchronization with two control loops and alignment-free horizontal oscillator

- \* Vertical count-down circuit

- \* Vertical driver optimized for DC-coupled vertical output stages

- \* Horizontal and vertical geometry processing with horizontal parallelogram and bow correction and horizontal and vertical zoom

- \* Low-power start-up of the horizontal drive circuit

#### 1.2.2 Sound Demodulation

- \* Separate SIF (Sound IF) input for single reference QSS (Quasi Split Sound) demodulation.

- \* AM demodulator without extra reference circuit

- \* The mono intercarrier sound circuit has a selective FM-PLL demodulator which can be switched to the different FM sound frequencies (4.5/5.5/6.0/6.5 MHz). The quality of this system is such that the external band-pass filters can be omitted. I

- \* The FM-PLL demodulator can be set to centre frequencies of 4.72/5.74 MHz so that a second sound channel can be demodulated. In such an application it is necessary that an external bandpass filter is inserted.

- \* The vision IF and mono intercarrier sound circuit can be used for the demodulation of FM radio signals. With an external FM tuner also signals with an IF frequency of 10.7 MHz can be demodulated.

- \* Switch to select between 2nd SIF from QSS demodulation or external FM (SSIF).

#### 1.2.3 Audio Interfaces and switching

- \* Audio switch circuit with 4 stereo inputs, a stereo output for SCART/CINCH and a stereo SPEAKER output with independent L&R analogue volume control.

- \* Analogue mono AVL circuit at left audio channel

#### 1.2.4 -Controller

- \* 80C51 -controller core standard instruction set and timing

- \* 0.4883 s machine cycle

- \* maximum of 256k x 8-bit flash programmable ROM

- \* maximum of 8k x 8-bit Auxiliary RAM

- \* 12-level Interrupt controller for individual enable/disable with two level priority

- \* Two 16-bit Timer/Counter registers

- \* One 24-bit Timer (16-bit timer with 8-bit Pre-scaler)

- \* Watch Dog timer

- \* Auxiliary RAM page pointer

- \* 16-bit Data pointer

- \* Stand-by, Idle and Power Down modes

- \* 24 general-purpose I/O pins

- \* 14 bits PWM for Voltage Synthesis Tuning

- \* 8-bit A/D converter with 4 multiplexed inputs

- \* 5 PWM (6-bits) outputs for analogue control functions

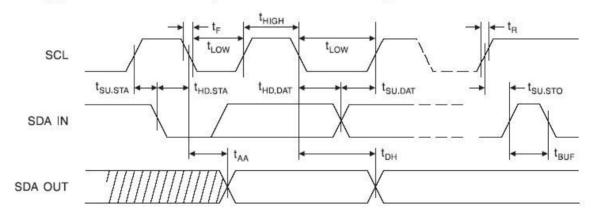

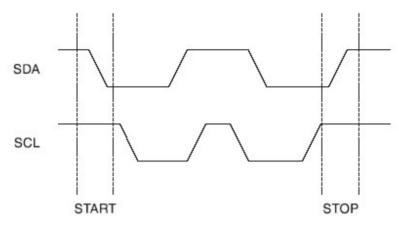

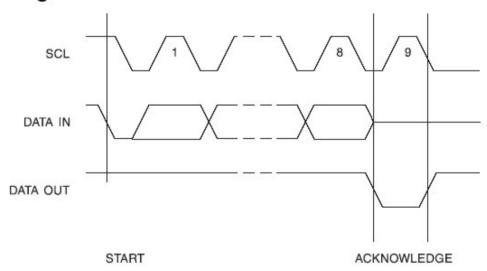

- \* I2C byte level bus interface.

- \* Remote Control Pre-processor (RCP)

- \* Universal Asynchronous Receiver Transmitter (UART)

#### 1.2.5 Display

- \* 50Hz/60Hz display timing modes

- \* Two page operation for 16:9 screens

- \* Serial and Parallel Display Attributes

- \* Single/Double/Quadruple Width and Height for characters

- \* Smoothing capability of both Double Size, Double Width & Double Height characters

- \* Scrolling of display region

- \* Variable flash rate controlled by software

- \* Soft colours using CLUT with 4096 colour palette

- \* Globally selectable scan lines per row (9/10/13/16/) and character matrix [12x9, 12x13, 12x16, 16x18, (VxH)]

- \* Fringing (Shadow) selectable from N-S-E-W direction

- \* Fringe colour selectable

- \* Contrast reduction of defined area

- \* Cursor

- \* Special Graphics Characters with two planes, allowing four colours per character

- \* 64 software redefinable On-Screen display characters

- \* 4 WST Character sets (G0/G2) in single device (e.g. Latin, Cyrillic, Greek, Arabic)

- \* G1 Mosaic graphics, Limited G3 Line drawing characters

- \* WST Character sets and Closed Caption Character set in single device

- \* Curtaining effect via software

- 1.3 Quick reference data

| SYMBOL                  | PARAMETER                                                               | MIN                 | TYP.            | MAX.              | UNIT    |

|-------------------------|-------------------------------------------------------------------------|---------------------|-----------------|-------------------|---------|

| Bupply                  |                                                                         |                     |                 |                   |         |

| Vp                      | analogue supply voltage TV processor                                    | 4.7                 | 5.0             | 5.3               | .V      |

| p                       | supply current (5.0 V)                                                  | 353                 | 190             |                   | mA      |

| Voda                    | digital supply TV processor / analogue supply periphery                 | 3.0                 | 3.3             | 3.6               | W       |

| DOA                     | supply current (3.3 V)                                                  | 0.50                | 40              | (25) V            | mA      |

| Vapore                  | digital supply to core/periphery                                        | 1.65                | 1.8             | 1.95              | V       |

| DOOP                    | supply current (1.8 V)                                                  | 7.5%                | 200             | -                 | mA      |

| V <sub>PMuxBo</sub> III | audio supply voltage                                                    | 4.7                 | 8.0             | 8.4               | V       |

| Mucio III               | supply current (S.D/8.0 V)                                              | WENT TO             | 0.5             | 12/1              | mA      |

| P <sub>tot</sub>        | total power dissipation                                                 | -                   | 1.87            | (H)               | W       |

| Input voltages          |                                                                         |                     |                 |                   |         |

| V <sub>(MErms)</sub>    | video IF amplifier sensitivity (RMB value)                              | -                   | 75              | 150               | βPA     |

| Visitims)               | QSS sound IF amplifier sensitivity (RMS value)                          | 025                 | 45              | 20-               | dΒμ∀    |

| VidS(F(rm)              | sound IF amplifier sensitivity (RMS value)                              | 000                 | 1.0             | (H)               | -mV     |

| VIAUDIO(ma)             | external audio input (RMS value)                                        | 757                 | 1.0             | 1.3               | W.      |

| Vicves(p-p)             | external CVSS/Y Input (peak-to-peak value)                              | nen                 | 1.0             | 1.4               | William |

| VICHROMA(p-p)           | external chroma input voltage (burst amplitude)<br>(peak-to-peak value) | NEW .               | 0.3             | 1.0               | ٧       |

| Vince(p-p)              | RGB Inputs (peak-to-peak value)                                         | (5 <del>-</del> 33) | 0.7             | 0.8               | (80)    |

| V <sub>(Y(p-p)</sub>    | luminance input signal (peak-to-peak value)                             | 9720                | 1.4 / 1.0       | (120) —           | · V     |

| Viutera / Viptopa       | U / Pg Input signal (peak-to-peak value)                                | 199                 | -1.33 /<br>-0.7 | 120               | Y.      |

| Viv(p-p) / ViPR(p-p)    | V / Pig Input signal (peak-to-peak value)                               | 988                 | -1.05 /<br>+0.7 | 900               | ٧       |

| Output elgnale          |                                                                         |                     | A274 C          |                   |         |

| VojiPV0((p-p)           | demodulated CVBS output (peak-to-peak value)                            | 1000                | 2.0             | 0800              | -V      |

| Vojassojeme)            | sound IF Intercarrier output (RMS value)                                | 848                 | 100             | 948               | mW      |

| VojAMOUT)(mai           | demodulated AM sound output (RMS value)                                 | ti <del>e</del> se  | 250             | 0 <del>0</del> 00 | mV      |

| Vojaudiosmi H           | non-controlled audio output signals (RMS value)                         | 1.0                 | 628             | 9283              | VV.     |

| Vojovnikovoja           | selected CVBB output (peak-to-peak value)                               | 19 <del>0</del> 30  | 2.0             | 5 <del>4</del> 35 | V       |

| l <sub>e(AGCOUT)</sub>  | tuner AGC output current range                                          | 0.                  | 75              | 1                 | mA      |

| VoRSB(p-p)              | RGB output signal amplitudes (peak-to-peak value)                       | 13 <del>4</del> 39  | 1.2             | 0-00              | V       |

| Гоношт                  | horizontal output current                                               | 10                  | (48)            | 9233              | mA      |

| OVERT                   | vertical output current (peak-to-peak value)                            | 0+30                | -1              | 0+00              | mA      |

| lottwo                  | EW drive output current                                                 | 64.5                | 723             | 1.2               | mΑ      |

<sup>[1]</sup> The supply voltage for the analogue audio part of the IC can be 5V or 8V. For a supply voltage of 5V the maximum signal amplitudes at in and outputs are 1V<sub>max</sub>. For a supply voltage of 8V the maximum output signal amplitude is 2 V<sub>max</sub>.

<sup>[2]</sup> The YUVIYP<sub>B</sub>P<sub>R</sub> input signal amplitudes are based on a colour bar signal with 75/100% saturation.

#### 1.4 Block diagram

Note: TDA12062block diagram

#### 1.5 Pinning information

Note: TDA12062's pinning

| SYMBOL               | 20000000                 |                                    |       | 2FP                      |                                    |      |                                     | QIP    |      | DESCRIPTION                                                                                   |  |

|----------------------|--------------------------|------------------------------------|-------|--------------------------|------------------------------------|------|-------------------------------------|--------|------|-----------------------------------------------------------------------------------------------|--|

|                      | "Stan                    | dard" ve                           | noisn | "Face down" version      |                                    |      | "Standard" &<br>"Face-down" version |        |      |                                                                                               |  |

|                      | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono  | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono | stereo<br>+ AV<br>stereo            | stereo | Mono |                                                                                               |  |

| VSSP2                | 1                        | 1                                  | 1     | 128                      | 128                                | 128  | 1                                   | 1      | 1    | ground                                                                                        |  |

| VSSC4                | 2                        | 2                                  | 2     | 127                      | 127                                | 127  | 1                                   | 1      | 1    | ground                                                                                        |  |

| VDDC4                | 3                        | 3                                  | 3     | 126                      | 126                                | 126  | 3                                   | 3      | 3    | digital supply to SDACs (1.8V)                                                                |  |

| VDDA3(3.3V)          | 4                        | 4                                  | 4     | 125                      | 125                                | 125  | 16                                  | 16     | 16   | supply (3.3 V)                                                                                |  |

| VREF_POS_LSL         | 5                        | 5                                  | 5     | 124                      | 124                                | 124  | 16                                  | 16     | 16   | positive reference voltage SDAC (3.3 V)                                                       |  |

| VREF_NEG_LSL+ HPL    | 6                        | 6                                  | 6     | 123                      | 123                                | 123  | 17                                  | 17     | 17   | negative reference voltage SDAC (0 V)                                                         |  |

| VREF_POS_LSR+<br>HPR | 7                        | 7                                  | 7     | 122                      | 122                                | 122  | 16                                  | 16     | 16   | positive reference voltage SDAC (3.3 V)                                                       |  |

| VREF_NEG_HPL+<br>HPR | 8                        | 8                                  | 8     | 121                      | 121                                | 121  | 17                                  | 17     | 17   | negative reference voltage SDAC (0 V)                                                         |  |

| VREF_POS_HPR         | 9                        | 9                                  | 9     | 120                      | 120                                | 120  | 16                                  | 16     | 16   | positive reference voltage SDAC (3.3 V)                                                       |  |

| XTALIN               | 10                       | 10                                 | 10    | 119                      | 119                                | 119  | 18                                  | 18     | 18   | crystal oscillator input                                                                      |  |

| XTALOUT              | 11                       | 11                                 | 11    | 118                      | 118                                | 118  | 19                                  | 19     | 19   | crystal oscillator output                                                                     |  |

| VSSA1                | 12                       | 12                                 | 12    | 117                      | 117                                | 117  | 20                                  | 20     | 20   | ground                                                                                        |  |

| VGUARD/SWIO          | 13                       | 13                                 | 13    | 116                      | 116                                | 116  | 78                                  | 78     | 78   | V-guard input / I/O switch (e.g. 4 mA current sinking<br>capability for direct drive of LEDs) |  |

| DECDIG               | 14                       | 14                                 | 14    | 115                      | 115                                | 115  | 21                                  | 21     | 21   | decoupling digital supply                                                                     |  |

| VP1                  | 15                       | 15                                 | 15    | 114                      | 114                                | 114  | 22                                  | 22     | 22   | 1st supply voltage TV-processor (+5 V)                                                        |  |

| PH2LF                | 16                       | 16                                 | 16    | 113                      | 113                                | 113  | 23                                  | 23     | 23   | phase-2 filter                                                                                |  |

| PH1LF                | 17.                      | 17                                 | 17    | 112                      | 112                                | 112  | 24                                  | 24     | 24   | phase-1 fiter                                                                                 |  |

| GND1                 | 18                       | 18                                 | 18    | 111                      | 111                                | 111  | 25                                  | 25     | 25   | ground 1 for TV-processor                                                                     |  |

| SECPLL               | 19                       | 19                                 | 19    | 110                      | 110                                | 110  | 26                                  | 26     | 26   | SECAM PLL decoupling                                                                          |  |

| DECBG                | 20                       | 20                                 | 20    | 109                      | 109                                | 109  | 27                                  | 27     | 27   | bandgap decoupling                                                                            |  |

| EWD/AVL III          | 21                       | 21                                 | 21    | 108                      | 108                                | 108  | 75                                  | 75     | 75   | East-West drive output or AVL capacitor                                                       |  |

| VDRB                 | 22                       | 22                                 | 22    | 107                      | 107                                | 107  | 77                                  | 77     | 77   | vertical drive B output                                                                       |  |

| VDRA                 | 23                       | 23                                 | 23    | 106                      | 106                                | 106  | 76                                  | 76     | 76   | vertical drive A output                                                                       |  |

| VIFIN1               | 24                       | 24                                 | 24    | 105                      | 105                                | 105  | 28                                  | 28     | 28   | IF input 1                                                                                    |  |

| SYMBOL                             |                          |                                    |        | 2FP                      |                                    |                   | QIP                                 |        |      | DESCRIPTION                                                                                                                                                            |  |

|------------------------------------|--------------------------|------------------------------------|--------|--------------------------|------------------------------------|-------------------|-------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                    | "Stan                    | dard" ve                           | nolere | "Face down" version      |                                    |                   | "Standard" &<br>"Face-down" version |        |      |                                                                                                                                                                        |  |

|                                    | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono   | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono              | Stereo<br>+ AV<br>stereo            | stereo | Mono |                                                                                                                                                                        |  |

| VIFIN2                             | 25                       | 25                                 | 25     | 104                      | 104                                | 104               | 29                                  | 29     | 29   | IF input 2                                                                                                                                                             |  |

| /SC                                | 26                       | 26                                 | 26     | 103                      | 103                                | 103               | 30                                  | 30     | 30   | vertical sawtooth capacitor                                                                                                                                            |  |

| REF                                | 27                       | 27                                 | 27     | 102                      | 102                                | 102               | 31                                  | 31     | 31   | reference current input                                                                                                                                                |  |

| GNDIF                              | 28                       | 28                                 | 28     | 101                      | 101                                | 101               | 32                                  | 32     | 32   | ground connection for IF amplifier                                                                                                                                     |  |

| SIFIN1/DVBIN1 Z                    | 29                       | 29                                 | 29     | 100                      | 100                                | 100               | 33                                  | 33     | 33   | SIF Input 1 / DVB Input 1                                                                                                                                              |  |

| SIFIN2/DVBIN2 🕮                    | 30                       | 30                                 | 30     | 99                       | 99 9                               | 99                | 34                                  | 34     | 34   | SIF Input 2 / DVB Input 2                                                                                                                                              |  |

| AGCOUT                             | 31                       | 31                                 | 31     | 98                       | 98                                 | 98                | 35                                  | 35     | 35   | tuner AGC output                                                                                                                                                       |  |

| EHTO                               | 32                       | 32                                 | 32     | 97                       | 97                                 | 97                | 74                                  | 74     | 74   | EHT/overvoltage protection input                                                                                                                                       |  |

| AVL/SWO/SSIF/<br>REFO/REFIN (2001) | 33                       | 33                                 | 33     | 96                       | 96                                 | 96                | 44                                  | 44     | 44   | Automatic Volume Levelling / switch output / sound IF<br>input / subcarrier reference output / external reference<br>signal input for I signal mixer for DVB operation |  |

| AUDIOINS                           | 2                        |                                    | 34     | -                        | =:                                 | 95                | -                                   | -      | w- 1 | audio 5 input                                                                                                                                                          |  |

| AUDIOIN5L                          | 34                       | 34                                 | =      | 95                       | 95                                 | -3                | -                                   | -4     | 1-00 | audio-5 input (left signal)                                                                                                                                            |  |

| AUDIOINSR                          | 35                       | 35                                 | -      | 94                       | 94                                 | 330               | -                                   | - 4    | 112  | audio-5 input (right signal)                                                                                                                                           |  |

| AUDOUTSL                           | 36                       | 36                                 | 9      | 93                       | 93                                 | -                 | 37                                  | 37     | -//  | audio output for SCART/CINCH (left signal)                                                                                                                             |  |

| AUDOUTSR                           | 37                       | 37                                 | 77     | 92                       | 92                                 | 350               | 38                                  | 38     | - 1  | audio output for SCART/CINCH (right signal)                                                                                                                            |  |

| DECSDEM                            | 38                       | 38                                 | 38     | 91                       | 91                                 | 91                | 64                                  | 64     | 64   | decoupling sound demodulator                                                                                                                                           |  |

| QSSO/AMOUT/<br>AUDEEM 🗵            | 39                       | 39                                 | 39     | 90                       | 90                                 | 90                | 36                                  | 36     | 36   | QSS Intercarrier output / AM output / deemphasis<br>(front-end audio out)                                                                                              |  |

| GND2                               | 40                       | 40                                 | 40     | 89                       | 89                                 | 89                | 39                                  | 39     | 39   | ground 2 for TV processor                                                                                                                                              |  |

| PLLIF                              | 41                       | 41                                 | 41     | 88                       | 88                                 | 88                | 40                                  | 40     | 40   | IF-PLL loop filter                                                                                                                                                     |  |

| SIFAGC/DVBAGC 🗵                    | 42                       | 42                                 | 42     | 87                       | 87                                 | 87                | 41                                  | 41     | 41   | AGC sound IF / Internal-external AGC for DVB applications                                                                                                              |  |

| OVBO/IFVO/FMRO 2                   | 43                       | 43                                 | 43     | 86                       | 86                                 | 86                | 42                                  | 42     | 42   | Digital Video Broadcast output / IF video output / FM radio output                                                                                                     |  |

| OVBO/FMRO 🗵                        | 44                       | 44                                 | 75     | 85                       | 85                                 | 8 <del>7</del> 83 | -                                   | æ      | =    | Digital Video Broadcast output / FM radio output                                                                                                                       |  |

| VCC8V                              | 45                       | 45                                 | 45     | 84                       | 84                                 | 84                | 43                                  | 43     | 43   | 8 Volt supply for audio switches                                                                                                                                       |  |

| AGC2SIF                            | 46                       | = 1                                | ₹.     | 83                       | =:                                 | 3 <del>7</del> 2  | 44                                  | =      |      | AGC capacitor second sound IF                                                                                                                                          |  |

| VP2                                | 47                       | 47                                 | 47     | 82                       | 82                                 | 82                | 45                                  | 45     | 45   | 2rd supply voltage TV processor (+5 V)                                                                                                                                 |  |

| Table 6: | Pinning Information |

|----------|---------------------|

|----------|---------------------|

| SYMBOL                 |                          |                                    |       | 2FP                      |                                    |        |                                         | QIP                |      | DESCRIPTION                                                       |

|------------------------|--------------------------|------------------------------------|-------|--------------------------|------------------------------------|--------|-----------------------------------------|--------------------|------|-------------------------------------------------------------------|

|                        | "Stan                    | dard" ve                           | noisn | "Face                    | down" v                            | nolsre | 100000000000000000000000000000000000000 | standard<br>-down" |      |                                                                   |

|                        | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono  | Stereo +<br>AV<br>atereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono   | Stereo<br>+ AV<br>stereo                | stereo             | Mono |                                                                   |

| IFVO/SVO/CVBS6 🗵       | 48                       | 48                                 | 48    | 81                       | 81                                 | 81     | 46                                      | 46                 | 46   | IF video output / selected CVBS output / CVBS input               |

| AUDIOIN4               | 3                        | -                                  | 49    | -01                      | -                                  | 80     | -                                       | 7                  | 47   | audio 4 Input                                                     |

| AUDIOIN4L              | 49                       | 49                                 | 5     | 80                       | 80                                 | =      | 47                                      | 47                 | Ti:  | audio-4 input (left signal)                                       |

| AUDIOIN4R              | 50                       | 50                                 | -     | 79                       | 79                                 | -      | 48                                      | 48                 | ÷    | audio-4 input (right signal)                                      |

| CVBS4/Y4               | 51                       | 51                                 | 51    | 78                       | 78                                 | 78     | 49                                      | 49                 | 49   | CVBS4/Y4 Input                                                    |

| C4                     | 52                       | 52                                 | 52    | 77                       | 77                                 | 77     | -                                       | -                  | ÷    | chroma-4 input                                                    |

| AUDIOIN2               | 2 8                      | 575                                | 53    | <del></del>              | 51 4                               | 76     | -                                       | -                  | 50   | audio 2 Input                                                     |

| AUDIOIN2L/SSIF         | 53                       | 53                                 | -     | 76                       | 76                                 | -      | 50                                      | 50                 | -    | audio 2 Input (left signal) / sound IF Input                      |

| AUDIOIN2R              | 54                       | 54                                 | 31    | 75                       | 75                                 | = 1    | 51                                      | 51                 | Ti:  | audio 2 Input (right signal)                                      |

| CVBS2/Y2               | 55                       | 55                                 | 55    | 74                       | 74                                 | 74     | 52                                      | 52                 | 52   | CVBS2/Y2 Input                                                    |

| AUDIOIN3               | 2 8                      | 57%                                | 56    | <del>d</del> e           | =:                                 | 73     | 7                                       | -0 A               | 53   | audio 3 Input                                                     |

| AUDIOIN3L              | 56                       | 56                                 | -     | 73                       | 73                                 | -      | 53                                      | 53                 | -    | audio 3 input (left signal)                                       |

| AUDIOIN3R              | 57                       | 57                                 | 2     | 72                       | 72                                 | 15     | 54                                      | 54                 | A    | audio 3 input (right signal)                                      |

| CVBS3/Y3               | 58                       | 58                                 | 58    | 71                       | 71                                 | 71     | 55                                      | 55                 | 55   | CVBS3/Y3 Input                                                    |

| C2/C3                  | 59                       | 59                                 | 59    | 70                       | 70                                 | 70     | 56                                      | 56                 | 56   | chroma-2/3 Input                                                  |

| AUDOUTLSL              | 60                       | 62                                 | -     | 69                       | 67                                 | -      | 57                                      | 59                 | 57   | audio output for audio power amplifier (left signal)              |

| AUDOUTLSR              | 61                       | 63                                 | =     | 68                       | 66                                 | =      | 58                                      | 60                 | 58   | audio output for audio power amplifier (right signal)             |

| AUDOUT/AMOUT/<br>FMOUT | 2                        |                                    | 62    | -                        | -                                  | 67     | -                                       | =                  | 59   | audio output / AM output / FM output, volume controlled           |

| AUDOUTHPL              | 62                       | -                                  | =     | 67                       | =                                  | =      | 59                                      | =                  | 7    | audio output for headphone channel (left signal)                  |

| AUDOUTHPR              | 63                       | -                                  | -     | 66                       | -                                  | -      | 60                                      | 2                  | -    | audio output for headphone channel (right signal)                 |

| CVBSO/PIP              | 64                       | 64                                 | 64    | 65                       | 65                                 | 65     | 61                                      | 61                 | 61   | CVBS / PIP output                                                 |

| SVM                    | 65                       | 65                                 | 65    | 64                       | 64                                 | 64     | 71                                      | 71                 | 71   | scan velocity modulation output                                   |

| FBISO/CSY              | 66                       | 66                                 | 66    | 63                       | 63                                 | 63     | 72                                      | 72                 | 72   | flyback input/sandcastle output or composite H/V timing<br>output |

| HOUT                   | 67                       | 67                                 | 67    | 62                       | 62                                 | 62     | 73                                      | 73                 | 73   | horizontal output                                                 |

| VSScomb                | 68                       | 68                                 | 68    | 61                       | 61                                 | 61     | 62                                      | 62                 | 62   | ground connection for comb filter                                 |

| VDDcomb                | 69                       | 69                                 | 69    | 60                       | 60                                 | 60     | 63                                      | 63                 | 63   | supply voltage for comb filter (5 V)                              |

| SYMBOL                                     |                          |                                    | (      | 2FP                      |                                    |      |                          | QIP                |          | DESCRIPTION                                                                                        |  |  |

|--------------------------------------------|--------------------------|------------------------------------|--------|--------------------------|------------------------------------|------|--------------------------|--------------------|----------|----------------------------------------------------------------------------------------------------|--|--|

|                                            | "Star                    | ndard" ve                          | ersion | "Face                    | "Face down" version                |      |                          | standard<br>-down" |          |                                                                                                    |  |  |

|                                            | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono   | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono | Stereo<br>+ AV<br>stereo | stereo             | Mono     |                                                                                                    |  |  |

| VIN (R/P <sub>R</sub> IN2/C <sub>X</sub> ) | 70                       | 70                                 | 70     | 59                       | 59                                 | 59   | -                        | 2                  | 2        | V-input for YUV interface (2 <sup>nd</sup> R input / P <sub>R</sub> input or C <sub>X</sub> input) |  |  |

| UIN (B/PBIN2)                              | 71                       | 71                                 | 71     | 58                       | 58                                 | 58   | -                        | 7                  | -        | U-input for YUV interface (2nd B input / PB input)                                                 |  |  |

| YIN (G/YIN2/CVBS-Y <sub>X</sub> )          | 72                       | 72                                 | 72     | 57                       | 57                                 | 57   | -                        | =                  | 5        | Y-Input for YUV Interface (2nd G Input / Y Input or CVBS/Y <sub>X</sub> Input))                    |  |  |

| YSYNC                                      | 73                       | 73                                 | 73     | 56                       | 56                                 | 56   | 65                       | 65                 | 65       | Y-Input for sync separator                                                                         |  |  |

| YOUT                                       | 74                       | 74                                 | 74     | 55                       | 55                                 | 55   | 66                       | 66                 | 66       | Y-output (for YUV interface)                                                                       |  |  |

| UOUT (INSSW2)                              | 75                       | 75                                 | 75     | 54                       | 54                                 | 54   | 1                        | ľ                  | <u> </u> | U-output for YUV Interface (2 <sup>nd</sup> RGB / YP <sub>B</sub> P <sub>R</sub> insertion input)  |  |  |

| VOUT (SWO1)                                | 76                       | 76                                 | 76     | 53                       | 53                                 | 53   | -                        | Ā                  | ¥        | V-output for YUV Interface (general purpose switch output)                                         |  |  |

| INSSW3                                     | 77                       | 77                                 | 77     | 52                       | 52                                 | 52   | 67                       | 67                 | 67       | 3rd RGB / YPBPR Insertion Input                                                                    |  |  |

| R/P <sub>R</sub> IN3                       | 78                       | 78                                 | 78     | 51                       | 51                                 | 51   | 68                       | 68                 | 68       | 3rd R Input / P <sub>R</sub> Input                                                                 |  |  |

| G/YIN3                                     | 79                       | 79                                 | 79     | 50                       | 50                                 | 50   | 69                       | 69                 | 69       | 3rd G Input / Y Input                                                                              |  |  |

| B/P <sub>B</sub> IN3                       | 80                       | 80                                 | 80     | 49                       | 49                                 | 49   | 70                       | 70                 | 70       | 3rd B Input / P <sub>B</sub> Input                                                                 |  |  |

| GND3                                       | 81                       | 81                                 | 81     | 48                       | 48                                 | 48   | 79                       | 79                 | 79       | ground 3 for TV-processor                                                                          |  |  |

| VP3                                        | 82                       | 82                                 | 82     | 47                       | 47                                 | 47   | 80                       | 80                 | 80       | 3 <sup>rd</sup> supply for TV processor                                                            |  |  |

| BCLIN                                      | 83                       | 83                                 | 83     | 46                       | 46                                 | 46   | 81                       | 81                 | 81       | beam current limiter input                                                                         |  |  |

| BLKIN                                      | 84                       | 84                                 | 84     | 45                       | 45                                 | 45   | 82                       | 82                 | 82       | black current input                                                                                |  |  |

| RO                                         | 85                       | 85                                 | 85     | 44                       | 44                                 | 44   | 83                       | 83                 | 83       | Red output                                                                                         |  |  |

| GO                                         | 86                       | 86                                 | 86     | 43                       | 43                                 | 43   | 84                       | 84                 | 84       | Green output                                                                                       |  |  |

| BO                                         | 87                       | 87                                 | 87     | 42                       | 42                                 | 42   | 85                       | 85                 | 85       | Blue output                                                                                        |  |  |

| VDDA1                                      | 88                       | 88                                 | 88     | 41                       | 41                                 | 41   | 86                       | 86                 | 86       | analog supply for TCG $\mu$ -Controller and digital supply for TV-processor (+3.3 V)               |  |  |

| VREFAD_NEG                                 | 89                       | 89                                 | 89     | 40                       | 40                                 | 40   | 87                       | 87                 | 87       | negative reference voitage (0 V)                                                                   |  |  |

| VREFAD_POS                                 | 90                       | 90                                 | 90     | 39                       | 39                                 | 39   | 88                       | 88                 | 88       | positive reference voltage (3.3 V)                                                                 |  |  |

| VREFAD                                     | 91                       | 91                                 | 91     | 38                       | 38                                 | 38   | 89                       | 89                 | 89       | reference voltage for audio ADCs (3.3/2 V)                                                         |  |  |

| GNDA                                       | 92                       | 92                                 | 92     | 37                       | 37                                 | 37   | 87                       | 87                 | 87       | ground                                                                                             |  |  |

| VDDA(1.8V)                                 | 93                       | 93                                 | 93     | 36                       | 36                                 | 36   | 90                       | 90                 | 90       | analogue supply for audio ADCs (1.8 V)                                                             |  |  |

| Table 6. | Disease. | the discount of the in- |

|----------|----------|-------------------------|

| Table 6: | Pinning  | Information             |

| SYMBOL        |                          | QFP                                |      |                          |                                     |      |                          |        |      | DESCRIPTION                                                                                    |

|---------------|--------------------------|------------------------------------|------|--------------------------|-------------------------------------|------|--------------------------|--------|------|------------------------------------------------------------------------------------------------|

|               | "Stan                    | "Face down" version                |      |                          | "Standard" &<br>"Face-down" version |      |                          |        |      |                                                                                                |

|               | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp | Mono | Stereo +<br>AV<br>stereo | AV<br>Stereo<br>No<br>audio<br>dsp  | Mono | Stereo<br>+ AV<br>stereo | stereo | Mono |                                                                                                |

| VDDA2(3.3)    | 94                       | 94                                 | 94   | 35                       | 35                                  | 35   | 88                       | 88     | 88   | supply voltage SDAC (3.3 V)                                                                    |

| VSSadc        | 95                       | 95                                 | 95   | 34                       | 34                                  | 34   | 1                        | 1      | 1    | ground for video ADC and PLL                                                                   |

| VDDadc(1.8)   | 96                       | 96                                 | 96   | 33                       | 33                                  | 33   | 90                       | 90     | 90   | supply voltage video ADC and PLL                                                               |

| INT0/P0.5     | 97                       | 97                                 | 97   | 32                       | 32                                  | 32   | 2                        | 2      | 2    | external interrupt 0 or port 0.5 (4 mA current sinking<br>capability for direct drive of LEDs) |

| P1.0/INT1     | 98                       | 98                                 | 98   | 31                       | 31 (                                | 31   | 4                        | 4      | 4    | port 1.0 or external Interrupt 1                                                               |

| P1.1/T0       | 99                       | 99                                 | 99   | 30                       | 30                                  | 30   | 5                        | 5      | 5    | port 1.1 or Counter/Timer 0 input                                                              |

| VDDC2         | 100                      | 100                                | 100  | 29                       | 29                                  | 29   | 3                        | 3      | 3    | digital supply to core (1.8 V)                                                                 |