# L64105 MPEG-2 Audio/Video Decoder

# **Technical Manual**

Preliminary

ww.DataSheet4U.con

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000041-00, First Edition (July 1998) This document describes revision A of LSI Logic Corporation's L64105 MPEG-2 Audio/Video Decoder and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

# To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

In particular, supply of the LSI Logic IC L64105 does not convey a license or imply a right under certain patents and/or other industrial or intellectual property rights claimed by IRT, CCETT and Philips, to use this IC in any ready-to-use electronic product. The purchaser is hereby notified that Philips, CCETT and IRT are of the opinion that a generally available patent license for such use is required from them. No warranty or indemnity of any sort is provided by LSI Logic regarding patent infringement.

Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved.

### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design and G10 are registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Contents

|           | Pref         | ace                               |      |  |  |

|-----------|--------------|-----------------------------------|------|--|--|

| Chapter 1 | Introduction |                                   |      |  |  |

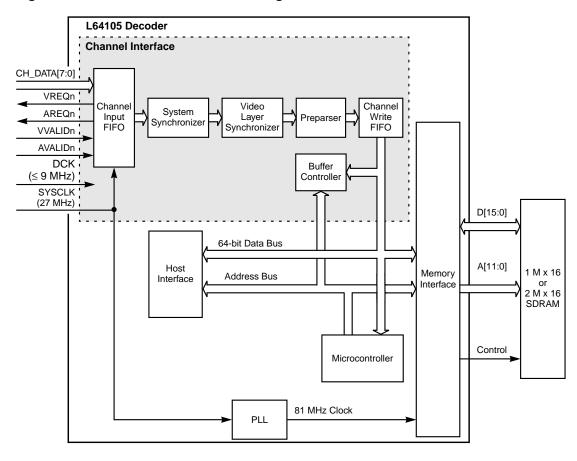

|           | 1.1          | An L64105 Application             | 1-1  |  |  |

|           | 1.2          | L64105 Overview                   | 1-2  |  |  |

|           |              | 1.2.1 Memory Utilization          | 1-5  |  |  |

|           |              | 1.2.2 Error Concealment           | 1-5  |  |  |

|           | 1.3          | Features                          | 1-6  |  |  |

| Chapter 2 | I/O \$       | Signal Descriptions               |      |  |  |

|           | 2.1          | Signals Organization              | 2-1  |  |  |

|           | 2.2          | Host Interface                    | 2-3  |  |  |

|           | 2.3          | Channel Interface                 | 2-5  |  |  |

|           | 2.4          | Memory Interface                  | 2-7  |  |  |

|           | 2.5          | Video Interface                   | 2-8  |  |  |

|           | 2.6          | Audio Interface                   | 2-9  |  |  |

|           | 2.7          | Miscellaneous and Test Interfaces | 2-11 |  |  |

| Chapter 3 | Regi         | ister Summary                     |      |  |  |

|           | 3.1          | Summary by Register               | 3-1  |  |  |

|           | 3.2          | Alphabetical Listing              | 3-30 |  |  |

| Chapter 4 | Regi         | ister Descriptions                |      |  |  |

|           | 4.1          | Host Interface Registers          | 4-2  |  |  |

|           | 4.2          | Video Decoder Registers           | 4-17 |  |  |

|           | 4.3          | Memory Interface Registers        | 4-38 |  |  |

|           | 4.4          | Microcontroller Registers         | 4-48 |  |  |

|           |              |                                   |      |  |  |

|           | 4.5               | Video In     | terface Registers                     | 4-58 |

|-----------|-------------------|--------------|---------------------------------------|------|

|           | 4.6               | Audio De     | ecoder Registers                      | 4-72 |

|           | 4.7               | RAM Tes      | st Registers                          | 4-91 |

| Chapter 5 | Host              | t Interface  |                                       |      |

|           | 5.1               | Overviev     | V                                     | 5-1  |

|           | 5.2               | Interface    | Signals                               | 5-2  |

|           | 5.3               | Register     | Access and Functions                  | 5-5  |

|           |                   | 5.3.1        | General Functions                     | 5-5  |

|           |                   | 5.3.2        | SCR Registers                         | 5-6  |

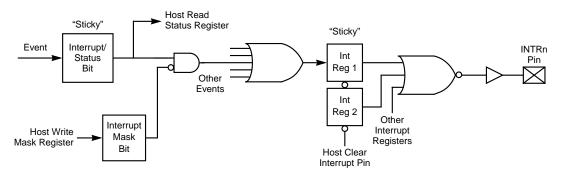

|           |                   | 5.3.3        | Interrupt Registers                   | 5-9  |

|           | 5.4               | SDRAM        | Access                                | 5-10 |

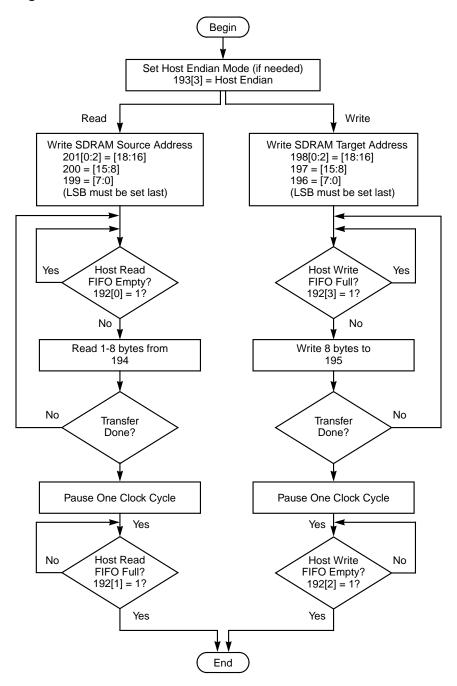

|           |                   | 5.4.1        | Host Reads/Writes                     | 5-10 |

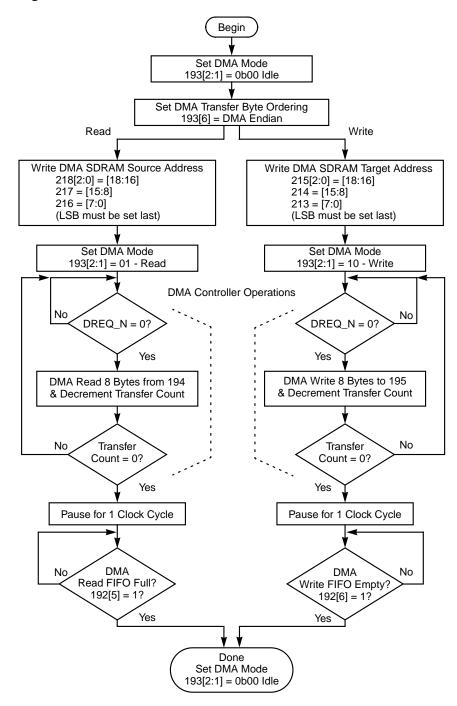

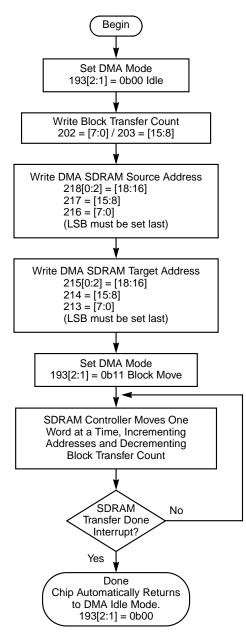

|           |                   | 5.4.2        | Host DMA SDRAM Transfers              | 5-14 |

|           |                   | 5.4.3        | SDRAM Block Move                      | 5-18 |

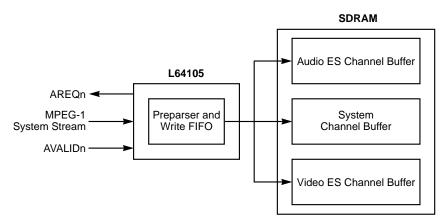

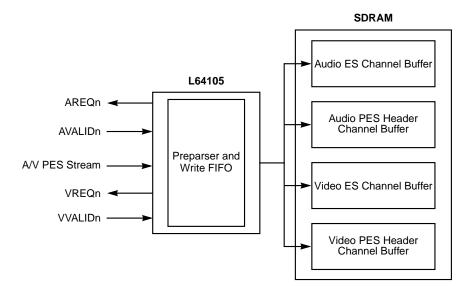

| Chapter 6 | Channel Interface |              |                                       |      |

|           | 6.1               | 6.1 Overview |                                       |      |

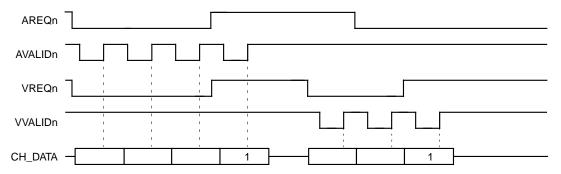

|           | 6.2               | Interface    | Signals Operation                     | 6-3  |

|           |                   | 6.2.1        | Asynchronous Mode                     | 6-4  |

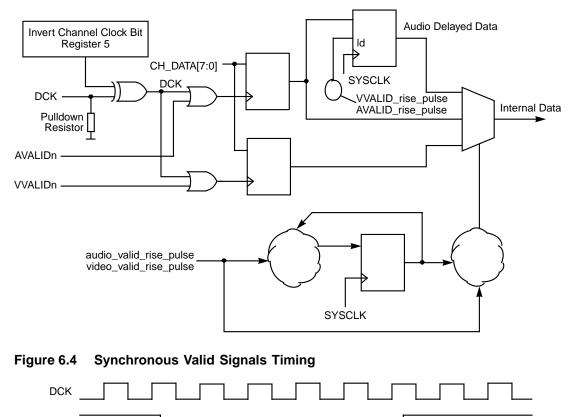

|           |                   | 6.2.2        | Synchronous VALIDn Inputs             | 6-5  |

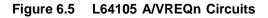

|           |                   | 6.2.3        | Synchronous A/VREQn Outputs           | 6-7  |

|           |                   | 6.2.4        | Channel Bypass Mode                   | 6-8  |

|           |                   | 6.2.5        | Channel Pause                         | 6-8  |

|           | 6.3               | Preparse     | er                                    | 6-9  |

|           |                   | 6.3.1        | Host Selection of Streams and Headers | 6-9  |

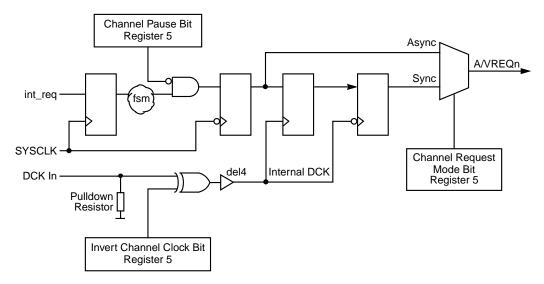

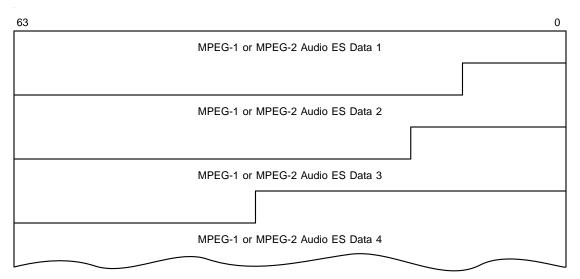

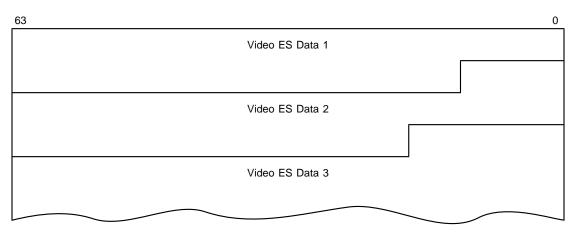

|           |                   | 6.3.2        | Elementary Streams                    | 6-12 |

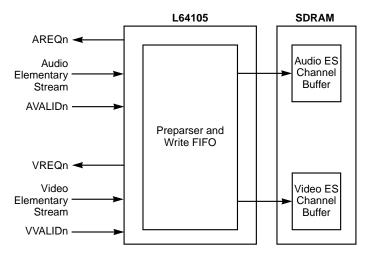

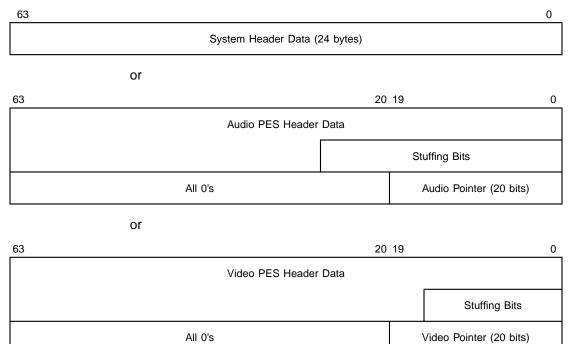

|           |                   | 6.3.3        | PES Packet Structure                  | 6-14 |

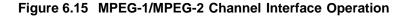

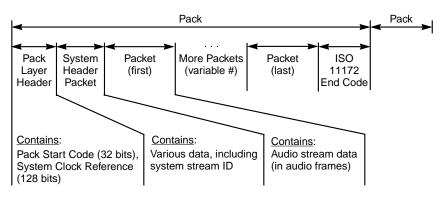

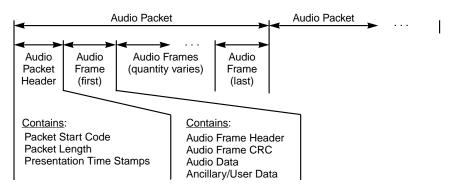

|           |                   | 6.3.4        | Preparsing an MPEG-1 System Stream    | 6-16 |

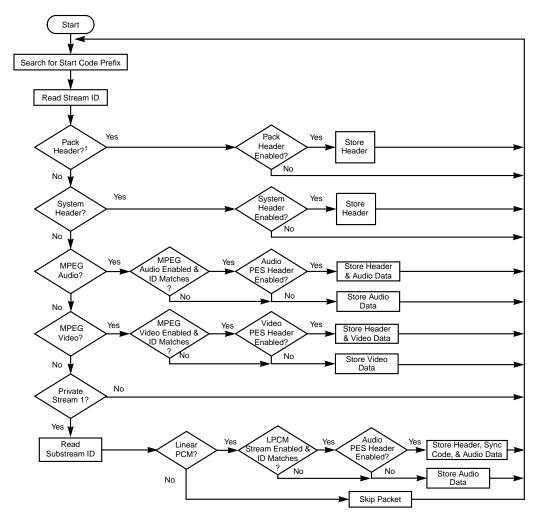

|           |                   | 6.3.5        | Preparsing a Program Stream           | 6-18 |

|           |                   | 6.3.6        | Error Handling in Program Streams     | 6-21 |

|           |                   | 6.3.7        | Preparsing A/V PES Packets from a     | 0.04 |

|           |                   |              | Transport Stream                      | 6-24 |

|           | ~ .               | 6.3.8        | Error Handling in A/V PES Mode        | 6-25 |

|           | 6.4               |              | Buffer Controller                     | 6-27 |

|           |                   | 6.4.1        | Buffer Reset                          | 6-28 |

|           |      | 6.4.2     | Detecting Potential Underflow Conditions<br>in the Video Channel | 6-29 |

|-----------|------|-----------|------------------------------------------------------------------|------|

|           | 6.5  | Summa     |                                                                  | 6-30 |

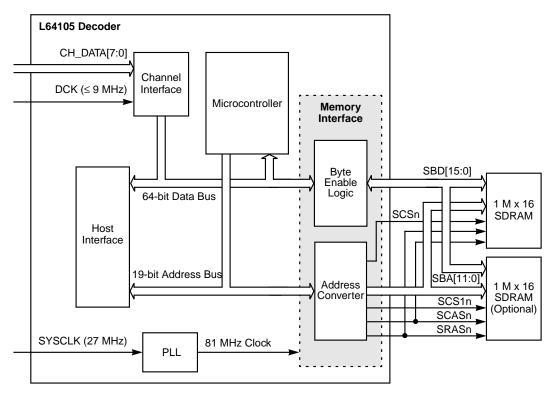

| Chapter 7 | Mem  | ory Inter | face                                                             |      |

|           | 7.1  | Overvie   | W                                                                | 7-1  |

|           | 7.2  | SDRAM     | 1 Configurations                                                 | 7-2  |

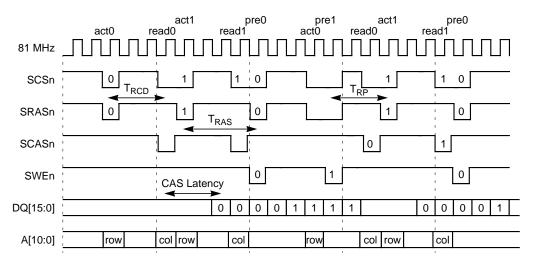

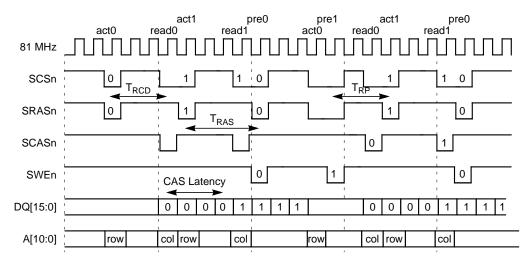

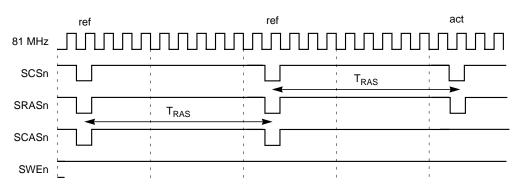

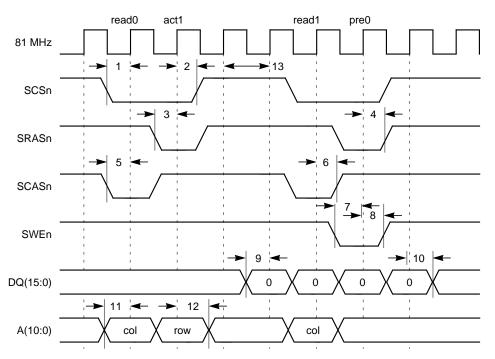

|           | 7.3  | SDRAM     | 1 Timing and Modes                                               | 7-3  |

|           | 7.4  | SDRAM     | Refresh and Arbitration                                          | 7-5  |

|           | 7.5  | Memory    | / Channel Buffer Allocation                                      | 7-6  |

|           | 7.6  | Memory    | / Frame Store Allocation                                         | 7-9  |

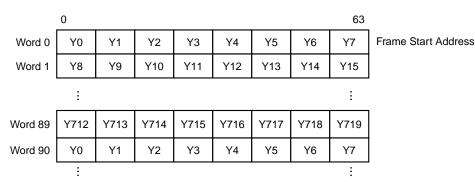

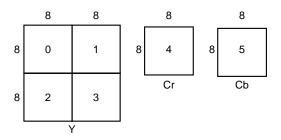

|           |      | 7.6.1     | Luma Store                                                       | 7-9  |

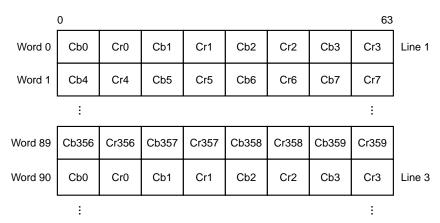

|           |      | 7.6.2     | Chroma Store                                                     | 7-9  |

|           |      | 7.6.3     | Normal Mode                                                      | 7-10 |

|           |      | 7.6.4     | Reduced Memory Mode (RMM)                                        | 7-11 |

|           | 7.7  | Summa     | ry                                                               | 7-12 |

| Chapter 8 | Vide | o Decode  | er Module                                                        |      |

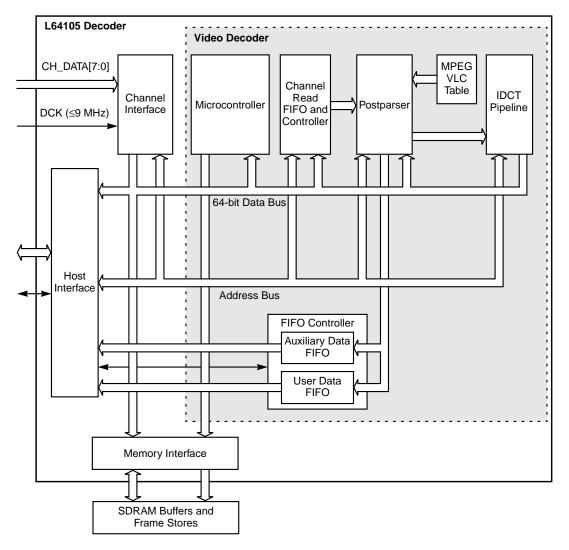

|           | 8.1  | Overvie   | W                                                                | 8-1  |

|           | 8.2  | Postpar   | ser Operation                                                    | 8-4  |

|           |      | 8.2.1     | Sequence Header                                                  | 8-4  |

|           |      | 8.2.2     | Sequence Extension                                               | 8-6  |

|           |      | 8.2.3     | Sequence Display Extension                                       | 8-7  |

|           |      | 8.2.4     | Group of Pictures Header                                         | 8-8  |

|           |      | 8.2.5     | Picture Header                                                   | 8-9  |

|           |      | 8.2.6     | Picture Coding Extension                                         | 8-11 |

|           |      | 8.2.7     | Quant Matrix Extension                                           | 8-13 |

|           |      | 8.2.8     | Host Access of Q Table Entries                                   | 8-14 |

|           |      | 8.2.9     | Picture Display Extension                                        | 8-15 |

|           |      | 8.2.10    | Copyright Extension                                              | 8-17 |

|           |      | 8.2.11    | User Data                                                        | 8-18 |

|           |      | 8.2.12    | Picture Data                                                     | 8-18 |

|           |      | 8.2.13    | Unsupported Syntax                                               | 8-18 |

|           |      | 8.2.14    | Auxiliary Data FIFO Operation                                    | 8-19 |

|           |      | 8.2.15    | User Data FIFO Operation                                         | 8-21 |

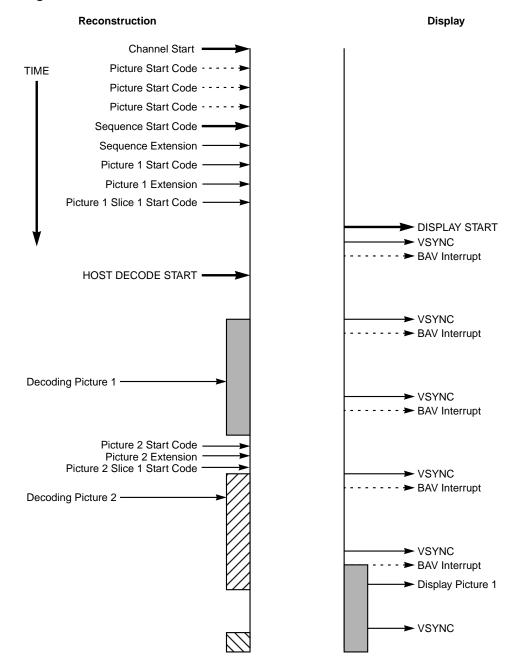

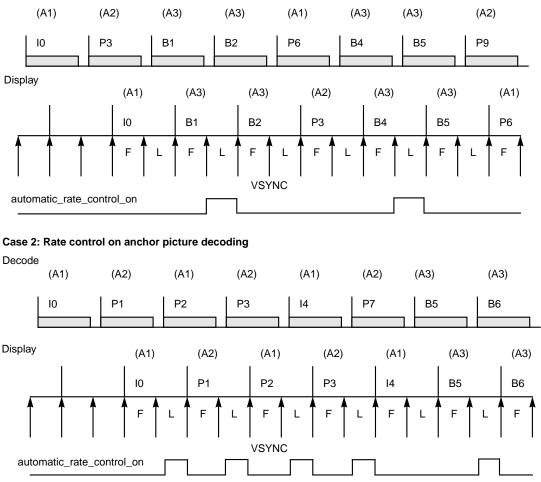

| 8.3      | Video     | Decoder Pacing                        | 8-24 |

|----------|-----------|---------------------------------------|------|

|          | 8.3.1     | Channel Start/Reset and Status Bits   | 8-25 |

|          | 8.3.2     | Video Decoder Start/Stop              | 8-26 |

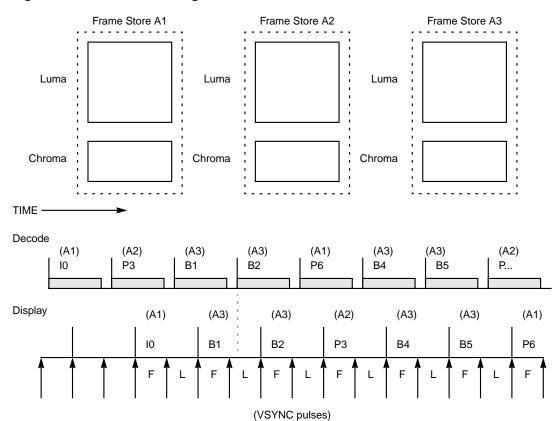

| 8.4      | Frame     | Store Modes                           | 8-30 |

|          | 8.4.1     | Normal (3-Frame Store) Mode           | 8-30 |

|          | 8.4.2     | Reduced Memory Mode                   | 8-32 |

|          | 8.4.3     | Two-Frame Store Mode                  | 8-34 |

|          | 8.4.4     | Decode and Display Frame Store Status |      |

|          |           | Indicators                            | 8-34 |

| 8.5      | Trick M   | lodes                                 | 8-35 |

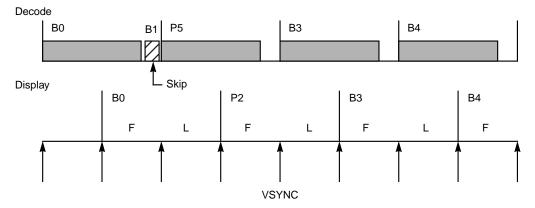

|          | 8.5.1     | Skip Frame                            | 8-35 |

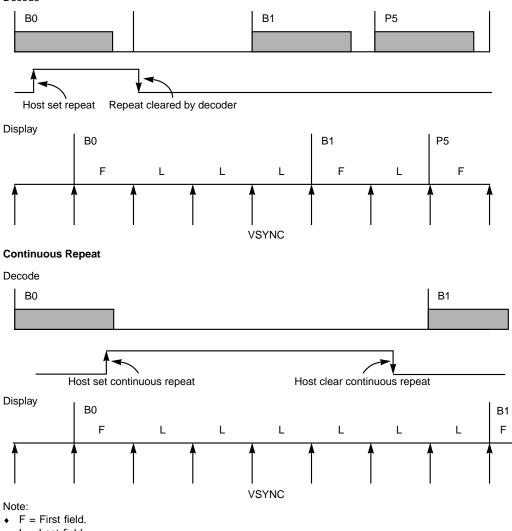

|          | 8.5.2     | Repeat Frame                          | 8-38 |

|          | 8.5.3     | Channel Buffer Underflow Panic Repeat | 8-40 |

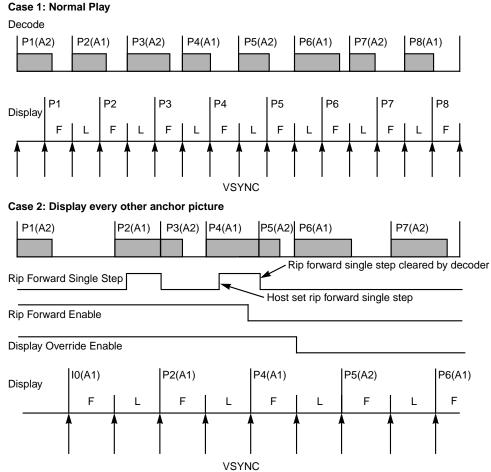

|          | 8.5.4     | Rip Forward Mode                      | 8-40 |

|          | 8.5.5     | Force Broken Link                     | 8-43 |

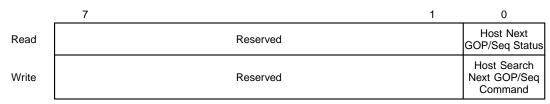

|          | 8.5.6     | Search for Next GOP/Seq Command       | 8-43 |

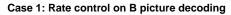

|          | 8.5.7     | Reconstruction Force Rate Control     | 8-43 |

|          | 8.5.8     | Sequence End Processing               | 8-46 |

| 8.6      | Error H   | landling and Concealment              | 8-48 |

|          | 8.6.1     | Error Conditions Detected             | 8-49 |

|          | 8.6.2     | Recovery Mechanisms                   | 8-49 |

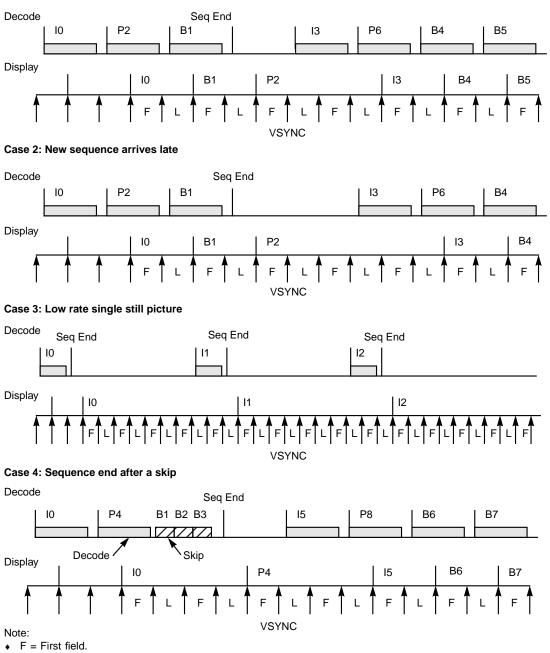

| <br>Vide | o Interfa | Ce                                    |      |

| 9.1      | Overvi    |                                       | 9-2  |

| 9.1 | Overview                             | 9-2  |

|-----|--------------------------------------|------|

| 9.2 | Television Standard Select           | 9-4  |

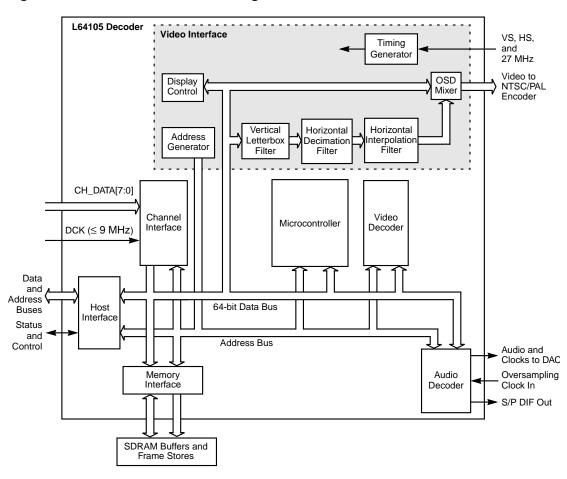

| 9.3 | Display Areas                        | 9-5  |

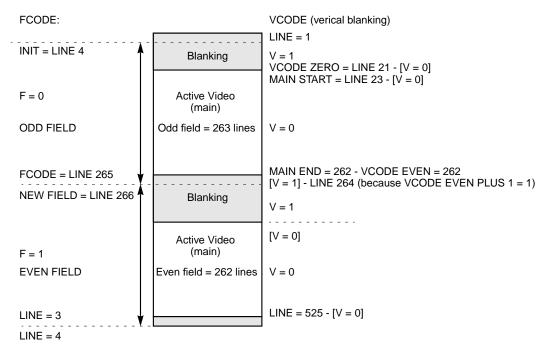

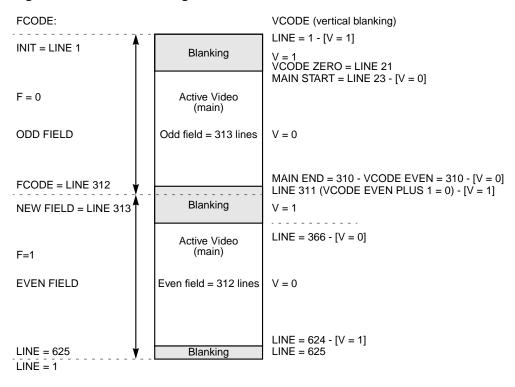

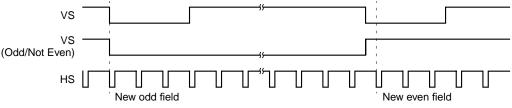

|     | 9.3.1 Vertical Timing                | 9-7  |

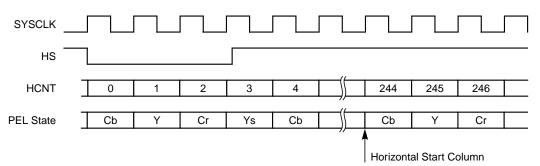

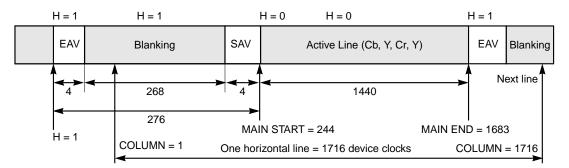

|     | 9.3.2 Horizontal Timing              | 9-10 |

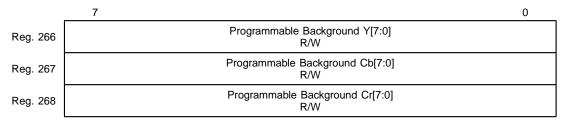

| 9.4 | Video Background Modes               | 9-12 |

| 9.5 | Still Image Display                  | 9-13 |

| 9.6 | Display Modes and Vertical Filtering | 9-16 |

| 9.7 | Reduced Memory Mode                  | 9-19 |

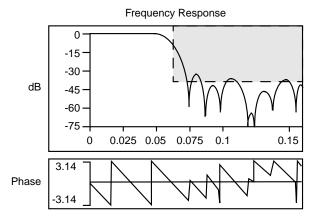

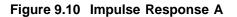

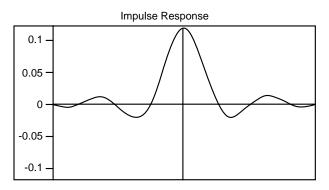

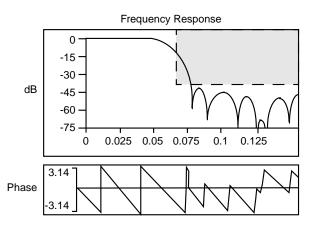

| 9.8 | Horizontal Postprocessing Filters    | 9-20 |

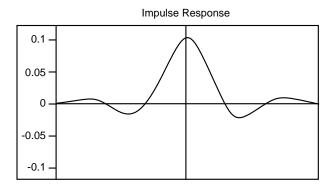

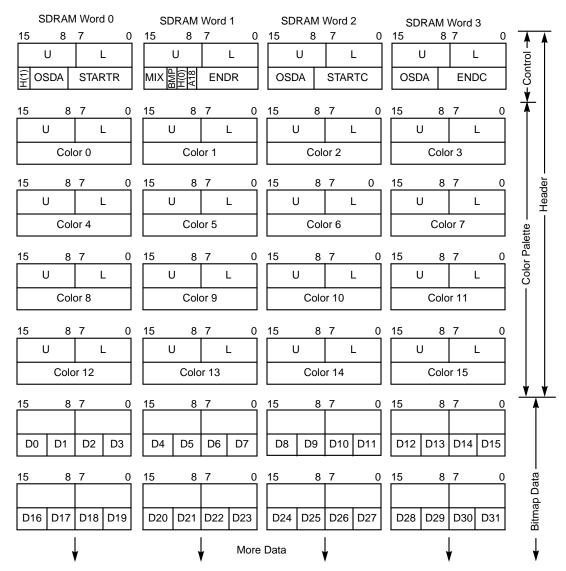

| 9.9 | On-Screen Display                    | 9-23 |

|     | 9.9.1 OSD Modes                      | 9-24 |

|     | 9.9.2 Internal OSD                   | 9-24 |

|     | 9.9.3 External OSD                   | 9-31 |

|     |                                      |      |

Chapter 9

|            | 9.10 | Pan an  | d Scan Operation                        | 9-32  |

|------------|------|---------|-----------------------------------------|-------|

|            |      | 9.10.1  | Host Controlled Pan and Scan            | 9-33  |

|            |      | 9.10.2  | Bitstream Controlled Pan and Scan       | 9-35  |

|            |      | 9.10.3  | Vertical Pan and Scan                   | 9-35  |

|            | 9.11 | Display | Freeze                                  | 9-36  |

|            | 9.12 | Pulldov | vn Operation                            | 9-38  |

|            | 9.13 | Video ( | Dutput Format and Timing                | 9-39  |

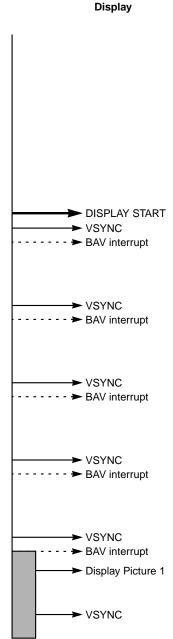

|            | 9.14 | Display | Controller Interrupts                   | 9-40  |

| Chapter 10 | Audi | o Decod | er Module                               |       |

|            | 10.1 | Feature | es                                      | 10-1  |

|            | 10.2 | Audio [ | Decoder Overview                        | 10-2  |

|            | 10.3 | Decodi  | ng Flow Control                         | 10-6  |

|            |      | 10.3.1  | Audio Decoder Play Mode                 | 10-6  |

|            |      | 10.3.2  | Audio Decoder Start/Stop                | 10-7  |

|            |      | 10.3.3  | Audio Formatter Play Mode               | 10-8  |

|            |      | 10.3.4  | Audio Formatter Start/Stop              | 10-8  |

|            |      | 10.3.5  | Autostart                               | 10-9  |

|            | 10.4 | MPEG    | Audio Decoder                           | 10-10 |

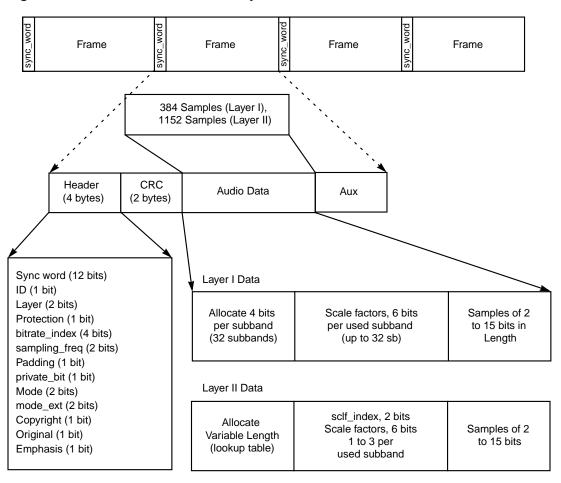

|            |      | 10.4.1  | MPEG Audio Syntax                       | 10-10 |

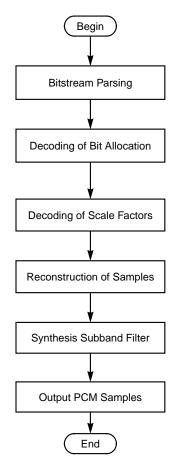

|            |      | 10.4.2  | MPEG Audio Decoding                     | 10-12 |

|            | 10.5 | Linear  | PCM Audio Decoder                       | 10-14 |

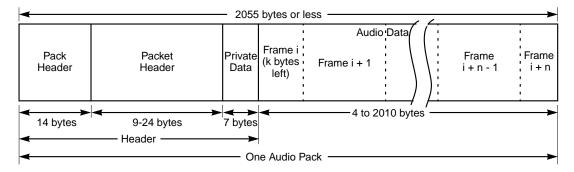

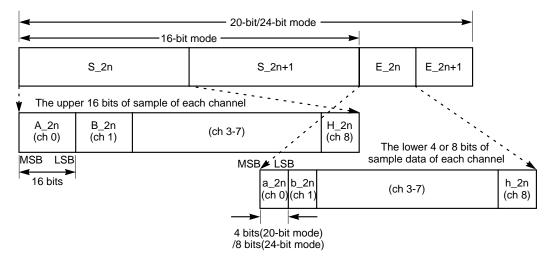

|            |      | 10.5.1  | Packet Header Syntax                    | 10-14 |

|            |      | 10.5.2  | Synchronization                         | 10-16 |

|            |      | 10.5.3  | Other Host Controls and Status          | 10-18 |

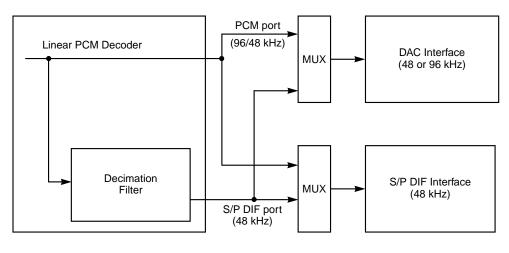

|            |      | 10.5.4  | Sample Decimation for S/P DIF           | 10-18 |

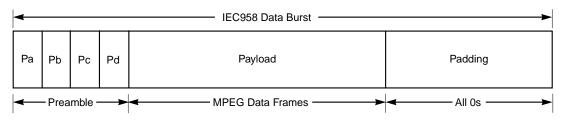

|            | 10.6 | MPEG    | Formatter                               | 10-19 |

|            |      | 10.6.1  | Number of IEC958 Frames when Formatting |       |

|            |      |         | MPEG Data                               | 10-21 |

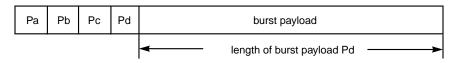

|            |      | 10.6.2  | Pd Field                                | 10-21 |

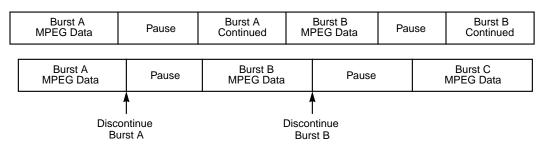

|            |      | 10.6.3  | Pause Burst                             | 10-22 |

|            |      | 10.6.4  | Synchronization                         | 10-24 |

|            |      | 10.6.5  | Error Conditions                        | 10-24 |

|            | 10.7 |         | IFO Mode                                | 10-26 |

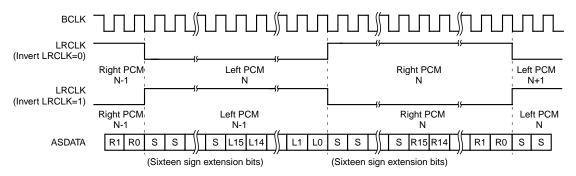

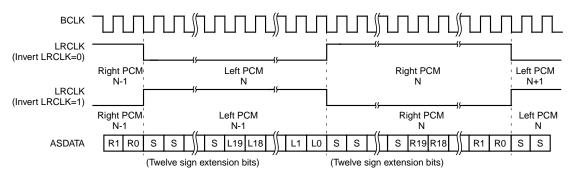

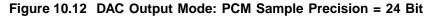

|            | 10.8 | DAC In  | terface                                 | 10-27 |

|            | 10.9 S/P DIF Interface                           | 10-29 |

|------------|--------------------------------------------------|-------|

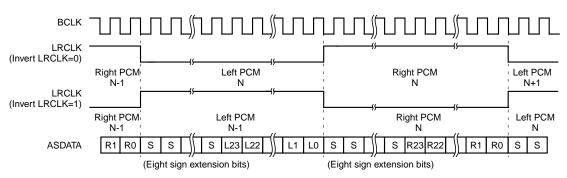

|            | 10.9.1 Biphase Mark Coding                       | 10-30 |

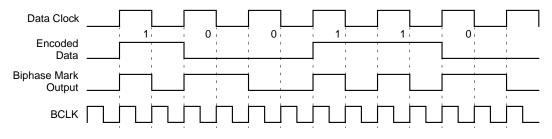

|            | 10.9.2 IEC958 Syntax                             | 10-30 |

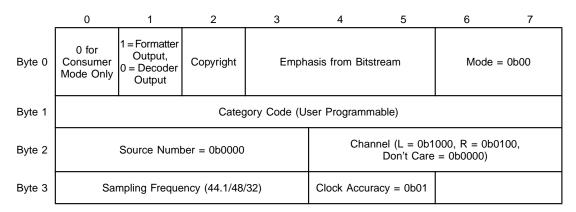

|            | 10.9.3 IEC958 Channel Status                     | 10-32 |

|            | 10.10 Clock Divider                              | 10-32 |

| Chapter 11 | Specifications                                   |       |

|            | 11.1 Electrical Requirements                     | 11-1  |

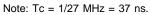

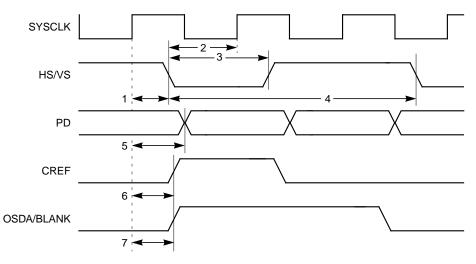

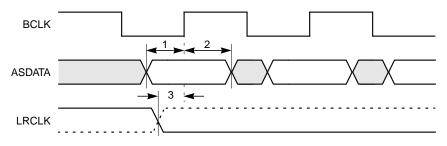

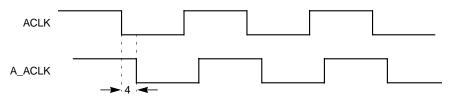

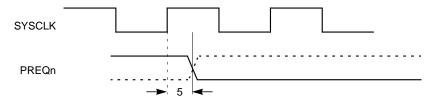

|            | 11.2 AC Timing                                   | 11-4  |

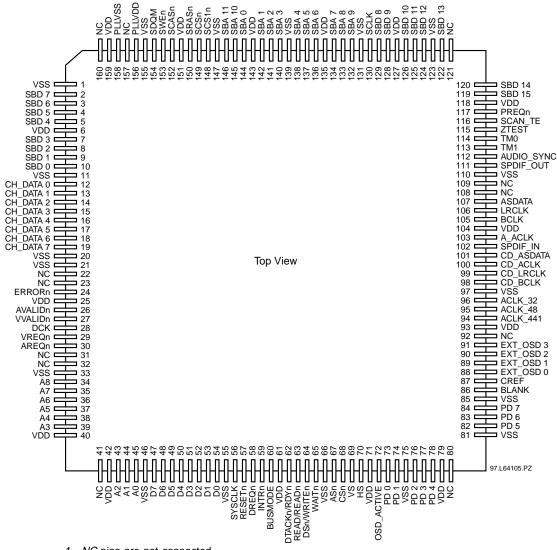

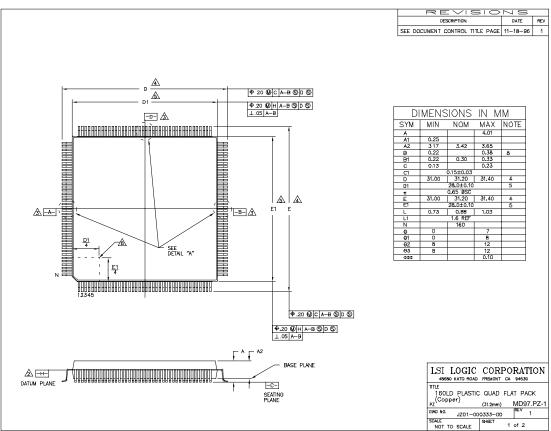

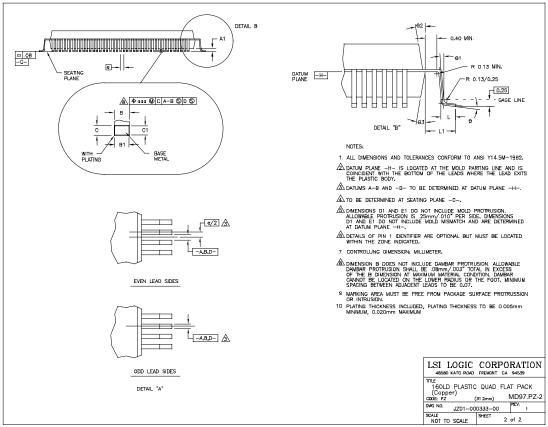

|            | 11.3 Pinouts and Packaging                       | 11-18 |

| Appendix A | Video/Audio Compression and Decompression Conc   | epts  |

|            | A.1 Video Compression and Decompression Concepts | s A-1 |

|            | A.1.1 Video Encoding                             | A-2   |

|            | A.1.2 Bitstream Syntax                           | A-5   |

|            | A.1.3 Video Decoding                             | A-7   |

|            | A.2 Audio Compression and Decompression Concepts | s A-7 |

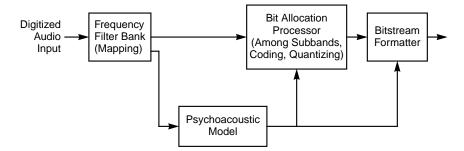

|            | A.2.1 MPEG Audio Encoding                        | A-8   |

|            | A.2.2 Audio Decoding                             | A-11  |

| Appendix B | Glossary of Terms and Abbreviations              |       |

|            | Index                                            |       |

|            | Customer Feedback                                |       |

| Figures    |                                                  |       |

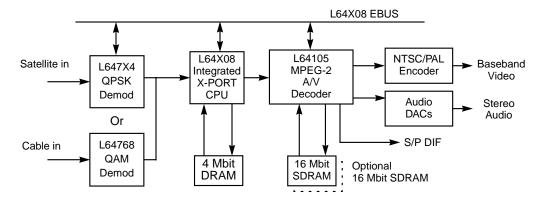

|            | 1.1 A Typical L64105 Application                 | 1-2   |

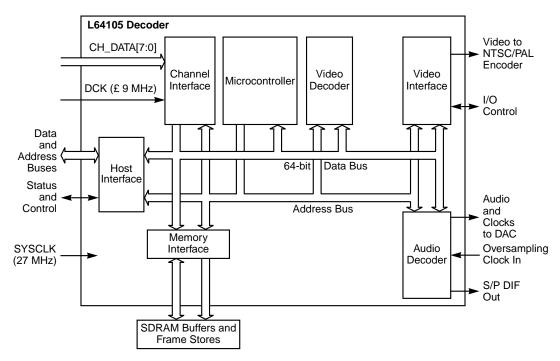

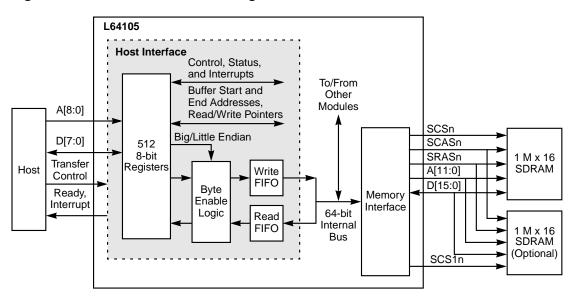

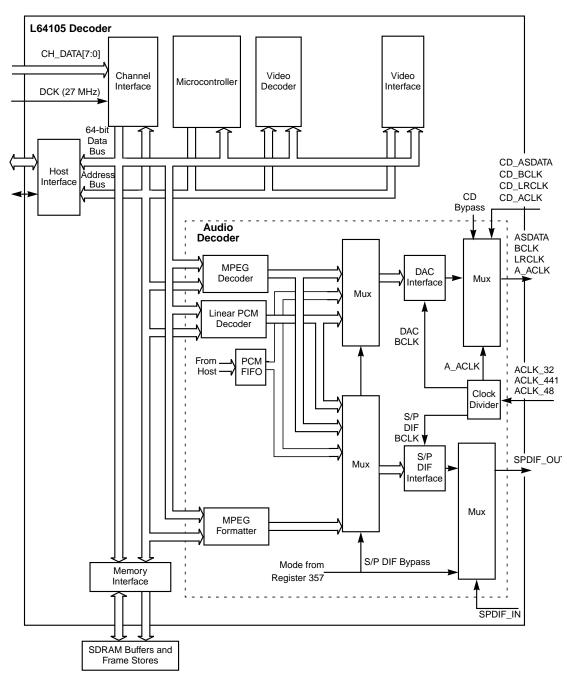

|            | 1.2 L64105 Decoder Block Diagram                 | 1-3   |

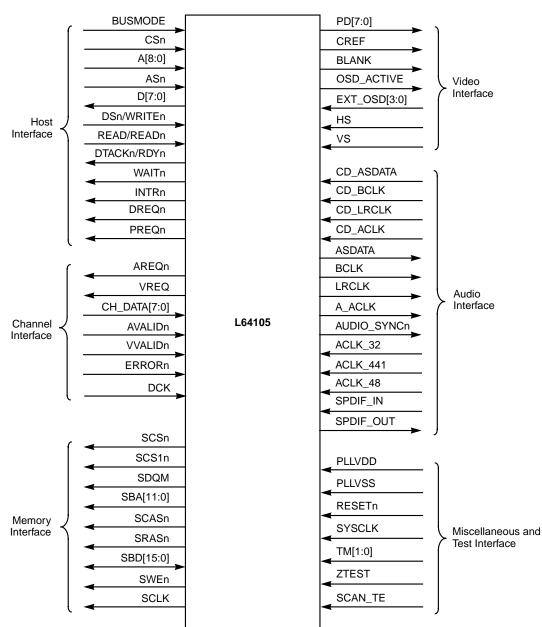

|            | 2.1 L64105 I/O Signals                           | 2-2   |

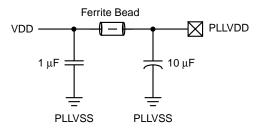

|            | 2.2 PLLVDD Decoupling Circuit                    | 2-11  |

|            | 4.1 Register 0 (0x000)                           | 4-2   |

|            | 4.2 Register 1 (0x001)                           | 4-3   |

|            | 4.3 Register 2 (0x002)                           | 4-5   |

|            | 4.4 Register 3 (0x003)                           | 4-7   |

|            |                                                  |       |

| 4.5  | Register 4 (0x004)                                                            | 4-8  |

|------|-------------------------------------------------------------------------------|------|

| 4.6  | Register 5 (0x005)                                                            | 4-9  |

| 4.7  | Register 6 (0x006)                                                            | 4-10 |

| 4.8  | Register 7 (0x007)                                                            | 4-11 |

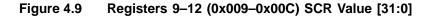

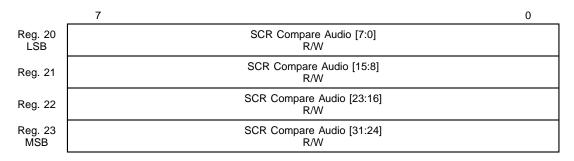

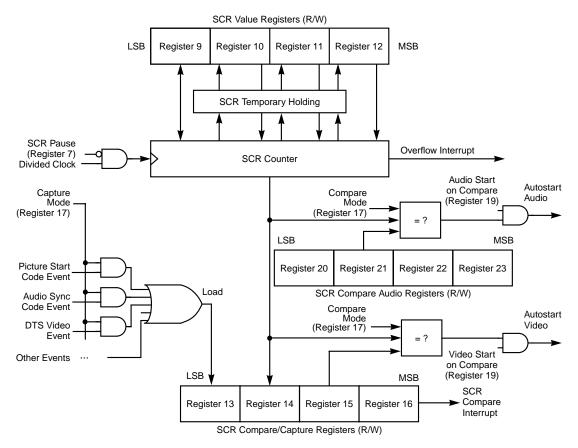

| 4.9  | Registers 9–12 (0x009–0x00C) SCR Value [31:0]                                 | 4-13 |

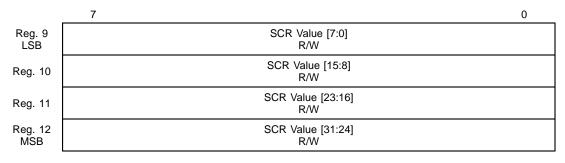

| 4.10 | Registers 13–16 (0x00D–0x010) SCR                                             |      |

|      | Compare/Capture [31:0]                                                        | 4-13 |

| 4.11 | Register 17 (0x011)                                                           | 4-14 |

| 4.12 | Register 18 (0x012)                                                           | 4-15 |

| 4.13 | Register 19 (0x013)                                                           | 4-15 |

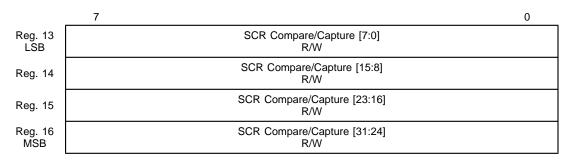

| 4.14 | Registers 20-23 (0x014-0x017)                                                 |      |

|      | SCR Compare Audio [31:0]                                                      | 4-16 |

| 4.15 | Register 28 (0x01C) Video Channel Bypass Data [7:0]                           | 4-16 |

| 4.16 | Register 29 (0x01D) Audio Channel Bypass Data [7:0]                           | 4-17 |

| 4.17 | Register 64 (0x040)                                                           | 4-17 |

| 4.18 | Register 65 (0x41)                                                            | 4-18 |

| 4.19 | Register 66 (0x042) User Data FIFO Output [7:0]                               | 4-19 |

| 4.20 | Register 67 (0x043) Aux Data FIFO Output [7:0]                                | 4-19 |

| 4.21 | Register 68 (0x044)                                                           | 4-20 |

| 4.22 | Register 69 (0x045)                                                           | 4-21 |

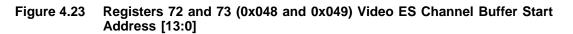

| 4.23 | Registers 72 and 73 (0x048 and 0x049)                                         |      |

|      | Video ES Channel Buffer Start Address [13:0]                                  | 4-22 |

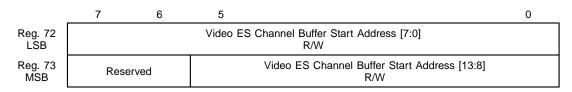

| 4.24 | Registers 74 and 75 (0x04A and 0x04B)                                         |      |

|      | Video ES Channel Buffer End Address [13:0]                                    | 4-23 |

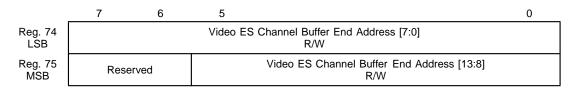

| 4.25 | Registers 76 and 77 (0x04C and 0x04D)                                         |      |

|      | Audio ES Channel Buffer Start Address [13:0]                                  | 4-23 |

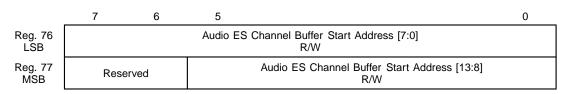

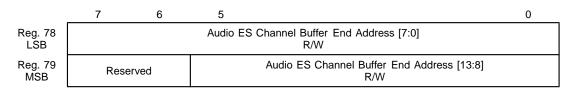

| 4.26 | Registers 78 and 79 (0x04E and 0x04F)                                         |      |

|      | Audio ES Channel Buffer End Address [13:0]                                    | 4-24 |

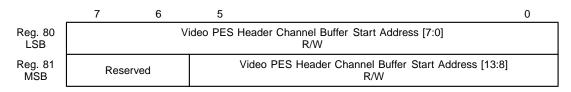

| 4.27 | Registers 80 and 81 (0x050 and 0x051)                                         |      |

|      | Video PES Header Channel Buffer Start Address [13:0]                          | 4-24 |

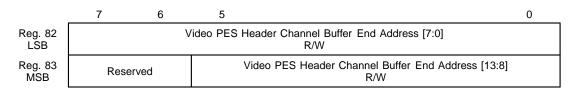

| 4.28 | Registers 82 and 83 (0x052 and 0x053)                                         |      |

|      | Video PES Header Channel Buffer End Address [13:0]                            | 4-24 |

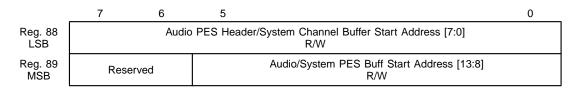

| 4.29 | Registers 88 and 89 (0x058 and 0x059)                                         |      |

|      | Audio PES Header/System Channel Buffer                                        | 4.05 |

| 4.20 | Start Address [13:0]                                                          | 4-25 |

| 4.30 | Registers 90 and 91 (0x05A and 0x05B) Audio                                   | 4-25 |

| 1 21 | PES Header/System Channel Buffer End Address [13:0]                           | 4-20 |

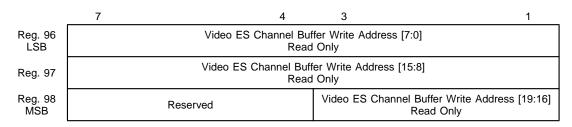

| 4.31 | Registers 96–98 (0x060–0x062)<br>Video ES Channel Buffer Write Address [19:0] | 4-26 |

|      |                                                                               | 4-20 |

| 4.32         | Registers 99–101 (0x063–0x065) Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|              | ES Channel Buffer Write Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-26         |

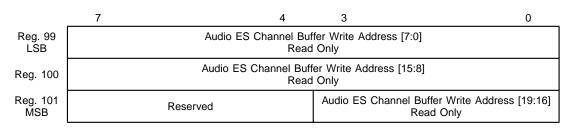

| 4.33         | Registers 102-104 (0x066-0x068) Video                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|              | PES Header Channel Buffer Write Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-27         |

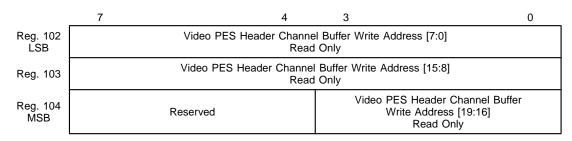

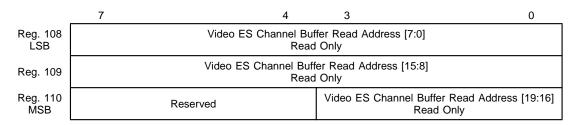

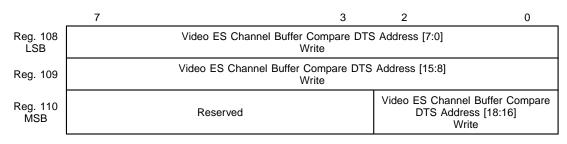

| 4.34         | Registers 108–110 (0x06C–0x06E) Video                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|              | ES Channel Buffer Read Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-27         |

| 4.35         | Registers 108–110 (0x06C–0x06E) Video                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|              | ES Channel Buffer Compare DTS Address [18:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-28         |

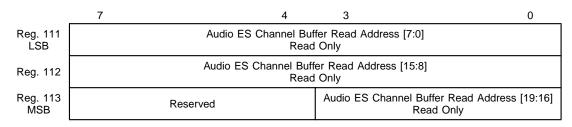

| 4.36         | Registers 111–113 (0x06F–0x071) Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|              | ES Channel Buffer Read Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-28         |

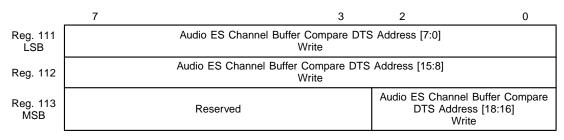

| 4.37         | Registers 111–113 (0x06F–0x071) Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|              | ES Channel Buffer Compare DTS Address [18:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-29         |

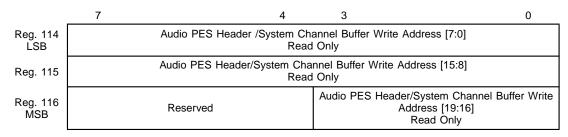

| 4.38         | Registers 114–116 (0x072–0x074) Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.00         |

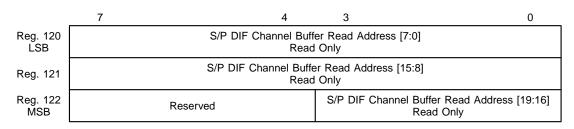

| 4.39         | PES Header/System Channel Buffer Write Address [19:0]<br>Registers 120–122 (0x078–0x07A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-29         |

| 4.39         | S/P DIF Channel Buffer Read Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-30         |

| 4.40         | Register 124 (0x07C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-30         |

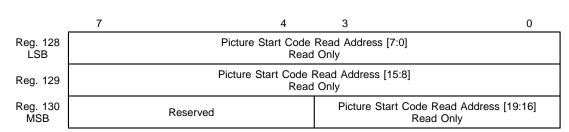

| 4.41         | Registers 128–130 (0x080–0x082)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4 00         |

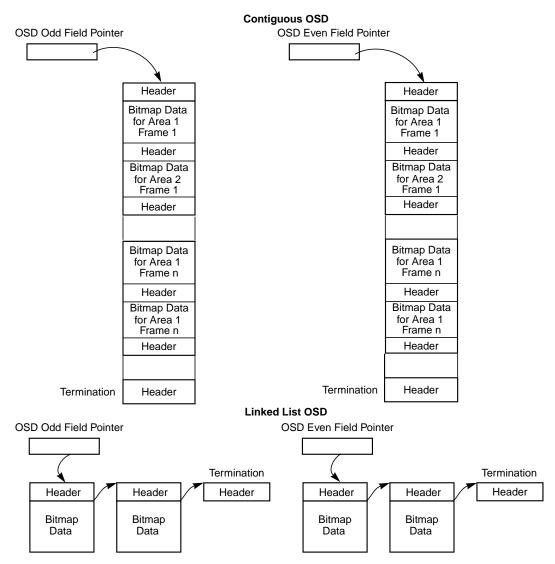

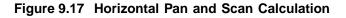

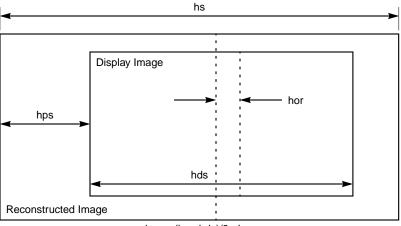

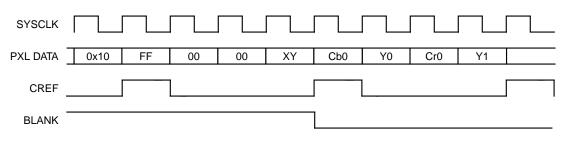

|              | Picture Start Code Read Address [19:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-31         |