# L8229

# Dual DMOS full bridge stepper/DC motor driver

## Preliminary Data

## Features

- Flexible Motor Driver configurations:

- Dual Full Bridge for one bipolar Stepping motor.

- Dual or single DC motor driver.

- Programmable by two input pins to achieve one of the following functionalities:

- Pin to pin compatible with ST L6219 or

- Stepping motor direct control with 8 current levels or

- Driver parameters control by means of Serial Port.

- Mixed Decay.

- Micro stepping function.

- BCD5 technology (No Charge Pump required).

- Supply Range from 8V to 38V.

- I<sub>OUT</sub> up to 1.2A (1.5A peak).

- **R**<sub>DSon</sub>=  $0.85\Omega$  (typ) for each switch.

- Input logic level compatible with 3.3V or 5V control signals.

- Package: PwSSO24.

# Description

This IC is designed to be very flexible in driving Stepping or DC motors.

By connecting to Vcc or to Gnu two program pins (pin 7 and 18) the use has the possibility to set up the device in different configurations.

1. The first configuration is an identical application of ST L6219 but with increased current. In this configuration L8229 provides a continuous current of the output stage up to 1.2A (1.5A peak).

The second configuration allows a functionality similar to previous one but with the possibility of choosing 8 different current

# PwSSO24

levels to perform a more accurate stepping functionality. This is achieved by multiplexing the input pins dedicated to set the evel of the current. Additionally the user can set the mixed mode decay for current recirculation.

- 3,4. The third and fourth cor figurations are intended to provide a very flexible programming for several parameters useful to drive different kind of Stepping and DC motors. This is achieved by means of a serial port interface that allows the user to configure the following parameters:

- a Current levels (32 values for each bridge).

- b) Current direction.

- c) Type of decay for Stepping motors (Mix/Slow) or for DC motors (Fast/Slow).

- d) Vref input (Ext/Int).

- e) Vref divider (:5/:10).

- f) Blanking time (4 values).

- g) Oscillator freq divider (4 values).

- h) Off time (32 values).

- i) Fast decay time (16 values).

- j) Syncronous rectification.

The functionalities of the two configurations are identical except that the internal bit address (first bit of SPI words) can be programmed to be 1 or 0: this enables two different L8229 to share a common serial bus.

## Order code

| Part number | Package | Packing |  |

|-------------|---------|---------|--|

| L8229       | PwSSO24 | Tube    |  |

| Septemb | ber 2006 |

|---------|----------|

|---------|----------|

# Contents

| 1      | Bloc  | c diagram                                   |

|--------|-------|---------------------------------------------|

| 2      | Pin o | escription                                  |

| 3      | Elec  | rical Characteristics10                     |

|        | 3.1   | Absolute maximum ratings 10                 |

|        | 3.2   | Operating ratings 10                        |

|        | 3.3   | General electrical characteristics 11       |

|        |       | 3.3.1 Output Drivers (OUTA or OUTB)11       |

|        |       | 3.3.2 Control Logic pins                    |

|        |       | 3.3.3 Analog Input Pins                     |

|        |       | 3.3.4 General                               |

| 4      | L621  | 9_HI and L6219_8 modes 13                   |

| 5      |       | 9_HI and L6219_8 Electrical characteristics |

|        | 5.1   | DC specifications 14                        |

|        | 5.2   | AC/transient specifications                 |

| 6      | L621  | 9_HI mode                                   |

|        | 6.1   | Input Logic (I0 and I1) 15                  |

|        | 6.2   | Phase                                       |

|        | 6.3   | Current Sensing                             |

|        | 6.4   | Single-pulse Generator 16                   |

|        | 6.5   | Output Stage                                |

| 0      | 6.6   | Vs, Vcc, Vref                               |

| TSU SU | L621  | 9_8 mode                                    |

| 0      | 7.1   | 8 Level Current Setting                     |

|        | 7.2   | Mixed Decay 18                              |

| 8      | L822  | 9_0 and L8229_1 modes 21                    |

|        | 8.1   | Serial interface specification 22           |

|        |       |                                             |

|              | 8.2  | SPI Bit  | definition                                                    | . 24 |

|--------------|------|----------|---------------------------------------------------------------|------|

|              |      | 8.2.1    | Word Description                                              | 24   |

|              |      | 8.2.2    | W0 (OPERATIVE: Bit 2=0, Bit 1=0)                              | 24   |

|              | 8.3  | W1 (PA   | ARAMETERS: Bit 2=0, Bit 1=1)                                  | . 25 |

|              | 8.4  | W2 (Fl   | JNCTIONAL: Bit 2=1, Bit 1=0)                                  | . 26 |

|              |      | 8.4.1    | Reading back SPI                                              | 27   |

| 9            | SPI  | program  | ming                                                          | . 28 |

|              | 9.1  | Curren   | t Control                                                     | . 28 |

|              | 9.2  | Timing   | s Control                                                     | . 30 |

|              | 9.3  | Decay    | Modes and Synchronous Rectification                           | . 33 |

|              | 9.4  | Mixed I  | Decay                                                         | . 35 |

|              |      | 1) ACTI  | VE SYNC recirculation could be divided in following cases.    | 35   |

|              |      |          | SSIVE SYNC recirculation could be divided in following cases: |      |

|              |      | 3) - SYI | NC OFF recirculation has only one case:                       | 36   |

|              |      | 4) LOW   | SIDE recirculation has only one case:                         | 37   |

|              | 9.5  |          |                                                               |      |

|              |      |          | VE SYNC recirculation is not allowed                          |      |

|              |      | 2) PASS  | SIVE SYNC recirculation                                       | 37   |

|              |      |          | C OFF                                                         |      |

|              |      | 4) LOW   | SIDE is identical to PASSIVE SYNC                             | 37   |

| 10           |      | lotor Dr | iver operation                                                | 38   |

| 10           |      |          |                                                               |      |

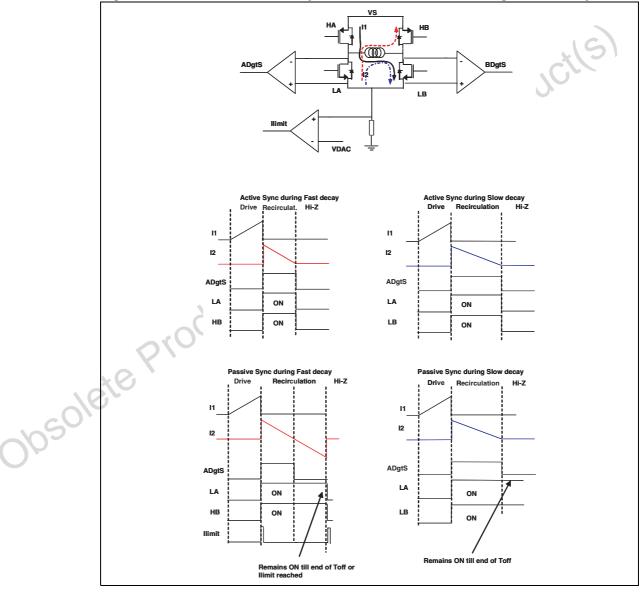

| 11           | Pack | age Info | ormation                                                      | . 40 |

| 12           | Revi | sion his | tory                                                          | . 41 |

|              | ×e   | X        |                                                               |      |

| 12<br>010501 | ere  |          |                                                               |      |

L8229

# List of tables

| Table 1.  | Pin Description                                 | . 7 |

|-----------|-------------------------------------------------|-----|

| Table 2.  | Programmable modes                              | . 9 |

| Table 3.  | Absolute maximum ratings                        | 10  |

| Table 4.  | Operating ratings (0°C £ Tj £ 125°C)            | 10  |

| Table 5.  | Output Drivers (OUTA or OUTB)                   | 11  |

| Table 6.  | Control Logic pins                              | 12  |

| Table 7.  | Analog Input Pins                               | 12  |

| Table 8.  | General                                         | 12  |

| Table 9.  | DC specifications                               | 14  |

| Table 10. | AC/transient specifications                     | 14  |

| Table 11. | Input Logic (I0 and I1).                        | 15  |

| Table 12. | Current levels                                  | 18  |

| Table 13. | AC/Transient Specification                      | 19  |

| Table 14. | Timing specifications                           | 19  |

| Table 15. | DC Specifications                               | 22  |

| Table 16. | AC/Transient Specifications                     | 22  |

| Table 17. | SPI Timing specifications                       | 23  |

| Table 18. | Word Description                                | 24  |

| Table 19. | W0                                              | 24  |

| Table 20. | W1                                              | 25  |

| Table 21. | W2                                              |     |

| Table 22. | Motor mode selected by W2                       | 28  |

| Table 23. | Nsleep mode selected by W1                      | 28  |

| Table 24. | Brake mode selected by W1                       | 28  |

| Table 25. | Vref mode selected by W2                        | 28  |

| Table 26. | Range mode selected by W2                       | 29  |

| Table 27. | Current direction selected by W0                | 29  |

| Table 28. | Current levels selected by W0 for DAC           | 29  |

| Table 29. | Oscillator frequency selected by W2             | 30  |

| Table 30. | Blanking time selected by W2                    | 30  |

| Table 31. | Fast decay time selected by W1                  |     |

| Table 32. | Toff time selected by W1                        |     |

| Table 33. | Stepping decay mode selected by W2              | 33  |

| Table 34. | DC decay mode selected by W2                    | 33  |

| Table 35. | Sync rectification selected by W1               |     |

| Table 36. | DC Motor Drivers - DC Specifications.           | 38  |

| Table 37. | DC Motor Drivers - AC/Transient Specifications. |     |

| Table 38. | DC Motor Drivers Truth Table                    |     |

| Table 39. | Document revision history                       | 41  |

| 103       |                                                 |     |

| 14        |                                                 |     |

# List of figures

| Figure 1.  | Block Diagram                                                   |

|------------|-----------------------------------------------------------------|

| Figure 2.  | Pin Connection (Top view)                                       |

| Figure 3.  | Ton and Toff                                                    |

| Figure 4.  | Half and Full Step Drive with Imax=1.2A17                       |

| Figure 5.  | Normal conduction and slow recirculation current paths          |

| Figure 6.  | L6219_8 mode Stepping Driving                                   |

| Figure 7.  | L6219_8 mode Fast and Slow Decay current paths                  |

| Figure 8.  | SPI Operations                                                  |

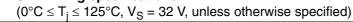

| Figure 9.  | Active and Passive synchronous rectification during Mixed Decay |

| Figure 10. | PowerSSO24 Mechanical Data & Package Dimensions                 |

obsolete Product(s). Obsolete Product(s)

57

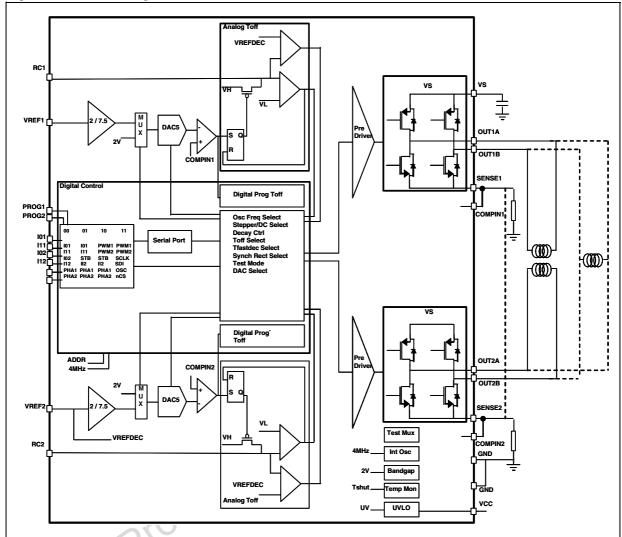

# 1 Block diagram

## Figure 1. Block Diagram

Note: T.

The sensing resistors used for the stepping motor configurations must be not inductive.

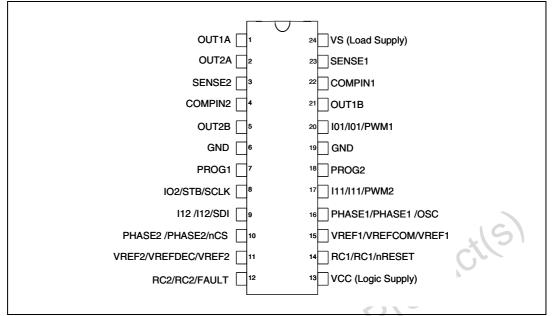

# 2 Pin description

Note: The pin functionality is different according to different configurations, so the relative pin function and name are different: the first name is relative to first configuration (L6219\_HI), the second name is relative to second configuration (L6219\_8), and the third name is relative to third and fourth configuration (L8229\_0 and L8229\_1).

| Pin N# | L6219_HI L6219_8 L8229_x<br>(Pin7&18=00) (Pin7&18=01) (Pin7&18=10<br>or 11) |              |     | Function                                                                                                                                                         |  |  |

|--------|-----------------------------------------------------------------------------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1      |                                                                             | OUT1A        | )   | Motor Driver Bridge 1 Output A.                                                                                                                                  |  |  |

| 2      |                                                                             | OUT2A        |     | Motor Driver Bridge 2 Output A.                                                                                                                                  |  |  |

| 3      | 0                                                                           | SENSE2       |     | Motor Driver Bridge 2 Sense Resistor.                                                                                                                            |  |  |

| 4      | × 0,                                                                        | COMPIN2      |     | Current Comparator input for Bridge2.                                                                                                                            |  |  |

| 5      | 10L                                                                         | OUT2B        |     | Motor Driver Bridge 2 Output B.                                                                                                                                  |  |  |

| 6      | $\mathbf{O}$                                                                | GND          |     | Ground.                                                                                                                                                          |  |  |

| 7      |                                                                             | PROG1        |     | Configuration Program pin. When used together with pin<br>18, it programs device into one of the four configurations<br>(see following Programmable Modes table) |  |  |

| 8      | 102                                                                         | IO2 STB SCLK |     | I02: Current level control bit for Bridge 2.<br>STB: Strobe input pin for current setting.<br>SCLK: Clock input pin for serial protocol.                         |  |  |

| 9      | 112                                                                         | 112          | SDI | I12: Current level control bit for Bridge 2.<br>SDI: Data input pin for serial protocol.                                                                         |  |  |

Table 1. Pin Description

| Table 1 | Pin Desc                 | ription (contin         | iued)                            |                                                                                                                                                            |  |

|---------|--------------------------|-------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin N#  | L6219_HI<br>(Pin7&18=00) | L6219_8<br>(Pin7&18=01) | L8229_x<br>(Pin7&18=10<br>or 11) | Function                                                                                                                                                   |  |

| 10      | PHASE2                   | PHASE2                  | nCS                              | PHASE2: Direction input control pin for Bridge 2.<br>nCS: Chip Select input pin for serial protocol.                                                       |  |

| 11      | VREF2                    | VREFDEC                 | VREF2                            | VREF2: Reference voltage input for Bridge 2.<br>VREFDEC: Mixed Decay Reference voltage for both<br>Bridges 1 and 2.                                        |  |

| 12      | RC2                      | RC2                     | FAULT                            | RC2: Toff input pin for Bridge 2.<br>FAULT: This pin is high when a generic fault is present.                                                              |  |

| 13      |                          | VCC                     |                                  | Logic and Low voltage analog Supply.                                                                                                                       |  |

| 14      | RC1                      | RC1                     | nRESET                           | RC1: Toff input pin for Bridge 1.<br>nRESET: Input pin for reset of serial port.                                                                           |  |

| 15      | VREF1                    | VREFCOM                 | VREF1                            | VREF1: Reference voltage input for Bridge 1.<br>VREFCOM: Common Reference voltage input for both<br>Bridges 1 and 2.                                       |  |

| 16      | PHASE1                   | PHASE1                  | OSC                              | PHASE1: Direction input control pin for Bridge 1.<br>OSC: Input for external oscillator used for timings.                                                  |  |

| 17      | 11                       | 111                     | PWM2                             | I11: Current level control bit for Bridge 1.<br>PWM2: PWM input control pin for Bridge 2 when used as<br>a DC motor driver.                                |  |

| 18      |                          | PROG2                   |                                  | Configuration Program pin. When used together with pin 7, it programs device into one of the four configurations (see following Programmable Modes table). |  |

| 19      |                          | GND                     | (                                | Ground.                                                                                                                                                    |  |

| 20      | 101                      | 101                     | PWM1                             | I01: Current level control bit for Bridge 1.<br>PWM1: PWM input control pin for bridge 1 when used<br>a DC motor driver                                    |  |

| 21      |                          | OUT1B                   |                                  | Motor Driver Bridge 1 Output B.                                                                                                                            |  |

| 22      |                          | COMPIN1                 |                                  | Current Comparator input for Bridge1.                                                                                                                      |  |

| 23      | SENSE1                   |                         |                                  | Motor Driver Bridge 1 Sense Resistor.                                                                                                                      |  |

| 24      | ×0 `                     | VS                      |                                  | Supply voltage for output stages.                                                                                                                          |  |

|         |                          |                         |                                  |                                                                                                                                                            |  |

Table 1.

Pin Description (continued)

Note:

ESD on pin PROG1 vs. V<sub>S</sub> is guaranteed up to +2KV/-1.75KV (Human Body Model, 1500Ohm, 100pF)

| Table 2.        | Programi          | nable modes                                                               |           |                                                        |

|-----------------|-------------------|---------------------------------------------------------------------------|-----------|--------------------------------------------------------|

| Pin #7<br>PROG1 | Pin # 18<br>PROG2 | Description                                                               | Mode name | Drive Configurations                                   |

| 0               | 0                 | L6219 compatible<br>(up to 1.2A lout)                                     | L6219_HI  | 1 x Stepping<br>MotorDriver.                           |

| 0               | 1                 | L6219 like with 8 current levels<br>(up to 1.2A lout) and Mixed<br>Decay. | L6219_8   | 1 x Stepping<br>MotorDriver.                           |

| 1               | 0                 | SPI operation, Chip Address = 0                                           | L8229_0   | 1 x Stepping<br>MotorDriver or 2 x DC<br>Motor Driver. |

| 1               | 1                 | SPI operation, Chip Address = 1                                           | L8229_1   | 1 x Stepping<br>MotorDriver or 2 x DC<br>Motor Driver. |

| eteP            | 10 <sup>0</sup>   | obsole                                                                    | stepre    | ducte                                                  |

Table 2. Programmable modes

## **Electrical Characteristics** 3

Independently from the selected configurations, L8229 has some electrical characteristics that are common for all modes. These are listed below while specific characteristics are listed in their respective functionality descriptions.

In all modes L8229 is powered by Vs supply voltage. The anti cross-conduction delay is controlled to provide sufficient time for cross-conduction suppression so that at no time both the upper and lower output devices (on the same side of the H bridge) are allowed to conduct simultaneously.

During an over-temperature event, when the device Tj is above Tj(shutdown), the internal thermal protection circuit disables the drive outputs until the device temperature drops below the lower thermal threshold temperature.

#### 3.1 Absolute maximum ratings

Table 3 Absolute maximum ratings

| Absolu<br>Table 3. | te maximum ratings                                           | Auct       | 5)   |

|--------------------|--------------------------------------------------------------|------------|------|

| Symbol             | Parameter                                                    | Value      | Unit |

| Vs                 | Supply voltage (including ripple).                           | 40         | V    |

| Vcc                | Logic and Low voltage analog supply voltage                  | 7          | V    |

| Ipeak              | Motor Driver Output Peak Current (see Note <sup>(1)</sup> ). | 1.5        | А    |

| Vref               | Vref input voltage.                                          | 7.5        | V    |

| Vsense             | Vsense output voltage.                                       | 2          | V    |

| Vin                | Logic input voltage.                                         | -0.3 to +7 | V    |

| Тj                 | Junction Temperature.                                        | 170        | °C   |

| T <sub>stg</sub>   | Storage Temperature.                                         | -25 to 150 | °C   |

1. This peak current is intended as start up current for max 1 second with D.C. ≤10%

## **Operating ratings** 3.2

#### Operating ratings (0°C $\leq$ T<sub>i</sub> $\leq$ 125°C) Table 4.

| Symbol | Parameter                                    | Test Condition                                                  | Min.  | Тур. | Max. | Unit |

|--------|----------------------------------------------|-----------------------------------------------------------------|-------|------|------|------|

| Vs     | Supply voltage (including ripple).           |                                                                 | 8.5   | 32   | 38   | V    |

| Vcc    | Logic and Low voltage analog supply voltage. |                                                                 | 3.135 | 5    | 5.25 | V    |

| I_Vs   | Vs Standby Current                           | L8229_0/1 configuration<br>Sleep mode:<br>NSLEEP (W1, bit3) = 0 |       | 3    | 6    | mA   |

Note: The programming pins, PROG1 and PROG2, must be soldered to Vcc or to GND and must not be driven when supplies are on.

| Symbol                     | Parameter                                                | Test Condition                      | Min. | Тур. | Max. | Unit |

|----------------------------|----------------------------------------------------------|-------------------------------------|------|------|------|------|

| I_Vcc <sub>L6219</sub>     | Vcc total supply current<br>(L6219_HI and L6219_8 modes) | Vcc=5.25V                           |      |      | 7    | mA   |

| I_Vcc <sub>L8229_0/1</sub> | Vcc total supply current<br>(L8229_0 or L8229_1 mode)    | Vcc=5.25V                           |      |      | 7    | mA   |

|                            |                                                          | Vcc=5.25V,<br>NSLEEP (W1, bit3) = 0 |      |      | 3    | mA   |

| Vin                        | Logic input voltage                                      |                                     | 0    |      | Vcc  | V    |

| lout                       | Motor Driver Output Current (continuous)                 |                                     |      |      | 1.2  | А    |

Operating ratings (0°C  $\leq$  T $_{j} \leq$  125°C) (continued) Table 4.

#### 3.3 **General electrical characteristics**

(0°C  $\leq$   $T_{j}$   $\leq$  125°C,  $V_{S}$  = 32V, unless otherwise specified)

#### 3.3.1 **Output Drivers (OUTA or OUTB)**

#### Output Drivers (OUTA or OUTB) Table 5.

| (0°C $\leq$ T <sub>j</sub> $\leq$ 125°C, V <sub>S</sub> = 32V, unless otherwise specified) |                            |                                                            |      |      |      |      |  |

|--------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------|------|------|------|------|--|

| 3.3.1                                                                                      | Output Drivers (OUTA       |                                                            | d    | 51   |      |      |  |

| Table 5.                                                                                   | Output Drivers (OUTA or    | OUTB)                                                      |      | 1    |      |      |  |

| Symbol                                                                                     | Parameter                  | Test Condition                                             | Min. | Тур. | Max. | Unit |  |

| D                                                                                          | Output ON Resistance       | Source Driver, I <sub>LOAD</sub> =-1.2A                    | X    |      | 1.3  | Ω    |  |

| R <sub>DSON</sub>                                                                          | (T <sub>j</sub> = 70 °C)   | Sink Driver, I <sub>LOAD</sub> =+1.2A                      | 1    |      | 1.3  | Ω    |  |

| lcex                                                                                       | Output leakage current     | Vout = Vs or Gnd                                           |      | 50   |      | μA   |  |

| V                                                                                          | Rody Diodo Forward Valtago | Sink Diode, IF = 1.2A                                      |      | 1    | 1.5  | V    |  |

| V <sub>F</sub>                                                                             | Body Diode Forward Voltage | Source Diode, IF = 1.2A                                    |      | 1    | 1.5  | V    |  |

|                                                                                            | . 1                        | Vs=12V, $R_L$ =12 $\Omega$ connected to Vs or Gnd          |      |      |      |      |  |

| tr                                                                                         | Output rising time         | Vs=24V, R <sub>L</sub> =38 $\Omega$ connected to Vs or Gnd | 100  |      | 350  | ns   |  |

|                                                                                            | 01000                      | Vs=36V, R <sub>L</sub> =58 $\Omega$ connected to Vs or Gnd |      |      |      |      |  |

|                                                                                            | -×0 <sup>7</sup>           | Vs=12V, $R_L$ =12 $\Omega$ connected to Vs or Gnd          |      |      |      |      |  |

| tf                                                                                         | Output falling time        | Vs=24V, R <sub>L</sub> =38 $\Omega$ connected to Vs or Gnd | 75   |      | 300  | ns   |  |

| 102                                                                                        |                            | Vs=36V, R <sub>L</sub> =58 $\Omega$ connected to Vs or Gnd |      |      |      |      |  |

| Tdead                                                                                      | Shoot through delay        |                                                            |      | 1    |      | μA   |  |

#### **Control Logic pins** 3.3.2

#### Table 6. **Control Logic pins**

| Symbol              | Parameter         | Test Condition                           | Min. | Тур. | Max. | Unit |

|---------------------|-------------------|------------------------------------------|------|------|------|------|

| V <sub>IN (H)</sub> | Input Voltage     | All logic input for<br>Vcc = 3.3V or 5V. | 2    |      |      | V    |

| V <sub>IN (L)</sub> | Input Voltage     | All logic input for<br>Vcc = 3.3V or 5V. |      |      | 0.8  | V    |

| I <sub>IN (H)</sub> | Input Current     | VIN = 2.0V                               | -20  |      | 20   | μA   |

| I <sub>IN (L)</sub> | Input Current     | VIN = 0.8V                               | -20  |      | 20   | μA   |

| Isdi                | SDI Input Current |                                          | -200 |      | 50   | μA   |

#### 3.3.3 **Analog Input Pins**

#### Table 7. **Analog Input Pins**

|                     | Analog input i ins                |                        |                 |      |      |      |      |  |  |  |

|---------------------|-----------------------------------|------------------------|-----------------|------|------|------|------|--|--|--|

| Symbol              | Description                       | 0                      | Condition       | Min. | Тур. | Max. | Unit |  |  |  |

| V <sub>ref</sub>    | V <sub>ref</sub> Input Voltage    |                        |                 | 1.5  | 1    | 7.5  | V    |  |  |  |

| I <sub>Vref</sub>   | V <sub>ref</sub> Input Current    | V <sub>ref</sub> = 5.0 | /               |      | 0    | 200  | μA   |  |  |  |

| V <sub>compin</sub> | V <sub>compin</sub> Input Voltage |                        |                 | 0    | 2    | 0.75 | V    |  |  |  |

| I <sub>compin</sub> | V <sub>compin</sub> Input Current |                        | k               | 0,   | 1    | 20   | μA   |  |  |  |

| V <sub>sense</sub>  | V <sub>sense</sub> Input Voltage  |                        | 10              |      |      | 0.75 | V    |  |  |  |

| I <sub>sense</sub>  | V <sub>sense</sub> Output Current |                        | 60 <sup>1</sup> |      | 50   | 100  | μA   |  |  |  |

| 3.3.4               |                                   |                        |                 |      |      |      |      |  |  |  |

| Table 8.            | General                           | aí                     |                 |      |      |      |      |  |  |  |

| Symbol              | Parameter                         | 31                     | Test Condition  | Min. | Тур. | Max. | Unit |  |  |  |

#### 3.3.4 General

#### Table 8. General

| Symbol                    | Parameter                                      | Test Condition | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------------|----------------|------|------|------|------|

| Vsc_off                   | Sense comparator offset                        |                |      | ±10  |      | mV   |

| Vs_UV                     | Vs undervoltage threshold                      |                |      | 7.5  |      | V    |

| Vs_UVhys                  | Vs undervoltage hysteresis                     |                |      | 300  |      | mV   |

| Vcc_UV                    | Vcc undervoltage threshold                     |                |      | 2.9  |      | V    |

| Vcc_UVhys                 | Vcc undervoltage hysteresis                    |                |      | 150  |      | mV   |

| Tj(shutdown)              | Thermal shutdown junction temperature          |                |      | 160  |      | °C   |

| Tj(enable_<br>hysteresis) | Thermal enable junction temperature hysteresis |                |      | 25   |      | °C   |

# 4 L6219\_HI and L6219\_8 modes

When configured in one of these modes the device has a functionality similar to ST L6219 with some improvements. The output stage is made by LDMOS devices instead of the BJT present in ST L6219. This allows a reduced saturation drop and an higher current handling with similar power dissipation. Additionally the recirculation diodes are internally available as a part of the LDMOS structure.

In case of:

- a) Undervoltage detection (UVD) or

- b) Thermal shutdown (TSD),

the outputs will be in Hi-Z mode (all outputs off) respectively until the supplies voltage goes over the UV threshold plus hysteresis or the themperature decreases below TSD threshold minus hysteresis.

In case of:

c) Overcurrent detection (OCD)

the outputs will be in Hi-Z mode (all outputs off) and will remain in this condition until the device is reset by turning off and on VCC supply voltage.

Common electrical characteristics of both L6219\_HI and L6219\_8 modes are listed below, while specific characteristics are listed in their respective functionality descriptions.

57

## 5 L6219\_HI and L6219\_8 Electrical characteristics

(0°C  $\leq$  T\_i  $\leq$  125°C, V\_S = 32 V, unless otherwise specified)

#### **DC** specifications 5.1

#### Table 9. **DC** specifications

| Symbol      | Description                                                                           | Condition                                     | Min  | Тур | Max  | Unit |

|-------------|---------------------------------------------------------------------------------------|-----------------------------------------------|------|-----|------|------|

|             |                                                                                       | $10 \leq 0.8 V\!, 11 \leq 0.8 V$              | 9.25 | 10  | 10.5 |      |

| Vref/Vsense | Current Limit Threshold (at trip point ) for $V_{ref} = 5V$ and $T_i \le 70^{\circ}C$ | $I0 \geq 2.0V, I1 \leq 0.8V$                  | 13.5 | 15  | 16.5 |      |

|             |                                                                                       | $10 \leq 0.8 \text{V},  11 \geq 2.0 \text{V}$ | 25.5 | 30  | 34.5 |      |

#### **AC/transient specifications** 5.2

#### Table 10. **AC/transient specifications**

| Symbol | Parameter                          | Test Condition       | Min. | Тур. | Max. | Uni |

|--------|------------------------------------|----------------------|------|------|------|-----|

| Toff   | Cut off time                       | Rt=56Kohm, Ct =820pF | 05   | 50   |      | μA  |

| Tdelay | Turn Off Delay for comparator      |                      |      | 1    |      | μA  |

| Tblank | Blanking time for Sense comparator | let.                 | 0    | 1    |      | μA  |

|        | Ċ                                  | (5) 000              |      |      |      |     |

|        | ete Product                        | (5) 000              |      |      |      |     |

L8229

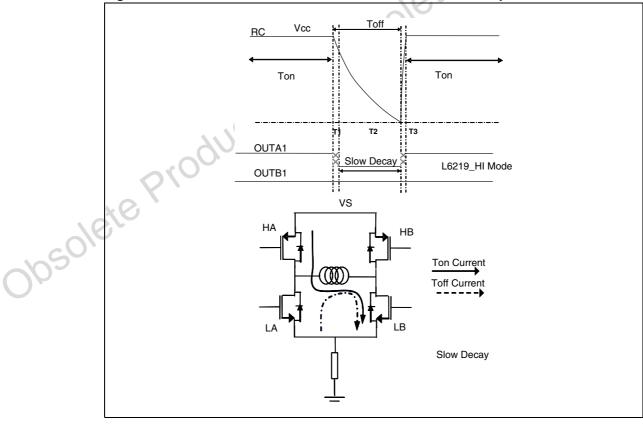

# 6 L6219\_HI mode

The device will be set into the L6219\_HI mode by asserting PROG1 and PROG2 pins (pin 7 and 18) to 00.

In the L6219\_HI mode, the device is pin and function compatible with the ST L6219 device. Please note that while ST L6219 allows good power dissipation by simply connecting to gnd the center pins because of the batwing frame, the L8229 power dissipation will be good only by connecting the exposed pad to a proper heat sink.

The circuit is intended to drive both windings of a bipolar stepping motor. The peak current control is made through switch mode regulation. There is a choice of three different current levels with the two logic inputs I01 and I11 for winding 1 and I02 and I12 for winding 2. The current can also be completely switched off.

## 6.1 Input Logic (I0 and I1)

The current level in the motor winding is selected with these inputs (see *Figure 1*). If any of the logic inputs is left open, the circuit will treat it as a high level input.

| Table 11. | Input Logi | c (I0 and I1) |

|-----------|------------|---------------|

|-----------|------------|---------------|

| 10X | I1X | Current Level              |

|-----|-----|----------------------------|

| Н   | Н   | No Current                 |

| L   | Н   | Low Current: 1/3 Io max    |

| н   | L   | Medium Current: 2/3 Io max |

| L   | L   | Maximum Current: Io max    |

## 6.2 Phase

This input pin determines the direction of current flow in the windings, depending on the motor connections. The signal is fed through a Schmitt trigger for noise immunity, and through a time delay in order to guarantee that no cross conduction occurs in the output stage during phase-shift. High level on the PHASE input causes the motor current to flow from OutA through the motor winding to OutB.

# Current Sensing

This part contains a low pass filter for the external current sensing resistor (Rs) and three comparators. Only one comparator is active at a time: it is activated by the input logic according to the current level chosen with signals I0 and I1.

The motor current flows through the sensing resistor Rs and when the current has increased so that the voltage across Rs becomes higher than the reference voltage on the other comparator input, the comparator output goes high, triggering the pulse generator.

The max peak current Imax can be defined by:

Imax = Vref / 10 Rs

57

Note that lout max is 1.2A and the wide range allowed for Vref requires the choice of a suitable sense resistor to prevent current range over the maximum.

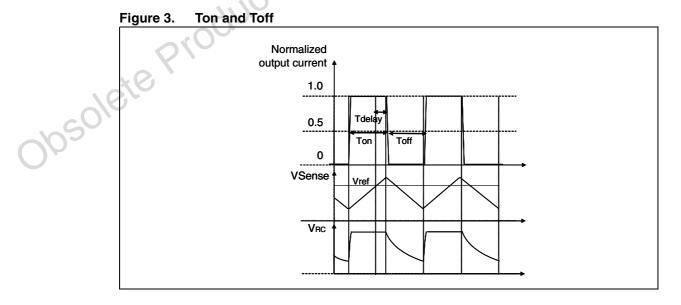

## 6.4 Single-pulse Generator

The pulse generator is a monostable circuit triggered on the positive going edge of the comparator output. The circuit output is high during the pulse time Toff that is determined by the time components Rt and Ct.

Toff =~ 1.1 x RtCt

(including switching dead time)

The single pulse turns off the power switch connected to the motor winding, causing the winding current to decrease during Toff. If a new trigger signal should occur during Toff it will be ignored.

## 6.5 Output Stage

Each of the two outputs stage contains four LDMOS transistors (P and N channel) connected in two H Bridges. The intrinsic body diode of the LDMOS serve as recirculation diode for flyback current.

The LDMOS are used to switch the power supply to the motor winding, thus driving a constant current through the winding. It should be noted however, that is not permitted to short-circuit the outputs. Internal circuitry is added in order to increase the accuracy of the motor current particularly with low current levels.

## 6.6 Vs, Vcc, Vref

The circuit will stand any order of turn-on or turn-off of the supply voltages Vs and Vcc. Normal dV/dt values are then assumed.

Preferably, Vref should be tracking Vcc during power-on and power-off if Vs is established.

57

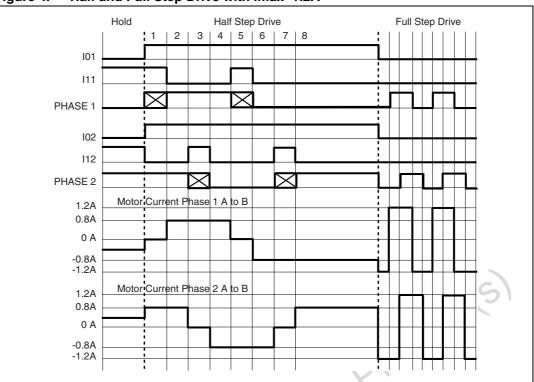

Figure 4. Half and Full Step Drive with Imax=1.2A

Figure 5. Normal conduction and slow recirculation current paths.

17/42

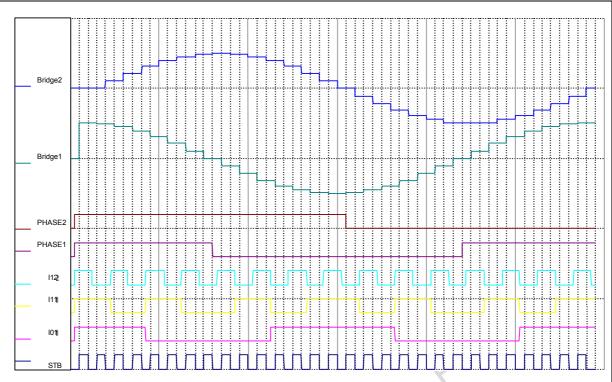

#### L6219 8 mode 7

A second configuration of the device is achieved when PROG1 and PROG2 pins (pin 7 and 18) are asserted to 01. The device is now configured into the L6219\_8 configuration. This device mode function is similar to L6219 HI, but with the possibility of using 8 current levels instead of 4, to implement a more accurate microstepping function and with the possibility to set a mixed decay for recirculation current. The remaining functionalities are identical to L6219\_HI mode.

#### 7.1 8 Level Current Setting

This setting is achieved by using pin 8 (STB) as a strobe for latching the current setting control inputs. The rising edge of STB will latch the I01, I11 and I12 inputs for decoding current levels settings for Bridge 1. Similarly the falling edge will latch the I01, I11 and I12 inputs for decoding current levels settings for Bridge 2.

In order to allow a good similitude to sine drive, the levels set by the input pins are not equally spaced but are choosen to approximate a sinusoidal wave.

On power up, the device is by default into a no current drive state for both H Bridges and will start driving only upon the rising or falling edges of STB.

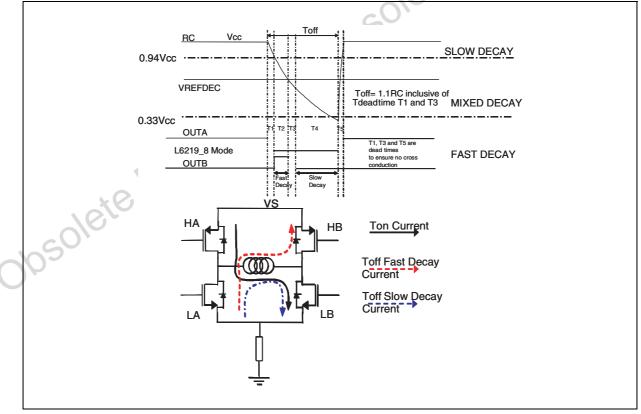

#### 7.2 **Mixed Decay**

VREFCOM input (pin 15) is the reference voltage for both bridges while VREFDEC input (pin 11) is a voltage reference for decay control. When the current setting is set from an higher level to a lower level, the device can be set to perform:

- 1. Slow decay (current is recirculated throught the low side drivers) when VREFDEC > 0.94Vcc.

- A mix of Fast followed by Slow decay when 0.33Vcc < VREFDEC < 0.94Vcc. 2.

- 3. Fast decay (current is recirculated from Sense to Vs) when VREFDEC < 0.33Vcc.

In case 2, VREFDEC voltage is compared with the RC discharging voltage during the Toff duration. Until the RC voltage is above VREFDEC there will be fast decay: the bridge outputs will be driven to enable recirculation from Rsense to VS. For RC voltages below VREFDEC, the bridges will be driven to recirculate through the low side drivers. (see Figure 8)

|      | Table 12. | Current le | evels |     |                              |          |

|------|-----------|------------|-------|-----|------------------------------|----------|

|      | STB       | 101        | l11   | l12 | Current level                |          |

| -nsu | <u> </u>  |            |       |     | Bridge1                      | Bridge 2 |

| )    | <u> </u>  | 0          | 0     | 0   | No current                   | -        |

|      | _F        | 0          | 0     | 1   | I <sub>OUT</sub> / Imax=0.22 | -        |

|      | <u> </u>  | 0          | 1     | 0   | I <sub>OUT</sub> / Imax=0.42 | -        |

|      | 1         | 0          | 1     | 1   | I <sub>OUT</sub> / Imax=0.61 | -        |

|      |           | 1          | 0     | 0   | I <sub>OUT</sub> / Imax=0.77 | -        |

|      | Ŀ         | 1          | 0     | 1   | I <sub>OUT</sub> / Imax=0.87 | -        |

|  | Table | 12. | Current | levels |

|--|-------|-----|---------|--------|

|--|-------|-----|---------|--------|

| Table 12. | Current le | vels (contil | nuea) |                              |                              |

|-----------|------------|--------------|-------|------------------------------|------------------------------|

| STB       | 101        | 111          | l12   | Current level                |                              |

| <u> </u>  | 1          | 1            | 0     | I <sub>OUT</sub> / Imax=0.93 | -                            |

| <u> </u>  | 1          | 1            | 1     | I <sub>OUT</sub> / Imax=1    | -                            |

| 7         | 0          | 0            | 0     | -                            | I <sub>OUT</sub> / Imax=1    |

|           | 0          | 0            | 1     | -                            | I <sub>OUT</sub> / Imax=0.93 |

|           | 0          | 1            | 0     | -                            | I <sub>OUT</sub> / Imax=0.87 |

|           | 0          | 1            | 1     | -                            | I <sub>OUT</sub> / Imax=0.77 |

|           | 1          | 0            | 0     | -                            | I <sub>OUT</sub> / Imax=0.61 |

| 7         | 1          | 0            | 1     | -                            | I <sub>OUT</sub> / Imax=0.42 |

|           | 1          | 1            | 0     | -                            | I <sub>OUT</sub> / Imax=0.22 |

|           | 1          | 1            | 1     | -                            | No current                   |

Current levels (continued) Table 12

#### AC/Transient Specification Table 13.

| Table 13. | AC/Transient Specification  |     |               | IG  |

|-----------|-----------------------------|-----|---------------|-----|

| Symbol    | Description                 | Min | Тур           | Мах |

| MD_h      | Mixed decay trip point high |     | 0.93Vcc ±75mV |     |

| MD_I      | Mixed decay trip point low  |     | 0.33Vcc ±50mV |     |

|           |                             |     |               |     |

#### Table 14. **Timing specifications**

$(0^{\circ}C \le T_i \le 125^{\circ}C, V_S = 32 V$ , unless otherwise specified)

| 6  | MHz<br>ns |

|----|-----------|

|    | ns        |

|    |           |

|    | ns        |

| 10 | ns        |

|    | ns        |

|    | ns        |

|    |           |

Figure 6.

#### Figure 7. L6219\_8 mode Fast and Slow Decay current paths

L6219\_8 mode Stepping Driving

57

productls

# 8 L8229\_0 and L8229\_1 modes

When in these modes, the device can be programmed via a serial interface. This allows a very precise microstepping functionality as well as the control of several parameters related to the motor functionality.

In this configuration there is also the possibility of driving two DC motors by means of two pulse width modulated (PWM) control signals.

The parameters that can be set are the following:

- 1. Current levels (32 values for each bridge).

- 2. Current direction.

- 3. Type of decay for stepping motor (Mix/Slow).

- 4. Vref input (Ext/Int)

- 5. Vref divider (:5/:10).

- 6. Blanking time (4 values).

- 7. Oscillator freq divider (4 values).

- 8. Off time (32 values).

- 9. Fast decay time (16 values).

- 10. Synchronous rectification (Active/Passive/LowSide/Off).

- 11. Choose of driving a Stepping or DC motor.

- 12. Possibility of paralleling bridges (in DC motor drive).

- 13. Slow or fast decay (in DC motor drive).

- 14. Possibility of setting outputs in brake mode.

- 15. Possibility of asserting Sleep mode to reduce current consumption and put outputs in HI-Z.

When in L8229 modes, pin 12 (FAULT) is used to provide a "Generic Fault" signal that is intended as a warning for the user. In case of:

a) Undervoltage detection (UVD): no action is taken on output bridges and the device will be working, leaving to the user the action of stopping the output bridges functionality.

During UVD event, the Generic Fault signal is pulled high.

- b) Thermal shutdown (TSD): output bridges will be in Hi-Z mode (all outputs off) until the temperature decreases below TSD threshold minus hysteresis. During TSD event, the Generic Fault signal is pulled high.

- c) Over current detection (OCD): output bridges will be in Hi-Z mode. Depending on the motor (Stepping or DC according to W2 bit 14), the OCD status will be latched as follows:

- for stepping motor driving the OCD status will be latched until SPI is reset by means of nRESET pin.

- for DC motor driving the OCD status will be latched until next positive PWM edge occurs.

For both above cases, the Generic Fault signal is pulled high until the OCD status persists.

)bsole

## Table 15. DC Specifications

$(0^{\circ}C \le T_i \le 125^{\circ}C, V_S = 32 V, unless otherwise specified)$

| Name                 | Description                                                     | Conditions | Min  | Тур | Мах  | Units |

|----------------------|-----------------------------------------------------------------|------------|------|-----|------|-------|

| Vref voltage         | Internal reference voltage                                      |            | 1.94 | 2   | 2.06 | V     |

| I <sub>off-rev</sub> | Reverse current detection offset (in Active Sync recirculation) |            |      | ±50 |      | mA    |

## Table 16. AC/Transient Specifications

$(0^{\circ}C \le T_i \le 125^{\circ}C, V_S = 32 V$ , unless otherwise specified)

| Name | Description          | Conditions | Min | Тур | Мах | Units |

|------|----------------------|------------|-----|-----|-----|-------|

| Osc  | Oscillator frequency |            |     | 4   |     | MHz   |

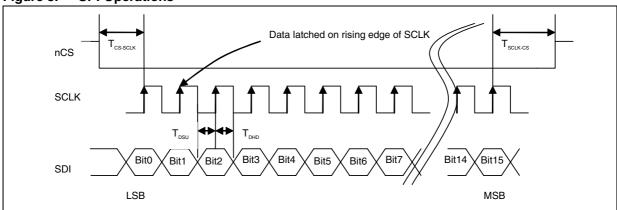

## 8.1 Serial interface specification

This device, when in L8229\_0 or L8229\_1 configuration, is managed via a Serial Interface Port for a total of 16 bits with 4 different words. This port provides an interface between the chip and external digital ASIC. For the user this port is write-only: assigned read registers are for test mode purposes only.

The interface consists of 3 signal lines: chip select (nCS, active low), serial clock (SCLK) and serial data input (SDI).

The digital ASIC initiates a serial transfer by pulling low the chip select line, nCS. Then it generates 16 clock pulses on SCLK while presenting the serial data on input SDI. The data is shifted into the L8229 on the rising edge of SCLK. The digital ASIC presents the data on SDI one setup time (Tdsu) before the rising edge of SCLK. The data is held constant for the data hold time (Tdhd) beyond the SCLK rising edge. The less significant bit, or LSB, is the first to be shifted out of the digital ASIC and into the chip, followed by the remaining bits. The last of the 16 bits is the most significant bit or MSB. SDI will remain at the value presented with the last bit of data. The nCS line is then returned to a high state. The low to high transition of nCS loads the data into the internal L8229 input register where all the inputs are presented to their appropriate functions in a parallel mode.

In the event that there are less or more than 16 SCLK rising edges during nCS=0, the device will interprete the packet as invalid. This enables the SPI bus to be shared with others devices with similar packet skipping functionality (and with programming word length different from 16 bits), without the use of nCS.

The outputs of the serial input port shall not "glitch" during any operation.

The serial interface is cleared by nRESET signal applied to pin 14. When nRESET=0, output stages are in Hi-Z mode (all outputs off). Please note that neither TSD nor OCD reset the SPI.

L8229

## Figure 8. SPI Operations

## Table 17. SPI Timing specifications

| Name     | Description                               | MIN | ТҮР | MAX  | Units |

|----------|-------------------------------------------|-----|-----|------|-------|

| Fclk     | Serial clock frequency                    |     | 8   | 12   | MHz   |

| Tclh     | SCLK high width                           | 30  |     | 710. | ns    |

| Tcll     | SCLK low width                            | 30  | 0   | 2.0  | ns    |

| Tcs-sclk | Delay nCS falling to first SCLK rising    | 10  | 010 |      | ns    |

| Tsclk-cs | Delay last SCLK rising edge to nCS rising | 10  |     |      | ns    |

| Tdsu     | Data valid to SCLK set up time            | 10  |     |      | ns    |

| Tdhd     | Data hold time                            | 10  |     |      | ns    |

| Tcs-cs   | Delay required from (n-1)CS to nCS        | 10  |     |      | ns    |

| Trd      | SDI rise time                             | 0   |     | 20   | ns    |

| Tfd      | SDI fall time                             | 0   |     | 20   | ns    |

| Trfc     | SCLK rise/fall time                       | 0   |     | 20   | ns    |

| solete   | Produce                                   |     |     |      |       |

#### 8.2 **SPI Bit definition**

#### **Word Description** 8.2.1

Each of the 3 words used to program the chip when in L8229\_0 or L8229\_1 mode has the 3 LSB used to address the word as follows:

Table 18. **Word Description**

| BIT #   | NAME                              | Val    | Value DESCRIPTION |                                                                                                                                                                                                         |  |

|---------|-----------------------------------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0       | 0 CHIP ADDRESS                    |        | )                 | This value addresses the word to chip #0 (if two L8229 are present on the same board and a single nCS line is used). Chip address is assigned by configuring the PROG bit according to <i>Table 2</i> . |  |

|         | OTHE ADDIESS                      | 1      | 1                 | This value addresses the word to chip #1 (if two L8229 are present on the same board and a single nCS line is used). Chip address is assigned by configuring the PROG bit according to <i>Table 2</i> . |  |

|         | -                                 | Bit 2  | Bit 1             | aller 1                                                                                                                                                                                                 |  |

|         |                                   | 0      | 0                 | W0: OPERATIVE register                                                                                                                                                                                  |  |

| 1 and 2 | WORD ADDRESS 1,<br>WORD ADDRESS 2 | 0      | 1                 | W1: PARAMETERS register                                                                                                                                                                                 |  |

|         |                                   | 1      | 0                 | W2 : FUNCTIONAL register                                                                                                                                                                                |  |

|         |                                   | 1      | 1                 | Not allowed                                                                                                                                                                                             |  |

| 8.2.2   | W0 (OPERATI                       | VE: Bi | t 2=0, I          | Bit 1=0)                                                                                                                                                                                                |  |

## W0 (OPERATIVE: Bit 2=0, Bit 1=0) 8.2.2

This word is mainly used to fix the current level and direction in the bridge.

1

#### Table 19. W0

| BIT # | NAME             | RESET<br>VALUE | DESCRIPTION                                                                                                                                                                                                      |

|-------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | CHIP ADDRESS     | 00             | This bit is used to select if the informations provided by bits 1 to 15 are referred to chip 0 or chip 1. This is useful in the case that two L8229 are present on the same board and a single nCS line is used. |

| 1     | WORD ADDRESS 1   | 0              | This is the LSB of the two bits used to address the word                                                                                                                                                         |

| 2     | WORD ADDRESS 2   | 0              | This is the MSB of the two bits used to address the word                                                                                                                                                         |

| 3     | DAC1 BIT 1 (LSB) | 0              | LSB for DAC intended to regulate the current of Bridge 1                                                                                                                                                         |

| 4     | DAC1 BIT 2       | 0              | BIT2 for DAC intended to regulate the current of Bridge 1                                                                                                                                                        |

| 5     | DAC1 BIT 3       | 0              | BIT3 for DAC intended to regulate the current of Bridge 1                                                                                                                                                        |

| 6     | DAC1 BIT 4       | 0              | BIT4 for DAC intended to regulate the current of Bridge 1                                                                                                                                                        |

| 7     | DAC1 BIT 5 (MSB) | 0              | MSB for DAC intended to regulate the current of Bridge 1                                                                                                                                                         |

| 8     | PHASE 1          | 0              | Controls the direction of current flow for Bridge1.<br>A logic 0 level causes current flow from A (source) to B (sink).                                                                                          |

| 9     | DAC2 BIT1 (LSB)  | 0              | LSB for DAC intended to regulate the current of Bridge 2                                                                                                                                                         |

| BIT # | NAME             | RESET<br>VALUE | DESCRIPTION                                                                                                             |

|-------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| 10    | DAC2 BIT 2       | 0              | BIT2 for DAC intended to regulate the current of Bridge 2                                                               |

| 11    | DAC2 BIT 3       | 0              | BIT3 for DAC intended to regulate the current of Bridge 2                                                               |

| 12    | DAC2 BIT 4       | 0              | BIT4 for DAC intended to regulate the current of Bridge 2                                                               |

| 13    | DAC2 BIT 5 (MSB) | 0              | MSB for DAC intended to regulate the current of Bridge 2                                                                |

| 14    | PHASE 2          | 0              | Controls the direction of current flow Bridge 2.<br>A logic HIGH level causes current flow from A (source) to B (sink). |

| 15    | PARALLEL OUTPUT  | 0              | This bit must be set to 1 when otputs are paralled to drive a single DC motor                                           |

#### Table 19. W0 (continued)

## W1 (PARAMETERS: Bit 2=0, Bit 1=1) 8.3

| Tab | le | 20. | W1 |

|-----|----|-----|----|

|-----|----|-----|----|

| Table 2 |                | ainly usec     | to set motor related parameters.                                                                                                                                                                                 |

|---------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT #   | NAME           | RESET<br>VALUE | DESCRIPTION                                                                                                                                                                                                      |

| 0       | CHIP ADDRESS   | 0              | This bit is used to select if the informations provided by bits 1 to 15 are referred to chip 0 or chip 1. This is useful in the case that two L8229 are present on the same board and a single nCS line is used. |

| 1       | WORD ADDRESS 1 | 0              | This is the LSB of the two bits used to address the word.                                                                                                                                                        |

| 2       | WORD ADDRESS 2 | 0              | This is the MSB of the two bits used to address the word.                                                                                                                                                        |

| 3       | NSLEEP         | 0              | This bit is used to decide if the device should exit sleep mode.                                                                                                                                                 |

| 4       | OFF1           | 0              | LSB for fixing the Toff time (see following <i>Table 32</i> ).                                                                                                                                                   |

| 5       | OFF2           | 0              | BIT 2 for fixing the Toff time (see following <i>Table 32</i> ).                                                                                                                                                 |

| 6       | OFF3           | 0              | BIT 3 for fixing the Toff time (see following <i>Table 32</i> ).                                                                                                                                                 |

| 7       | OFF4           | 0              | BIT 4 for fixing the Toff time (see following <i>Table 32</i> ).                                                                                                                                                 |

| 8       | OFF5           | 0              | MSB for fixing the Toff time (see following Table 32).                                                                                                                                                           |

| 9       | FASTDEC1       | 0              | LSB for fixing the Fast Decay time (see following Table 31).                                                                                                                                                     |

| 10      | FASTDEC2       | 0              | BIT 2 for fixing the Fast Decay time (see following <i>Table 31</i> ).                                                                                                                                           |

| 11      | FASTDEC3       | 0              | BIT 3 for fixing the Fast Decay time (see following <i>Table 31</i> ).                                                                                                                                           |

| 12      | FASTDEC4       | 0              | MSB for fixing the Fast Decay time (see following <i>Table 31</i> ).                                                                                                                                             |

| 13      | SYNCRECT1      | 0              | LSB to decide the rectification mode (see following Table 35).                                                                                                                                                   |

| 14      | SYNCRECT2      | 0              | MSB to decide the rectification mode (see following <i>Table 35</i> ).                                                                                                                                           |

| 15      | Brake          | 0              | This bit is used to put outputs in brake mode                                                                                                                                                                    |

# 8.4 W2 (FUNCTIONAL: Bit 2=1, Bit 1=0)

This word is mainly used to set the functional mode

## Table 21. W2

| BIT # | NAME                 | RESET<br>VALUE | DESCRIPTION                                                                                                                                                                                                    |

|-------|----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | CHIP ADDRESS         | 0              | This bit is used to select if the informations provided by bits 1 to 15 ar referred to chip 0 or chip 1. This is useful in the case that two L8229 ar present on the same board and a single nCS line is used. |

| 1     | WORD ADDRESS 1       | 0              | This is the LSB of the two bits used to address the word.                                                                                                                                                      |

| 2     | WORD ADDRESS 2       | 0              | This is the MSB of the two bits used to address the word.                                                                                                                                                      |

| 3     | MIX/SLOW 1 (St. mot) | 0              | This bit is to decide if Slow or Mixed Decay is applied to Bridge 1 (Stepping motor).                                                                                                                          |

| 4     | MIX/SLOW 2 (St. mot) | 0              | This bit is to decide if Slow or Mixed Decay is applied to Bridge 2 (Stepping motor).                                                                                                                          |

| 5     | REFERENCE INT/EXT    | 0              | This bit is used to decide if the reference voltage will be internal (0) or external (1)                                                                                                                       |

| 6     | RANGE                | 0              | This bit is to decide if the reference voltage will be divided by 10 (0) o by 5 (1).                                                                                                                           |

| 7     | BLANK LSB            | 0              | This is the LSB bit used to fix the Blanking time (see following <i>Table 30</i> ).                                                                                                                            |

| 8     | BLANK MSB            | 0              | This is the MSB bit used to fix the Blanking time (see following <i>Table 30</i> ).                                                                                                                            |

| 9     | OSC LSB              | 0              | This is the LSB bit used to fix the Oscillator values (see following <i>Table 29</i> ).                                                                                                                        |

| 10    | OSC MSB              | 0              | This is the MSB bit used to fix the Oscillator values (see following <i>Table 29</i> ).                                                                                                                        |

| 11    | TEST 1               | 0              | This bit is used for trim mode.                                                                                                                                                                                |

| 12    | TEST 2               | 0              | This bit is used for trim mode.                                                                                                                                                                                |

| 13    | TEST 3               | 0              | This bit is used for trim mode.                                                                                                                                                                                |

| 14    | STEP/DC              | 0              | This bit is used to set the drive of a Stepping Motor (0) or a DC Motor (1).                                                                                                                                   |

| 15    | SLOW/FAST (DC mot)   | 0              | This bit is used to decide if Slow (0) or Fast (1) decay is applied to DC Motor configuration                                                                                                                  |

#### 8.4.1 **Reading back SPI.**

When W2 bit 11 to 13 are to 111, read back from SPI is enabled. This function is to check the actual data in W0 and W1; W2 can't be read back.

To read back the following procedure is requested:

- 1. Set PROG1=1, PROG2=0

- Write W0 and W1 to SDI 2.

- 3. Write W2 (with bits 11, 12, 13 set to 111) to SDI. This enables read back mode from SPI.

- Write 0001 1111 1111 1111 to SDI (the first three bits mean that W0 is requested to be 4. read out, the other bits have no sense just to fill the blank bits). This allows to check if the SDI output is W0 bit3~15.

- Write W2 (with bits 11, 12, 13 set to 111) to SDI. This enables read back mode from 5. SPI.

- 6. Write 0101 1111 1111 1111 to SDI (the first three bits mean that W1 is requested to be read out, the other bits have no sense just to fill the blank bits). This allows to check if the SDI output is W1 bit3~15.

a swite fur ans write fur obsolete production If the data to be read out are the same as the data write in, it means write function of SPI is

# 9 SPI programming

On power up, the device is by default in sleep mode. Before coming out from sleep, the device needs to be programmed to drive either Stepping or DC motor. This is controlled by W2 bit 14. Default is stepping motor drive.

Table 22. Motor mode selected by W2

| Bit 14 | Mode           |

|--------|----------------|

| 0      | Stepping motor |

| 1      | DC motor       |

The device can be awoken from the sleep mode by means of the bit 3 of W1.

| Table 23. | Nsleep | mode | selected | bv W1 | ſ |

|-----------|--------|------|----------|-------|---|

|           |        |      |          |       | - |

| Bit 3 | Mode   |      |

|-------|--------|------|

| 0     | Sleep  | *(5) |

| 1     | Normal | CL   |

The device can be set in brake mode ( both outputs are LL) by means of W1 bit 15. Please note that Brake mode overcomes Nsleep mode.

## Table 24. Brake mode selected by W1

| Bit 15 | Mode   |  |

|--------|--------|--|

| 0      | Normal |  |

| 1      | Brake  |  |

# 9.1 Current Control

Current level in the motor is set by means of a combination of Vref (ext or int), Rsense and DAC control bits.

The max current is set as follows:

## Imax = Vref / (Range x Rsense)

Vref can be set to be internal at 2V or externally applied to VREF1 and VREF2 pins. On power up, the default is the internal 2V.

Table 25.Vref mode selected by W2

| Bit 5 | Mode                     |  |

|-------|--------------------------|--|

| 0     | Internal ref. 2V         |  |

| 1     | External ref. (7.5V max) |  |

Vref voltage is divided according to Range value that is defined by W2 bit 6 to be either 10 or 5.

| Bit 6 | Mode       |  |

|-------|------------|--|

| 0     | Range = 10 |  |

| 1     | Range = 5  |  |

## Table 26. Range mode selected by W2

The direction of current is determined by W0 bits 8 and 14. During Ton, outputs will be according to following table:

|  | Table 27. | <b>Current direction</b> | selected by W0 |  |

|--|-----------|--------------------------|----------------|--|

|--|-----------|--------------------------|----------------|--|

| Bit 8 (14) | OUT A | OUT B |

|------------|-------|-------|

| 0          | L     | Н     |

| 1          | Н     | L     |

The 5 bit DACs for each Bridge enable an accurate resolution control defined by Current levels table below. The current level lset is then defined as:

Iset = Vdac / (Range x Rsense)

where:

## Vdac = (DAC/31) x Vref

where DAC is defined from 0 to 31, so the current level is fixed by W0 bits 7 (MSB) to 3 (LSB) (13 to 9) as in following table.

| Table 28. | Current levels selected by W0 for DAC |

|-----------|---------------------------------------|

|        | Bit 7 (13) | Bit 6 (12) | Bit 5 (11) | Bit 4 (10) | Bit 3 (9) | IPH_A (B)/Imax |

|--------|------------|------------|------------|------------|-----------|----------------|

|        | 0          | 0          | 0          | 0          | 0         | 0              |

|        | 0          | 0          | 0          | 0          | 1         | 1/31           |

|        | 0          | 0          | 0          | 1          | 0         | 2/31           |

|        | 0          | 0, 5       | 0          | 1          | 1         | 3/31           |

|        | 0          | 0          | 1          | 0          | 0         | 4/31           |

|        | 0          | 0          | 1          | 0          | 1         | 5/31           |

|        | 0          | 0          | 1          | 1          | 0         | 6/31           |

|        | 0          | 0          | 1          | 1          | 1         | 7/31           |

| 10     | 0          | 1          | 0          | 0          | 0         | 8/31           |

| Obsole | 0          | 1          | 0          | 0          | 1         | 9/31           |

| 05     | 0          | 1          | 0          | 1          | 0         | 10/31          |

| 06     | 0          | 1          | 0          | 1          | 1         | 11/31          |

|        | 0          | 1          | 1          | 0          | 0         | 12/31          |

|        | 0          | 1          | 1          | 0          | 1         | 13/31          |

|        | 0          | 1          | 1          | 1          | 0         | 14/31          |

|        | 0          | 1          | 1          | 1          | 1         | 15/31          |

|        | 1          | 0          | 0          | 0          | 0         | 16/31          |

| Bit 7 (13) | Bit 6 (12) | Bit 5 (11) | Bit 4 (10) | Bit 3 (9) | IPH_A (B)/Imax |

|------------|------------|------------|------------|-----------|----------------|

| 1          | 0          | 0          | 0          | 1         | 17/31          |

| 1          | 0          | 0          | 1          | 0         | 18/31          |

| 1          | 0          | 0          | 1          | 1         | 19/31          |

| 1          | 0          | 1          | 0          | 0         | 20/31          |

| 1          | 0          | 1          | 0          | 1         | 21/31          |

| 1          | 0          | 1          | 1          | 0         | 22/31          |

| 1          | 0          | 1          | 1          | 1         | 23/31          |

| 1          | 1          | 0          | 0          | 0         | 24/31          |

| 1          | 1          | 0          | 0          | 1         | 25/31          |

| 1          | 1          | 0          | 1          | 0         | 26/31          |

| 1          | 1          | 0          | 1          | 1         | 27/31          |

| 1          | 1          | 1          | 0          | 0         | 28/31          |