LA4302T

## 8.5 W $\times$ 1 BTL or 4 W $\times$ 2 (SE) Audio Frequency Power Amplifier for Desktop PCs

## **Overview**

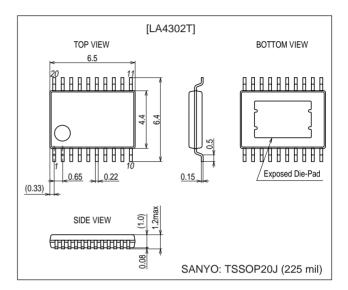

The LA4302T is a power amplifier IC that is designed for desktop PCs and applications that use a 4-layer (copper foil) circuit board. It is provided in an ultraminiature package (TSSOP20J) that includes heat dissipation pad.

This IC supports both single-channel high-power (BTL) operation and single ended (SE) stereo operation. These operating modes are controlled with an electronic switch. This product also supports the use of a common circuit board in multiple products.

## **Features**

- Ultraminiature package (TSSOP20J): Can be surface mounted on a 4-layer circuit board and requires no heat sink.

- $P_O = 8.5 \text{ W} \times 1$  channel ( $V_{CC} = 12 \text{ V}$ ,  $R_L = 8 \Omega$ , THD = 10%: BTL operation)

- $P_O = 4 \text{ W} \times 2 \text{ channels}$  ( $V_{CC} = 12 \text{ V}$ ,  $R_L = 4 \Omega$ , THD = 10%: SE operation)

- Built-in electronic switch for switching between BTL and SE operation

- Full complement of built-in protection circuits, including circuits that protect against shorting to the power supply, shorting to ground, load shorting, and overheating)

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## **Specifications** Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol              | Conditions                               | Ratings     | Unit |

|-----------------------------|---------------------|------------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max | No signal                                | 18          | V    |

| Maximum output current      | I <sub>O</sub> peak | Per channel                              | 1.5         | A    |

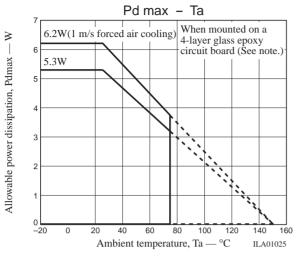

| Allowable power dissipation | Pd max              | When mounted on the Sanyo circuit board* | 5.3         | W    |

| Operating temperature       | Topr                |                                          | -20 to +75  | °C   |

| Storage temperature         | Tstg                |                                          | -40 to +150 | °C   |

\*: Dimensions: 114.3 × 76.1 × 1.6 mm³, Material: 4-layer glass epoxy printed circuit board

Inner copper foil layers: 74 × 67 mm, back surface copper foil: 30% of the circuit board area, with 15 through holes in the IC heat dissipation pad area for connection to the layers.

#### Operating Conditions at Ta = $25^{\circ}C^{*1}$

| Parameter                                | Symbol             | Conditions    | Ratings  | Unit |

|------------------------------------------|--------------------|---------------|----------|------|

| Recommended supply voltage               | V <sub>CC</sub>    |               | 12       | V    |

| Recommended load resistance range        | R <sub>L</sub> op  | BTL operation | 8        | Ω    |

| Recommended load resistance range        |                    | SE operation  | 4        | Ω    |

| Allowable operation supply voltage range | V <sub>CC</sub> op | *2            | 10 to 16 | V    |

Notes: 1. Must be used in ranges of  $V_{CC}$ ,  $R_L$ , and the output level such that the maximum ratings are not exceeded.

2. The LA4302T is designed for use with a V<sub>CC</sub> voltage of 12 V. Even if this device is used within the allowable operation supply voltage range, at high output levels or at high ambient temperatures, problems, such as sound being interrupted due to the operation of the various protection circuits, become more likely to occur at higher V<sub>CC</sub> voltages. In particular, if V<sub>CC</sub> exceeds 12 V, designers must verify carefully that problems such as inadequate thermal dissipation or excessive voltage fluctuations (with the load current) in the power supply do not occur in the end product.

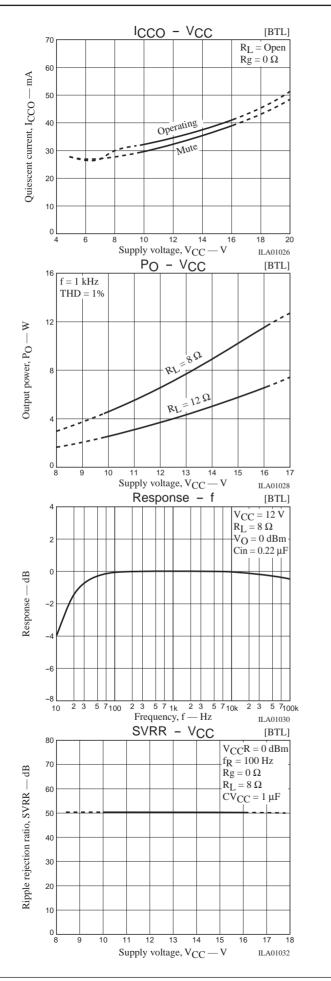

#### Operating Characteristics at Ta = 25°C, $V_{CC}$ = 12 V, $R_L$ = 8 $\Omega$ (BTL), 4 $\Omega$ (SE), f = 1 kHz, Rg = 600 $\Omega$

| Deventer                                                       | Cumhal                | O and little and                                           |      | L La it |                 |        |  |

|----------------------------------------------------------------|-----------------------|------------------------------------------------------------|------|---------|-----------------|--------|--|

| Parameter                                                      | Symbol                | Conditions                                                 | min  | typ     | max             | - Unit |  |

| Quiescent current                                              | Icco                  | $Rg = 0, R_L = open$                                       |      | 40      | 90              | mA     |  |

| Standby current                                                | lst                   | V <sub>STB</sub> = 0 V                                     |      | 0       | 10              | μA     |  |

|                                                                |                       | Amplifier operation                                        | 8.8  |         | V <sub>CC</sub> | V      |  |

| Standby, mute, amplifier operation threshold voltages (pin 17) | Vmode                 | Muted                                                      | 2.5  |         | 7.5             | V      |  |

|                                                                |                       | Standby                                                    | 0    |         | 1.5             | V      |  |

|                                                                | V                     | SE operation (1/2 $V_{CC} \le pin 6$ voltage)              | 6    |         | V <sub>CC</sub> | V      |  |

| BTL/SE (single ended) threshold voltage (pin 6)                | V <sub>SW</sub>       | BTL operation (pin 6 voltage < $1/2 V_{CC}$ )              | 0    |         | 5.4             | V      |  |

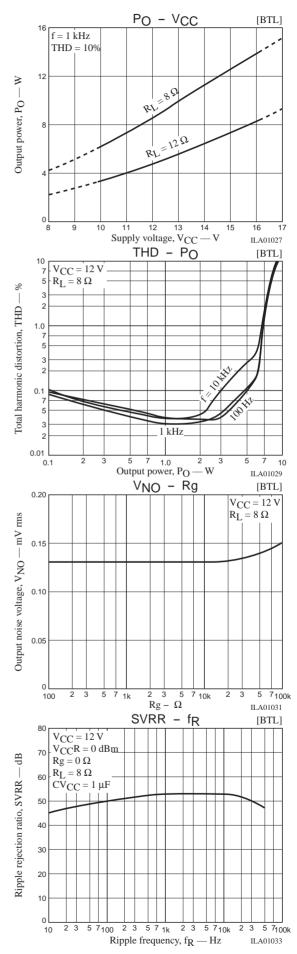

| [BTL Operation]                                                |                       |                                                            |      |         |                 |        |  |

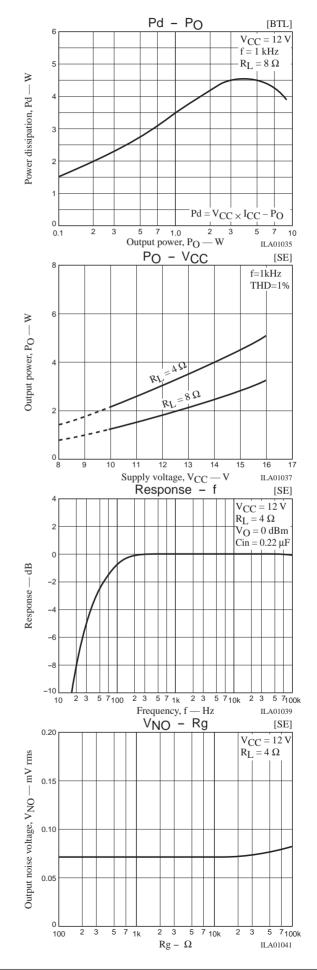

| Output power                                                   | P <sub>O</sub> 1      | THD = 10%                                                  | 6.5  | 8.5     |                 | W      |  |

| Total harmonic distortion                                      | THD1                  | P <sub>O</sub> = 1 W, Filter = FLAT                        |      | 0.04    | 0.15            | %      |  |

| Voltage gain                                                   | VG1                   | $V_0 = 0 \text{ dBm}$                                      | 24   | 26      | 28              | dB     |  |

| Output noise voltage (RMS)                                     | V <sub>NO</sub> 1     | Rg = 0, BPF = 20 Hz to 20 kHz                              |      | 0.15    | 0.25            | mV     |  |

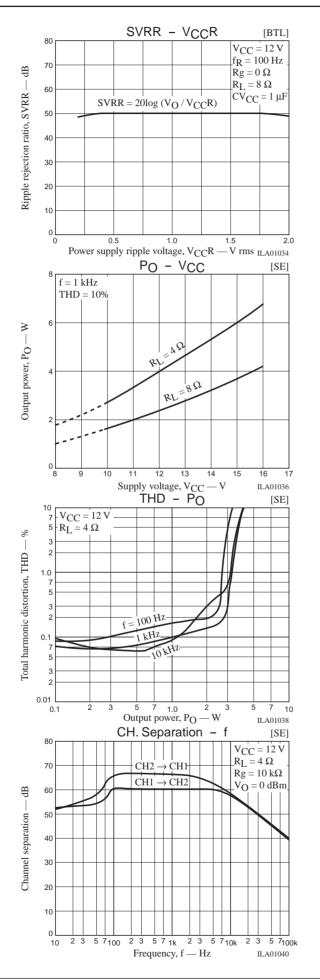

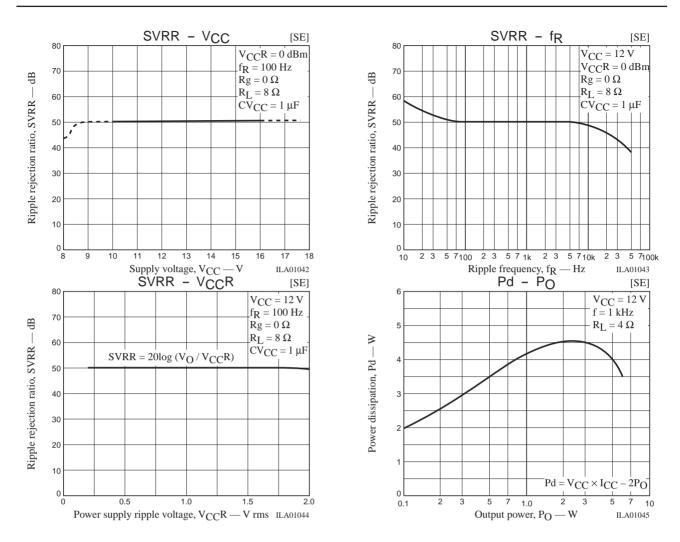

| Ripple rejection ratio                                         | SVRR1                 | Rg = 0, V <sub>CC</sub> R = 0 dBm, f <sub>R</sub> = 100 Hz | 45   | 50      |                 | dB     |  |

| Input resistance                                               | Ri 1                  | Channel 1, independent input                               | 42   | 60      | 78              | kΩ     |  |

| Output offset voltage                                          | V <sub>N</sub> offset | Rg = 0                                                     | -350 |         | +350            | mV     |  |

| Muting attenuation V <sub>ATT</sub> 1                          |                       | $V_0 = 1 V_{RMS}$ , BPF = 20 Hz to 20 kHz                  | 70   | 80      |                 | dB     |  |

| [SE (Single Ended) Operation]                                  |                       |                                                            |      |         |                 |        |  |

| Output power                                                   | P <sub>O</sub> 2      | THD = 10%                                                  | 3    | 4       |                 | W      |  |

| Total harmonic distortion                                      | THD2                  | P <sub>O</sub> = 1 W, Filter = FLAT                        |      | 0.15    | 0.25            | %      |  |

| Voltage gain                                                   | VG2                   | V <sub>O</sub> = 0 dBm                                     | 18   | 20      | 22              | dB     |  |

| Output noise voltage (RMS)                                     | V <sub>NO</sub> 2     | Rg = 0, BPF = 20 Hz to 20 kHz                              |      | 0.07    | 0.15            | mV     |  |

| Ripple rejection ratio                                         | SVRR2                 | Rg = 0, V <sub>CC</sub> R = 0 dBm, f <sub>R</sub> = 100 Hz | 40   | 50      |                 | dB     |  |

| Channel separation                                             | CH. Sep               | $Rg = 10 k\Omega$ , $V_0 = 0 dBm$                          | 40   | 55      |                 | dB     |  |

| Input resistance                                               | Ri 2                  |                                                            | 42   | 60      | 78              | kΩ     |  |

| Muting attenuation                                             | V <sub>ATT</sub> 2    | $V_0 = 1 V_{RMS}$ , BPF = 20 Hz to 20 kHz                  | 70   | 80      |                 | dB     |  |

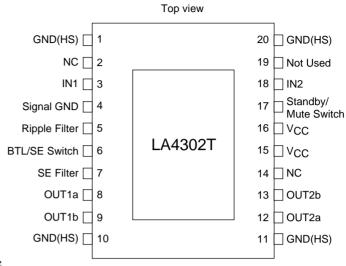

#### **Pin Assignments**

Note: The SANYO evaluation board described in the note to Maximum Ratings table on the previous page.

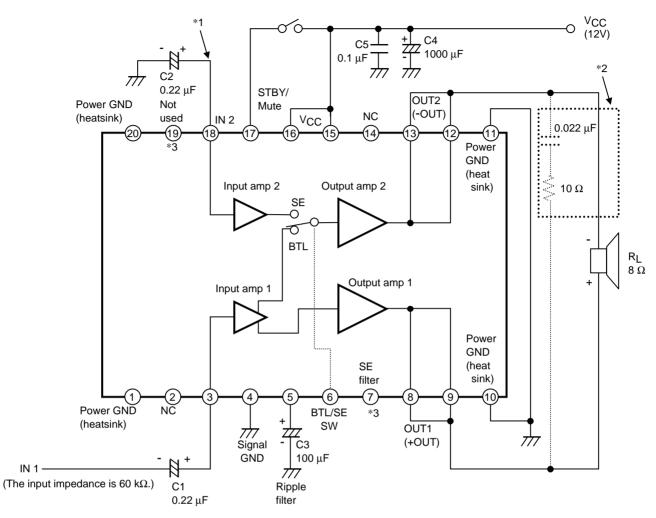

### **Block Diagram**

#### Notes

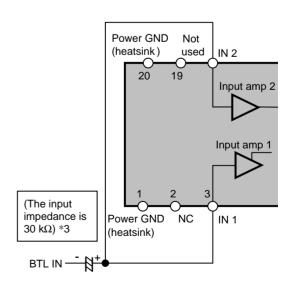

- 1. Figure 2 presents another input method as an alternative to that shown in the BTL usage example. Applications may use this alternative method, but note that the input impedance will be 30 k $\Omega$ . (The value of the capacitor must be doubled to achieve the same low band frequency characteristics as those of the standard usage example.)

- 2. Oscillations may appear in the output waveform under conditions that depend on the IC operating conditions and the connected load. If this problem occurs, the oscillation stability can be improved by inserting a 0.022  $\mu$ F capacitor (use a capacitor with excellent temperature characteristics) and a 10  $\Omega$  resistor in series in the positions shown in dotted lines in figure 1. Verify the quality of the output waveform in an actual end product.

- 3. Pins 7 and 19 must not be connected to any signal; they must be left open. (This is because they are connected inside the chip.) Pin 7 can be connected to ground through a 0.047  $\mu$ F capacitor as shown in figure 3, Standard SE Usage Example, on the next page.

# Figure 2 BTL Usage Example (Alternative Input Pin Connection Method)

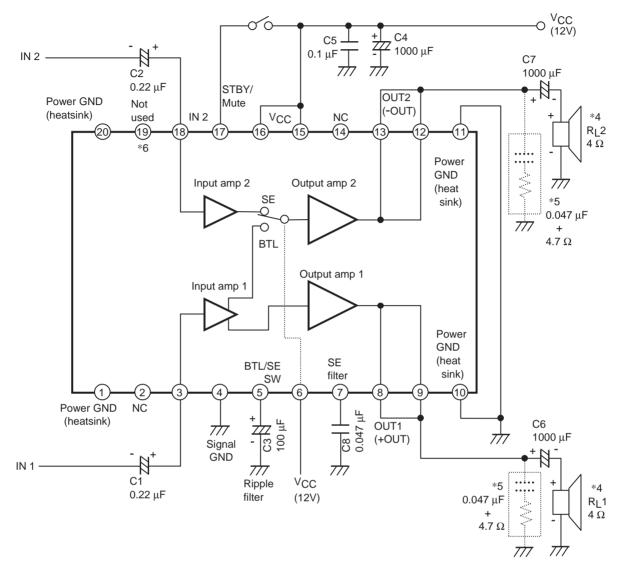

#### Notes

- 4. The speakers must both be connected with the plus (+) side closest to the IC.

- 5. Oscillations may appear in the output waveform under conditions that depend on the IC operating conditions and the connected load. If this problem occurs, the oscillation stability can be improved by inserting 0.047  $\mu$ F capacitors (use capacitors with a low variation in capacitance with temperature) and 4.7  $\Omega$  resistors in series in the two positions shown in dotted lines in figure 3. Verify the quality of the output waveform in an actual end product.

- 6. Pin 19 must not be connected to any signal; it must be left open. (This is because it is connected inside the chip.)

| Pin No.         | 1        | 2  | 3    | 4       | 5    | 6      | 7         | 8     | 9     | 10       |

|-----------------|----------|----|------|---------|------|--------|-----------|-------|-------|----------|

| Pin             | GND (HS) | NC | IN1  | Sig–GND | RF   | BTL/SE | SE-Filter | OUT1a | OUT1b | GND (HS) |

| Pin voltage (V) | 0        | _  | 3.54 | 0       | 5.93 | 0/12   | 8.85      | 6.03  | 6.03  | 0        |

|                 |          |    |      |         |      |        |           |       |       |          |

| Pin No.         | 11       | 12 | 13   | 14      | 15   | 16     | 17        | 18    | 19    | 20       |

Vcc1

12

NC

STBY/Mute

12

IN2

3 54

Not Use

3.65\*

Vcc2

12

GND (HS)

0

5.96 \*: When Tj is 25°C. (See the description of the pin 19 function on page 8 for details.)

OUT2a

OUT2b

5.96

#### **External Components**

Pin

Pin voltage (V)

GND (HS)

0

C1, C2: These are the input coupling capacitors; a value of 0.22 µF or lower is recommended. If the value used is too large, the charge time when power is first applied will become longer and impulse noise problems may be aggravated. Since the LA4302T input resistance is 60 k $\Omega$ , the low-frequency cutoff frequency, f<sub>L</sub>, at the IC input when C1 and C2 are 0.22 µF will be close to 12.1 Hz.

$$f_{L} = \frac{1}{2\pi \cdot C1 (C2) \cdot Ri} = \frac{1}{2\pi \times 0.22 \ \mu F \times 60 \ k\Omega} \approx 12.1 \ (Hz)$$

The LA4302T input pin voltages are fixed at about 3.5 V. If electrolytic capacitors are used, the DC potential of the output blocks of the circuit in the previous stage must be taken into consideration when determining the capacitor polarity.

- C3: This capacitor is used both as a ripple filter and to set the amplifier startup time (the time until an output is provided after power is first applied). We recommend a value of 100 µF. Note that if the value of this capacitor is too low, the filter's ability to remove low-frequency components will be reduced and at the same time the amplifier startup time will be reduced, potentially aggravating impulse noise in the output.

- C4, C5: These are the power supply filter capacitors. It is desirable that the lengths of the lines to the  $V_{CC}$  pin and the power system ground pin in the circuit board pattern be made as short as possible. We recommend a value of 470  $\mu$ F or higher for C4. If the value of this capacitor is too small, impulse noise in the output when V<sub>CC</sub> is turned off may be aggravated. Although C5 may be omitted, it is desirable that it be included if the pattern for C4 is extended.

- C6, C7 (SE operation):

These are the output coupling capacitors. Since these capacitors, in conjunction with the value of R<sub>L</sub>, influence the low band cutoff frequency  $f_L$ ',  $f_L$ ' must be taken into consideration when determining the value of these capacitors. We recommend a value of 1000  $\mu F$  or lower. The low band cutoff frequency  $f_L$ ' will be close to 40 Hz when C6 and C7 are 1000  $\mu$ F and R<sub>L</sub> is 4  $\Omega$ .

$$f_{L}' = \frac{1}{2\pi \cdot C6 (C7) \cdot R_{L}} = \frac{1}{2\pi \times 1000 \,\mu\text{F} \times 4 \,\Omega} \approx 40 \text{ (Hz)}$$

```

C8 (SE operation):

```

C8 is used as the IC internal power supply line filter for SE operation. This capacitor is used to stabilize operation when transients occur at power on. We recommend a value in the range 0.047  $\mu$ F up to 1  $\mu$ F. This capacitor is not shown in the standard BTL usage example circuit, and is not required. However, a capacitor in the recommended range for SE mode may be used in BTL mode.

#### Oscillation prevention RC circuits:

These circuits are used if oscillation occurs in the output waveform due to the speaker used. It is desirable to use capacitors with a low temperature coefficient. See the standard usage examples on pages 4 and 5.

#### **Pin Function Descriptions**

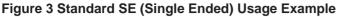

Standby / Muting Function

- Pin 17 functions as a three position switch that controls the standby and muting functions. The table below lists the IC operating state as controlled by the voltage applied to pin 17. (See figure 4 for the equivalent circuit for the pin 17 input circuit.)

- When power is first applied to the LA4302T, its startup time function (a function that automatically mutes the output for the time until an output is generated after power is first applied) operates. This means that no impulse noises will be generated even if pin 17 is directly connected to pin 15 or 16 ( $V_{CC}$ ).

| Voltage applied to pin 17 | Operating state                                      |  |  |  |  |

|---------------------------|------------------------------------------------------|--|--|--|--|

| 8.8 to V <sub>CC</sub>    | Amplifier operating state (muting is off)            |  |  |  |  |

| 2.5 to 7.5 V              | Amplifier operating state but with the outputs muted |  |  |  |  |

| 0 to 1.5 V                | Standby state                                        |  |  |  |  |

Method for Clearing the Muted State (This section is provided for reference purposes.)

As described above, if a voltage in the range 2.5 to 7.5 V is applied to pin 17, the amplifier will start, but will be in the muted state and no output will be generated. The following method can be used by a 5 V microcontroller or other circuit to control the voltage applied to pin 17 to control the amplifier output by applications that desire to clear the muted state from circuits that operate at a voltage in the 2.5 to 7.5 V range: Connect pin 19 (an unused pin) to pin 4 (the signal system ground).

This bypasses the mute circuit's operating current and clears the muted state. This does not release the starting time function.

Figure 4 Internal Equivalent Circuit for Pins 17 and 19

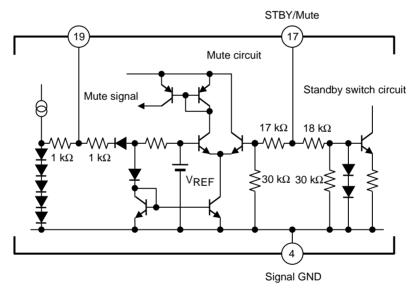

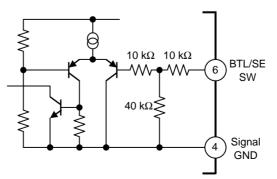

Function of the BTL/SE Switching Pin

• The LA4302T provides internal electronic switching between BTL and SE operation. The LA4302T operates in BTL mode when pin 6 is either open or at a voltage less than  $1/2V_{CC}$ , and it operates in SE mode when pin 6 is at a voltage greater than or equal to  $1/2V_{CC}$ . Figure 5 shows the equivalent circuit for the pin 6 internal circuit.

Figure 5 Pin 6 Internal Equivalent Circuit

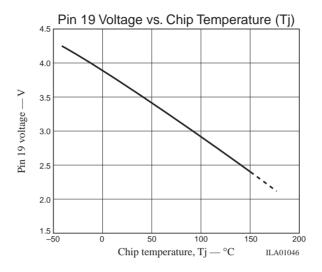

Pin 19 Function (Chip temperature Tj check)

• The LA4302T allows applications to verify the chip temperature (Tj) during IC operation by measuring the pin 19 DC voltage.

Temperature conversion: The figure below shows the temperature characteristics of the pin 19 internal circuit, which can be used for temperature measurement.

#### **Usage Notes**

Maximum Ratings

• If the IC is operated in the vicinity of the maximum rating limits, even slight changes in operating conditions can result in the maximum ratings being exceeded. Since this can lead to permanent damage to the IC itself, applications should provide adequate margins in the power supply voltages and other parameters and assure that the IC is operated in ranges that never exceed the maximum ratings.

Notes on IC Heat Dissipation

• The LA4302T features an ultraminiature surface mounting package (TSSOP20J) that includes heat dissipating pads.

Since this device is designed for heat dissipation by surface mounting on a 4-layer circuit board, adequate thermal dissipation must be provided for the actual usage conditions.

Through holes should be provided in the section of the circuit board where the IC package heat dissipating pads are mounted, and adequate thermal dissipation must be provided by connecting the pads to the copper foil layer that can be used. See pragraph Pin 19 Function (Chip temperature Tj check) above, for more information on determining whether or not the thermal dissipation provided is adequate for the usage conditions.

#### Protection Circuits

- While the LA4302T includes a full complement of built-in protection circuits, care is still required when using this device. In particular, do not short any IC pins to each other.

- The LA4302T includes a thermal protection circuit to prevent damage to or destruction of the IC should abnormal internal heat generation occur. This means that should the IC junction temperature (Tj) rise above about 160°C due to inadequate heat dissipation or other reason, the thermal protection circuit will operate to gradually reduce the output level, and finally stop IC operation should the temperature rise further. If the temperature is reduced by lowering the input level or other means, the thermal protection circuit will recover automatically.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 2003. Specifications and information herein are subject to change without notice.