# SANYO Semiconductors **DATA SHEET**

# LB11889M — For VCR Capstan Three-Phase Brushless Motor Driver

#### Overview

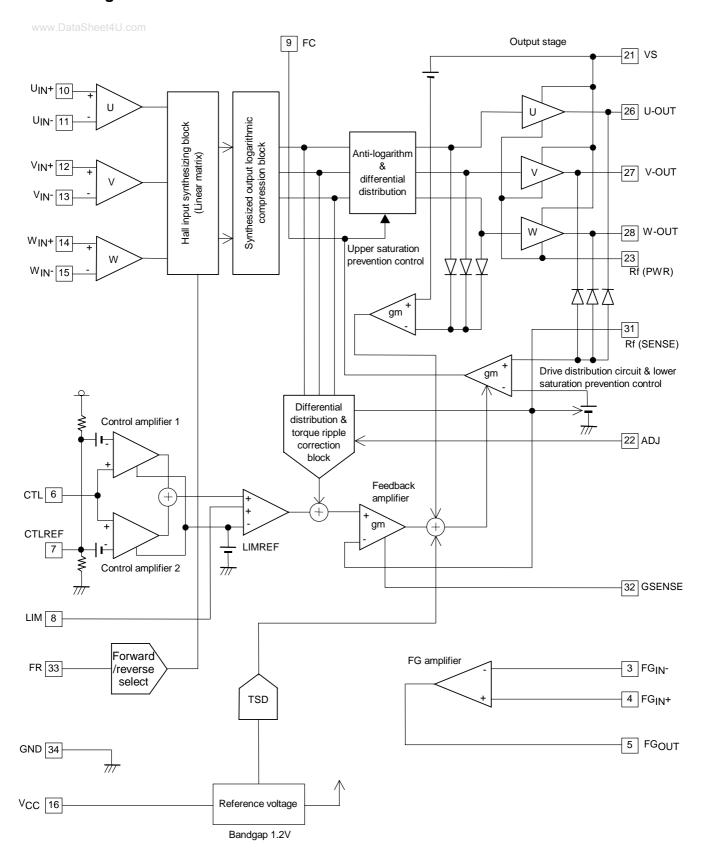

The LB11889M is three-phase brushless motor driver for VCR capstan motors.

#### **Features**

- 3-phase full-wave current linear drive.

- Torque ripple correction circuit (fixed correction ratio).

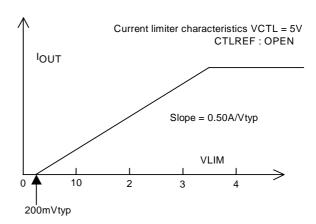

- Current limiter circuit with control characteristics gain switching.

- Output stage upper/lower oversaturation prevention circuit (No external capacitor required).

- FG amplifier built in.

- Thermal shutdown circuit built in.

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                           | Symbol              | Conditions     | Ratings     | Unit |

|-------------------------------------|---------------------|----------------|-------------|------|

| Maximum power supply voltage        | V <sub>CC</sub> max |                | 7           | V    |

|                                     | VS max              |                | 24          | V    |

| Maximum output current              | I <sub>O</sub> max  |                | 1.3         | Α    |

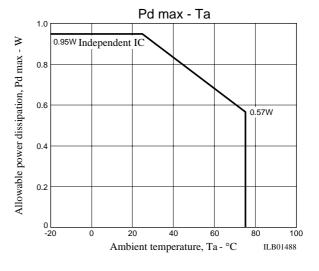

| Allowable power dissipation voltage | Pd max              | Independent IC | 950         | mW   |

| Operating temperature               | Topr                |                | -20 to +75  | °C   |

| Storage temperature                 | Tstg                |                | -55 to +150 | °C   |

#### Allowable Operating Range at Ta = 25°C

| Parameter            | Symbol  | Conditions                         | Ratings        | Unit  |

|----------------------|---------|------------------------------------|----------------|-------|

| Power supply voltage | VS      |                                    | 5 to 22        | V     |

|                      | Vcc     |                                    | 4.5 to 5.5     | V     |

| Hall input amplitude | VHALL   | Between hall inputs                | ±30 to ±80     | mVo-p |

| GSENSE input range   | VGSENSE | Relative to the control system GND | -0.20 to +0.20 | V     |

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

# LB11889M

## **Electrical Characteristics** at Ta = 25 °C, $V_{CC} = 5V$ , VS = 15V

| Doromotor                                       | Cumbal                      | Conditions Ratings min typ                                                                     |       |      | Unit  |      |

|-------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Parameter<br>www.DataSheet4U.com                | Symbol                      |                                                                                                |       | typ  | max   | Unit |

| V <sub>CC</sub> power supply current            | Icc                         | $R_L = \infty$ , VCTL = 0V, VLIM = 0V (at static mode)                                         |       | 12   | 18    | mA   |

| Output                                          |                             |                                                                                                |       |      |       |      |

| Output saturation voltage                       | V <sub>O</sub> sat1         | $I_O$ = 500mA, Rf = 0.5Ω, sink+source<br>VCTL = VLIM = 5V (With saturation prevention)         |       | 2.1  | 2.6   | V    |

|                                                 | V <sub>O</sub> sat2         | $I_O$ = 1.0A, Rf = 0.5Ω, sink+source<br>VCTL = VLIM = 5V (With saturation prevention)          |       | 2.6  | 3.5   | V    |

| Output leak current                             | l <sub>O</sub> leak         |                                                                                                |       |      | 1.0   | mA   |

| FR                                              |                             |                                                                                                |       |      |       |      |

| FR pin input threshold voltage                  | VFSR                        |                                                                                                | 2.25  | 2.50 | 2.75  | V    |

| FR pin input input bias current                 | lb (FSR)                    |                                                                                                | -5.0  |      |       | μΑ   |

| Control                                         |                             |                                                                                                |       |      |       |      |

| CTLREF pin voltage                              | VCREF                       |                                                                                                | 2.37  | 2.50 | 2.63  | V    |

| CTLREF pin input range                          | VCREF IN                    |                                                                                                | 1.70  |      | 3.50  | V    |

| CTL pin input bias current                      | lb (CTL)                    | VCTL = 5V, CTLREF : OPEN                                                                       |       |      | 8.0   | μΑ   |

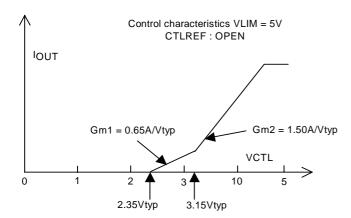

| CTL pin control start voltage                   | VCTL (ST)                   | Rf = 0.5Ω, VLIM = 5V, I <sub>O</sub> ≥10mA<br>With hall input logic fixed (U, V, W = H, H, L)  | 2.20  | 2.35 | 2.50  | V    |

| CTL pin control switching voltage               | VCTL (ST2)                  | Rf = 0.5Ω, VLIM = 5V                                                                           | 3.00  | 3.15 | 3.30  | V    |

| CTL pin control Gm1                             | Gm1 (CTL)                   | Rf = $0.5\Omega$ , $\Delta I_O$ = 200mA<br>With hall input logic fixed (U, V, W = H, H, L)     | 0.52  | 0.65 | 0.78  | A/V  |

| CTL pin control Gm2                             | Gm2 (CTL)                   | Rf = $0.5\Omega$ , $\triangle VCTL = 200mV$<br>With hall input logic fixed (U, V, W = H, H, L) | 1.20  | 1.50 | 1.80  | A/V  |

| Current limiter                                 |                             |                                                                                                |       |      |       | •    |

| LIM current limiter offset voltage              | Voff (LIM)                  | Rf = 0.5Ω, VCTL = 5V, $I_O \ge 10$ mA<br>With hall input logic fixed (U, V, W = H, H, L)       | 140   | 200  | 260   | mV   |

| LIM pin input bias current                      | lb (LIM)                    | VCTL = 5V, CTLREF : OPEN, VLIM = 0V                                                            | -2.5  |      |       | μА   |

| LIM pin current limiter level                   | llim                        | Rf = 0.5Ω, VCTL = 5V, VLIM = 2.06V<br>With hall input logic fixed (U, V, W = H, H, L)          | 830   | 900  | 970   | mA   |

| Hall amplifier                                  |                             | , , , , , , , , , , , , , , , , , , , ,                                                        | 1     |      | l .   | 1    |

| Hall amplifier input offset voltage             | Voff (HALL)                 |                                                                                                | -6    |      | +6    | mV   |

| Hall amplifier input bias current               | lb (HALL)                   |                                                                                                |       | 1.0  | 3.0   | μА   |

| Hall amplifier common-mode                      | VCM (HALL)                  |                                                                                                | 1.3   |      | 3.3   | V    |

| TRC                                             | 1 , ,                       |                                                                                                |       |      |       |      |

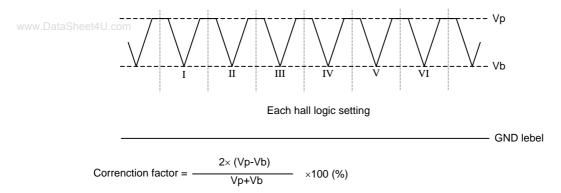

| Torque ripple correction factor                 | TRC                         | At bottom and peak of Rf waveform at $I_O = 200$ mA (RF = $0.5\Omega$ , ADJ-OPEN) Note 2       |       | 9    |       | %    |

| ADJ pin voltage                                 | VADJ                        | (                                                                                              | 2.37  | 2.50 | 2.63  | V    |

| FG amplifier                                    | ı                           |                                                                                                | ·I    |      |       |      |

| FG amplifier input offset voltage               | Voff (FG)                   |                                                                                                | -8    |      | +8    | mV   |

| FG amplifier input bias current                 | Ib (FG)                     |                                                                                                | -100  |      |       | nA   |

| FG amplifier output saturation                  | V <sub>O</sub> sat (FG)     | At internal pull-up resistor on the sink side                                                  |       |      | 0.5   |      |

| voltage                                         |                             |                                                                                                |       |      | 0.5   | V    |

| FG amplifier common-mode input voltage          | VCM (FG)                    |                                                                                                | 0.5   |      | 4.0   | V    |

| Saturation                                      |                             |                                                                                                |       |      |       |      |

| Saturation prevention circuit lower set voltage | V <sub>O</sub> sat<br>(DET) | Voltage between each OUT and Rf at $I_O$ = 10mA, Rf = 0.5 $\Omega$ , VCTL = VLIM = 5V          | 0.175 | 0.25 | 0.325 | V    |

| TSD                                             |                             |                                                                                                | 1     |      | 1     |      |

| TSD operating temperature                       | T-TSD                       | (Design target) Note.1                                                                         |       | 180  |       | °C   |

| TSD temperature hysteresis width                | ΔTSD                        | (Design target) Note.1                                                                         |       | 20   |       | °C   |

| tomporataro myotoroolo width                    | 1                           | (= -5.5.1 (2.901) 1.00011                                                                      |       | 20   |       |      |

Note 1. No measurements are made on the parameters with Note (Design target).

Note 2. The torque ripple correction factor is obtained based on the voltage waveform across Rf as shown below.

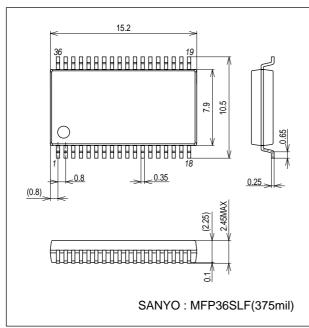

# **Package Dimensions**

unit : mm (typ) 3280A

#### **Truth Table and Control Function**

|          | Source → Sink     |   | Hall input |   |    |

|----------|-------------------|---|------------|---|----|

| www.Data |                   |   | ٧          | W | FR |

| 1        | $V \rightarrow W$ | н | Н          | L | Н  |

| ı        | $W \rightarrow V$ |   |            |   | L  |

| 2        | $U \rightarrow W$ | Н | L          | _ | Н  |

|          | $W \rightarrow U$ | П | L          | L | L  |

| 3        | $U \rightarrow V$ | Н | L          | Н | Н  |

| 3        | $V \rightarrow U$ | П | ١          | Г | L  |

| 4        | $W \rightarrow V$ | L | L          | Н | Н  |

| 4        | $V \rightarrow W$ | L | ١          | Г | L  |

| -        | $W \rightarrow U$ | L | Н          | Н | Н  |

| 5        | $U \rightarrow W$ |   |            |   | L  |

|          | $V \rightarrow U$ |   |            |   | Н  |

| 6        | $U \rightarrow V$ | L | Н          | L | L  |

Note) "H" for FR represents a voltage of 2.75V or greater; "L" represents a voltage of 2.25V or lower (at  $V_{CC} = 5V$ ). Note) Input "H" for all input represents that (+) is higher than each phase input (-) by 0.01V or greater; input "L"

represents that (+) is lower than each phase input (-) by 0.01V or greatre.

Note) Since this drive scheme is the 180° energizing scheme, phases other than Sink, Source phases are not turned OFF.

#### **Control Function & Current Limiter Function**

# LB11889M

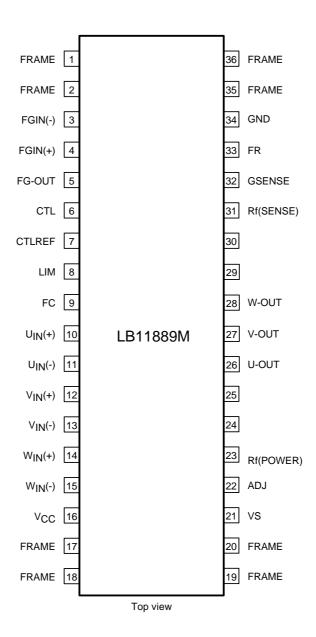

# **Pin Functions**

| Pin name                                                                                                             | Pin no.                    | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| www.fGint(-)Shee                                                                                                     | t4U.c3m                    | Input pin for the FG amplifier to be used with inverted input.  A feedback resistor is connected between this pin and FG OUT.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| FGIN (+)                                                                                                             | 4                          | Noninverting input pin for the FG amplifier to be used as differential input. No bias is applied internally.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| FG-OUT                                                                                                               | 5                          | FG amplifier output pin with resistive load internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| CTL                                                                                                                  | 6                          | Speed control pin. Control is performed by means of constant current drive which is applied by current feedback from Rf. $Gm = 0.65AV \& 1.50A/V TYP$ at Rf = $0.5\Omega$                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CTLREF                                                                                                               | 7                          | Control reference voltage pin. The voltage is set at approximately $V_{CC}/2$ internally, but can be varied by applying a voltage through a low impedance. (The input impedance is approximately $2.5k\Omega$ .)                                                                                                                                                                                                                                                                                                                     |  |  |

| LIM                                                                                                                  | 8                          | Current limiter function control pin. This pin voltage is capable of varying the output current linealy.<br>Slope = $0.5A/V$ TYP at Rf = $0.5\Omega$                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| FC                                                                                                                   | 9                          | Speed control loop's frequency characteristics correction pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| U <sub>IN</sub> +, U <sub>IN</sub> -<br>V <sub>IN</sub> +, V <sub>IN</sub> -<br>W <sub>IN</sub> +, W <sub>IN</sub> - | 10, 11<br>12, 13<br>14, 15 | U phase hall element input pin. "H" for logic represents IN+>IN  V phase hall element input pin. "H" for logic represents IN+>IN  W phase hall element input pin. "H" for logic represents IN+>IN                                                                                                                                                                                                                                                                                                                                    |  |  |

| VCC                                                                                                                  | 16                         | Power supply pin used to supply to each circuit other than the output blocks inside the IC.  This voltage must be stabilized to reject noise and ripple.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| VS                                                                                                                   | 21                         | Power supply pin for output blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ADJ                                                                                                                  | 22                         | Pin to be used to adjust the torque ripple correction factor externally.  When adjusting the correction factor, apply voltage externally to the ADJ pin through a low impedance.  Increasing the applied voltage decreases the correction factor; lowering the applied voltage increases the correction factor.  The rate of change, when left open, ranges approximately from 0 to 2 times.  (Approximately V <sub>CC</sub> /2 is set internally and the input impedance is approximately 5kΩ.)                                     |  |  |

| Rf (PWR)<br>Rf (SNS)                                                                                                 | 23<br>31                   | Output current detection pins. Current feedback is provided to the control blocks by connecting Rf between the pins and GND. The operation of the lower over-saturation prevention circuit and torque ripple correction circuit depends on the pin voltage.  In particular, since the oversaturation prevention level is set by the pin voltage, decreasing the Rf value extremely may cause the lower over-saturation prevention to work less efficiently in the large current region. The PWR pin and SENSE pin must be connected. |  |  |

| U <sub>OUT</sub><br>VOUT<br>WOUT                                                                                     | 26<br>27<br>28             | U phase output pin V phase output pin W phase output pin W phase output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| GSENSE                                                                                                               | 32                         | GND sensing pin.  By connecting this pin to GND in the vicinity of the Rf resistor side of the Rf included motor GND wiring, the influence that the GND common impedance exerts on Rf can be excluded. (Must not be left open.)                                                                                                                                                                                                                                                                                                      |  |  |

| FR                                                                                                                   | 33                         | Forward/reverse select pin.  This pin voltage determines forward/reverse. (Vth = 2.5V typ. At V <sub>CC</sub> = 5V)                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| GND                                                                                                                  | 34                         | GND for other than output transistors.  The lowest potential of output transistors is on the Rf pin.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

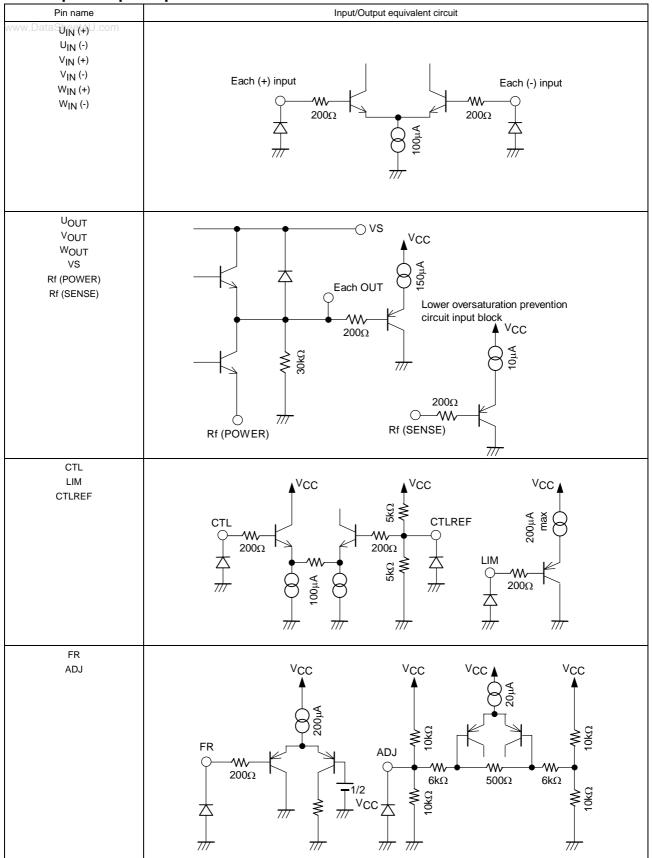

# **Each Input/Output Equivalent Circuit**

Continued on next page.

## LB11889M

| Pin name                          | Input/output equivalent circuit                                        |

|-----------------------------------|------------------------------------------------------------------------|

| ww.Data FGIN (+) .com<br>FGIN (+) | FG <sub>IN</sub> (-)  FG <sub>IN</sub> (+)  300Ω  FG <sub>IN</sub> (+) |

| FGOUT<br>FC                       | Vcc Vcc                                                                |

|                                   | FGOUT SEE SEE SEE SEE SEE SEE SEE SEE SEE SE                           |

#### **Block Diagram**

#### **Pin Assignment**

www.DataSheet4U.com

Note: Although the FRAME pins and the GND pin are not connected internally in the IC, the FRAME pins must be connected to the GND pin externally for ground potential stabilization.

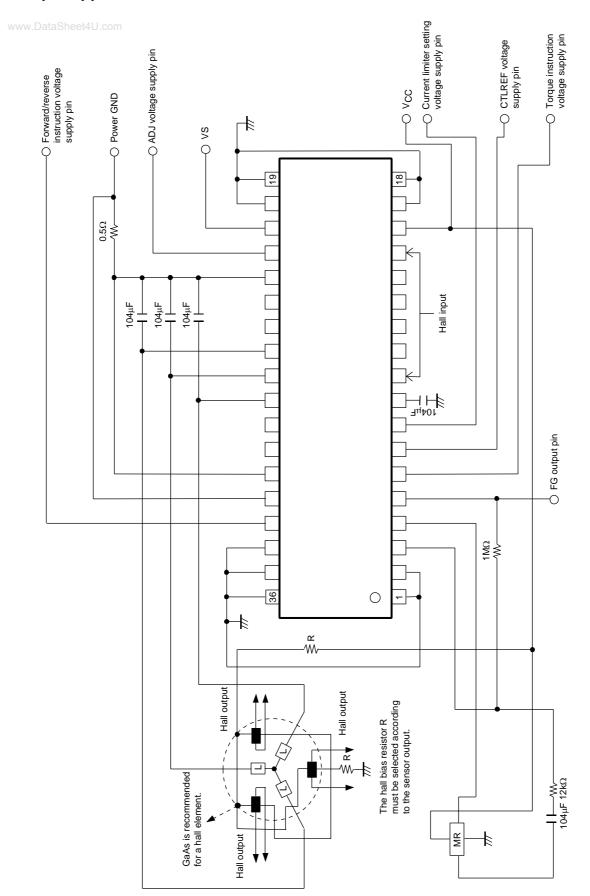

# **Sample Application Circuit**

Note) The component values shown in this application circuit example one merely provided as examples, and circuit operating characteristics are not guaranteed.

www.DataSheet4U.com

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 2006. Specifications and information herein are subject to change without notice.