# LC65E29

# On-Chip UVEPROM IC 4-Bit Single-Chip Microcontroller

# Preliminary

## **Overview**

The LC65E29 is a one-time programmable (on-chip UVEPROM) version of Sanyo's LC6529N/F/L 4-bit single-chip CMOS microcontroller. It provides identical functionality to, and pin compatibility with, the mask ROM versions of the LC6529N/F/L, and provides a 1-KB internal EPROM. The LC65E29 is provided in a DIC24S or MFC30S windowed ceramic package, and is appropriate for use during program development and hardware evaluation since it allows programs to be erased and reloaded repeatedly.

Additionally, the LC65E29 can function as a one-time programmable UVEPROM version of the Sanyo LC6527N/F/L and LC6528N/F/L by using the 29T27 adapter socket.

## Features

• Mask option settings can be switched by setting EPROM data.

All options, except for the port output circuit type can be set with EPROM data.

- 1K bytes of UVEPROM (ultraviolet erasable EPROM) on chip

- Can be programmed and read using a general-purpose EPROM programmer.

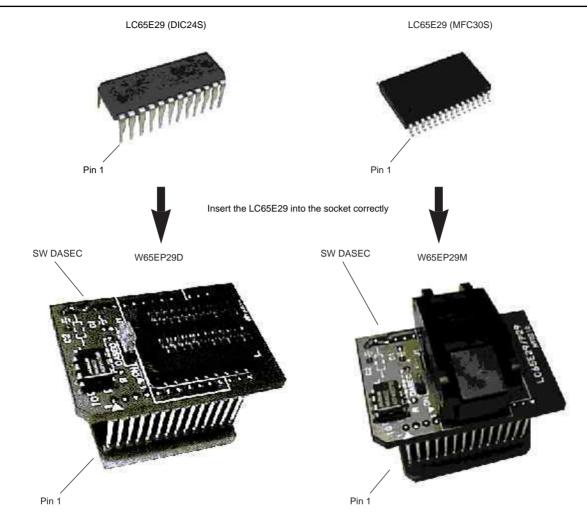

The use of a conversion socket (24 pins  $\rightarrow$  28 pins: W65EP29D, 30 pins  $\rightarrow$  28 pins: W65EP29M) allows the LC65E29 to be programmed and read using a general-purpose EPROM programmer.

- EPROM data security function

- · Pin compatible with the mask ROM version

- Instruction cycle time: 0.92 µs to 20 µs

- Packages: DIC24S and MFC30S

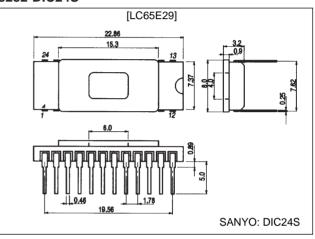

# **Package Dimensions**

unit: mm

3232-DIC24S

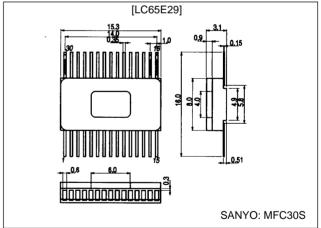

# unit: mm

#### 3212A-MFC30S

Note: 1. These dimensional drawings are for reference purposes, and are provided without dimensional tolerances. Contact your Sanyo representative for the official dimensional drawings.

2. The point where the leads are trimmed may be changed.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

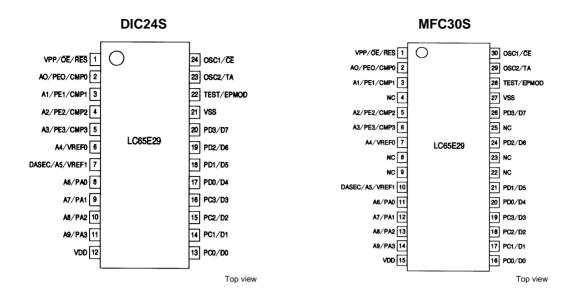

#### **Pin Assignments**

#### **Product Series Structure**

| Type number                  | Number of pins | ROM capacity | RAM capacity | Package                |

|------------------------------|----------------|--------------|--------------|------------------------|

| LC6527N/F/L, LC6528N/F/L     | 18             | 1K, 0.5K     | 64W, 32W     | DIP18, MFP18           |

| LC6529N/F/L                  | 24/30          | 1K           | 64W          | DIP24S, SSOP24, MFP30S |

| LC65E29                      | 24/30          | 1K           | 64W          | DIC24S, MFC30S         |

| LC65P29                      | 24/30          | 1K           | 64W          | DIP24S, MFP30S         |

| LC6543N/F/L, LC6546N/F/L     | 30             | 2K, 1K       | 128W, 64W    | DIP30S, MFP30S         |

| LC65E43                      | 30             | 2K           | 128W, 64W    | DIC30S, MFC30S         |

| LC65P43                      | 30             | 2K           | 128W, 64W    | DIP30S, MFP30S         |

| LC651104N/F/L, LC651102N/F/L | 30             | 4K, 2K       | 256W         | DIP30S, MFP30S         |

| LC651204N/F/L, LC651202N/F/L | 30             | 4K, 2K       | 256W         | DIP30S, MFP30S         |

| LC65E1104                    | 30             | 4K           | 256W         | DIC30S, MFC30S         |

| LC65P1104                    | 30             | 4K           | 256W         | DIP30S, MFP30S         |

#### **Usage Notes**

The LC65E29 is designed for program development and evaluation for systems that use the LC6529N/F/L. The following points require attention when using this product.

• Mounting notes

When using this device, the window must be covered with an opaque seal.

• Differences between the LC65E29 and the LC6529N/F/L

|                | Parameter                                | LC65P29                                                                  | LC6529N                                                            | LC6529F                                  | LC6529L                                       |  |  |  |

|----------------|------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|--|--|--|

|                | Ports C and D output option during reset | High or low can be specified (option code)                               | High or low can be specified (mask option)                         |                                          |                                               |  |  |  |

|                | Port output type during reset            | Open-drain output only<br>(ports A, C, and D)                            | Open-drain or pull-up register can be specified (mask option)      |                                          |                                               |  |  |  |

|                | Oscillator circuit option                | CF/RC or EXT can be specified (option code)                              | CF/RC or EXT can be specified (mask option)                        | CF or EXT can be specified (mask option) | CF/RC or EXT can be specified (mask option)   |  |  |  |

| Option         | Divider circuit option                   | 1/1, 1/3, or 1/4 can be specified (option code)                          | 1/1,1/3 or 1/4 can be specified (mask option)                      | Only 1/1 is possible<br>(mask option)    | 1/1,1/3 or 1/4 can be specified (mask option) |  |  |  |

|                | Comparator input and port E input option | Comparator or port E can be specified (option code)                      | Comparator or port E can be specified (mask option)                |                                          |                                               |  |  |  |

|                | Comparator function option               | Feedback resistor present<br>or absent can be specified<br>(option code) | Feedback resistor present or absent can be specified (mask option) |                                          |                                               |  |  |  |

|                | Minimum cycle time                       | 0.92 $\mu s$ (V_{DD} $\geq$ 3.0 V)                                       | 2.77 $\mu s~(V_{DD} \geq 3.0~V)$                                   | 0.92 µs (V <sub>DD</sub> ≥ 3.0 V)        | 3.84 µs (V <sub>DD</sub> ≥ 2.2 V)             |  |  |  |

| stic           | Operating temperature                    | +10 to +40°C                                                             |                                                                    | –40 to +85°C                             | 1                                             |  |  |  |

| Characteristic | Supply voltage                           | 3.0 to 6.0 V                                                             | 3.0 to 6.0 V                                                       | 3.0 to 6.0 V                             | 2.2 to 6.0 V                                  |  |  |  |

| Char           | Current drain                            | 5.0 mA typ.                                                              | 2.0 mA typ.                                                        | 2.5 mA typ.                              | 2.0 mA typ.                                   |  |  |  |

|                | Reset port input low-level current       | –50 μA typ.                                                              |                                                                    |                                          |                                               |  |  |  |

| Other items    | Package                                  | DIC24S windowed<br>package<br>MFC30S windowed<br>package                 | DIP24S, SSOP24, MFP30S                                             |                                          |                                               |  |  |  |

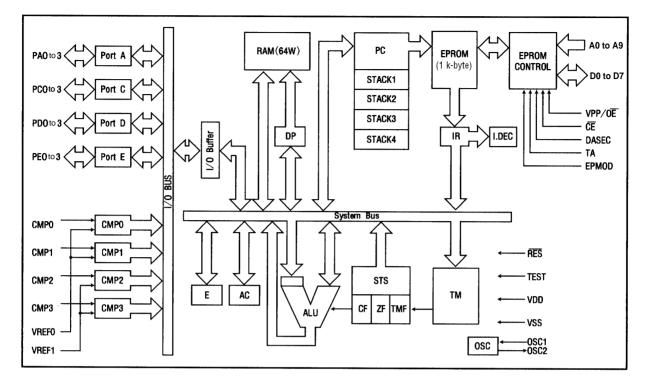

#### System Block Diagram

#### RAM: Data memory

- ALU: Arithmetic and logic unit

- DP: Data pointer

- E: E register

- AC: Accumulator

- OSC: Oscillator circuit

- TM: Timer

- STS: Status register

#### EPROM: Program memory

- PC: Program counter

- I.R: Instruction register

- I.DEC: Instruction decoder

- CF: Carry flag

- ZF: Zero flag

- TMF: Timer overflow flag

#### **Pin Descriptions**

| Pin name                                                 | Number<br>of pins | I/O    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Option                                                                                                                                                                                    | State during reset                                                                                          | Function in<br>PROM mode                                                                           |

|----------------------------------------------------------|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| V <sub>DD</sub><br>V <sub>SS</sub>                       | 1<br>1            | _      | Power supply. Must be connected to +5 V<br>during normal operation.<br>Power supply. Must be connected to 0 V<br>during normal operation.                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                           |                                                                                                             |                                                                                                    |

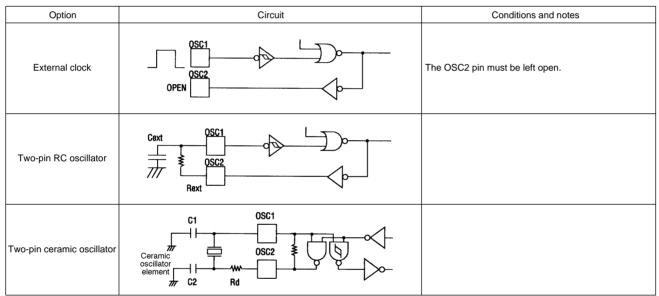

| OSC1/CE<br>OSC2/TA                                       | 1                 | 1<br>O | System clock oscillator connections. Leave<br>OSC2 open and input the external clock to<br>OSC1 if an external clock is used.                                                                                                                                                                                                                                                                                                                                        | <ol> <li>Two-pin RC oscillator<br/>(Single-pin external<br/>clock input)</li> <li>Two-pin ceramic<br/>oscillator</li> <li>Divisor option: 1/1, 1/3,<br/>or 1/4</li> </ol>                 |                                                                                                             | EPROM contorol<br>signal inputs<br>CE<br>TA                                                        |

| PA0/A6<br>PA1/A7<br>PA2/A8<br>PA3/A9                     | 4                 | I/O    | <ul> <li>I/O ports A0 to A3<br/>Input in 4-bit units (IP instruction)<br/>Output in 4-bit units (OP instruction)<br/>Data testing in 1-bit units (BP and BNP<br/>instructions)<br/>Data set and clear operations in 1-bit units<br/>(SPB and RPB instructions)</li> <li>PA3 is used for standby mode control.</li> <li>Applications must assure that chattering<br/>(key bounce) noise is not input to PA3<br/>during a HALT instruction execution cycle.</li> </ul> | Open-drain output                                                                                                                                                                         | High-level output (The<br>n-channel output<br>transistor turned off.)                                       | • Address inputs<br>A6 to A9                                                                       |

| PC0/D0<br>PC1/D1<br>PC2/D2<br>PC3/D3                     | 4                 | I/O    | <ul> <li>I/O ports C0 to C3<br/>The pin functions are identical to those of<br/>pins A0 to A3.<br/>However, there is no standby mode<br/>control function.</li> <li>The output during a reset can be specified<br/>to be either high or low as an option.</li> </ul>                                                                                                                                                                                                 | <ol> <li>Open-drain output</li> <li>High-level output<br/>during reset</li> <li>Low-level output<br/>during reset</li> <li>Selection of items 2 or<br/>3 is in 4-bit units.</li> </ol>    | <ul> <li>High-level output</li> <li>Low-level output<br/>(Depending on an<br/>option selection.)</li> </ul> | • Data I/O<br>D0 to D3                                                                             |

| PD0/D4<br>PD1/D5<br>PD2/D6<br>PD3/D7                     | 4                 | I/O    | <ul> <li>I/O ports D0 to D3</li> <li>The pin functions are identical to those of<br/>pins PC0 to PC3.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | The same as for pins<br>PC0 to PC3                                                                                                                                                        | The same as pins PC0 to PC3                                                                                 | • Data I/O<br>D4 to D7                                                                             |

| PE0/CMP0/A0<br>PE1/CMP1/A1<br>PE2/CMP2/A2                | 4                 | I      | <ul> <li>When comparator input is selected:<br/>CMP0 and CMP1 use V<sub>REF</sub>0 as the<br/>reference voltage.<br/>CMP2 and CMP3 use V<sub>REF</sub>1 as the<br/>reference voltage.</li> <li>Comparator inputs CMP0 to CMP3<br/>Data input in 4-bit units (IP instruction)</li> <li>Data testing in 1-bit units (BP and BNP<br/>instructions)</li> </ul>                                                                                                           | <ol> <li>Comparator input</li> <li>Port E input</li> <li>No feedback resistor</li> <li>Feedback resistor<br/>present</li> <li>Selection of items 1 or<br/>2 is in 4-bit units.</li> </ol> |                                                                                                             | Address inputs<br>A0 to A3                                                                         |

| PE3/CMP3/A3                                              | 4                 | I      | <ul> <li>When input is selected for port E</li> <li>Input ports E0 to E3<br/>Input in 4-bit units (IP instruction)</li> <li>Data testing in 1-bit units (BP and BNP instructions)</li> </ul>                                                                                                                                                                                                                                                                         | Items 3 and 4 are only<br>specified when item 1<br>is selected.                                                                                                                           |                                                                                                             |                                                                                                    |

| V <sub>REF</sub> 0/A4<br>V <sub>REF</sub> 1/A5/<br>DASEC | 2                 | I      | <ul> <li>Comparator reference voltage inputs<br/>V<sub>REF</sub>0 and V<sub>REF</sub>1<br/>V<sub>REF</sub>0 is the reference voltage input for<br/>CMP0 and CMP1.<br/>V<sub>REF</sub>1 is the reference voltage input for<br/>CMP2 and CMP3.</li> <li>When PE0/CMP0 to PE3/CMP3 are<br/>selected to function as port E inputs,<br/>these pins are connected to V<sub>SS</sub>.</li> </ul>                                                                            |                                                                                                                                                                                           |                                                                                                             | <ul> <li>Address inputs<br/>A4 and A5</li> <li>EPROM control<br/>signal input<br/>DASEC</li> </ul> |

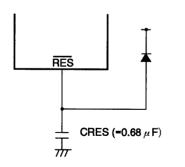

| RES/VPP/OE                                               | 1                 | I      | <ul> <li>System reset input</li> <li>Connect an external capacitor to effect the power-on reset.</li> <li>Input a low level for at least 4 clock cycles to effect a reset restart.</li> </ul>                                                                                                                                                                                                                                                                        |                                                                                                                                                                                           |                                                                                                             | • EPROM control<br>signal input<br>VPP/ OE                                                         |

| EST/EPMOD                                                | 1                 | I      | <ul> <li>IC test pin</li> <li>This pin must be connected to V<sub>SS</sub> during<br/>normal operation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                             | • EPROM control<br>signal input<br>EPMOD                                                           |

#### **User Options**

• Ports C and D output level during reset option

One of the following two options for the output level during a reset can be selected for each of the ports C and D in 4-bit units.

| Option                     | Conditions and notes         |

|----------------------------|------------------------------|

| High-level output at reset | Ports C and D in 4-bit units |

| Low-level output at reset  | Ports C and D in 4-bit units |

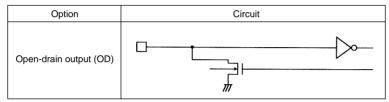

• Port output circuit type option

The I/O ports A, C, and D are always set up as open-drain outputs.

#### • Oscillator circuit options

#### • Divisor option

| Option                    | Circuit                           | Conditions and notes                                                                        |

|---------------------------|-----------------------------------|---------------------------------------------------------------------------------------------|

| No divisor (1/1)          | Timing<br>generator               | Can be used with any of the 3 oscillator options. (N, F, and L versions)                    |

| Divide-by-3 circuit (1/3) | Timing<br>generator               | Can only be used with the external clock and ceramic oscillator options. (N and L versions) |

| Divide-by-4 circuit (1/4) | □ fosc fosc 4<br>Timing generator | Can only be used with the external clock and ceramic oscillator options. (N and L versions) |

Comparator input/port E input option

Whether the 4 port pins PE0/CMP0, PE1/CMP1, PE2/CMP2, and PE3/CMP3 function as comparator inputs or as port E inputs can be selected.

| Option            | Conditions and notes          |  |  |  |

|-------------------|-------------------------------|--|--|--|

| Comparator inputs | All 4 bits specified together |  |  |  |

| Port E inputs     | All 4 bits specified together |  |  |  |

#### • Comparator function option

One of two options relating to the comparator function can be selected.

| Option                    | Circuit              | Conditions and notes                                                                   |

|---------------------------|----------------------|----------------------------------------------------------------------------------------|

| No feedback resistor      | CMP0 to 3<br>VREF0.1 | The comparator can be used without hysteresis.                                         |

| Feedback resistor present |                      | When used with an added external resistor, the comparator can be used with hysteresis. |

#### **Usage Procedures**

• Option specification procedures

User options can be selected interactively by running the LC6529 option entry software (SU60K). This creates an option file (file.opt).

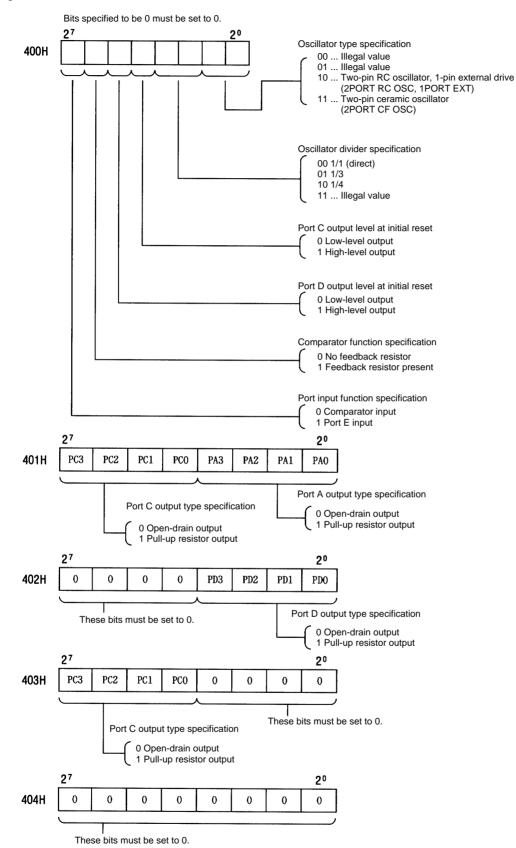

Assembling the user program with the macro assembler (M60K) creates an object file. An evaluation file (file.eva) can be created by linking the object file and the option file with the linker (L60K). Then, a HEX format object file, which includes both the user program and the mask options, can be created by converting the evaluation file with the file conversion software (E2H60K). This creates the option codes in the option specification area (locations 400 to 404H).

It is also possible to store data directly to the option specification area. Refer to the "Option data area and definition" on page 9 to do this.

Refer to the "LC65/66K Software Manual" for details.

• EPROM programming procedure

A general-purpose EPROM programmer can be used to write the created data to the LC65E29 by using a special-purpose write conversion board (either the W65EP29D or the W65EP29M).

— The EPROM programmers listed below can be used.

| Manufacturer       | Models that can be used            |

|--------------------|------------------------------------|

| ADVANTEST          | R4945, R4944A, R4943 or equivalent |

| ANDO               | —                                  |

| AVAL               | —                                  |

| MINATO Electronics | —                                  |

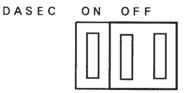

— The "27512 (VPP: 12.5 V) Intel fast write" method must be used for writing. Specify locations 0 to 404 as the address settings, and make sure that the DASEC jumper is in the off position.

• Using the data security function

The data security function is a function that prevents data written previously to the microcontroller EPROM from being read out. Use the following procedure to apply the data security to the LC65E29.

- 1. Set the DASEC jumper on the write conversion board to the on position.

- 2. Write the data once again.

At this point, the EPROM writer will indicate an error since this function has operated, but actually, no error has occurred in either the programmer or the IC.

Notes: • The data security function will not be applied if the data value FF is written to all address in step 2.

- The data security function will not be applied if the sequence  $BLANK \rightarrow PROGRAM \rightarrow VERIFY$  is performed at step 2.

- Always return the jumper to the off position after performing this procedure.

## LC65E29

• For normal writing

• For writing with the security function applied

· Option data area and definition

Note: Although all ports are set up to be open-drain outputs regardless of the port option data in the LC65E29, be sure to specify the port option data when you use the LC6529N/F/L (mask ROM version).

| Parameter                   | Cumhal              | Applicable                      | Conditions                                             |                              | Ratings                                         |                       |      |  |

|-----------------------------|---------------------|---------------------------------|--------------------------------------------------------|------------------------------|-------------------------------------------------|-----------------------|------|--|

| Parameter                   | Symbol              | pins/notes                      | Conditions                                             | min                          | typ                                             | max                   | Unit |  |

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                 |                                                        | -0.3                         |                                                 | +7.0                  | V    |  |

| Output voltage              | Vo                  | OSC2                            |                                                        | Values up to<br>are allowed. | Values up to the generated voltage are allowed. |                       |      |  |

|                             | V <sub>I</sub> 1    | OSC1*1                          |                                                        | -0.3                         |                                                 | V <sub>DD</sub> + 0.3 | V    |  |

| Input voltage               | V <sub>I</sub> 2    | TEST, RES                       |                                                        | -0.3                         |                                                 | V <sub>DD</sub> + 0.3 | V    |  |

| input voltage               | V <sub>I</sub> 3    | Ports with<br>PE specifications |                                                        | -0.3                         |                                                 | V <sub>DD</sub> + 0.3 | V    |  |

| I/O voltage                 | V <sub>IO</sub>     | PA, PC, PD                      |                                                        | -0.3                         |                                                 | +15                   | mA   |  |

| Peak output current         | I <sub>OP</sub>     | PA, PC, PD                      |                                                        | -2                           |                                                 | +20                   | mA   |  |

|                             | I <sub>OA</sub>     | PA, PC, PD                      | The 100 ms average per pin                             | -2                           |                                                 | +20                   | mA   |  |

| Average output current      | $\Sigma I_{OA}$ 1   | PA                              | The total current for pins PA0 to PA3*2                | -6                           |                                                 | +40                   | mA   |  |

|                             | Σ I <sub>OA</sub> 2 | PC, PD                          | The total current for pins PC0 to PC3 and PD0 to PD3*2 | -14                          |                                                 | +90                   | mA   |  |

| Allowable newer discinction | Pdmax1              |                                 | Ta = +10 to +40°C(DIC24S)                              |                              |                                                 | 360                   | mW   |  |

| Allowable power dissipation | Pdmax2              |                                 | Ta = +10 to +40°C(MFC30S)                              |                              |                                                 | 150                   | mW   |  |

| Operating temperature       | Topr                |                                 |                                                        | +10                          |                                                 | +40                   | °C   |  |

| Storage temperature         | Tstg                |                                 |                                                        | -55                          |                                                 | +125                  | °C   |  |

# Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}$ = 0 V

Notes: 1. Values up to the generated oscillator amplitude are allowed when driven internally using the guaranteed circuit constant values with the oscillator circuit shown in figure 2.

2. The average over a 100 ms period.

# Allowable Operating Conditions at Ta = +10 to +40 $^{\circ}C,$ V\_{SS} = 0 V, V\_{DD} = 3.0 to 6.0 V

|                                            |                               |                        | Applicable      | 0                                                            |                     |                     | Ratings     |                      | Unit     |  |

|--------------------------------------------|-------------------------------|------------------------|-----------------|--------------------------------------------------------------|---------------------|---------------------|-------------|----------------------|----------|--|

| Parameter                                  |                               | Symbol                 | pins/notes      |                                                              | V <sub>DD</sub> [V] | min                 | min typ max |                      | Unit     |  |

| Ope                                        | rating supply voltage         | V <sub>DD</sub>        | V <sub>DD</sub> |                                                              |                     | 3.0                 |             | 6.0                  | V        |  |

| Star                                       | ndby supply voltage           | V <sub>ST</sub>        | V <sub>DD</sub> | RAM and register retention *                                 |                     | 1.8                 |             | 6.0                  | V        |  |

|                                            |                               | V <sub>IH</sub> 1      | PA, PC, PD      | Output n-channel transistor off                              |                     | 0.7 V <sub>DD</sub> |             | 13.5                 | V        |  |

| High                                       | n-level input voltage         | V <sub>IH</sub> 2      | PE              | When the port E input option is selected                     |                     | 0.7 V <sub>DD</sub> |             | V <sub>DD</sub>      | V        |  |

| l ngi                                      | never input voltage           | V <sub>IH</sub> 3      | RES             |                                                              | 1.8 to6.0           | 0.8 V <sub>DD</sub> |             | V <sub>DD</sub>      | V        |  |

|                                            |                               | V <sub>IH</sub> 4      | OSC1            | When the RC oscillator and external clock option is selected |                     | 0.8 V <sub>DD</sub> |             | V <sub>DD</sub>      | V        |  |

|                                            |                               | V <sub>IL</sub> 1      | PA, PC, PD      | Output n-channel transistor off                              |                     | V <sub>SS</sub>     |             | 0.3 V <sub>DD</sub>  | V        |  |

|                                            |                               | V <sub>IL</sub> 2      | PE              | When the port E input option is selected                     |                     | V <sub>SS</sub>     |             | 0.3 V <sub>DD</sub>  | V        |  |

| Low                                        | -level input voltage          | V <sub>IL</sub> 3      | OSC1            | When the RC oscillator and external clock option is selected |                     | V <sub>SS</sub>     |             | 0.25 V <sub>DD</sub> | V        |  |

|                                            |                               | V <sub>IL</sub> 4      | TEST            |                                                              |                     | V <sub>SS</sub>     |             | 0.3 V <sub>DD</sub>  | V        |  |

|                                            |                               | V <sub>IL</sub> 5      | RES             |                                                              |                     | V <sub>SS</sub>     |             | 0.25 V <sub>DD</sub> | V        |  |

|                                            | rating frequency (cycle time) | fop(t <sub>CYC</sub> ) |                 |                                                              |                     | 200 (20)            |             | 4330 (0.92)          | kHz (µs) |  |

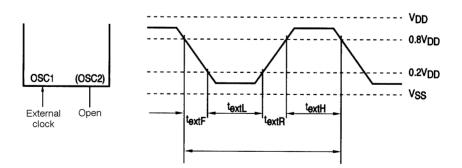

| ns                                         | Frequency                     | fext(text)             | OSC1            | See Figure 1                                                 |                     | 200 (20)            |             | 4330 (0.92)          | kHz (µs) |  |

| External clock conditions                  | Pulse width                   | textH, textL           | OSC1            | See Figure 1                                                 |                     | 69                  |             |                      | ns       |  |

| Exte                                       | Rise and fall times           | textR, textF           | OSC1            | See Figure 1                                                 |                     |                     |             | 50                   | ns       |  |

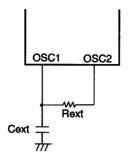

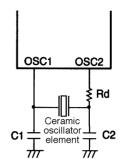

|                                            |                               | Cext                   | OSC1, OSC2      | See Figure 2                                                 | 4 to 6              |                     | 220 ±5%     |                      | pF       |  |

| stants                                     | Two-pin RC oscillator         | Cext                   | OSC1, OSC2      | See Figure 2                                                 |                     |                     | 220 ±5%     |                      | рF       |  |

| eed o                                      |                               | Rext                   | OSC1, OSC2      | See Figure 2                                                 | 4 to 6              |                     | 6.8 ±1%     |                      | kΩ       |  |

| Guaranteed oscillator<br>circuit constants |                               | Rext                   | OSC1, OSC2      | See Figure 2                                                 |                     |                     | 15.0 ±1%    |                      | kΩ       |  |

| Ö                                          | Ceramic oscillator            |                        |                 | See Figure 3                                                 |                     |                     | See Table 1 |                      |          |  |

Note \*: Applications must maintain the operating supply voltage (V<sub>DD</sub>) until the IC has entered the standby state when a HALT instruction is executed. Also, applications must assure that chattering (key bounce) noise is not input to the PA3 pin during a HALT instruction execution cycle.

# Electrical Characteristics at Ta = +10 to +40 $^{\circ}C,$ V\_{SS} = 0 V, V\_{DD} = 3.0 to 6.0 V

|                          |                    | Paramotor                        | Symbol              | Applicable                                                   | Conditions                                                                                                         |                     |                     | Ratings             |      |     |  |

|--------------------------|--------------------|----------------------------------|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|-----|--|

|                          | Parameter          |                                  | Symbol              | pins/notes                                                   | Conditions                                                                                                         | V <sub>DD</sub> [V] | min                 | typ                 | max  | Uni |  |

|                          |                    |                                  | l <sub>IH</sub> 1   | PA, PC, PD                                                   | Output n-channel transistor off (Includes the n-channel transistor off leakage current) $V_{\rm IN} = 13.5~V$      |                     |                     |                     | 5.0  | μA  |  |

| High-level input current |                    | I <sub>IH</sub> 2                | PE                  | When the port E input option is selected $V_{IN} = V_{DD}$   |                                                                                                                    |                     |                     | 5.0                 | μA   |     |  |

|                          |                    |                                  | I <sub>IH</sub> 3   | OSC1                                                         | When the RC oscillator and<br>external clock option is selected<br>$V_{IN} = V_{DD}$                               |                     |                     |                     | 1.0  | μA  |  |

|                          |                    |                                  | I <sub>IL</sub> 1   | PA, PC, PD                                                   | Output n-channel transistor off<br>(Includes the n-channel<br>transistor off leakage current)<br>$V_{IN} = V_{SS}$ |                     | -1.0                |                     |      | μA  |  |

| Lov                      | v-le               | evel input current               | I <sub>IL</sub> 2   | PE                                                           | When the port E input option is selected $V_{IN} = V_{SS}$                                                         |                     | -1.0                |                     |      | μA  |  |

|                          |                    |                                  | I <sub>IL</sub> 3   | RES                                                          | V <sub>IN</sub> = V <sub>SS</sub>                                                                                  |                     | -80                 | -50                 |      | μA  |  |

|                          |                    |                                  | I <sub>IL</sub> 4   | OSC1                                                         | When the RC oscillator and external clock option is selected $V_{IN} = V_{SS}$                                     |                     | -1.0                |                     |      | μA  |  |

|                          |                    |                                  | V <sub>OL</sub> 1   | PA, PC, PD                                                   | I <sub>OL</sub> = 10 mA                                                                                            |                     |                     |                     | 1.5  | V   |  |

| Lov                      | w-l∈               | evel output voltage              | V <sub>OL</sub> 2   | PA, PC, PD                                                   | I <sub>OL</sub> = 1.8 mA<br>(When all port I/O levels are<br>1 mA or lower)                                        |                     |                     |                     | 0.4  | V   |  |

|                          |                    |                                  | V <sub>HIS</sub> 1  | RES                                                          |                                                                                                                    |                     |                     | 0.1 V <sub>DD</sub> |      | V   |  |

| Hysteresis voltage       |                    | V <sub>IHS</sub> 2               | OSC1*1              | When the RC oscillator and external clock option is selected |                                                                                                                    |                     | 0.1 V <sub>DD</sub> |                     | V    |     |  |

|                          |                    | ) oo cillotor                    | ID <sub>DOP</sub> 1 | V <sub>DD</sub>                                              | Figure 2. 850 kHz (typ)                                                                                            |                     |                     | 5                   | 8    | mA  |  |

|                          | RC                 | Coscillator                      | ID <sub>DOP</sub> 2 | V <sub>DD</sub>                                              | Figure 2. 400 kHz (typ)                                                                                            |                     |                     | 4.5                 | 7    | mA  |  |

|                          |                    | Ceramic oscillator*2             | ID <sub>DOP</sub> 3 | V <sub>DD</sub>                                              | Figure 3. 4 MHz, 1/1, 1/3, and 1/4 divisor ratios                                                                  |                     |                     | 5                   | 8    | mA  |  |

|                          | ~                  |                                  | ID <sub>DOP</sub> 4 | V <sub>DD</sub>                                              | Figure 3. 2 MHz, 1/1, 1/3, and 1/4 divisor ratios                                                                  |                     |                     | 4.5                 | 7    | mA  |  |

| current arain            | C                  |                                  | ID <sub>DOP</sub> 5 | V <sub>DD</sub>                                              | Figure 3. 800 kHz, 1/1 divisor ratio                                                                               |                     |                     | 5                   | 8    | mA  |  |

|                          |                    |                                  | ID <sub>DOP</sub> 6 | V <sub>DD</sub>                                              | Figure 3. 400 kHz, 1/1 divisor ratio                                                                               |                     |                     | 4.5                 | 7    | mA  |  |

|                          | Ex                 | ternal clock*2                   | ID <sub>DOP</sub> 7 | V <sub>DD</sub>                                              | 200 to 4330 kHz, 1/1, 1/3, and 1/4 divisor ratios                                                                  |                     |                     | 5                   | 8    | mA  |  |

|                          | C+/                | andby mode                       | IDDst1              | V <sub>DD</sub>                                              | Output n-channel transistor off Port = $V_{DD}$                                                                    | 6                   |                     | 0.05                | 10   | μA  |  |

|                          | 010                |                                  | IDDst2              | V <sub>DD</sub>                                              | Output n-channel transistor off<br>Port = $V_{DD}$                                                                 | 3                   |                     | 0.025               | 5    | μA  |  |

| 1                        | RC oscillator      | Oppillator fraguency             | fMOSC               | OSC1, OSC2                                                   | Figure 2. Cext = 220 pF ±5%<br>Rext = 15.0 kΩ ±1%                                                                  |                     | 275                 | 400                 | 711  | kHz |  |

|                          | RC os              | Oscillator frequency             | INIOSC              | OSC1, OSC2                                                   | Figure 2. Cext = 220 pF $\pm$ 5%<br>Rext = 6.8 k $\Omega \pm$ 1%                                                   | 4 to 6              | 579                 | 850                 | 1179 | kHz |  |

| ciel                     |                    |                                  |                     | OSC1, OSC2                                                   | Figure 3. fo = 4 MHz                                                                                               |                     | 3840                | 4000                | 4160 | kHz |  |

| 9                        | tor                | Oscillator frequency             | fFOSC*3             | OSC1, OSC2                                                   | Figure 3. fo = 2 MHz                                                                                               |                     | 1920                | 2000                | 2080 | kHz |  |

| 5                        | cilla              | Comator nequency                 |                     | OSC1, OSC2                                                   | Figure 3. fo = 800 kHz                                                                                             |                     | 768                 | 800                 | 832  | kHz |  |

|                          | Ceramic oscillator |                                  |                     | OSC1, OSC2                                                   | Figure 3. fo = 400 kHz                                                                                             |                     | 384                 | 400                 | 416  | kHz |  |

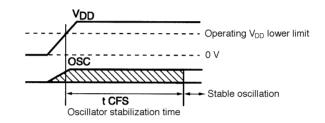

|                          | ami                |                                  |                     |                                                              | Figure 4. fo = 4 MHz                                                                                               |                     |                     |                     | 10   | ms  |  |

| -                        | Cer                | Oscillator stabilization time    | tCFS                |                                                              | Figure 4. fo = 2 MHz<br>fo = 800 kHz<br>fo = 400 kHz                                                               |                     |                     |                     | 10   | ms  |  |

| Pul                      | l-up               | o resistor reset port            | Ru                  |                                                              | V <sub>IN</sub> = V <sub>SS</sub>                                                                                  | 5                   | 70                  | 100                 | 150  | kΩ  |  |

|                          |                    | al reset characteristics:<br>ime | tRST                |                                                              |                                                                                                                    |                     |                     | See Figure 6.       |      | ms  |  |

| Pin capacitance          |                    | pacitance                        | Ср                  |                                                              | f = 1 MHz<br>$V_{IN} = V_{SS}$ for all input pins<br>other than the measured pin                                   |                     |                     | 10                  |      | pF  |  |

Image: Intermediate of the intermediate of

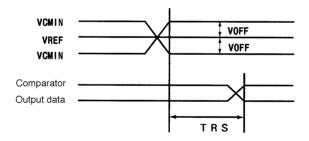

# Comparator Characteristics (When the comparator input option is selected)

at Ta = +10 to +40°C,  $V_{SS} = 0$  V,  $V_{DD} = 3.0$  to 6.0 V

| Parameter                       | Symbol            | Applicable            | Conditions                                        |                     | Ratings               |     |                       | - Unit |

|---------------------------------|-------------------|-----------------------|---------------------------------------------------|---------------------|-----------------------|-----|-----------------------|--------|

| Palameter                       | Symbol            | pins/notes            | Conditions                                        | V <sub>DD</sub> [V] | min                   | typ | max                   |        |

| Reference input voltage range   | VRF <sub>IN</sub> | V <sub>REF</sub> 0, 1 |                                                   |                     | V <sub>SS</sub> + 0.3 |     | V <sub>DD</sub> – 1.7 | V      |

| Common-mode input voltage range | VCMIN             | CMP0 to 3             |                                                   |                     | V <sub>SS</sub>       |     | V <sub>DD</sub> – 1.7 | V      |

| Offset voltage                  | V <sub>OFF</sub>  |                       | VCMIN = $V_{SS}$ to $V_{DD}$ – 1.7 V              |                     |                       | ±50 | ±300                  | mV     |

| Response speed                  | TRS1              |                       | See Figure 5.                                     | 4 to 6              |                       | 1.0 | 5.0                   | μs     |

|                                 | TRS2              |                       | See Figure 5.                                     |                     |                       | 1.0 | 200                   | μs     |

|                                 | I <sub>IH</sub> 1 | V <sub>REF</sub> 0, 1 |                                                   |                     |                       |     | 1.0                   | μA     |

| High-level input current        | I <sub>IH</sub> 2 | CMP0 to 3             | When the feedback resistor option is not selected |                     |                       |     | 5.0                   | μA     |

|                                 | I <sub>IL</sub> 1 | V <sub>REF</sub> 0, 1 |                                                   |                     | -1.0                  |     |                       | μA     |

| Low-level input current         | I <sub>IL</sub> 2 | CMP0 to 3             | When the feedback resistor option is not selected |                     | -1.0                  |     |                       | μA     |

| Feedback resistance             | RCMFB             | CMP0 to 3             | When the feedback resistor option is selected     |                     |                       | 460 |                       | kΩ     |

#### Table 1 Guaranteed Ceramic Oscillator Circuit Constants

| Standard type           |         |                       |                       |             |             |        | Chip type             |                       |            |            |

|-------------------------|---------|-----------------------|-----------------------|-------------|-------------|--------|-----------------------|-----------------------|------------|------------|

| Oscillator type         |         | Manufacturer          | Oscillator<br>element | C1          | C2          | Rd     | Manufacturer          | Oscillator<br>element | C1         | C2         |

| External capacitor type | 4 MHz   | Murata Mfg. Co., Ltd. | CSA4.00MG             | 33 pF ±10%  | 33 pF ±10%  | —      | Murata Mfg. Co., Ltd. | CSAC4.00MGC           | 33 pF ±10% | 33 pF ±10% |

|                         |         | Kyocera Corporation   | KBR-4.0MSA            | 33 pF ±10%  | 33 pF ±10%  | —      | —                     | —                     | —          | _          |

|                         | 2 MHz   | Murata Mfg. Co., Ltd. | CSA2.00MG             | 33 pF ±10%  | 33 pF ±10%  | —      | Murata Mfg. Co., Ltd. | CSAC2.00MGC           | 33 pF ±10% | 33 pF ±10% |

|                         |         | Kyocera Corporation   | KBR-2.0MS             | 47 pF ±10%  | 47 pF ±10%  | —      | —                     | —                     | —          | _          |

|                         | 800 kHz | Murata Mfg. Co., Ltd. | CSB800J               | 100 pF ±10% | 100 pF ±10% | 3.3 KΩ | —                     | —                     | —          | _          |

|                         |         | Kyocera Corporation   | KBR-800F/Y            | 150 pF ±10% | 150 pF ±10% | —      | —                     | —                     | —          | _          |

|                         | 400 kHz | Murata Mfg. Co., Ltd. | CSB400P               | 220 pF ±10% | 220 pF ±10% | 3.3 KΩ | —                     | —                     | —          | _          |

|                         |         | Kyocera Corporation   | KBR-400BK/Y           | 330 pF ±10% | 330 pF ±10% | —      | —                     | —                     | —          | _          |

| Internal capacitor type | 4 MHz   | Murata Mfg. Co., Ltd. | CST4.00MGW            | _           | _           | _      | —                     | —                     | _          | _          |

|                         |         | Kyocera Corporation   | KBR-4.0MKS            | _           | _           | _      | Kyocera Corporation   | KBR-4.0MWS            | _          | _          |

|                         | 2 MHz   | Murata Mfg. Co., Ltd. | CST2.00MG             | _           | _           | _      | _                     | _                     | _          | _          |

|                         |         | _                     | _                     | _           | _           | _      | Kyocera Corporation   | KBR-2.0MWS            | _          | —          |

Figure 1 External Clock Input Waveform

Figure 3 Ceramic Oscillator Circuit

Figure 4 Oscillator Stabilization Time

Figure 5 Comparator Response Speed TRS Timing

Note: The reset period due to a CRES with a value of 0.68 µF will be 10 to 100 ms when the power supply rise time is zero.

If the power supply rise time is relatively long, increase the value of CRES so that the reset time is at least 10 ms, which is the oscillator stabilization time.

Figure 6 Reset Circuit

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any and all SANYO products described or contained herein fall under strategic products (including services) controlled under the Foreign Exchange and Foreign Trade Control Law of Japan, such products must not be exported without obtaining export license from the Ministry of International Trade and Industry in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 1998. Specifications and information herein are subject to change without notice.