CMOS IC

LC67F5104A

# 32-BIT SINGLE CHIP MICROCONTROLLER

# **UnderDevelopment**

# **Overview**

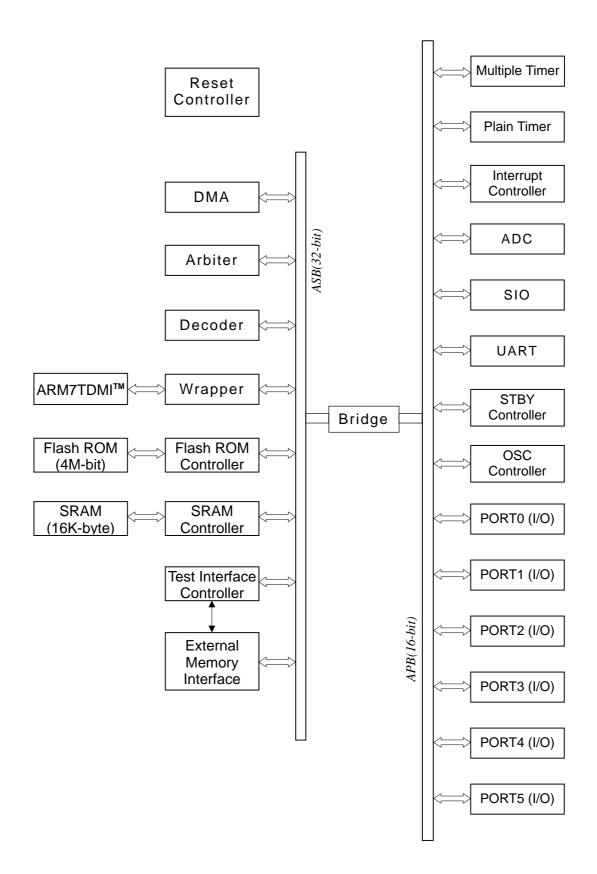

The LC67F5104A is a CMOS 32-bit RISC microcontroller which is ideally suited for CD-R/RW or DVD applications. This microcontroller contains the ARM7TDMI<sup>™</sup> core produced by ARM, and various peripherals such as 4M-bit flash ROM, 128K-bit SRAM, DMA controller, interrupt controller, I/O ports, serial interface, 8-bit AD converter and timers all in a 100-pin package single chip.

# Features

| (1) Operating Power Supply Voltage | 2.25 to 2.75V (I/O, ADC 3.0 to 3.6V) |

|------------------------------------|--------------------------------------|

| (2) Operating Temperature          | 0 to 75°C                            |

| (3) Package Type                   | TQFP-100                             |

| (4) CPU Core                       | ARM7TDMI <sup>™</sup>                |

| (5) Flash ROM                      | 4M bits on chip                      |

| (6) SRAM                           | 128K bits on chip                    |

|                                    |                                      |

### (7) Maximum Operating Frequency

Oscillator CF Oscillator/external clock input **RC** Oscillator

# 1MHz (Typical)

18MHz

- The system clock frequency can be selected to be 1/1, 1/2, 1/4 or 1/8 of the oscillation frequency.

- The on-chip RC is automatically selected at reset or release of the standby mode.

- The clock selection is programmable.

- (8) Write Protected Area in Flash

(Located at the end of the 4M-bit memory area) 16KB

This area cannot be written to when the microcontroller is in normal operating mode. It can only be written to in the "Flash ROM Setting" mode.

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition tanges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

This product incorporates technology licensed from Silicon Storage Technology Inc. ARM is the registered trademark of ARM Limited. ARM7TDM is the trademark of ARM Limited.

is the applying trademark of SANYO Electric Co., Ltd.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

(9) Ports

| Input/output ports | 56 ports |

|--------------------|----------|

| Input ports        | 8 ports  |

(10) Serial Interface (One channel)

Synchronous full duplex SIO with three lines

- Selectable 8 or 16-bit data length

- Selectable transfer bit order: LSB first or MSB first

- Transfer clock

Internal or external clock selectable

Internal clock can be selected ranging in value from  $8 \times$  system clock to  $1024 \times$  system clock by the on-chip 8-bit baud rate generator.

- Clock polarity selectable

Clock pin level selectable when not transferring

Error detection

- Overflow error Receive register over-write error

### (11) UART (One channel)

Full duplex buffer enables continuous data transfer

- Selectable transfer rate

Transfer rate can be selected ranging in value from  $16 \times$  system clock to  $4096 \times$  system clock by the on-chip 8-bit baud rate generator.

The transfer speed ranges from 4288bps to 1070000bps at 18MHz oscillation (while the UART standard is 110bps to 1152000bps).

Table 1 shows transfer rate examples.

| Operating Frequency |           | 18MHz         |               | 17.2872MHz |               |               |  |

|---------------------|-----------|---------------|---------------|------------|---------------|---------------|--|

| Bit Rate (Bits/s)   | Set value | Transfer Rate | Difference(%) | Set value  | Transfer Rate | Difference(%) |  |

| 4800                | 22        | 4808          | +0.16         | 31         | 4802          | +0.04         |  |

| 9600                | 139       | 9615          | +0.16         | 143        | 9562          | -0.40         |  |

| 19200               | 197       | 19068         | -0.69         | 200        | 19294         | +0.49         |  |

| 38400               | 227       | 38793         | +1.02         | 228        | 38588         | +0.49         |  |

| 57600               | 236       | 56250         | -2.34         | 237        | 56866         | -1.27         |  |

| 115200              | 246       | 112500        | -2.34         | 247        | 120050        | +4.21         |  |

| 230400              | 251       | 225000        | -2.34         | 251        | 216090        | -6.21         |  |

Table 1Transfer Rate Examples

The formulae used to calculate are as follows:

| Set Value     | $= 256 - \{\text{Operating Frequency} / (16 \times \text{Bit Rate})\}$ |

|---------------|------------------------------------------------------------------------|

| Transfer Rate | = Operating Frequency / $\{16 \times (256 - \text{Set Value})\}$       |

| Difference    | = (Transfer Rate – Bit Rate) / Bit Rate × 100                          |

- 1 or 2 stop bit(s) selectable

- 7 or 8-bit data length selectable

- Parity selection: even, odd or none

- Error detection: parity, framing and receive buffer overwrite error

# (12) Plain Timer

- (i) Watchdog Timer

- 8-bit baud rate generator and 16-bit free run counter

- Reset or interrupt generation selectable on counter overflow

- The counter clock can be selected to be 1/1, 1/2, 1/4 or 1/8 of the system clock

- The maximum time until overflow is 14.4 seconds at 18MHz oscillation

- (ii) 16-Bit Free Run Counter

- The interrupt request is generated at counter overflow

- The counter clock can be selected to be 1/1, 1/2, 1/4 or 1/8 of the system clock

- Overflow interval can be selected to be 2.5, 5, 10 or 20ms at 18MHz oscillation

# (13) ADC

- 8-channel 8-bit AD converter

- Successive approximation method

- Vref input (2.9 < Vref < AVcc)

- Interrupt at AD conversion completion

- Scan mode

- Conversion time : around 5.33µs at 18MHz oscillation

# (14) DMA Controller

- 2 channels of independent operation

- Memory to memory transfer on the ASB bus

- Transfer between memory mapped device and memory on the ASB bus

- Transfer data size can be selected from byte, half word (2 bytes) or word (4 bytes)

# (15) Interrupt Controller

- External interrupts 7 sources

- Internal interrupts 23 sources Total: 30 sources

- 2 vector addresses: FIQ and IRQ vectors FIQ has higher priority than IRQ

- Triggers for external interrupts (HPIRQ, EXT0IRQ ~ EXT5IRQ) can be selected to be rising edge/ high level or falling edge/ low level.

- Standby mode can be released by the level detection of any of external interrupts.

- Individual interrupt enabling/disabling is provided for every interrupts except HPIRQ

- Interrupt enabling/disabling of all interrupts together (except HPIRQ) is provided.

- FIQ or IRQ vector is selectable for each interrupt except HPIRQ.

- HPIRQ interrupt is fixed to FIQ vector. The vectors can be selected when all interrupts (except HPIRQ) are disabled.

- Status register indicating interrupt sources is provided.

# (16) Power Save Mode

(i) Three Power Save Modes

Sleep mode, software standby mode and hardware standby mode

(ii) Module Standby Function

Clock for serial interface, UART, multiple timer, plain timer and AD converter can be stopped by program control to reduce the current consumption.

# (17) Multiple Timer

5-channel 16-bit timer

- Maximum of 12 types of pulse output and 10 types of pulse input are provided.

- Counter input can be selected from the following:

- Internal clock  $\Phi, \Phi/2, \Phi/4, \Phi/8$

- External clock TCK1, TCK2, TCK3, TCK4

- Operation mode for each channel can be selected from the following:

- Waveform output by PCS (Phase Control Signal)

- Low, high or toggle output is selectable NOTE: Low or high only for channel 2

- PLS (Pulse Length Scaler) function Rising edge, falling edge or both edges detection is selectable

- Counter clear function

- Counter clear by PCS or PLS

- Synchronous operation

- Simultaneous data write to multiple timer counters

- Simultaneous clear by PCS or PLS

- Synchronous input and output of registers by synchronous counter operation

- PWM mode

- Duty programmable PWM output

- Maximum of 5 phases PWM output is possible by synchronous operation

- The following operation modes are selectable on channels 3 and 4

- Reset Synchronous PWM mode Three-phase output of Positive or Negative PWM is possible by combining channels 3 and 4.

• Complementary PWM mode

Three-phase output of Positive or Negative PWM with no overlapping is possible by combining channels 3 and 4.

- Buffer operation

- PLS can be double buffered.

- PCS can be updated automatically.

- Interrupts

Each channel has 2 PCS or PLS interrupts and an overflow interrupt source. All interrupts can be requested independently.

### (18) Memory Area

1GB of internal memory and 1GB of external memory area

The external memory area consists of 4 areas of 256MB each. (Area 0 to3)

NOTE: Only the first 16MB of each external memory area can be used.

The internal and external memory address map is shown in Table 2.

| Memory Area | Address                 | Description                            | Note |

|-------------|-------------------------|----------------------------------------|------|

|             | 7FFF FFFFh ~ 7000 0000h | External memory (Area 3)               |      |

| External    | 6FFF FFFFh ~ 6000 0000h | External memory (Area 2)               |      |

| Memory      | 5FFF FFFFh ~ 5000 0000h | External memory (Area 1)               |      |

| ,           | 4FFF FFFFh ~ 4000 0000h | External memory (Area 0)               |      |

|             | 3FFF FFFFh ~ 2200 0000h | Access forbidden (Reserved)            |      |

|             | 21FF FFFFh ~ 2000 0000h | Peripheral input/output registers etc. |      |

| Internal    | 1FFF FFFFh ~ 1400 0000h | Access forbidden (Reserved)            |      |

| Memory      | 1777 1400 000011        | Some registers assigned                |      |

| -           | 13FF FFFFh ~ 1000 0000h | On-chip RAM                            |      |

|             | 0FFF FFFFh ~ 0000 0000h | On-chip ROM                            |      |

Table 2 Memory Address Map

#### • Configuration of Internal Memory Area

The memory address space 3FFF FFFF to 0000 0000 is allocated as 1GB internal memory area. This area consists of the on-chip ROM, on-chip RAM, the peripheral input/output registers, etc.

Table 3 shows the address map of the internal memory area.

| Memory Area                      | Address                 | Description                            | Note  |

|----------------------------------|-------------------------|----------------------------------------|-------|

| Reserved Area                    | 3FFF FFFFh ~ 2001 0000h | Access forbidden (Reserved)            |       |

| Peripheral I/O<br>Registers, etc | 2000 FFFFh ~ 2000 0000h | Peripheral input/output registers etc. |       |

| Reserved Area                    | 1FFF FFFFh ~ 1400 4000h | Access forbidden (Reserved)            |       |

| Registers, etc                   | 1400 3FFFh ~ 1400 3000h | Registers, etc.                        |       |

| Reserved Area                    | 1400 2FFFh ~ 1400 2000h | Access forbidden (Reserved)            |       |

| Registers, etc                   | 1400 1FFFh ~ 1400 0000h | 0000h Registers, etc.                  |       |

| On ohin RAM Area                 | 13FF FFFFh ~ 1000 4000h | Access forbidden (Reserved)            |       |

| On-chip RAM Area                 | 1000 3FFFh ~ 1000 0000h | On-chip RAM area                       | 16KB  |

| On chin BOM Area                 | 0FFF FFFFh ~ 0008 0000h | Access forbidden (Reserved)            |       |

| On-chip ROM Area                 | 0007 FFFFh ~ 0000 0000h | On-chip Flash ROM area                 | 512KB |

Table 3

Internal Memory Address Map Details

• Configuration of External Memory Area

Four areas (Area 0 to 3) are allocated as the external memory area.

Area 0 is also used for the external ROM operation mode at reset.

Each area has independent select signals ( $nCS0 \sim nCS3$ ) and the number of waits can be set independently for each area.

Table 4 shows the address map of the external memory area.

| Memory Area | Address                 | Description                 | Note |

|-------------|-------------------------|-----------------------------|------|

| Area 3      | 7FFF FFFFh ~ 7100 0000h | Access forbidden (Reserved) |      |

| Alea S      | 70FF FFFFh ~ 7000 0000h | External memory (Area 3)    | 16MB |

| Area 2      | 6FFF FFFFh ~ 6100 0000h | Access forbidden (Reserved) |      |

| Alea Z      | 60FF FFFFh ~ 6000 0000h | External memory (Area 2)    | 16MB |

| Area 1      | 5FFF FFFFh ~ 5100 0000h | Access forbidden (Reserved) |      |

| Alea I      | 50FF FFFFh ~ 5000 0000h | External memory (Area 1)    | 16MB |

| Area 0      | 4FFF FFFFh ~ 4100 0000h | Access forbidden (Reserved) |      |

| Alea U      | 40FF FFFFh ~ 4000 0000h | External memory (Area 0)    | 16MB |

Table 4 External Memory Address Map Details

#### (19) External Memory Access

Wait Control

The number of wait state cycles for each area can be selected by a dedicated register.

8 wait cycles are provided: 0,1,2,3,4,5,6 or 7 (1 ~7 for write accesses)

The number of waits (set in the dedicated register) can be extended by inserting the external wait control signal.

Note: When the CF oscillation (1/1 divider) is used as the system clock, at least 1 wait cycle should be set for a read access.

External memory data accesses are shown in Tables 5, 6.

Reading from External Memory

|         | 8                      |                          |                             |

|---------|------------------------|--------------------------|-----------------------------|

|         | Data Width             | Access from 8-bit Device | Access from 16-bit Device   |

|         | 8 bits One 1-byte read |                          | One 1-byte read             |

|         | 16 bits                | Two 1-byte reads         | One 2-byte read             |

| 32 bits |                        | Four 1-byte reads        | Two 2-bytes reads           |

|         |                        | Table 5                  | External Data Access (READ) |

Table 5 External Data Access (READ)

Writing to External Memory

| Data Width | Access to 8-bit Device | Access to 16-bit Device |

|------------|------------------------|-------------------------|

| 8 bits     | One 1-byte write       | One 1-byte write        |

| 16 bits    | Two 1-byte writes      | One 2-byte write        |

| 32 bits    | Four 1-byte writes     | Two 2-byte writes       |

Table 6 External Data Access (WRITE)

#### (20) External ROM Operation Mode

The following 7 modes can be selected by setting the mode control pins (M2, M1, M0) at reset. For external ROM operation, 6 kinds of operating mode are provided with varying combinations of external data bus width and accessible memory address area.

Area 0 is always selected when external ROM operation mode is selected at reset.

Table 7 shows the details of external ROM operation mode.

| Operation Mode                                        | M1 | M2 | М3 | External Memory<br>Area on Boot | External Data<br>Bus Width | Address Output |

|-------------------------------------------------------|----|----|----|---------------------------------|----------------------------|----------------|

| Internal ROM operation                                | 0  | 0  | 0  | -                               | *1                         | *1             |

| External ROM operation 1                              | 0  | 0  | 1  | 1MB                             | 8 bits                     | A19 ~ A0       |

| External ROM operation 2                              | 0  | 1  | 0  | 8MB                             | 8 bits                     | A22 ~ A0       |

| External ROM operation 3                              | 0  | 1  | 1  | 16MB                            | 8 bits                     | A23 ~ A0       |

| External ROM operation 4                              | 1  | 0  | 0  | 1MB                             | 16 bits                    | A19 ~ A0       |

| External ROM operation 5                              | 1  | 0  | 1  | 8MB                             | 16 bits                    | A22 ~ A0       |

| External ROM operation 6                              | 1  | 1  | 0  | 16MB                            | 16 bits                    | A23 ~ A0       |

|                                                       | 1  | 1  | 1  | Forbidden                       | Forbidden                  | Forbidden      |

| Table 7. Oatting of the External DOM as another seads |    |    |    |                                 |                            |                |

Table 7 Setting of the External ROM operation mode

\*1 For internal ROM operation, ports can be selected by software to be used as address lines A0 to A23 or as normal input/output ports. (The default is ports are set to input for I/O.) Also, for internal ROM operation ports can be selected by software to be used as the data bus or as normal input/output ports. (The default is ports are set to input for I/O.)

Table 8 shows data access in the external ROM operation mode

| Data Width                                             | Access to 8-bit Device | Access to 16-bit Device |  |  |

|--------------------------------------------------------|------------------------|-------------------------|--|--|

| 8 bits                                                 | One 1-byte read        |                         |  |  |

| 16 bits                                                | Two 1-byte reads       | One 2-byte read         |  |  |

| 32 bits                                                | Four 1-byte reads      | Two 2-byte reads        |  |  |

| Table 9 Date Access in the External POM Operation Made |                        |                         |  |  |

Table 8 Data Access in the External ROM Operation Mode

Please note that even in the case where Thumb instruction are used, the ARM core always executes ARM instructions first at reset. It should switch to the Thumb instruction mode after reset. This also applies to external ROM boots. Since the RC oscillator is selected at reset, no wait cycles are inserted for the external ROM operation modes. Before switching the clock to the CF, please set the appropriate number of wait cycles by software.

#### (21) On Board Rewrite Function for Flash ROM

16KB boot area is provided in order to support the on board rewrite function for the internal Flash ROM. This boot program area is from address 0x7C000 to 0x7FFFF and can not be erased or written in normal CPU setting mode. Therefore the program area for the normal operation mode consists of 496 KB from  $0x00000 \sim 0x7BFFF$ .

On board programming

Program execution will start from address 0x7C000 if the BOOT terminal is "High" at reset. The program data to be written is received by some methods such as serial interface and stored in the internal RAM by the boot program. The boot program then jumps to the internal RAM area and rewrites the contents of Flash ROM with the program data which was stored in RAM. After the boot program jumps to RAM, and before it starts the actual rewriting of the Flash ROM, the boot control register flag should be set (in software).

In order to use the on board Flash rewrite system, software is also required for the PC. Please contact the SANYO sales office for further information.

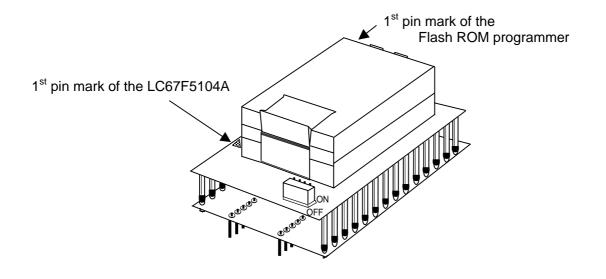

#### (22) Rewrite Function Using the PROM Writer

The general purpose PROM writer supports both the reading and writing of the internal Flash ROM using the dedicated conversion board.

- (i) Conversion board name : W67F5106TQ

- (ii) Available Flash ROM writer information

| Maker Name | Model   | Version Available | Device Code |

|------------|---------|-------------------|-------------|

| ANDO       | AF-9708 | *                 | *           |

#### (23) Development Tools

Emulator: ADVICE (PW920) produced by Yokogawa Digital Computer Corporation

#### (24) Flash ROM Programming Service

SANYO will perform Flash ROM programming and sealing on die encapsulation for a charge. For details, please contact your SANYO sales office.

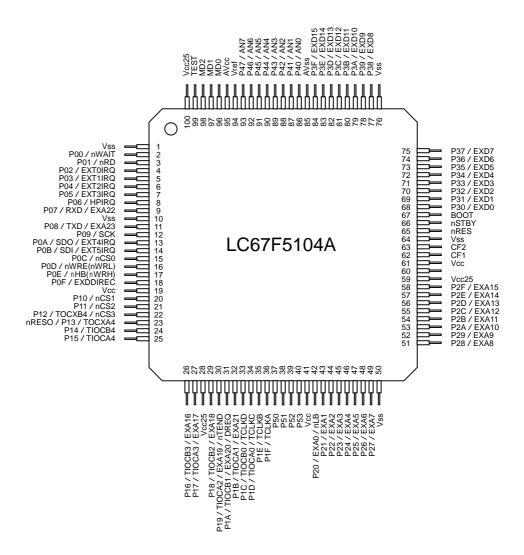

# **Pin Assignment**

# System Block Diagram

# **Pin Descriptions**

| Туре                   | Symbol               | Pin Number     | I/O              | Name and function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|----------------------|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Vcc                  | 19,41,61       | -                | <b>3.3V power supply</b><br>For connection to the 3.3V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power supply           | Vcc25                | 28, 59, 100    | _                | 2.5V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                      |                |                  | For connection to the 2.5V power supply.<br>Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | Vss                  | 1,10,50,64,76  | -                | For connection to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | CF1                  | 62             | Input            | CF oscillator pin<br>For connection to the CF oscillator.<br>Can also be used as external clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock                  | CF2                  | 63             | Output           | CF oscillator pin<br>For connection to the CF oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | Φ                    | 60             | Output           | System clock<br>Supplies the system clock to external devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operating mode control | MD2 ~ MD0            | 98,97,96       | Input            | Mode pins         For setting internal and external ROM modes, access area and data bus width (in external ROM modes).         • Internal ROM operation         Internal Flash ROM is selected after reset.         • External ROM operation (1 to 6)         ROM connected to the external access area 0 is selected after reset.         These pin states should not be changed during operation.         M2       M1       M0       Operating Mode         0       0       Internal ROM operation 1         0       1       External ROM operation 2         0       1       External ROM operation 1         0       1       External ROM operation 1         0       1       External ROM operation 2         0       1       External ROM operation 2         0       1       External ROM operation 3         1       0       1       External ROM operation 4         1       0       1       External ROM operation 5         1       1       0       External ROM operation 6 |

|                        | BOOT                 | 67             | Input            | BOOT pin<br>Normally Low; High during boot mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | nRES                 | 65             | Input            | Reset Input<br>When driven Low, the chip is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| System Control         | nRESO                | 23             | Output           | Reset Output<br>Outputs a reset signal to external devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | nSTBY                | 66             | Input            | Standby<br>When driven Low, the chip enters Hardware<br>Standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupts             | HPIRQ                | 8              | Input            | High priority external interrupt request<br>This pin is fixed as an FIQ interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | EXT5IRQ ~<br>EXT0IRQ | 14,13,7,6,5,4  | Input            | External Interrupt requests 0 to 5<br>Setting as FIQ or IRQ is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | TCLKD ~<br>TCLKA     | 33 ~ 36        | Input            | Clock inputs A to D<br>Inputs external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | TIOCA4 ~<br>TIOCA0   | 25,27,30,32,34 | Input/<br>output | Input capture/output compare A0 to A4<br>GRA0 to GRA4 output compare, input<br>capture or PWM output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Timers                 | TIOCB4 ~<br>TIOCB0   | 24,26,29,31,33 | Input/<br>output | Input capture/output compare B0 to B4<br>GRB0 to GRB4 output compare, input<br>capture or PWM output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                        | TOCXA4               | 23             | Output           | Output compare XA4<br>PWM output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                        | TOCXB4               | 24             | Output           | Output compare XB4<br>PWM output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Туре             | Symbol       | Pin Number                       | I/O              | Name and function                                                                                                                   |

|------------------|--------------|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                  | SDI          | 14                               | Input            | Receive data<br>Serial interface data input pin                                                                                     |

| Serial interface | SDO          | 13                               | Output           | Transmit data<br>Serial interface data output pin                                                                                   |

|                  | SCK          | 12                               | Input/<br>output | Serial clock<br>Serial interface clock input/output pin                                                                             |

| UART             | TXD          | 11                               | Output           | Transmit data<br>UART data output pin                                                                                               |

| UANT             | RXD          | 9                                | Input            | Receive data<br>UART data input pin                                                                                                 |

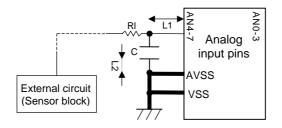

|                  | AN7 ~AN0     | 93 ~ 86                          | Input            | Analog 0 to 7<br>Analog input pins                                                                                                  |

| AD converter     | AVcc         | 95                               | Input            | Power supply(+3.3V) pin for the A/D converter<br>Connect to the system power supply(+3.3V)<br>when not using the A/D converter.     |

| AD conventer     | AVss         | 85                               | Input            | Ground pin for the A/D converter<br>Connect to system ground(0V).                                                                   |

|                  | Vref         | 94                               | Input            | Reference voltage input pin for the A/D converter<br>Connect to the system power supply(+3.3V)<br>when not using the A/D converter. |

| Address bus      | EXA23 ~ EXA0 | 11,9,32~29,27,26<br>58~51, 49~42 | Output           | External address bus<br>Output address signals for external memory access.                                                          |

| Data bus         | EXD15 ~ EXD0 | 84~77,75~68                      | Input/<br>output | External data bus<br>Bi-directional data bus for external memory<br>devices.                                                        |

|                  | nCS3 ~ nCS0  | 22,21,20,15                      | Output           | Chip selection<br>Signals for selecting external memory areas<br>0 to 3.                                                            |

|                  | EXDDIREC     | 18                               | Output           | External data bus direction<br>Indicates whether the access to the selected<br>external memory area is read or write.               |

|                  | nRD          | 3                                | Output           | Read<br>When Low, indicates reading from the selected<br>external memory area.                                                      |

| Bus control      | nWRE         | 16                               | Output           | Write enable<br>When Low, indicates writing to the external<br>memory area selected.                                                |

|                  | nWRL         | 16                               | Output           | Write enable low signal<br>Enables lower byte write of external device.                                                             |

|                  | nWRH         | 17                               | Output           | Write enable high signal<br>Enables upper byte write of external device.                                                            |

|                  | nLB          | 42                               | Output           | Low byte selection<br>Selects lower byte of external memory device.                                                                 |

|                  | nHB          | 17                               | Output           | High byte selection<br>Selects upper byte of external memory device.                                                                |

|                  | nWAIT        | 2                                | Input            | Wait<br>Requests the insertion of wait state(s) (in the<br>number of bus cycles) when accessing an external<br>memory area.         |

| DMAC             | nTEND        | 30                               | Output           | DMA transfer end                                                                                                                    |

|                  | DREQ         | 31                               | Input            | DMA request                                                                                                                         |

| Туре      | Symbol    | Pin Number   | I/O              | Name and function                                                                |

|-----------|-----------|--------------|------------------|----------------------------------------------------------------------------------|

|           | P00 ~ P0F | 2~9,11~18    | Input/<br>output | Port 0<br>16-bit input/output pins<br>The direction of each pin is programmable. |

|           | P10 ~ P1F | 20~27,29~36  | Input/<br>output | Port 1<br>16-bit input/output pins<br>The direction of each pin is programmable. |

| I/O ports | P20 ~ P2F | 42~49, 51~58 | Input/<br>output | Port 2<br>16-bit input/output pins<br>The direction of each pin is programmable. |

|           | P30 ~ P3F | 68~75, 77~84 | Input/<br>output | Port 3<br>16-bit input/output pins<br>The direction of each pin is programmable. |

|           | P40 ~ P47 | 86 ~ 93      | Input            | Port 4<br>8-bit input pins                                                       |

|           | P50 ~ P53 | 37 ~ 40      | Input/<br>output | Port 5<br>4-bit input/output pins<br>The direction of each pin is programmable.  |

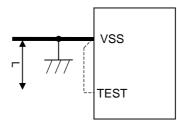

| TEST      | TEST      | 99           | Input            | Test pin<br>High in Test mode (otherwise Low).                                   |

# **Electrical Characteristics**

1. Absolute Maximum Ratings / Ta=25°C, VSS=0V

| Parameter                          | Symbol         | Applicable Pins / Notes          | Conditions          | Ratings         | Unit |

|------------------------------------|----------------|----------------------------------|---------------------|-----------------|------|

| Max. supply voltage                | Vccmax         | Vcc                              |                     | -0.3 ~ +4.0     | V    |

| Max. supply vollage                | Vcc25max       | Vcc25                            |                     | -0.3 ~ +3.0     | V    |

| Input voltage                      | Vi             | All input only pins              |                     | -0.3 ~ Vcc+0.3  | V    |

| I/O voltage                        | Vio            | All I/O pins                     |                     | -0.3 ~ Vcc+0.3  | V    |

| High level output peak<br>current  | Іорн           | All output and I/O pins          | per pin value       | 10              | mA   |

| High level total<br>output current | Σιοαή          | Total of all output and I/O pins | total pins<br>value | 80              | mA   |

| Low level output peak<br>current   | IOPL           | All output and I/O pins          | per pin value       | 10              | mA   |

|                                    | $\Sigma$ ioal  | Total of all output and I/O pins | total pins<br>value | 120             | mA   |

| Low level total                    | $\Sigma$ IOAL1 | P00~P0F, P10~P17                 | total pins<br>value | 60              | mA   |

| output current                     | $\Sigma$ ioal2 | P18~P1F, P50~P53, P20~P2F        | total pins<br>value | 60              | mA   |

|                                    | $\Sigma$ ioal3 | P30~P3F                          | total pins<br>value | 60              | mA   |

| Reference voltage                  | Vref           | Vref *NOTE 1                     |                     | -0.3 ~ AVcc+0.3 | V    |

| Analog supply voltage              | AVccmax        | AVcc *NOTE1                      |                     | -0.3 ~ +4.0     | V    |

| Analog input voltage               | Van            | Each analog input pin            |                     | -0.3 ~ AVcc+0.3 | V    |

| Allowable power dissipation        | Pdmax          | TQFP100                          | Ta=0 ~ +75°C        | 500             | mW   |

| Operating temperature              | Topg           |                                  |                     | 0 ~ +75         | °C   |

| Storage temperature                | Tstg           |                                  |                     | -55 ~ +125      | °C   |

\*NOTE 1 AVcc and Vref should be connected to the supply voltage (Vcc) when the A/D converter is not in use or when in Standby mode

# 2. DC Characteristics (preliminary specifications) / Ta=0 ~ 75°C, VSS=0V

| Parameter                              | Symbol | Appliaghla Ding / Natag                                                              | Conditions                   |         | Rating  |             | Unit |

|----------------------------------------|--------|--------------------------------------------------------------------------------------|------------------------------|---------|---------|-------------|------|

| Parameter                              | Symbol | Applicable Pins / Notes                                                              | Conditions                   | Min.    | Typical | Max.        | Unit |

| Operating supply voltage<br>(I/O, ADC) | Vcc    | Vcc, AVcc                                                                            |                              | 3.0     | 3.3     | 3.6         | V    |

| Operating supply voltage (internal)    | Vcc25  | Vcc25                                                                                |                              | 2.25    | 2.5     | 2.75        | V    |

| High level input voltage               | VIH1   | P00~P0F, P10~P1F, P20~P2F<br>P30~P3F, P40~P47, P50~P53<br>CF1 (External clock input) |                              | 0.75Vcc |         | Vcc         | V    |

|                                        | VIH2   | nRES, nSTBY, TEST, MD0,<br>MD1, MD2                                                  |                              | 0.80Vcc |         | Vcc         | V    |

| Low level input voltage                | Vı∟    | All input and I/O pins<br>CF1 (External clock input)                                 |                              | Vss     |         | 0.15Vc<br>c | V    |

| Schmitt trigger voltage                | Vsн    | All input and I/O pins                                                               |                              |         | 0.08Vcc |             | V    |

| High level output voltage              | Voh1   | All output and I/O pins (except for $\Phi$ , P50~P53)                                | Iон = -4mA                   | Vcc-0.8 |         |             | V    |

| •                                      | Voh2   | Φ, P50~P53                                                                           | lон = -4mA                   | Vcc-0.4 |         |             | V    |

| Low level output voltage               | Vol    | All output and I/O pins                                                              | lo∟= 4mA                     |         |         | 0.4         | V    |

| High level input current               | Ін     | All input and I/O pins<br>(output off for I/O pins)                                  | Vin = Vcc                    | -10     |         | +10         | μΑ   |

| Low level input current                | lı.    | All input and I/O pins<br>(output off for I/O pins)                                  | Vin = Vss                    | -10     |         | +10         | μΑ   |

| Input pin capacitance                  | CIN    | All input pins                                                                       | f=1MHz, Ta=25°C,<br>Vin = 0V |         |         | 15          | pF   |

| Output pin capacitance                 | Соит   | All output pins                                                                      | f=1MHz, Ta=25°C,<br>Vin=0V   |         |         | 15          | pF   |

| I/O pin capacitance                    | Ci/o   | All I/O pins                                                                         | f=1MHz, Ta=25°C,<br>Vin = 0V |         |         | 15          | pF   |

3. Sample Current Dissipation Characteristics (preliminary specifications) / Ta=0 ~ 75°C, VSS=0V

The sample current dissipation characteristics were measured with Sanyo's evaluation board using the recommended circuit values indicated in Sample Oscillation Circuit Characteristics externally. The current through the LSI output transistor is not included.

|        | Parameter                             | Symbol              | Applicable   | Conditions                                                                                                  | Rating |         |      | Unit |

|--------|---------------------------------------|---------------------|--------------|-------------------------------------------------------------------------------------------------------------|--------|---------|------|------|

|        | Falameter                             | Symbol              | Pins / Notes | Conditions                                                                                                  | Min.   | Typical | Max. | Unit |

|        | Normal operation 1 *NOTE 1            | IDDRUN1             |              |                                                                                                             |        | 23      | 34   | mA   |

| tion   | Normal operation 2 *NOTE 2            | IDDRUN2             |              | <ul> <li>System clock: CF17.28MHz<br/>(1/1 divider)</li> <li>Internal RC oscillation<br/>stopped</li> </ul> |        | 19      | 29   | mA   |

| ssipat | Sleep mode<br>*NOTE 3                 | IDDslp              |              |                                                                                                             |        | 9       | 16   | mA   |

| nt Dis | Module Standby mode<br>*NOTE 4        | IDDMSTBY            | Vcc          |                                                                                                             |        | 6       | 13   | mA   |

| rer    | Standby mode                          | <b>IDD</b> STBY     |              | All oscillation stopped                                                                                     |        | 4       | 400  | μA   |

| Currei | External clock operation 1 *NOTE 1    | IDDEXCLC1           |              | External clock: 36MHz                                                                                       |        | 23      | 34   | mA   |

|        | External clock operation 2<br>*NOTE 2 | eration 2 IDDEXCLC2 |              | (System clock: 1/2 divider)                                                                                 |        | 19      | 29   | mA   |

\*NOTE 1: These values are for when the program is fetched from the internal Flash ROM and ADC is operating.

\*NOTE 2: These values are for when the program is fetched from the internal SRAM and ADC is operating. Writing to the internal Flash ROM is not included.

\*NOTE 3: These values are for when ADC is halted.

\*NOTE 4: These values are for sleep mode with all modules halted.

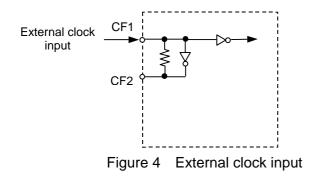

### 4. AC Characteristics(preliminary specifications) Figure 5 Load

| Parameter                                    | Symbol       | Applicable Pins / Notes                      | Conditions |      | Ratir   | ng   |      |

|----------------------------------------------|--------------|----------------------------------------------|------------|------|---------|------|------|

| Farameter                                    | Symbol       | Applicable Fills / Notes                     | Conditions | Min. | Typical | Max. | Unit |

| CF oscillator frequency range                | fcfck        | Ceramic resonator<br>oscillation at 17.28MHz | Figure 1   |      | 17.28   |      | MHz  |

| RC oscillator frequency range                | frcck        | Internal RC clock                            |            | 0.4  |         | 2.0  | MHz  |

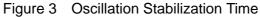

| External clock frequency range               | fexck        | External clock input<br>*NOTE 1              | Figure 4   | 0.4  |         | 36.0 | MHz  |

| Extornal clock pulse width                   | tскь         | CF1:<br>0.5MHz~18MHz input                   | Figure 4   | 17   |         |      | nS   |

| External clock pulse width                   | tскн         | CF1:<br>18MHz~36MHz input                    | Figure 4   | 10   |         |      | nS   |

| External clock<br>rising / falling edge time | texr<br>texf | CF1: 18MHz input                             | Figure 4   |      |         | 10   | nS   |

| System clock frequency                       | fsysck       | *NOTE 2                                      |            | 0.05 |         | 18   | MHz  |

4-1 Allowable operation clock / Ta= $0 \sim 75^{\circ}$ C, VSS=0V

\*NOTE 1: For external clock operation, if the external oscillator frequency is more than 18MHz, set the oscillation divider ratio to at least 1/2 before switching the system clock from internal RC to external clock.

\*NOTE 2: The system clock frequency is selectable from 1/1~1/8 division of the main clock. The divider is provided in the OSC module.

4-2 Control signal timing (preliminary specifications) / Ta= $0 \sim +75^{\circ}$ C, VSS=0V

| Parameter                                     | Symbol          | Applicable Pins / Notes   | Conditions |      | Ratir   | ng   |      |

|-----------------------------------------------|-----------------|---------------------------|------------|------|---------|------|------|

| i arameter                                    | Symbol          | Applicable 1 lins / Notes | Conditions | Min. | Typical | Max. | Unit |

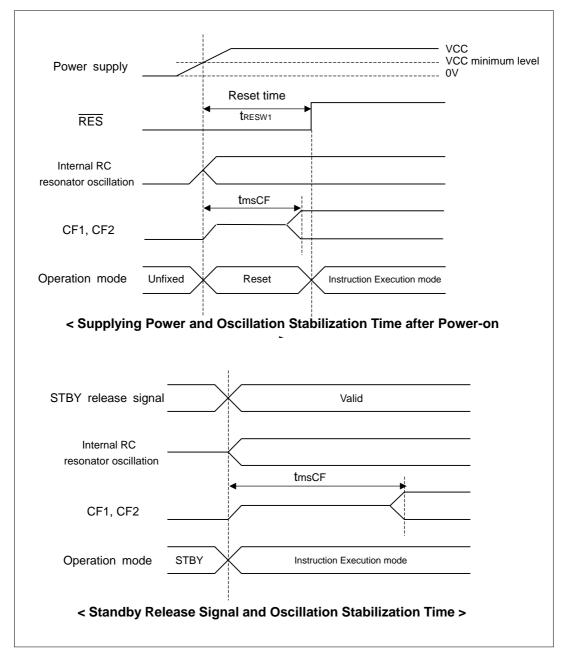

| nRES pulse width<br>(when supplying power)    | tresw1          | nRES                      | Figure 3   | 10   |         |      | ms   |

| nRES pulse width<br>(during normal operation) | tresw2          | nRES                      |            | 40   |         |      | μS   |

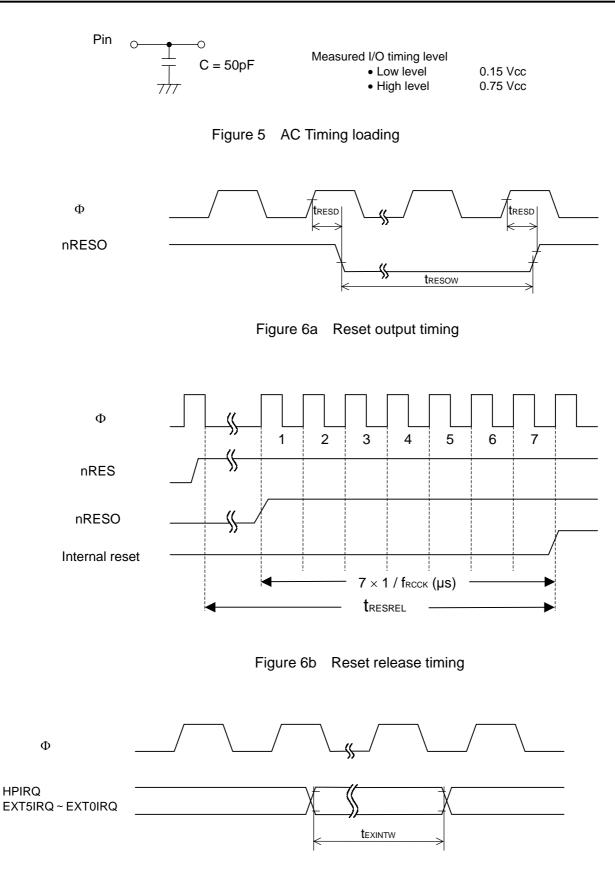

| nRESO output delay time                       | tresd           | nRESO                     | Figure 6a  |      |         | 20   | ns   |

| nRESO output pulse width<br>(WDT reset)       | tresow          | nRESO                     | Figure 6a  | 50   |         |      | Тсус |

| Reset release time                            | tresrel         | nRES                      | Figure 6b  |      |         | 30   | μS   |

| External interrupt pulse width *NOTE 1        | <b>t</b> exintw | HPIRQ, EXT5IRQ~ EXT0IRQ   | Figure 7   | 4    |         |      | Тсус |

| Oscillation stabilizing time (CF)             | tmsCF           |                           | Figure 2   | 10   |         |      | ms   |

\*NOTE 1: Regarding the external interrupt pulse width when using a noise filter, please refer to the manual.

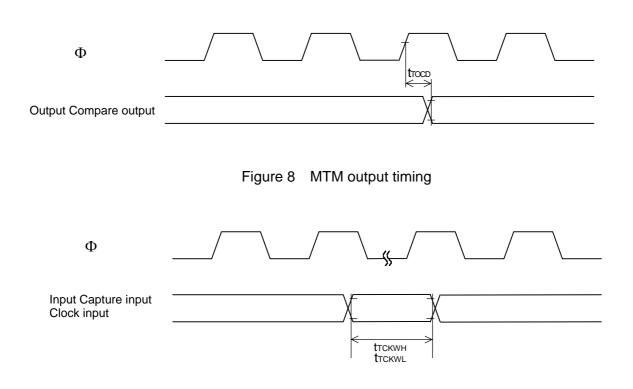

4-3 Multiple timer input/output timing (preliminary specifications) /  $Ta=0 \sim +75^{\circ}C$ , VSS=0V

| Para         | Parameter             |                | Symbol Applicable Pins / Notes                    |            | Rating |         |      |      |

|--------------|-----------------------|----------------|---------------------------------------------------|------------|--------|---------|------|------|

| T arameter   |                       | Symbol         | Applicable 1 IIIs / Notes                         | Conditions | Min.   | Typical | Max. | Unit |

| Timer output | delay time            | <b>t</b> тоср  | TIOCA0~TIOCA4,<br>TIOCB0~TIOCB4<br>TOCXA4, TOCXB4 | Figure 8   |        |         | 20   | ns   |

| Timer clock  | Single edge detection | tтскwн         | TCLKA~TCLKD                                       | Figure 9   | 1.5    |         |      | Тсус |

| pulse width  | Both edges detection  | <b>t</b> TCKWL | TIOCA0~TIOCA4<br>TIOCB0~TIOCB4                    | Figure 9   | 2.5    |         |      | Тсус |

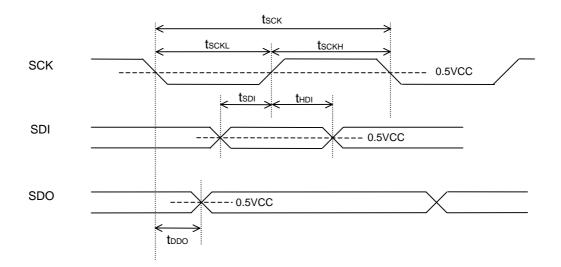

| Parameter                     | Symbol | Applicable Pins / Notes  | Conditions | Rating |         |      |      |  |

|-------------------------------|--------|--------------------------|------------|--------|---------|------|------|--|

| Falailletei                   | Symbol | Applicable Fills / Notes | Conditions | Min.   | Typical | Max. | Unit |  |

| Input clock cycle             | Тѕск   | SCK                      | Figure 10  | 8      |         |      | Тсус |  |

| Input clock low pulse width   | TSCKL  | SCK                      | Figure 10  | 4      |         |      | Тсус |  |

| Input clock high pulse width  | Тѕскн  | SCK                      | Figure 10  | 4      |         |      | Тсус |  |

| Output clock cycle            | Тѕско  | SCK                      | Figure 10  | 8      |         |      | Тсус |  |

| Output clock low pulse width  | TSCKOL | SCK                      | Figure 10  | 4      |         |      | Тсус |  |

| Output clock high pulse width | Тѕскон | SCK                      | Figure 10  | 4      |         |      | Тсус |  |

| Input data setup time         | tsdi   | SCK(input), SDI          | Figure 10  | 2      |         |      | Тсус |  |

| Input data hold time          | Тны    | SCK(input), SDI          | Figure 10  | 2      |         |      | Тсус |  |

| Output delay time             | Tddo   | SCK(output), SDO         | Figure 10  |        | 2       |      | Тсус |  |

4-4 Serial input/output timing (preliminary specifications) / Ta=0 ~ +75°C, VSS=0V

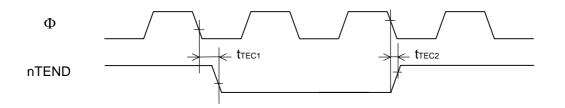

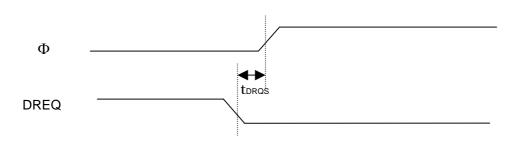

4-5 DMAC input/output timing (preliminary specifications) /  $Ta=0 \sim +75^{\circ}C$ , VSS=0V

| Parameter          | Symbol Ap         | Applicable Pins / Notes | Conditions | Rating |         |      |      |

|--------------------|-------------------|-------------------------|------------|--------|---------|------|------|

|                    |                   |                         |            | Min.   | Typical | Max. | Unit |

| nTEND delay time 1 | t <sub>TEC1</sub> | nTEND                   | Figure 11  |        |         | 20   | ns   |

| nTEND delay time 2 | t <sub>TEC2</sub> | nTEND                   | Figure 11  |        |         | 20   | ns   |

| DREQ set up time   | <b>t</b> dreq     |                         | Figure 12  | 35     |         |      | ns   |

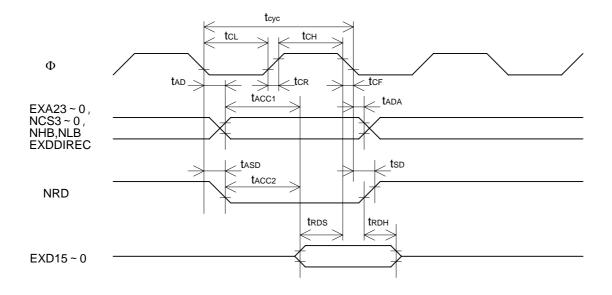

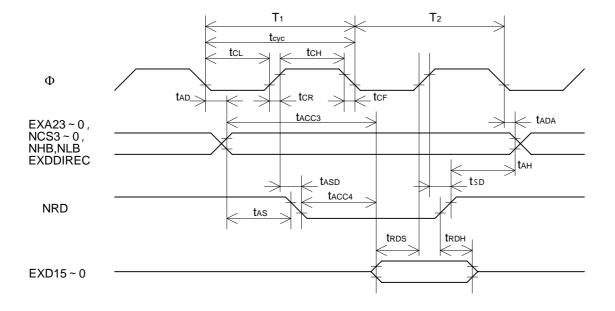

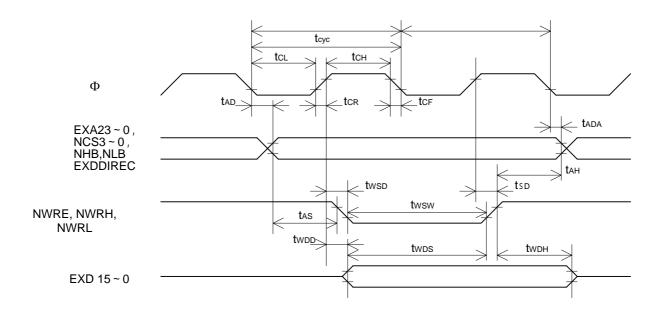

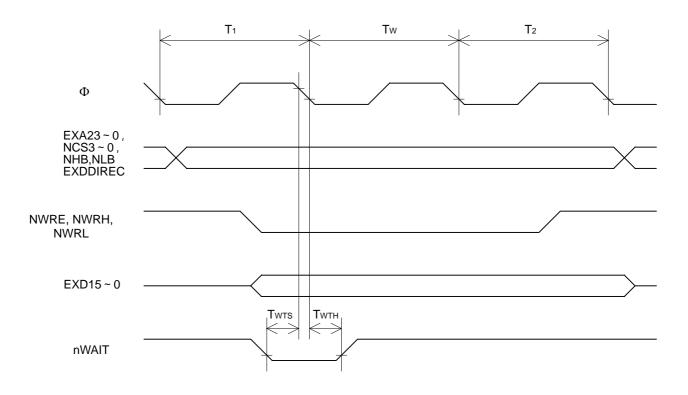

4-6 Bus timing (preliminary specifications) / Ta= $0 \sim +75^{\circ}$ C, VSS=0V

|                                   | · ·               | Applicable Pins /                | Conditions       |      | Ratin   | g     |      |

|-----------------------------------|-------------------|----------------------------------|------------------|------|---------|-------|------|

| Parameter                         | Symbol            | Notes                            | Conditions       | Min. | Typical | Max.  | Unit |

| Clock cycle time                  | <b>t</b> cyc      | Φ                                | Figures 14 a,b,c | 55   |         | 20000 |      |

| Clock pulse width low level time  | tc∟               | Φ                                | Figures 14 a,b,c | 15   |         |       |      |

| Clock pulse width high level time | tсн               | Φ                                | Figures 14 a,b,c | 15   |         |       |      |

| Clock rising time                 | <b>t</b> CR       | Φ                                | Figures 14 a,b,c |      |         | 10    |      |

| Clock falling time                | <b>t</b> CF       | Φ                                | Figures 14 a,b,c |      |         | 10    |      |

| Address delay time 1              | tad               | EXA23~0, Φ                       | Figures 14 a,b,c |      |         | 25    |      |

| Address delay time 2              | <b>t</b> ada      | EXA23~0, Φ                       | Figures 14 a,b,c | -13  |         |       |      |

| Address hold time                 | tан               | EXA23~0, NRD                     | Figures 14 b,c   | 5    |         |       |      |

| Address strobe delay time         | tasd              | Φ, NRD                           | Figures 14 a,b   |      |         | 25    |      |

| Write strobe delay time           | twsp              | Φ, NWRE, NWRL, NWRH              | Figure 14 c      |      |         | 25    |      |

| Strobe delay time                 | tsd               | Φ, NRD, NWRE,<br>NWRL, NWRH      | Figures 14 a,b,c |      |         | 25    |      |

| Write data strobe pulse width     | twsw              | NWRE, NWRL, NWRH                 | Figure14 c       | 35   |         |       | ns   |

| Address setup time                | t <sub>AS</sub>   | EXA23~0, NRD, NWRE<br>NWRL, NWRH | Figures 14 b,c   | 5    |         |       |      |

| Read data setup time              | trds              | EXD15~0, Φ                       | Figures 14 a,b   | 20   |         |       |      |

| Read data hold time               | <b>t</b> rdh      | EXD15~0, NRD                     | Figures 14 a,b   | 0    |         |       |      |

| Write data delay time             | twdd              | EXD15~0, Φ                       | Figure 14 c      |      |         | 25    |      |

| Write data set up time            | twos              | EXD15~0, NWRE,<br>NWRL, NWRH     | Figure 14 c      | 20   |         |       |      |

| Write data hold time              | <b>t</b> wdh      | EXD15~0, NWRE,<br>NWRL, NWRH     | Figure 14 c      | 15   |         |       |      |

| Read data access time 1           | tACC1             | EXD15~0, EXA23~0                 | Figure 14 a      |      |         | 10    |      |

| Read data access time 2           | t <sub>ACC2</sub> | EXD15~0, NRD                     | Figure 14 a      |      |         | 10    |      |

| Read data access time 3           | t <sub>ACC3</sub> | EXD15~0, EXA23~0                 | Figure 14 b      |      |         | 15    |      |

| Read data access time 4           | tACC4             | EXD15~0, NRD                     | Figure 14 b      |      |         | 7     |      |

| Wait setup time                   | <b>t</b> wrs      | Φ, NWAIT                         | Figure 14 d      | 15   |         |       |      |

| Wait hold time                    | twтн              | Φ, NWAIT                         | Figure 14 d      | 0    |         |       |      |

| Parameter                      | Symbol   | Applicable Dina / Natas                   | Conditions                    |           | 1.1     |      |      |

|--------------------------------|----------|-------------------------------------------|-------------------------------|-----------|---------|------|------|

| Parameter                      |          | Applicable Pins / Notes                   | Conditions                    | Min.      | Typical | Max. | Unit |

| ADC Resolution                 | N        | AN0~AN7                                   |                               |           | 8       |      | bit  |

| ADC Differential linear        | Edef1    | AN0~AN7                                   | Vref =AVcc                    |           |         | ±1   | LSB  |

| error                          | Edef2    | ANO~AN7                                   | Vref =2.90V                   |           |         | ±1   | LSB  |

| ADC Linear error               | Elin1    | AN0~AN7                                   | Vref =AVcc                    |           |         | ±1   | LSB  |

|                                | Elin2    | AN0~AN7                                   | Vref =2.90V                   |           |         | ±1   | LSB  |

| ADC Conversion time<br>*NOTE 1 | Tcad     | AN0~AN7                                   | When system<br>clock is 18MHz | 5.33      |         |      | μS   |

| ADC Reference resistance       | RAVref   | Resistance value between<br>Vref and AVss |                               |           | 25      |      | kΩ   |

| Input reference voltage        | VAVref   | Vref                                      |                               | 2.90      |         | AVcc | V    |

| Analog input voltage range     | VAin     | AN0~AN7                                   |                               | AVss      |         | Vref | V    |

| 0 scale offset voltage         | VOoff    |                                           |                               |           |         | 60   | mV   |

| Full scale offset voltage      | Vfulloff |                                           |                               | Vref - 60 |         |      | mV   |

| ADC Operating clock            | ADCCLK   |                                           |                               | 0.1       |         | 2.25 | MHz  |

# 5. ADC Characteristics (preliminary specifications) / $Ta=0 \sim 75^{\circ}C$ , VSS=0V

\*NOTE 1: The conversion time is for normal single mode operation with 18MHz system clock.

\*NOTE 2: Please note that when the ADC returns from Standby mode, about 5µs is required for the internal ladder resistors to become stable.

### 6. Flash ROM Characteristics / Ta= $0 \sim 75^{\circ}$ C, VSS=0V

| Parameter                    | Symbol  | Applicable Pins /<br>Notes | Conditions                       |      | Unit    |      |       |

|------------------------------|---------|----------------------------|----------------------------------|------|---------|------|-------|

| Falallietei                  |         |                            | Conditions                       | Min. | Typical | Max. | Unit  |

| On-board rewriting current   | FICCW   |                            | VCC25=2.25~2.75V<br>VCC=3.0~3.6V |      |         | 10   | mA    |

| Erase time<br>(Sector erase) | FTSE    |                            | 1 sector is 2K bytes.            | 20   |         |      | ms    |

| Rewrite time                 | FTWP    |                            | 32 bits                          |      |         | 42   | μs    |

| Number of Sector rewrites    | FSECWRT |                            | *NOTE 1                          |      |         | 1000 | times |

\*NOTE 1: Definition of Flash ROM rewriting

- The data in the Flash ROM is rewritten in sector units (2K bytes).

- A pair of one erase and one write together of a sector unit is considered to be one rewrite. (The 2K bytes in one sector are assumed to be rewritten contiguously as one unit.)

- The same address cannot be written to more than twice (with respect to one erase).

- Cumulative writing time: A sector consists of 8 sub-blocks (each of 256K bytes) and the cumulative writing time for one of these sub-blocks should be 8ms at most.

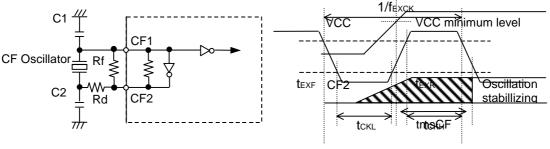

# **Recommended Oscillation Circuit and Sample Characteristics**

The oscillation circuit sample characteristics in the table below are based on the following:

- The recommended circuit parameters were verified by an oscillator manufacturer using Sanyo's oscillation evaluation board; and

- The sample characteristics provided are the result of evaluation performed with these recommended circuit parameters connected externally.

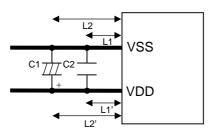

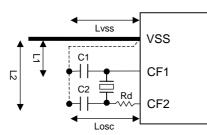

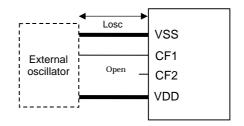

| Frequency | Manufacturer | Oscillator         | Recommended circuit parameters |      |      |    |            | supply voltage | Time for<br>Oscillation to<br>Stabilize<br>*NOTE |  |

|-----------|--------------|--------------------|--------------------------------|------|------|----|------------|----------------|--------------------------------------------------|--|

|           |              |                    | C1                             | C2   | Rf   | Rd |            | Typical        | Min.                                             |  |

| 17.28MHz  | MURATA       | CSACV17M2X55J01-R0 | 10pF                           | 10pF | Open | 0Ω | 3.0 ~ 3.6V |                | 10ms                                             |  |

| 18.00MHz  | MURATA       | CSACV18MOX55J-R0   | 10pF                           | 10pF | Open | 0Ω | 3.0 ~ 3.6V |                | 10ms                                             |  |

Recommended oscillation circuit and sample characteristics (Ta=  $0 \sim +75^{\circ}$ C)

\*NOTE The time for oscillation to stabilize is the period of time required for the CF oscillator to stabilize either from the point when VCC reaches the minimum voltage level after power-on or from when standby mode is released. (Refer to Figure 2)

The values of the oscillation circuit sample characteristics may differ depending on the application board. For further assistance, please contact your oscillator manufacturer while taking note of the following.

- Since the precision of the oscillation frequency is affected by the amount of wiring on the application board etc., the oscillation frequency should be appropriately adjusted on the mass production board.

- •The oscillation frequencies and operating supply voltage ranges in the above table are for an operating temperature range of 0 to  $+75^{\circ}$ C. In the case the oscillation circuit is used out of this range or used for products requiring high reliability such as automotive products, please contact your oscillator manufacturer.

- When using an oscillator which is not mentioned in the oscillation circuit sample characteristics, please contact the Sanyo sales office.

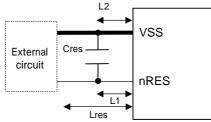

Since the recommended oscillation circuit is easily affected by such things as noise and the amount of wiring please refer to the following points when performing wiring and layout. (As the circuit is designed to have low oscillation gain in order to reduce power dissipation, noise etc. will easily affect the circuit. Therefore, special care should be taken when putting together the recommended oscillation circuit.)