## SANYO Semiconductors DATA SHEET

# LC863448C,LC863440C LC863432C,LC863428C — LC863424C,LC863420C LC863416C

**CMOSIC** 48K/40K/32K/28K/24K/20K/16K-byte ROM, CGROM16K-byte on-chip 640/512-byte RAM and 352x9 bit OSD RAM 8-bit 1-chip Microcontroller

#### Overview

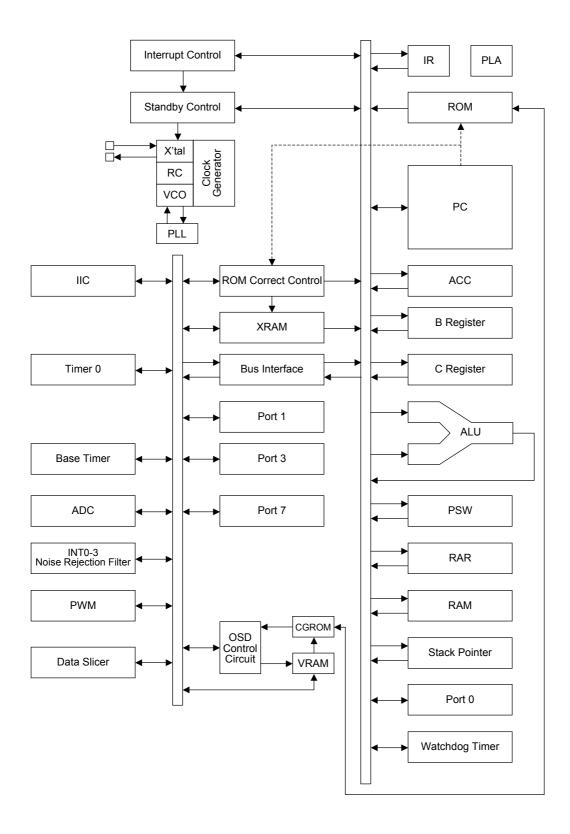

The LC863448C/40C/32C/28C/24C/20C/16C are 8-bit single chip microcontrollers with the following on-chip functional blocks:

- CPU : Operable at a minimum bus cycle time of 0.424μs

- On-chip ROM capacity

Program ROM: 48K/40K/32K/28K/24K/20K/16K bytes

CGROM: 16K bytes

- On-chip RAM capacity: 640/512 bytes

- OSD RAM : 352×9 bits

- Closed-Caption TV controller and the on-screen display controller

- Closed-Caption data slicer

- Four channels×6-bit AD Converter

- Three channels×7-bit PWM

- 16-bit timer/counter, 14-bit base timer

- IIC-bus compliant serial interface circuit (Multi-master type)

- ROM correction function

- 12-source 8-vectored interrupt system

- Integrated system clock generator and display clock generator

Only one X'tal oscillator (32.768kHz) for PLL reference is used for both generators

TV control and the Closed Caption function

All of the above functions are fabricated on a single chip.

Note: This product includes the IIC bus interface circuit. If you intend to use the IIC bus interface, please notify us of this in advance of our receiving your program ROM code order.

Purchase of SANYO IIC components conveys a license under the Philips IIC Patents Rights to use these components in an IIC system, provided that the system conforms to the IIC Standard Specification as defined by Philips.

### Trademarks

IIC is a trademark of Philips Corporation.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

### **Features**

■Read-Only Memory (ROM): 49152×8 bits / 40960×8 bits / 32768×8 bits /

28672×8 bits / 24576×8 bits / 20480×8 bits /

16384×8 bits for program 16128×8 bits for CGROM

■Random Access Memory (RAM): 512×8 bits (working area): LC863448C/40C

384×8 bits (working area): LC863432C/28C/24C/20C/16C

128×8 bits (working or ROM correction function)

352×9 bits (for CRT display)

#### **■**OSD Functions

• Screen display : 36 characters×16 lines (by software)

• RAM : 352 words (9 bits per word)

Display area: 36 words×8 lines Control area: 8 words×8 lines

Characters

Up to 252 kinds of 16×32 dot character fonts (4 characters including 1 test character are not programmable)

Each font can be divided into two parts and used as two fonts (Ex. 16×16 dot character font×2)

At least 111 characters need to be divide between a 16×17 dot and 8×9 dot character font to display the caption fonts.

• Various character attributes

Character colors : 16colors (analog mode: IVp-p output ) / 8colors (digital mode)

Character background colors : 16colors (analog mode: IVp-p output ) / 8colors (digital mode)

Fringe / shadow colors : 16colors (analog mode: IVp-p output ) / 8colors (digital mode)

Full screen colors : 16colors (analog mode: IVp-p output ) / 8colors (digital mode)

Rounding Underline

Italic character (slanting)

- Attribute can be changed without spacing

- Vertical display start line number can be set for each row independently (Rows can be overlapped)

- Horizontal display start position can be set for each row independently

- Horizontal pitch (9 to 16 dots)\*1 and vertical pitch (1 to 32 dots) can be set for each row independently

- Different display modes can be set for each row independently

Caption • Text mode / OSD mode 1 / OSD mode 2 (Quarter size) / Simplified graphic mode

• Ten character sizes \*1

Horez.  $\times$  Vert. = (1 $\times$ 1), (1 $\times$ 2), (2 $\times$ 2), (2 $\times$ 4), (0.5 $\times$ 0.5) (1.5 $\times$ 1), (1.5 $\times$ 2), (3 $\times$ 2), (3 $\times$ 4), (0.75 $\times$ 0.5)

- Shuttering and scrolling on each row

- Simplified Graphic Display

Note \*1: range depends on display mode: refer to the manual for details.

- ■Data Slicer (closed caption format)

- Closed caption data and XDS data extraction

- NTSC/PAL, and extracted line can be specified

### ■Bus Cycle Time / Instruction-Cycle Time

| Bus Cycle Time | Instruction Cycle Time | Clock Divider | System Clock Oscillation               | Oscillation Frequency | Voltage      |

|----------------|------------------------|---------------|----------------------------------------|-----------------------|--------------|

| 0.424µs        | 0.848µs                | 1/2           | Internal VCO<br>(Ref: X'tal 32.768kHz) | 14.156MHz             | 4.5V to 5.5V |

| 7.5µs          | 15.0µs                 | 1/2           | Internal RC                            | 800kHz                | 4.5V to 5.5V |

| 91.55µs        | 183.1µs                | 1/1           | Crystal                                | 32.768kHz             | 4.5V to 5.5V |

| 183.1µs        | 366.2µs                | 1/2           | Crystal                                | 32.768kHz             | 4.5V to 5.5V |

#### **■**Ports

• Input / Output Ports : 4 ports (23 terminals)

Data direction programmable in nibble units : 1 port (8 terminals)

(If the N-ch open drain output is selected by option, the corresponding port data can be read in output mode.)

Data direction programmable for each bit individually: 3 ports (15 terminals)

#### ■AD Converter

• 4 channels×6-bit AD converters

#### ■Serial Interfaces

• IIC-bus compliant serial interface (Multi-master type)

Consists of a single built-in circuit with two I/O channels. The two data lines and two clock lines can be connected internally.

#### ■PWM Output

• 3 channels×7-bit PWM

#### **■**Timer

• Timer 0 : 16-bit timer/counter

With 2-bit prescaler + 8-bit programmable prescaler

Mode 0: Two 8-bit timers with a programmable prescaler

Mode 1: 8-bit timer with a programmable prescaler + 8-bit counter

Mode 2: 16-bit timer with a programmable prescaler

Mode 3: 16-bit counter

The resolution of timer is 1 tCYC.

• Base Timer

Generate every 500ms overflow for a clock application

(using 32.768kHz crystal oscillation for the base timer clock)

Generate every 976µs, 3.9ms, 15.6ms, 62.5ms overflow

(using 32.768kHz crystal oscillation for the base timer clock)

Clock for the base timer is selectable from 32.768kHz crystal oscillation, system clock or programmable prescaler output of Timer 0

- ■Remote Control Receiver Circuit (connected to the P73/INT3/T0IN terminal)

- Noise rejection function

- Polarity switching

### ■Watchdog Timer

External RC circuit is required

Interrupt or system reset is activated when the timer overflows

#### ■ROM Correction Function

Max 128 bytes / 2 addresses

#### **■**Interrupts

- 12 sources 8 vectored interrupts

- 1. External Interrupt INTO

- 2. External Interrupt INT1

- 3. External Interrupt INT2, Timer/counter T0L (Lower 8 bits)

- 4. External Interrupt INT3, base timer

- 5. Timer/counter T0H (Upper 8 bits)

- 6. Data slicer

- 7. Vertical synchronous signal interrupt  $(\overline{VS})$ , horizontal line  $(\overline{HS})$

- 8. IIC, Software

- Interrupt Priority Control

Three interrupt priorities are supported (low, high and highest) and multi-level nesting is possible. Low or high priority can be assigned to the interrupts from 3 to 8 listed above. For the external interrupt INTO and INT1, low or highest priority can be set.

#### ■Sub-routine Stack Level

• A maximum of 128 levels (stack is built in the internal RAM)

### ■Multiplication/Division Instruction

- 16 bits×8 bits (7 instruction cycle times)

- 16 bits÷8 bits (7 instruction cycle times)

#### ■3 Oscillation Circuits

- Built-in RC oscillation circuit used for the system clock

- Built-in VCO circuit used for the system clock and OSD

- X'tal oscillation circuit used for base timer, system clock and PLL reference

### ■Standby Function

• HALT mode

The HALT mode is used to reduce the power dissipation. In this operation mode, the program execution is stopped. This mode can be released by the interrupt request or the system reset.

• HOLD mode

The HOLD mode is used to stop the oscillations; RC (internal), VCO, and X'tal oscillations. This mode can be released by the following conditions.

- Pull the reset terminal (RES) to low level.

- Feed the selected level to either P70/INT0 or P71/INT1.

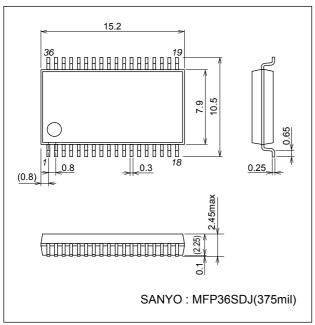

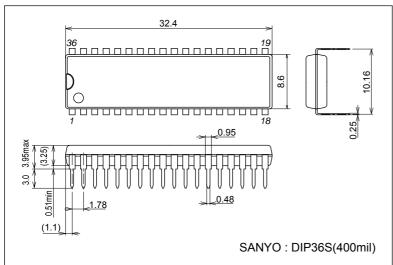

#### **■**Package

- MFP36SDJ (Lead-free type)

- DIP36S (Lead-free type)

#### **■**Development Tools

Flash EEPROM: LC86F3448AEvaluation chip: LC863096

• Emulator: EVA86000 (main) + ECB863200A (evaluation chip board)

+ SUB863400A (sub board) + POD36-CABLE (cable) + POD36-DIP (for DIP36S) or POD36-MFP (for MFP36SDJ)

### **Package Dimensions**

unit: mm (typ)

3263

### **Package Dimensions**

unit: mm (typ)

3170A

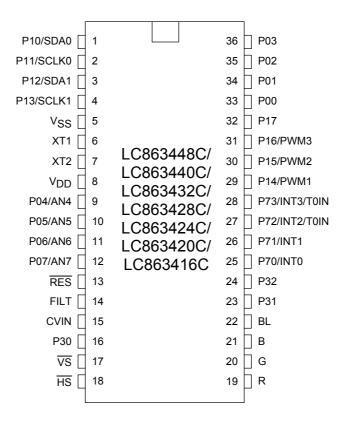

### **Pin Assignment**

Top view

SANYO: MFP36SDJ "Lead-free Type" SANYO: DIP36S "Lead-free Type"

### **System Block Diagram**

### **Pin Description**

Pin Description Table

| Terminal        | 1/0 | Function Description                                                                                          | Option                      |

|-----------------|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------|

| V <sub>SS</sub> | -   | Negative power supply                                                                                         |                             |

| XT1             | 1   | Input terminal for crystal oscillator                                                                         |                             |

| XT2             | 0   | Output terminal for crystal oscillator                                                                        |                             |

| V <sub>DD</sub> | -   | Positive power supply                                                                                         |                             |

| RES             | 1   | Reset terminal                                                                                                |                             |

| FILT            | 0   | Filter terminal for PLL                                                                                       |                             |

| CVIN            | 1   | Video signal input terminal                                                                                   |                             |

| VS              | 1   | Vertical synchronization signal input terminal                                                                |                             |

| HS              | 1   | Horizontal synchronization signal input terminal                                                              |                             |

| R               | 0   | Red (R) output terminal of RGB image output                                                                   |                             |

| G               | 0   | Green (G) output terminal of RGB image output                                                                 |                             |

| В               | 0   | Blue (B) output terminal of RGB image output                                                                  |                             |

| BL              | 0   | Fast blanking control signal                                                                                  |                             |

|                 |     | Switch TV image signal and caption/OSD image signal                                                           |                             |

| Port 0          | I/O | •8-bit input/output port,                                                                                     | Pull-up resistor            |

| P00 to P07      |     | Input/output can be specified in nibble unit                                                                  | provided/not provided       |

|                 |     | (If the N-ch open drain output is selected by option, the corresponding port dat can be read in output mode.) | a Output Format CMOS/Nch-OD |

|                 |     | •Other functions                                                                                              | OWCOMEN OB                  |

|                 |     | AD converter input port (P04 to P07: 4 channels)                                                              |                             |

| Port 1          | I/O | •8-bit input/output port                                                                                      | Output Format               |

| P10 to P17      |     | Input/output can be specified for each bit                                                                    | CMOS/Nch-OD                 |

|                 |     | (programmable pull-up resister provided)  •Other functions                                                    |                             |

|                 |     | P10 IIC0 data I/O                                                                                             |                             |

|                 |     | P11 IIC0 clock output                                                                                         |                             |

|                 |     | P12 IIC1 data I/O                                                                                             |                             |

|                 |     | P13 IIC1 clock output                                                                                         |                             |

|                 |     | P14 PWM1 output                                                                                               |                             |

|                 |     | P15 PWM2 output P16 PWM3 output                                                                               |                             |

|                 |     | 1 10   1 vvivis output                                                                                        |                             |

| Port 3          | I/O | •3-bit input/output port                                                                                      |                             |

| P30 to P32      | 1   | Input/output can be specified for each bit                                                                    |                             |

|                 |     | (CMOS output/input with programmable pull-up resister)                                                        |                             |

| Port 7          | I/O | •4-bit input/output port                                                                                      |                             |

| P70             |     | Input or output can be specified for each bit P70: I/O with programmable pull-up resister                     |                             |

| P71 to P73      |     | P71 to P73: CMOS output/input with programmable pull-up resister                                              |                             |

|                 |     | •Other functions                                                                                              |                             |

|                 |     | P70 INT0 input/HOLD release input/                                                                            |                             |

|                 |     | Nch-Tr. output for watchdog timer                                                                             |                             |

|                 |     | P71 INT1 input/HOLD release input P72 INT2 input/Timer 0 event input                                          |                             |

|                 |     | P73 INT3 input (noise rejection filter connected)/                                                            |                             |

|                 |     | Timer 0 event input                                                                                           |                             |

|                 |     | Interrupt receiver format, vector addresses                                                                   |                             |

|                 |     | Rising Falling Rising/ H level L level Vector                                                                 |                             |

|                 |     | INTO enable enable disable enable enable 03H                                                                  |                             |

|                 |     | INT1 enable enable disable enable enable OBH                                                                  |                             |

|                 |     | INT2 enable enable enable disable disable 13H                                                                 |                             |

|                 |     | INT3 enable enable enable disable disable 1BH                                                                 |                             |

|                 |     |                                                                                                               |                             |

Note: A capacitor of at least 10µF must be inserted between VDD and VSS when using this IC.

- Output form and existence of pull-up resistor for all ports can be specified for each bit.

- Programmable pull-up resistor is always connected regardless of port option, CMOS or N-ch open drain output in port 1.

### • Port status in reset

| Terminal | I/O | Pull-up resistor status at selecting CMOS output option |

|----------|-----|---------------------------------------------------------|

| Port 0   | 1   | Pull-up resistor OFF, ON after reset release            |

| Port 1   | I   | Programmable pull-up resistor OFF                       |

**Absolute Maximum Ratings** at  $Ta = 25^{\circ}C$ , VSS = 0V

| Dave                      |                | Command and         | Dina              | O an dition a               |                     |      | Ratings | 3                    |      |

|---------------------------|----------------|---------------------|-------------------|-----------------------------|---------------------|------|---------|----------------------|------|

| Para                      | ameter         | Symbol              | Pins              | Conditions                  | V <sub>DD</sub> [V] | min  | typ     | max                  | unit |

| Maximum voltage           | supply         | V <sub>DD</sub> max | V <sub>DD</sub>   |                             |                     | -0.3 |         | +6.5                 |      |

| Input volta               | age            | V <sub>I</sub> (1)  | RES, HS, VS, CVIN |                             |                     | -0.3 |         | V <sub>DD</sub> +0.3 | V    |

| Output vo                 | ltage          | V <sub>O</sub> (1)  | R, G, B, BL, FILT |                             |                     | -0.3 |         | V <sub>DD</sub> +0.3 |      |

| Input/outp                | out voltage    | V <sub>IO</sub>     | Ports 0, 1, 3, 7  |                             |                     | -0.3 |         | V <sub>DD</sub> +0.3 | İ    |

| High<br>level             | Peak<br>output | IOPH(1)             | Ports 0, 1, 3, 7  | •CMOS output •For each pin. |                     | -4   |         |                      |      |

| output<br>current         | current        | IOPH(2)             | R, G, B, BL       | •CMOS output •For each pin. |                     | -5   |         |                      |      |

|                           | Total          | ΣΙΟΑΗ(1)            | Ports 0, 1        | Total of all pins.          |                     | -20  |         |                      |      |

|                           | output         | ΣΙΟΑΗ(2)            | Ports 3, 7        | Total of all pins.          |                     | -10  |         |                      |      |

|                           | current        | ΣΙΟΑΗ(3)            | R, G, B, BL       | Total of all pins.          |                     | -12  |         |                      | mA   |

| Low                       | Peak           | IOPL(1)             | Ports 0, 1, 3     | For each pin.               |                     |      |         | 20                   |      |

| level                     | output         | IOPL(2)             | Port 7            | For each pin.               |                     |      |         | 15                   |      |

| output                    | current        | IOPL(3)             | R, G, B, BL       | For each pin.               |                     |      |         | 5                    |      |

| current                   | Total          | ΣIOAL(1)            | Ports 0, 1        | Total of all pins.          |                     |      |         | 40                   |      |

|                           | output         | ΣIOAL(2)            | Ports 3, 7        | Total of all pins.          |                     |      |         | 20                   |      |

|                           | current        | ΣIOAL(3)            | R, G, B, BL       | Total of all pins.          |                     |      |         | 12                   |      |

| Maximum                   | power          | Pd max              | MFP36SDJ          | Ta=-10 to +70°C             |                     |      |         | 360                  |      |

| dissipation               | n              |                     | DIP36S            | 1                           |                     |      |         | 610                  | mW   |

| Operating temperaturange  |                | Topr                |                   |                             |                     | -10  |         | +70                  | °C   |

| Storage<br>temperaturange | ıre            | Tstg                |                   |                             |                     | -55  |         | +125                 |      |

# Recommended Operating Range at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

|                             |                     |                                                                                     |                                                    |                     |                      | Ratings |                     |       |

|-----------------------------|---------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|---------------------|----------------------|---------|---------------------|-------|

| Parameter                   | Symbol              | Pins                                                                                | Conditions                                         | V <sub>DD</sub> [V] | min                  | typ     | max                 | unit  |

| Operating                   | V <sub>DD</sub> (1) | V <sub>DD</sub>                                                                     | 0.844μs ≤ tCYC ≤ 0.852μs                           |                     | 4.5                  |         | 5.5                 |       |

| supply voltage range        | V <sub>DD</sub> (2) |                                                                                     | 4μs ≤ tCYC ≤ 400μs                                 |                     | 4.5                  |         | 5.5                 |       |

| Hold voltage                | VHD                 | V <sub>DD</sub>                                                                     | RAMs and the registers data are kept in HOLD mode. |                     | 2.0                  |         | 5.5                 |       |

| High level input            | V <sub>IH</sub> (1) | Port 0                                                                              | Output disable                                     | 4.5 to 5.5          | 0.6V <sub>DD</sub>   |         | $V_{DD}$            |       |

| voltage                     | V <sub>IH</sub> (2) | Ports 1, 3 (Schumitt) Port 7 (Schumitt) port input/interrupt HS, VS, RES (Schumitt) | Output disable                                     | 4.5 to 5.5          | 0.75V <sub>DD</sub>  |         | V <sub>DD</sub>     | V     |

|                             | V <sub>IH</sub> (3) | Port 70 Watchdog timer input                                                        | Output disable                                     | 4.5 to 5.5          | V <sub>DD</sub> -0.5 |         | V <sub>DD</sub>     |       |

| Low level input             | V <sub>IL</sub> (1) | Port 0                                                                              | Output disable                                     | 4.5 to 5.5          | V <sub>SS</sub>      |         | 0.2V <sub>DD</sub>  |       |

| voltage                     | V <sub>IL</sub> (2) | Ports 1, 3 (Schumitt) Port 7 (Schumitt) port input/interrupt HS, VS, RES (Schumitt) | Output disable                                     | 4.5 to 5.5          | V <sub>SS</sub>      |         | 0.25V <sub>DD</sub> |       |

|                             | V <sub>IL</sub> (3) | Port 70 Watchdog timer input                                                        | Output disable                                     | 4.5 to 5.5          | V <sub>SS</sub>      |         | 0.6V <sub>DD</sub>  |       |

| CVIN                        | VCVIN               | CVIN                                                                                |                                                    | 5.0                 | 0.7Vp-p              | 1Vp-p   | 1.4Vp-p             | Vp-p* |

| Operation cycle time        | tCYC(1)             |                                                                                     | •All functions operating                           | 4.5 to 5.5          | 0.844                | 0.848   | 0.852               |       |

|                             | tCYC(2)             |                                                                                     | OSD and Data     slicer are not     operating      | 4.5 to 5.5          | 0.844                |         | 400                 | μs    |

| Oscillation frequency range | FmRC                |                                                                                     | Internal RC oscillation                            | 4.5 to 5.5          | 0.4                  | 0.8     | 3.0                 | MHz   |

<sup>\*</sup> Vp-p: Peak-to-peak voltage

# Electrical Characteristics at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

| Parameter                                                                | Symbol              | Pins                                    | Conditions                                                                                    |                     |                      | Ratings            |     | unit |

|--------------------------------------------------------------------------|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------|-----|------|

| Farameter                                                                | Symbol              | FIIIS                                   | Conditions                                                                                    | V <sub>DD</sub> [V] | min                  | typ                | max | unit |

| High level input current                                                 | l <sub>IH</sub> (1) | Ports 0, 1, 3, 7                        | Output disable Pull-up MOS Tr. OFF VIN=VDD (including the off-leak current of the output Tr.) | 4.5 to 5.5          |                      |                    | 1   |      |

|                                                                          | I <sub>IH</sub> (2) | • RES<br>• HS , VS                      | •V <sub>IN</sub> =V <sub>DD</sub>                                                             | 4.5 to 5.5          |                      |                    | 1   |      |

| Low level input current                                                  | I <sub>IL</sub> (1) | Ports 0, 1, 3, 7                        | Output disable Pull-up MOS Tr. OFF VIN=VSS (including the off-leak current of the output Tr.) | 4.5 to 5.5          | -1                   |                    |     | μΑ   |

|                                                                          | I <sub>IL</sub> (2) | • RES<br>• HS , VS                      | V <sub>IN</sub> =V <sub>SS</sub>                                                              | 4.5 to 5.5          | -1                   |                    |     |      |

| High level output voltage                                                | V <sub>OH</sub> (1) | •CMOS output of ports 0, 1, 3, 71 to 73 | I <sub>OH</sub> =-1.0mA                                                                       | 4.5 to 5.5          | V <sub>DD</sub> -1   |                    |     |      |

|                                                                          | V <sub>OH</sub> (2) | R, G, B, BL                             | I <sub>OH</sub> =-0.1mA<br>R. G. B: digital mode                                              | 4.5 to 5.5          | V <sub>DD</sub> -0.5 |                    |     |      |

| Low level output                                                         | V <sub>OL</sub> (1) | Ports 0, 1, 3, 71 to 73                 | I <sub>OL</sub> =10mA                                                                         | 4.5 to 5.5          |                      |                    | 1.5 | V    |

| voltage                                                                  | V <sub>OL</sub> (2) | Ports 0, 3, 71 to 73                    | I <sub>OL</sub> =1.6mA                                                                        | 4.5 to 5.5          |                      |                    | 0.4 |      |

|                                                                          | V <sub>OL</sub> (3) | •R, G, B, BL<br>•Port 1                 | I <sub>OL</sub> =3.0mA<br>R. G. B: digital mode                                               | 4.5 to 5.5          |                      |                    | 0.4 |      |

|                                                                          | V <sub>OL</sub> (4) | Port 70                                 | I <sub>OL</sub> =1mA                                                                          | 4.5 to 5.5          |                      |                    | 0.4 |      |

| Pull-up MOS<br>Tr. resistance                                            | Rpu                 | Ports 0, 1, 3, 7                        | V <sub>OH</sub> =0.9V <sub>DD</sub>                                                           | 4.5 to 5.5          | 13                   | 38                 | 80  | kΩ   |

| Bus terminal<br>short circuit<br>resistance<br>(SCL0-SCL1,<br>SDA0-SDA1) | RBS                 | •P10 to P12<br>•P11 to P13              |                                                                                               | 4.5 to 5.5          |                      | 130                | 300 | Ω    |

| Hysteresis voltage                                                       | VHYS                | •Ports 1, 3, 7<br>• RES<br>• HS , √S    | Output disable                                                                                | 4.5 to 5.5          |                      | 0.1V <sub>DD</sub> |     | ٧    |

| Input clump<br>voltage                                                   | VCLMP               | CVIN                                    |                                                                                               | 5.0                 | 2.3                  | 2.5                | 2.7 |      |

| Pin capacitance                                                          | СР                  | All pins                                | •f=1MHz •Every other terminals are connected to V <sub>SS</sub> . •Ta=25°C                    | 4.5 to 5.5          |                      | 10                 |     | pF   |

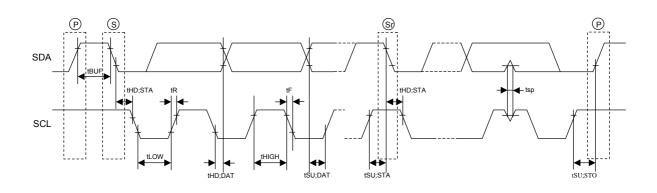

### **IIC Input/Output Conditions** at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

| Parameter                             | Cumbal  | Stan | ıdard | High     | speed | unit |

|---------------------------------------|---------|------|-------|----------|-------|------|

| Parameter                             | Symbol  | min  | max   | min      | max   | unit |

| SCL Frequency                         | fSCL    | 0    | 100   | 0        | 400   | kHz  |

| BUS free time between stop - start    | tBUF    | 4.7  | -     | 1.3      | -     | μs   |

| HOLD time of start, restart condition | tHD;STA | 4.0  | -     | 0.6      | -     | μs   |

| L time of SCL                         | tLOW    | 4.7  | -     | 1.3      | -     | μs   |

| H time of SCL                         | tHIGH   | 4.0  | -     | 0.6      | -     | μs   |

| Set-up time of restart condition      | tSU;STA | 4.7  | -     | 0.6      | -     | μs   |

| HOLD time of SDA                      | tHD;DAT | 0    | -     | 0        | 0.9   | μs   |

| Set-up time of SDA                    | tSU;DAT | 250  | -     | 100      | -     | ns   |

| Rising time of SDA, SCL               | tR      | -    | 1000  | 20+0.1Cb | 300   | ns   |

| Falling time of SDA, SCL              | tF      | -    | 300   | 20+0.1Cb | 300   | ns   |

| Set-up time of stop condition         | tSU;STO | 4.0  | -     | 0.6      | -     | μs   |

Refer to figure 8

Note 1: Cb: Total capacitance of all BUS (unit : pF)

### Pulse Input Conditions at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

| Parameter      | Cumbal  | Dine                                           | Conditions                     |                     |     | Ratings |     | umit |

|----------------|---------|------------------------------------------------|--------------------------------|---------------------|-----|---------|-----|------|

| Parameter      | Symbol  | Pins                                           | Conditions                     | V <sub>DD</sub> [V] | min | typ     | max | unit |

| High/low level | tPIH(1) | •INT0, INT1                                    | •Interrupt acceptable          | 4.5 to 5.5          | 1   |         |     |      |

| pulse width    | tPIL(1) | •INT2/T0IN                                     | •Timer0-countable              | 4.5 (0 5.5          | '   |         |     |      |

|                | tPIH(2) | INT3/T0IN                                      | •Interrupt acceptable          |                     |     |         |     |      |

|                | tPIL(2) | (1tCYC is selected for noise rejection clock.) | •Timer0-countable              | 4.5 to 5.5          | 2   |         |     |      |

|                | tPIH(3) | INT3/T0IN                                      | •Interrupt acceptable          |                     |     |         |     | tCYC |

|                | tPIL(3) | (16tCYC is selected for                        | •Timer0-countable              | 4.5 to 5.5          | 32  |         |     |      |

|                |         | noise rejection clock.)                        |                                |                     |     |         |     |      |

|                | tPIH(4) | INT3/T0IN                                      | •Interrupt acceptable          |                     |     |         |     |      |

|                | tPIL(4) | (64tCYC is selected for                        | •Timer0-countable              | 4.5 to 5.5          | 128 |         |     |      |

|                |         | noise rejection clock.)                        |                                |                     |     |         |     |      |

|                | tPIL(5) | RES                                            | Reset acceptable               | 4.5 to 5.5          | 200 |         |     |      |

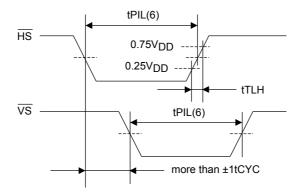

|                | tPIH(6) | HS, VS                                         | •Display position controllable |                     |     |         |     |      |

|                | tPIL(6) |                                                | •The active edge of            |                     |     |         |     | μs   |

|                |         |                                                | HS and VS must be apart        | 4.5 to 5.5          | 3   |         |     | μο   |

|                |         |                                                | at least 1tCYC.                |                     |     |         |     |      |

|                |         |                                                | •Refer to figure 4.            |                     |     |         |     |      |

| Rising/falling | tTHL    | HS                                             | Refer to figure 4.             | 4.5 to 5.5          |     |         | 500 | ns   |

| time           | tTLH    |                                                |                                | 4.5 (0 5.5          |     |         | 300 | 115  |

### **AD Converter Characteristics** at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

| Danamatan                  | O. made at | Diag                                | O andiki ana                 |                     | Ratings         |      |                 | unit |

|----------------------------|------------|-------------------------------------|------------------------------|---------------------|-----------------|------|-----------------|------|

| Parameter                  | Symbol     | Pins                                | Conditions                   | V <sub>DD</sub> [V] | min             | typ  | max             | unit |

| Resolution                 | N          |                                     |                              |                     |                 | 6    |                 | bit  |

| Absolute precision         | ET         |                                     | (Note 2)                     |                     |                 |      | ±1              | LSB  |

| Conversion time            | tCAD       | Vref selection to conversion finish | 1 bit conversion time=2×Tcyc | 4.5 to 5.5          |                 | 1.69 |                 | μs   |

| Analog input voltage range | VAIN       | AN4 to AN7                          |                              |                     | V <sub>SS</sub> |      | V <sub>DD</sub> | V    |

| Analog port                | IAINH      |                                     | VAIN=V <sub>DD</sub>         |                     |                 |      | 1               |      |

| input current              | IAINL      |                                     | VAIN=V <sub>SS</sub>         |                     | -1              |      |                 | μА   |

Note 2: Absolute precision does not include quantizing error (1/2LSB).

Analog Mode RGB Characteristics at  $Ta = -10^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{SS} = 0V$

| Darameter     | Cymhal | Complete Direct Complete Compl |                  |                     | Ratings |      |      |      |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|---------|------|------|------|

| Parameter     | Symbol | Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Conditions       | V <sub>DD</sub> [V] | min.    | typ. | max. | unit |

| Analog output |        | R.G.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Low level output |                     | 0.45    | 0.5  | 0.55 |      |

| voltage       |        | Analog<br>output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Intensity output |                     | 0.90    | 1.0  | 1.10 | ٧    |

|               |        | mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Hi level output  | 5.0                 | 1.35    | 1.5  | 1.65 |      |

| Time setting  |        | R.G.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70%              |                     |         |      | 50   | ns   |

|               |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10pf load        |                     |         |      | 30   | 113  |

### Sample Current Dissipation Characteristics at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$

The sample current dissipation characteristics is the measurement result of Sanyo provided evaluation board when the recommended circuit parameters shown in the sample oscillation circuit characteristics are used externally.

The currents through the output transistors and the pull-up MOS transistors are ignored.

| Parameter                                                    | Symbol     | Pins            | Conditions                                                                                                                                                                             |                     |     | Ratings |      | unit  |

|--------------------------------------------------------------|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------|------|-------|

| Parameter                                                    | Symbol     | PINS            | Conditions                                                                                                                                                                             | V <sub>DD</sub> [V] | min | typ     | max  | uriit |

| Current dissipation<br>during basic<br>operation<br>(Note 3) | IDDOP(1)   | V <sub>DD</sub> | *FmX'tal=32.768kHz     X'tal oscillation     *System clock : VCO     *VCO for OSD operating     OSD is Digital mode     Internal RC oscillation stops                                  | 4.5 to 5.5          |     | 11      | 25   | mA    |

|                                                              | IDDOP(2)   | V <sub>DD</sub> | FmX'tal=32.768kHz X'tal scillation     System clock : VCO     VCO for OSD operating     OSD is Analog mode     Internal RC oscillation stops                                           | 4.5 to 5.5          |     | 20      | 35   |       |

|                                                              | IDDOP(3)   | V <sub>DD</sub> | •FmX'tal=32.768kHz X'tal scillation •System clock : X'tal (Instruction cycle time: 366.2µs) •VCO for system VCO for OSD, internal RC oscillation stop •Data slicer, AD converters stop | 4.5 to 5.5          |     | 65      | 300  | μΑ    |

| Current dissipation<br>in HALT mode<br>(Note 3)              | IDDHALT(1) | V <sub>DD</sub> | •HALT mode •FmX'tal=32.768kHz X'tal oscillation •System clock : VCO •VCO for OSD stops •Internal RC oscillation stops                                                                  | 4.5 to 5.5          |     | 3       | 9    | mA    |

|                                                              | IDDHALT(2) | V <sub>DD</sub> | HALT mode FmX'tal=32.768kHz X'tal oscillation VCO for system stops VCO for OSD stops System clock: Internal RC                                                                         | 4.5 to 5.5          |     | 300     | 1000 |       |

|                                                              | IDDHALT(3) | V <sub>DD</sub> | •HALT mode •FmX'tal=32.768kHz X'tal oscillation •VCO for system stops •VCO for OSD stops •System clock : X'tal (Instruction cycle time: 366.2μs)                                       | 4.5 to 5.5          |     | 57      | 200  | μΑ    |

| Current dissipation in HOLD mode (Note 3)                    | IDDHOLD    | V <sub>DD</sub> | •HOLD mode •All oscillation stops.                                                                                                                                                     | 4.5 to 5.5          |     | 0.05    | 20   | μΑ    |

Note 3: The currents through the output transistors and the pull-up MOS transistors are ignored.

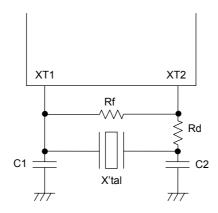

### **Recommended Oscillation Circuit and Sample Characteristics**

The sample oscillation circuit characteristics in the table below is based on the following conditions:

Recommended circuit parameters are verified by an oscillator manufacturer using a Sanyo provided oscillation evaluation board.

Sample characteristics are the result of the evaluation with the recommended circuit parameters connected externally.

Recommended oscillation circuit and sample characteristics ( $Ta = -10^{\circ}C$  to  $+70^{\circ}C$ )

| Fraguenav | Manufacturer   | Ossillator | Red  | commended | circuit param | eters |                  |      | llation<br>ing time | Notes |

|-----------|----------------|------------|------|-----------|---------------|-------|------------------|------|---------------------|-------|

| Frequency | Manufacturer   | Oscillator | C1   | C2        | Rf            | Rd    | voltage<br>range | typ  | max                 | Notes |

| 32.768kHz | SEIKO<br>EPSON | C-002RX    | 18pF | 18pF      | OPEN          | 390kΩ | 4.5 to 5.5V      | 1.0s | 1.5s                |       |

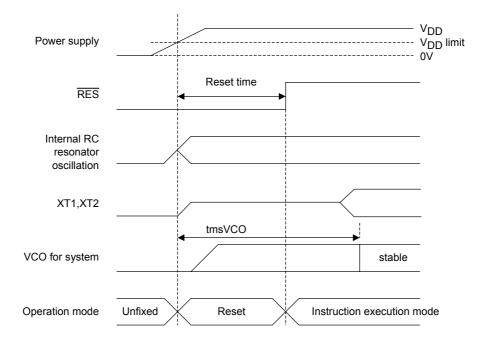

Notes: The oscillation stabilizing time period is the time until the VCO oscillation for the internal system becomes stable after the following conditions. (Refer to Figure 2.)

- 1. The V<sub>DD</sub> becomes higher than the minimum operating voltage after the power is supplied.

- 2. The HOLD mode is released.

The sample oscillation circuit characteristics may differ applications. For further assistance, please contact with oscillator manufacturer with the following notes in your mind.

- Since the oscillation frequency precision is affected by wiring capacity of the application board, etc., adjust the oscillation frequency on the production board.

- The above oscillation frequency and the operating supply voltage range are based on the operating temperature of -10°C to +70°C. For the use with the temperature outside of the range herein, or in the applications requiring high reliability such as car products, please consult with oscillator manufacturer.

- When using the oscillator which is not shown in the sample oscillation circuit characteristics, please consult with Sanyo sales personnel.

Since the oscillation circuit characteristics are affected by the noise or wiring capacity because the circuit is designed with low gain in order to reduce the power dissipation, refer to the following notices.

- The distance between the clock I/O terminal (XT1 terminal XT2 terminal) and external parts should be as short as possible.

- The capacitors' VSS should be allocated close to the microcontroller's GND terminal and be away from other GND.

- The signal lines with rapid state changes or with large current should be allocated away from the oscillation circuit.

Figure 1 Recommended Oscillation Circuit

Reset Time and Oscillation Stabilizing Time

HOLD Release Signal and Oscillation Stabilizing Time

Figure 2 Oscillation Stabilizing Time

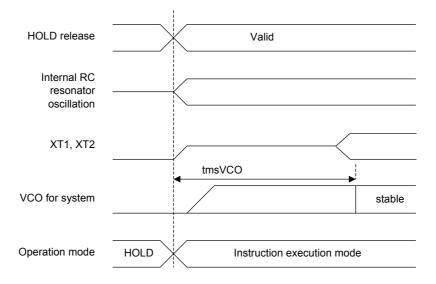

Figure 3 Pulse Input Timing Condition - 1

Figure 4 Pulse Input Timing Condition - 2

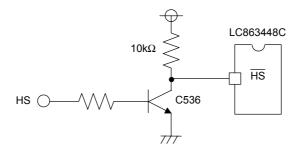

Figure 5 Recommended Interface Circuit

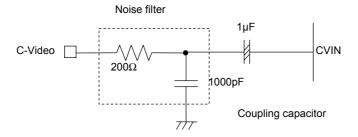

Output impedance of C-Video before Noise filter should be less then  $100\Omega$ .

Figure 6 CVIN Recommended Circuit

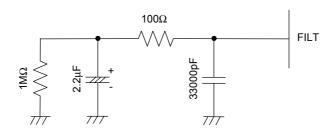

Figure 7 FILT Recommended Circuit Note: Place FILT parts on board as close to the microcontroller as possible.

$S: start\ condition \\ P: stop\ condition \\ Standard\ mode: not\ exist \\ High\ speed\ mode: less\ than\ 50ns$

Sr: restart condition

Figure 8 IIC Timing

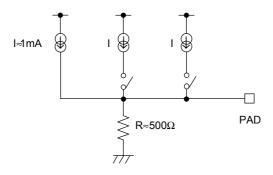

Figure 9 R.G.B. Analog Output Equivalent Circuit

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 2006. Specifications and information herein are subject to change without notice.