# High Voltage Multi-Mode PWM Controller with BNO Function

**REV: 00**

#### **General Description**

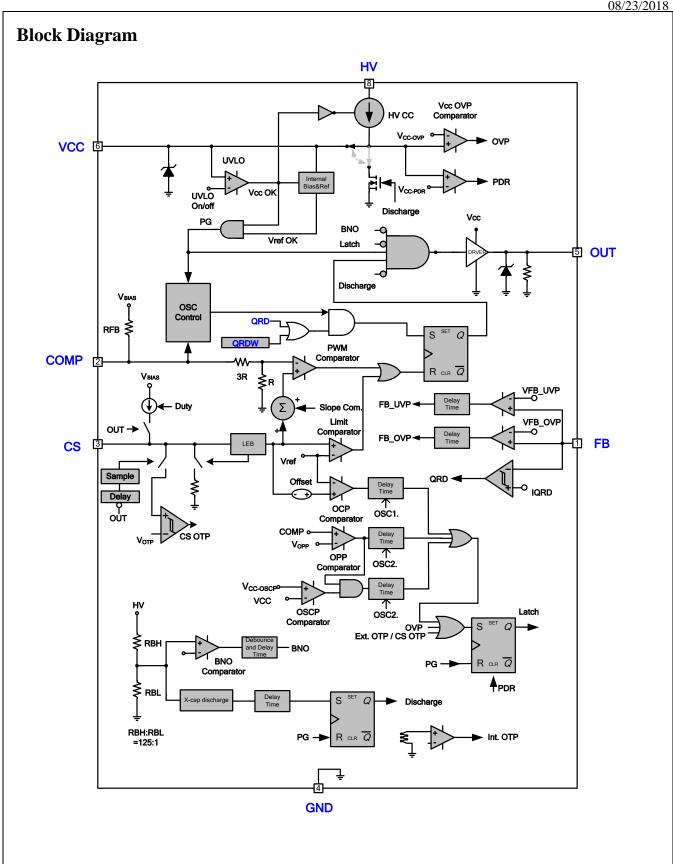

The LD5762S is a green mode PWM IC built-in with brown-in/ out functions in a SOP-7 package. The device could therefore minimize the component counts, circuit space, and reduces the overall material cost of power applications.

The LD5762S features HV start, sleep-mode, green-mode power-saving operation, and internal slope compensation, Soft-start functions which could minimum the power loss and improve the system performance.

With complete protection with it, like OPP (Over Power Protection), OVP (Over Voltage Protection), OCP (Over Current protection) and brown-in/out protection, LD5762S prevents the circuit from being damaged in abnormal conditions.

Furthermore, the LD5762S features frequency swapping and soft driving function to minimize the noise and improve EMI.

#### **Features**

- Secondary-side feedback control with quasi-resonant

+ CCM operation

- High-Voltage (710V) Startup Circuit

- Built-in Brown-in/out Function on HV pin

- Built- in X-Cap Discharge on HV pin

- OVP (Over Voltage Protection) on VCC/FB

- OPP (Over Power Protection)

- OCP (Over Current Protection)

- OSCP(Output Short Circuit Protection)

- Adj. CS\_OTP (Over Temperature Protection)

- Peak Load FSW Boost

- Soft Driving

- +300mA/-800mA Driving Capability

### **Applications**

Printer

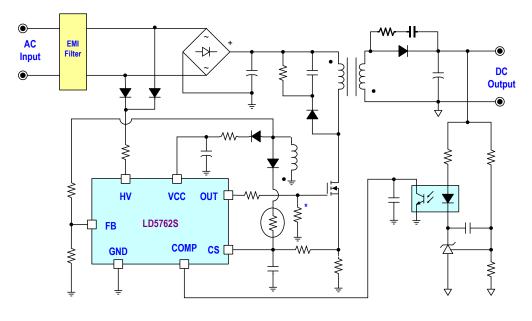

### **Typical Application**

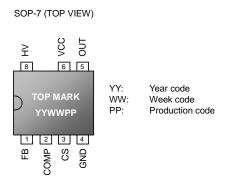

### **Pin Configuration**

### **Ordering Information**

| Part number | Package | Top Mark  | Shipping         |

|-------------|---------|-----------|------------------|

| LD5762S GR  | SOP-7   | LD5762SGR | 2500/tape & reel |

The LD5762S is RoHs compliant/ green packaged.

### **Protection Mode**

| Part number | VCC_OVP | OSCP  | CS_OTP | OPP   | FB_UVP | FB_OVP |

|-------------|---------|-------|--------|-------|--------|--------|

| LD5762S     | Latch   | Latch | Latch  | Latch | Latch  | Latch  |

### **Pin Descriptions**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FB   | Auxiliary voltage sense, output voltage protection and quasi resonant detection.                                                                                                                                                                                                                                                                                                               |

| 2   | COMP | Voltage feedback pin. Connect a photo-coupler with it to close the control loop and achieve the regulation.                                                                                                                                                                                                                                                                                    |

| 3   | cs   | Current sense pin, connect it to sense the MOSFET current                                                                                                                                                                                                                                                                                                                                      |

| 4   | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | OUT  | Gate drive output to drive the external MOSFET                                                                                                                                                                                                                                                                                                                                                 |

| 6   | VCC  | Supply voltage pin                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | NC   | Unconnected Pin                                                                                                                                                                                                                                                                                                                                                                                |

| 8   | HV   | Connect this pin to Line/ Neutral of AC main voltage through resistor to provide the startup current for the controller. When VCC voltage increase to trip the point of UVLO(on), this HV loop will be turned off to reduce the power loss on the startup circuit.  An internal resistor divider between HV to GND pin will monitor AC line voltage to activate Brown-in/out function control. |

### **Absolute Maximum Ratings**

| -0.3V~33V      |

|----------------|

| -0.3V~710V     |

| -0.3V~6V       |

| -0.3V~VCC+0.3V |

| 150°C          |

| -65°C to 150°C |

| 160°C/W        |

| 250mW          |

| 260°C          |

| 2.5KV          |

| 250V           |

| 1KV            |

| 200V           |

| +300/-800mA    |

|                |

#### Caution:

Stress exceeding maximum ratings may damage the device. Maximum ratings are stress ratings only. Functional operation above the recommended operating conditions is not implied. Extended exposure to stress above recommended operating conditions may affect device reliability.

### **Recommended Operating Conditions**

| Item                           | Min. | Max. | Unit |

|--------------------------------|------|------|------|

| Operating Junction Temperature | -40  | 125  | °C   |

| Supply VCC Voltage             | 8.5  | 26.5 | V    |

| HV resistor Value (AC Side)    | 8    | 17.5 | ΚΩ   |

| HV to GND Capacitor Value      |      | 300  | pF   |

| Comp Pin Capacitor             | 1    | 10   | nF   |

| CS Pin Capacitor Value         | 47   | 390  | pF   |

### **Electrical Characteristics**

$(T_A = +25^{\circ}C \text{ unless otherwise stated, VCC=15.0V})$

| PARAMETER                            | CONDITIONS                                             | SYMBOL                | MIN | TYP                | MAX | UNITS           |

|--------------------------------------|--------------------------------------------------------|-----------------------|-----|--------------------|-----|-----------------|

| High-Voltage Supply (HV Pin)         |                                                        |                       |     |                    |     |                 |

| High-Voltage Current Source          | VCC< UVLO <sub>(ON)</sub> ,<br>HV=500V                 | I <sub>HV</sub>       | 2   | 2.8                | 3.5 | mA              |

| HV Discharge capability HV=500V      |                                                        | I <sub>HV_DIS</sub>   | 2   | 2.5                | 3.5 | mA              |

| HV Pin Total Input Current (HV+ BNO) | HV=500 V <sub>DC</sub> ,VCC><br>UVLO <sub>(ON)</sub> , | I <sub>HV_LEAK</sub>  |     |                    | 35  | μА              |

| HV Pin Brown-In Level (HVBI)         | HV pin =half rectifier wave increase                   | $V_{HVBI}$            | 98  | 105                | 115 | V <sub>DC</sub> |

| HV Pin Brown-out<br>Level(HVBO)      | HV pin = half rectifier wave decrease                  | $V_{HVBO}$            | 78  | 88                 | 98  | V <sub>DC</sub> |

| HV Pin BNO Hysteresis                | HV <sub>BI</sub> -HV <sub>BO</sub>                     | $\DeltaV_{HV}$        | 9   | 17                 | 25  | $V_{DC}$        |

| Brown-in De-bounce Time              | V <sub>COMP</sub> =3V                                  | T <sub>D_HVBI</sub>   | 200 | 400                | 550 | μS              |

| Brown-out Detection Delay time       | V <sub>COMP</sub> =3V                                  | T <sub>D_HVBO</sub>   |     | 68                 |     | ms              |

| HV Pin Min. Operation Voltage        | VCC=15V<br>(DetVmin = VHV-VCC<br>= 30V)                | V <sub>HV_MIN</sub>   | 45  |                    |     | V               |

| X-Cap discharge Detection Delay time | V <sub>COMP</sub> =3V                                  | T <sub>D_XCAP</sub>   | 52  | 68                 | 82  | ms              |

| Supply Voltage (VCC Pin)             |                                                        |                       |     |                    |     |                 |

| Startup Current                      | VCC=15V ,HV=500V                                       | I <sub>CC_ST</sub>    |     | 25                 | 50  | μΑ              |

|                                      | V <sub>COMP</sub> =3V                                  | I <sub>CC_OP1</sub>   |     | 2                  |     | mA              |

| Operating Current                    | V <sub>COMP</sub> =0V                                  | I <sub>CC_OP2</sub>   |     | 0.33               |     | mA              |

| (with 1nF load on OUT pin)           | Latch mode                                             | I <sub>CC_OPL</sub>   |     | 0.43               |     | mA              |

|                                      | Auto mode                                              | I <sub>CC_OPR</sub>   |     | 0.28               |     | mA              |

| UVLO <sub>(OFF)</sub>                |                                                        | VCC_OFF               | 5.5 | 6                  | 6.5 | V               |

| UVLO <sub>(ON)</sub>                 |                                                        | VCC_on                | 15  | 16                 | 17  | V               |

| PDR                                  | *                                                      | VCC_ <sub>PDR</sub>   |     | UVLO<br>(OFF)-1.1V |     | V               |

| VCC HVBI Level HV>HVBI (Fig 1.)      |                                                        | VCC_ <sub>HVBI</sub>  |     | UVLO<br>(OFF)+4V   |     | V               |

| VCC OVP Level                        |                                                        | VCC_OVP               | 31  | 32                 | 33  | V               |

| VCC OVP De-bounce Time               | V <sub>COMP</sub> =3V                                  | T <sub>D_VCCOVP</sub> |     | 120                |     | μS              |

| PARAMETER                                  | CONDITIONS                              | SYMBOL                 | MIN  | TYP                        | MAX  | UNITS |

|--------------------------------------------|-----------------------------------------|------------------------|------|----------------------------|------|-------|

| Oscillator for Switching Frequ             | ency                                    |                        |      |                            |      |       |

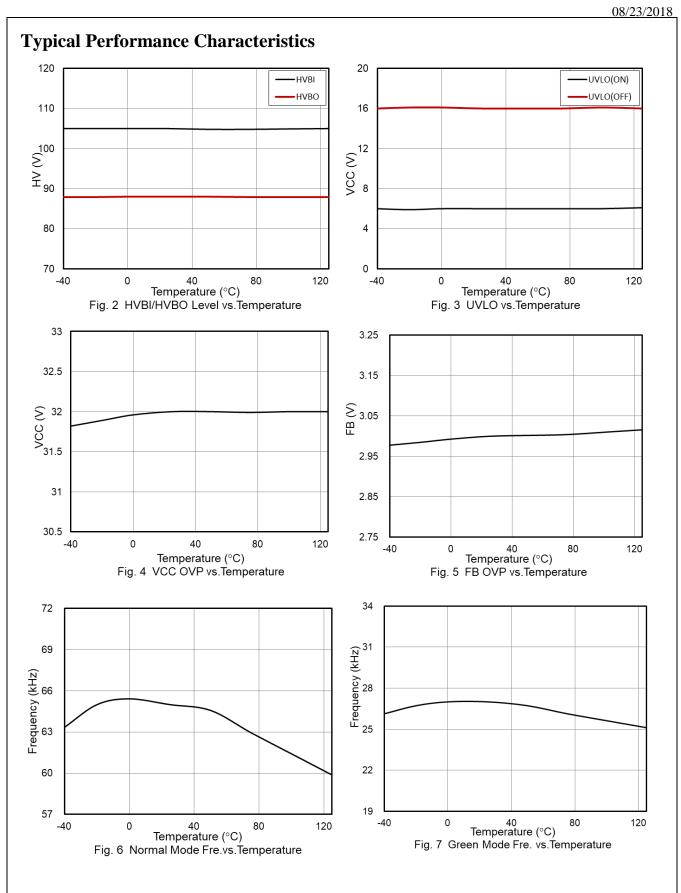

|                                            | V <sub>COMP</sub> =3V                   | F <sub>SW_N</sub>      | 61   | 65                         | 69   | KHz   |

| Frequency                                  | V <sub>COMP</sub> =4.4V<br>(VHV<250VDC) | F <sub>SW_H</sub>      | 115  | 130                        | 140  | KHz   |

| Green Mode Frequency                       | V <sub>COMP</sub> =1.3V                 | F <sub>SW_GREEN</sub>  | 22   | 25                         | 28   | KHz   |

|                                            | Frequency= 25kHz                        | F <sub>TRM1</sub>      |      | ±4                         |      | kHz   |

| Trembling Frequency                        | Frequency= 65kHz                        | F <sub>TRM2</sub>      |      | ±6                         |      | kHz   |

|                                            | Frequency=130kHz                        | F <sub>TRM3</sub>      |      | ±10                        |      | kHz   |

| Modulation Frequency                       | * Frequency= 65kHz                      | F <sub>SW_MOD</sub>    |      | 200                        |      | Hz    |

| F <sub>SW</sub> Temp. Stability            | *-40°C ~105°C                           | $F_{SW\_TS}$           | 0    | 3                          | 4    | %     |

| F <sub>SW</sub> Voltage Stability          | *VCC=8V-(OVP-1V)                        | F <sub>SW_VS</sub>     | 0    |                            | 1    | %     |

| Maximum On Time                            |                                         | DMAX                   | 78   | 83                         | 88   | %     |

| OSCP (Output Short Circuit Pr              | rotection)                              |                        |      | -                          |      |       |

| OSCP Trip Level                            |                                         | VCC_oscp               |      | UVLO <sub>OFF</sub><br>+4V |      | V     |

| OSCP Delay Time                            |                                         | T <sub>D_OSCP</sub>    |      |                            | 10   | ms    |

| Voltage Feedback (Comp Pin)                |                                         |                        |      |                            |      | •     |

| Input Voltage to Current-Sense Attenuation | *                                       | A <sub>V</sub>         |      | 1/4.0                      |      | V/V   |

| Comp Impedance                             |                                         | Z <sub>COMP</sub>      |      | 42                         |      | kΩ    |

| Open Loop Voltage                          | COMP pin open                           | V <sub>COMP_OPEN</sub> | 4.9  | 5.2                        | 5.5  | V     |

| OPP Tripped Level                          | TC: track COMP pin open voltage         | V <sub>OPP</sub>       | 4.4  | 4.6                        | 4.8  | V     |

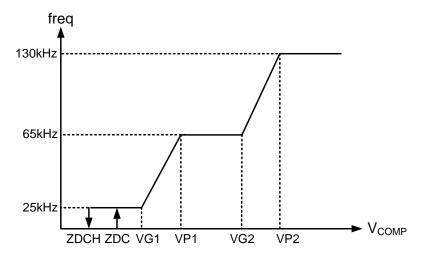

| Peak Mode Threshold VCOMP                  |                                         | $V_{P2}$               | 3.7  | 3.9                        | 4.1  | V     |

| Peak Mode Down Threshold                   | (Fig 1.)                                | $V_{G2}$               | 3.4  | 3.6                        | 3.8  | V     |

| PWM Mode Threshold<br>VCOMP                | 0.9 of F <sub>SW-N</sub> ,              | V <sub>P1</sub>        | 1.35 | 1.55                       | 1.75 | V     |

| Green Mode Threshold<br>VCOMP              | 1.1 of F <sub>SW-GREEN</sub> ,          | $V_{G1}$               | 1.1  | 1.3                        | 1.5  | V     |

| Zero Duty Threshold VCOMP                  | Zero Duty                               | $V_{ZDC}$              | 0.9  | 1                          | 1.1  | V     |

| on Burst mode                              | Hysteresis                              | $V_{ZDCH}$             |      | 110                        |      | mV    |

| PARAMETER                   | CONDITIONS               | SYMBOL                  | MIN  | TYP  | MAX   | UNITS |

|-----------------------------|--------------------------|-------------------------|------|------|-------|-------|

| Current Sensing (CS Pin)    |                          |                         |      |      |       |       |

| 1: 21/16                    | (VHV<250VDC)             | $V_{\text{CS\_MAX\_L}}$ | 0.81 | 0.85 | 0.89  | V     |

| Limit Voltage               | (VHV>250VDC)             | V <sub>CS_MAX_H</sub>   | 0.76 | 0.8  | 0.84  | V     |

| OCP Voltage                 |                          | V <sub>CS_OCP</sub>     | 0.26 | 0.28 | 0.3   | V     |

| ODD Commonation Commont     | Duty=50%                 | I <sub>OPP_50_L</sub>   | 75   | 85   | 95    | μА    |

| OPP Compensation Current    | Duty=20%                 | I <sub>OPP_20_H</sub>   | 210  | 225  | 240   | μА    |

| OCP Delay Time              |                          | T <sub>D_OCP</sub>      | 3.5  | 4.5  | 5.5   | S     |

| OCP Reset Time              |                          | T <sub>D_OCPRS</sub>    |      | 2    |       | ms    |

| Leading Edge Blanking Time  |                          | $T_LEB$                 |      | 380  |       | ns    |

| Delay to Output             |                          | $T_{PD}$                |      | 80   |       | ns    |

| Slope Compensation Level    | *                        | $V_{SLP_{L}}$           | 0    |      | 0.156 | V     |

| Slope Compensation Position | *                        | $V_{SLP}$               | 0    |      | 83    | %     |

| Gate Drive Output (OUT Pin) |                          |                         |      |      |       |       |

| Output Low Level            | VCC=15V, Io=20mA         | $V_{OL}$                | 0    |      | 1     | V     |

| Output High Level           | VCC=15V, Io=20mA         | $V_{OH}$                | 8    |      | VCC   | V     |

| Rising Time                 | Load Capacitance= 1000pF | Tr                      |      | 90   |       | ns    |

| Falling Time                | Load Capacitance= 1000pF | $T_f$                   |      | 20   |       | ns    |

| OUT Pin Clamping Voltage    | VCC= 21V,1nF on OUT pin  | V <sub>O_CLAMP</sub>    |      | 13.5 |       | V     |

| OPP (Over Power Protection) |                          |                         |      |      |       |       |

| OPP Delay Time              |                          | $T_{D\_OPP}$            | 3.5  | 4.5  | 5.5   | S     |

| OPP Reset Time              |                          | $T_{D\_OPPRS}$          |      | 2    |       | ms    |

| PARAMETER                            | CONDITIONS                               | SYMBOL                 | MIN  | TYP                  | MAX  | UNITS |

|--------------------------------------|------------------------------------------|------------------------|------|----------------------|------|-------|

| QRD (Quasi Resonant Dete             | ction, FB Pin)                           |                        |      |                      |      |       |

| UVP Trip voltage Level               |                                          | $V_{FB\_UVP}$          | 0.45 | 0.5                  | 0.55 | V     |

| De-bounce Cycle                      |                                          | T <sub>SKIP</sub>      |      | 1                    |      | Cycle |

| FB UVP De-bounce Time                |                                          | T <sub>FB_UVP</sub>    |      | 2.5                  |      | ms    |

| OVP Trip voltage Level               |                                          | $V_{FB\_OVP}$          | 2.85 | 3                    | 3.15 | V     |

| De-bounce Cycle                      |                                          | T <sub>D_FBOVP</sub>   |      | 8                    |      | Cycle |

| QRD Trip Level                       | *                                        | I <sub>QRD</sub>       |      | 20                   |      | μА    |

| QRD Delay Time                       | *                                        | T <sub>QRD</sub>       |      | 100                  |      | ns    |

| Soft Start                           |                                          |                        |      |                      |      |       |

| Soft Start Duration(1)               | After OPP, OCP, OTP, BNO, OVP is tripped | T <sub>SS1</sub>       |      | 6                    |      | ms    |

| Soft Start Duration(2)               | *Fsw=65kHz                               | T <sub>SS2</sub>       | 30   |                      |      | ms    |

| Internal OTP                         |                                          |                        |      |                      |      |       |

| OTP Tripped Level(T <sub>OTP</sub> ) | *                                        | T <sub>INOTP</sub>     |      | 140                  |      | °C    |

| OTP Hysteresis                       | *                                        | T <sub>INOTP_HYS</sub> |      | T <sub>OTP</sub> -30 |      | °C    |

| OTP De-bounce Time                   | *                                        | $T_{D\_INOTP}$         |      | 50                   |      | μS    |

| CS_OTP (Over Temperature             | Protection Protection)                   |                        |      |                      |      |       |

| OTP Trip Current Level               |                                          | V <sub>CSOTP</sub>     | 0.25 | 0.28                 | 0.31 | V     |

| VCS Discharge Time                   | *Gate On<br>(Ron=100ohm)                 | T <sub>DIS_CS</sub>    |      | LEB                  |      | ns    |

| CS OTP De-bounce Time                |                                          | T <sub>D_CSOTP</sub>   |      | 16                   |      | cycle |

<sup>\*:</sup> Guaranteed by design.

Fig. 1  $V_{\text{COMP}}$  vs. PWM Frequency

## **Application Information Operation Overview**

As long as the green power requirement becomes a trend and the power saving is getting more and more important for the switching power supplies and switching adaptors, the traditional PWM controllers are not able to support such new requirements. Furthermore, the cost and size limitation force the PWM controllers to be more powerful and with more functions to reduce the external part counts. The LD5762S is ideal for these applications. Its detailed features are described as below.

## Internal High-Voltage Startup Circuit and Under Voltage Lockout (UVLO)

The traditional circuit provides the startup current through a startup resistor to power up the PWM controller. However, it consumes much significant power to meet the current power saving requirement. In most cases, startup resistors carry larger resistance and spend more time to start up.

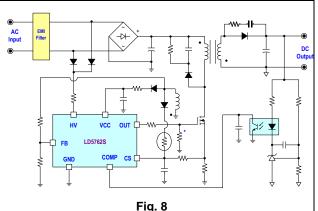

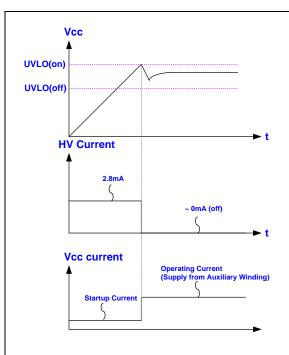

To achieve the optimized topology, as shown in Fig. 8, LD5762S is implemented with a high-voltage startup circuit for such requirement. At startup, the high-voltage current source sinks current of AC Line/or Neutral to provide startup current and charge the capacitor connected to VCC.

During the startup transient, the HV current will supply around 2.8mA to VCC capacitor until this VCC voltage reaches the UVLO threshold VCC. By using such configuration, the turn-on delay time will be almost same no matter under low-line or high-line conditions.

As VCC trips UVLO(off), HV pin will recharge VCC capacitor till VCC voltage rises back to UVLO(on) again. Since then, HV pin would no longer charge the capacitor and instead, send a gate drive signal to draw supply current for VCC from the auxiliary winding of the transformer. That minimizes the power loss on the start-up circuit successfully.

An UVLO comparator is embedded to detect the voltage across the VCC pin to ensure the supply voltage enough to power on the LD5762S and in addition, to drive the power MOSFET. As shown in Fig. 9, a hysteresis is provided to prevent shutdown from the voltage dip during startup. The turn-on and turn-off threshold level are set at 16V and 6V, respectively.

Fig. 9

#### **QR Mode Detection**

The transformer will be demagnetized after the main power MOSFET turns off. A quasi resonant signal will be detected from auxiliary winding by FB pin through the external resister.

As soon as the current of the secondary side diode is down to zero during MOSFET-off period, the transformer's core is demagnetized completely.  $V_{DS}$  of MOSFET will resonate in discontinuous current mode. The resonance frequency ( $F_{QR}$ ) will be obtained as below.

$$F_{QR} = \frac{1}{2\pi\sqrt{L_{m} \times C_{R}}} (Hz)$$

L<sub>M</sub> = Inductance of primary winding

C<sub>R</sub> = Resonance equivalent parasitic capacitance

If  $V_{DS}$  voltage falls to resonant valley level from max plateau value, the QRD comparator will be tripped while FB pin current is close to  $20\mu A$ .

#### **Brown in/out Protection**

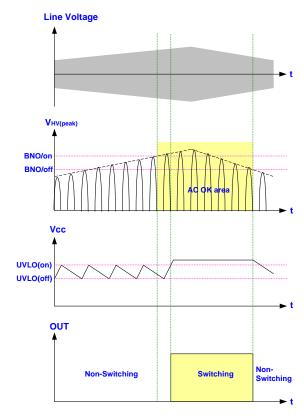

The LD5762S features Burn-in/out function on HV pin. As the built-in comparator detects the half wave rectify line voltage condition, it will shut off the controller to prevent from any damage. Fig. 10 shows the operation. When  $V_{HV} < HVBO$ , the gate output will remain off even when the VCC already reaches  $UVLO(_{ON})$ . It therefore forces the VCC hiccup between  $UVLO(_{ON})$  and  $UVLO(_{OFF})$ . Unless the line voltage rises over HVBI  $V_{AC}$ , the gate output will not start switching even as the next  $UVLO(_{ON})$  is tripped. A hysteresis is implemented to prevent the false-triggering during turn-on and turn-off.

Fig. 10

## Current Sensing, Leading-Edge Blanking and the Negative Spike on CS Pin

The typical current mode PWM controller feedbacks both current signal and voltage signal to close the control loop and achieve regulation. The LD5762S detects the primary MOSFET current across CS pin to control in peak current mode and also limit the pulse-by-pulse current. The maximum voltage threshold of the current sensing pin is 0.85V (VHV<250VDC) or 0.8V (VHV>250VDC). Thus the MOSFET peak current can be calculated as:

$$I_{PEAK(MAX)} = \frac{0.85V}{R_S} \quad (VHV < 250VDC)$$

or

$$I_{PEAK(MAX)} = \frac{0.8V}{R_S}$$

(VHV>250VDC)

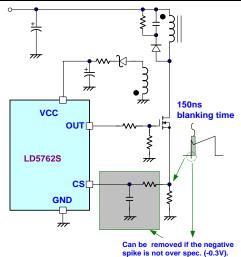

A 380ns leading-edge blanking (LEB) time is designed in the input of CS pin to prevent false-triggering from the current spike. In the low power applications, if the total pulse width of the turn-on spikes is less than 250ns and the negative spike on the CS pin does not exceed -0.3V, the R-C filter (as shown in Fig. 11) is free to eliminate.

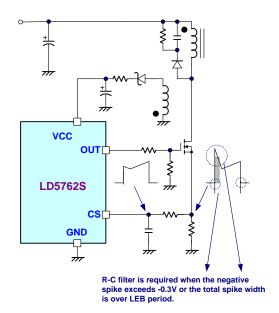

However, the total pulse width of the turn-on spike is related to the output power, circuit design and PCB layout. It is strongly recommended to add a small R-C filter (as shown in Fig. 12) for larger power application to avoid the CS pin from being damaged by the negative turn-on spike.

Fig. 11

Fig. 12

#### **Output Stage and Maximum Duty-Cycle**

An output stage of a CMOS buffer with typical 300mA driving capability is incorporated to drive a power MOSFET directly. And the maximum duty-cycle of LD5762S is limited to 83% to avoid the transformer saturation.

#### Voltage Feedback Loop

The voltage feedback signal is provided from the TL431 on the secondary side through the photo-coupler to the COMP pin of LD5762S. Similar to UC384X, its input stage is with 1 diodes voltage offset to feed the voltage divider with 1/4 ratio, that is,

$$V_{CS(PWM COMPARATOR)} = \frac{1}{4} \times V_{COMP}$$

A pull-high resistor is embedded internally to optimize the external circuit.

#### **Internal Slope Compensation**

A fundamental issue of current mode control is the stability problem when its duty-cycle is operated for more than 50%. To stabilize the control loop, the slope compensation is required in the traditional UC384X design by injecting the ramp signal from the RT/CT pin through a coupling capacitor. LD5762S has internal slope compensation circuit to simplify the external circuit design.

#### Oscillator and Switching Frequency

The LD5762S has the switching frequency between 65 kHz  $\pm$  6kHz internally to optimize its performance in EMI, thermal treatment, component sizes and transformer design.

#### **Dual-Oscillator Green-Mode Operation**

There are many different topologies has been implemented in different chips for the green-mode or power saving requirements such as "burst-mode control", "skipping-cycle mode", "variable off-time control "...etc. The basic operation theory of all these approaches intended to reduce the switching cycles under light-load or no-load condition either by skipping some switching pulses or reduce the switching frequency.

By using LD proprietary dual-oscillator technique, the green-mode frequency can be well controlled and further to avoid the generation of audible noise.

#### On/Off Control

Pulling COMP pin below  $V_{ZDC}$  will immediately disable the gate output of LD5762S. Remove the pull-low signal to reset it.

#### Over Power Protection (OPP) - Latch Mode

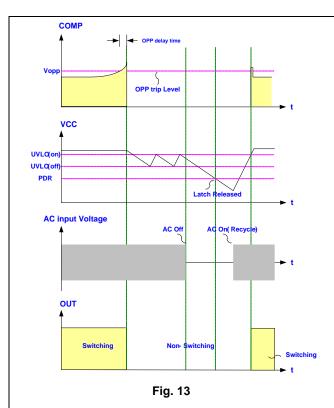

The LD5762S features latch mode of smart OPP protection. Fig. 13 shows the waveform under fault condition. The feedback system will force the voltage loop toward the saturation and thus pull the voltage high across COMP pin (VCOMP). When the VCOMP ramps up to the OPP threshold of 4.6V and stays for longer than OPP delay time, the protection will be activated and then latch off the gate output to stop switching of the power circuit. The delay time is to prevent the false-triggering during power-on, turn-off transient and in peak load condition. As soon as the over load condition is removed, the controller will remain latched until the VCC drops lower than PDR. It is necessary to restart AC power-on recycling to resume the output.

## Over Current Protection (OCP) - Latch Mode

When the switching current is higher than the OCP threshold, the internal counter counts up. When the total accumulated counting time is more than 4.5s, the controller triggers the OCP. This protection is latch mode function.

## Under Voltage Protection on FB (FB\_UVP) - Latch Mode

In order to prevent output short situation, LD5762S is implemented by FB\_UVP. When the output load is shorted to ground, the voltage suddenly decreases to zero, which always reflects to auxiliary winding during the gate off region. Therefore, as VFB is lower than 0.5V & VCOMP > 4.6V during gate off region, the FB\_UVP is triggered. And when the condition is maintained for 2.5ms, LD5762S is in latch mode.

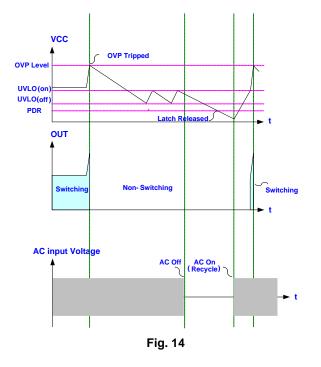

## Over Voltage Protection on VCC (OVP) – Latch Mode

The  $V_{GS}$  ratings of the nowadays power MOSFETs are mostly with 32V maximum. To protect the  $V_{GS}$  from the fault condition, LD5762S is implemented with OVP function on VCC. As the VCC voltage is larger than the OVP threshold voltage, the output gate drive circuit will be shut off simultaneously and stop switching the power MOSFET.

The VCC OVP is latch-off type of protection. Once the VCC trips OVP level (which is usually caused by the feedback loop opened), it will be latched off and try to recover. Turn off AC power to let VCC fall below PDR level to release overvoltage protection. And then restart the power to resume the operation. The de-latch level is defined by internal PDR. See Fig. 14 for its operation.

#### On-Chip OTP - Auto Recovery

An internal OTP circuit is embedded inside the LD5762S to provide the worst-case protection for this controller. When the chip temperature rises higher than

the trip OTP level, the output will be disabled until the chip is cooled down below the hysteresis window.

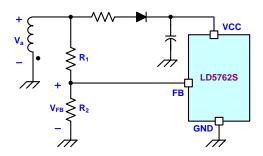

## Over Voltage Protection on FB Pin (FB\_OVP) – Latch Mode

An output overvoltage protection is implemented in the LD5762S. The auxiliary winding voltage can be reflected from secondary winding, in which the FB pin voltage is proportional to output voltage during the gate off time. OVP is worked by sensing the auxiliary voltage via the divided resistors R2, refereeing to Fig. 15. The equation of FB OVP is shown as follows.

$$R_2 = \frac{R_1 \cdot V_{FB\_OVP}}{V_a - V_{FB\_OVP}}$$

$$V_a = \frac{N_a}{N_S} (V_O + V_F)$$

Fig. 15

$V_{FB\_OVP}$  is the FB pin OVP trip voltage level.  $V_a$  is the auxiliary winding voltage which reflects from the forward voltage  $V_F$  of Schottky diode and output voltage  $V_O$ .  $N_S$  is turns ration of secondary-side winding.

If  $V_{\text{FB}}$  overs the FB\_OVP trip level, the internal counter starts counting 8 cycles, and then LD5762S goes to latch mode.

## Over Temperature Protection on CS Pin (CS OTP) - Latch Mode

LD5762S is implemented over temperature protection on CS pin which senses voltage to determine NTC status during gate off region. As  $V_{\rm CS}$  is greater than 0.28V and continues for 16 cycles, CS\_OTP is triggered, than LD5762S is in latch mode.

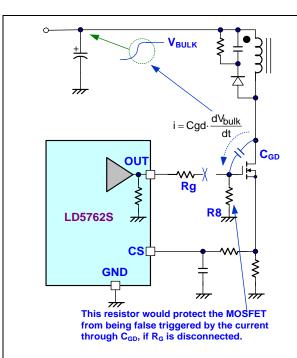

## Pull-Low Resistor on the Gate Pin of MOSFET

The LD5762S consists of an anti-floating resistor at OUT pin to protect the output from damage in abnormally operation or condition due to false triggering of MOSFET. Even so, we still recommend adding an external one at the MOSFET gate terminal to provide more protection in case of disconnection of gate resistor  $R_{\rm G}$  during power-on.

In such single-fault condition, as shown in Fig. 16, the resistor R8 can provide a discharge path to avoid the MOSFET from being false-triggered by the current through the gate-to-drain capacitor  $C_{GD}$ . Therefore, the MOSFET should be always pulled low and placed in the off-state as the gate resistor is disconnected or opened in any case.

Fig. 16

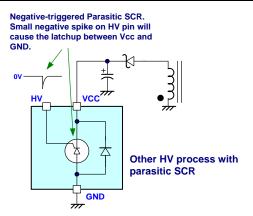

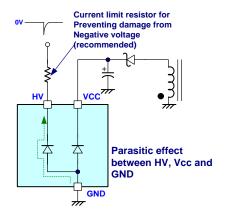

#### Protection Resistor on the Hi-V Path

In some other Hi-V process and design, there may be a parasitic SCR caused around HV pin, VCC and GND. As shown in Fig. 17, a small negative spike on the HV pin may trigger this parasitic SCR and cause latch-up between VCC and GND. It may damage the chip because of the equivalent short-circuit induced by such latch-up behavior.

Hi-V technology will eliminate parasitic SCR in LD5762S. Fig. 18 shows the equivalent Hi-V structure circuit of LD5762S. So that LD5762S is more capable to sustain negative voltage than similar products. However, a  $40 \mathrm{K}\Omega$  resistor is recommended to be added in the Hi-V path to play as a current limit resistor whenever a negative voltage is applied.

Fig. 17

Fig. 18

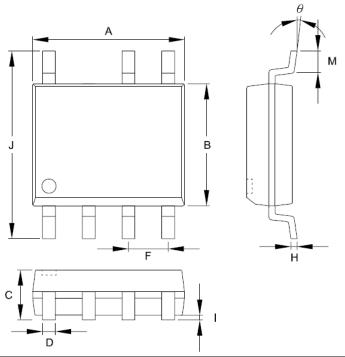

## **Package Information** SOP-7

|         | Dimensions i | n Millimeters | Dimensio | ns in Inch |

|---------|--------------|---------------|----------|------------|

| Symbols | MIN          | MAX           | MIN      | MAX        |

| А       | 4.801        | 5.004         | 0.189    | 0.197      |

| В       | 3.810        | 3.988         | 0.150    | 0.157      |

| С       | 1.346        | 1.753         | 0.053    | 0.069      |

| D       | 0.330        | 0.508         | 0.013    | 0.020      |

| F       | 1.194        | 1.346         | 0.047    | 0.053      |

| Н       | 0.178        | 0.254         | 0.007    | 0.010      |

| I       | 0.102        | 0.254         | 0.004    | 0.010      |

| J       | 5.791        | 6.198         | 0.228    | 0.244      |

| М       | 0.406        | 1.270         | 0.016    | 0.050      |

| θ       | 0°           | 8°            | 0°       | 8°         |

#### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

### **Revision History**

| REV. | Date       | Change Notice          |

|------|------------|------------------------|

| 00   | 08/23/2018 | Original Specification |