# Transition-Mode PFC and Quasi-Resonant Current Mode PWM Controller

**REV: 03**

### **General Description**

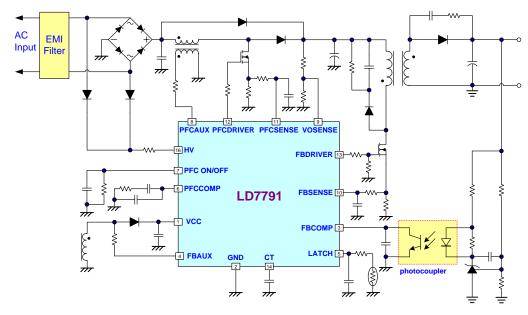

The LD7791 features transition mode Power Factor correction (PFC) controller and Quasi-Resonant (QR) current mode controller for cost effective and fewer external components design of high power application.

The intelligent PFC switching ON/OFF, zero current detection (ZCD) and frequency limitation mechanism enable it to reach better efficiency under any load conditions.

The device also integrates several functions of protection, such as X-CAP discharge, Brown-in/out protection, Over Load protection (OLP), Over Temperature Protection (OTP), Over Voltage Protection (OVP) and Over Current Protection (OCP) with High / Low Line Compensation. Therefore it can protect the system from being damaged due to occasional failure.

The LD7791 is available in a SOP-16 package.

#### **Features**

- Integrate PFC and QR Flyback Controller

- Transition Mode PFC Controller

- Quasi-Resonant Operation for Flyback

- Built-in X-CAP Discharging

- Brown In/Out Protection

- Internal Soft-Start Function

- Adjustment OLP De-bounce time

- External Latch Protection

- PFC Light Load Turn-off Control

- OVP (Over Voltage Protection)

- OCP (Cycle by cycle current limiting)

- 500mA/-1200mA Driving Capability

- Internal OTP function

### **Applications**

- AC-DC High Power Adapter

- Open Frame SMP

### **Typical Application**

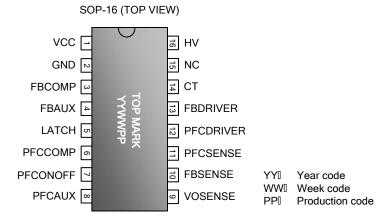

## **Pin Configuration**

## **Ordering Information**

| Part number | Package | Top Mark   | Shipping          |

|-------------|---------|------------|-------------------|

| LD7791 GS   | SOP-16  | LD7791 GS  | 2500 /tape & reel |

| LD7791A GS  | SOP-16  | LD7791A GS | 2500 /tape & reel |

| LD7791B GS  | SOP-16  | LD7791B GS | 2500 /tape & reel |

The LD7791 is ROHS compliant/ green packaged.

## **Options & Protection Mode**

| Part number | PFC Turn-off De-bounce (CT w/ 47nF) | Flyback burst<br>Mode trip | Brown-in<br>Level | OVP<br>(VCC & FBAUX) | OLP   | External<br>Latch | Internal<br>OTP |

|-------------|-------------------------------------|----------------------------|-------------------|----------------------|-------|-------------------|-----------------|

| LD7791 GS   | 1sec                                | On: 0.8V<br>Off: 0.6V      | 105               | Auto                 | Auto  | Latch             | Auto            |

| LD7791A GS  | 1sec                                | On: 0.8V<br>Off: 0.6V      | 105               | Latch                | Auto  | Latch             | Auto            |

| LD7791B GS  | 8sec                                | On: 1.1V<br>Off: 0.9V      | 102               | Latch                | Latch | Latch             | Auto            |

## **Pin Descriptions**

| Pin | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC       | Supply voltage pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2   | GND       | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | FBCOMP    | Voltage feedback pin for flyback stage. Connect a photo-coupler to close the control loop and achieve the regulation.                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | FBAUX     | Zero current detection and over voltage protection for flyback stage.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | LATCH     | External latch protection pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | PFCCOMP   | Output of the error amplifier for PFC voltage loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7   | PFCONOFF  | Threshold voltage setting of FBCOMP for PFC ON/OFF loading control.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8   | PFCAUX    | Zero current detection for PFC stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9   | VOSENSE   | Voltage sense for PFC output, regulation voltage is 2.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10  | FBSENSE   | Current sense pin. Connect it to sense the Flyback MOSFET current.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11  | PFCSENSE  | Current sense pin. Connect it to sense the PFC MOSFET current.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12  | PFCDRIVER | Gate drive output to drive the external MOSFET for PFC.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13  | FBDRIVER  | Gate drive output to drive the external MOSFET for Flyback.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14  | СТ        | Timer setting for Open Loop Protection, PFC light-load turn-off and flyback soft-start.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15  | NC        | Unconnected Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16  | HV        | Connect this pin to Line/Neutral of AC main voltage through a resistor to provide the startup current for the controller. When VCC voltage increases to trip the point of UVLO(ON), this HV loop will be turned off to reduce the power loss over the startup circuit.  HV pin Internal circuit will detect the AC peak voltage, providing Brown in/out and High / Low Line Detection function.  HV pin internal circuit will discharge X-CAP's energy through HV current source when AC line is disconnected. |

| <b>Absolute Maximum Ratings</b>                                 |                  |

|-----------------------------------------------------------------|------------------|

| VCC                                                             | -0.3V~ VCC OVP   |

| HV                                                              | -0.3V~ 500V      |

| FBCOMP, PFCCOMP, FBSENSE, PFCSENSE, FBAUX, PFCAUX,              |                  |

| VOSENSE, LATCH, CT, PFCONOFF                                    | -0.3V ~ 6V       |

| FBDRIVER, PFCDRIVER                                             | -0.3V ~ VCC+0.3V |

| Power Dissipation                                               | 600mW            |

| Package Thermal Resistance SOP-16, $\theta_{\rm JA}$            | 110°C/W          |

| Package Thermal Resistance SOP-16, $\theta$ JC.                 | 36°C/W           |

| Junction Temperature                                            | 150°C            |

| Lead Temperature (Soldering, 10sec)                             | 260°C            |

| Storage Temperature Range                                       | -55°C ~ 150°C    |

| ESD Voltage Protection, Human Body Model, (Pin 3~11 and Pin 14) | 3.5KV            |

| ESD Voltage Protection, Human Body Model, (Pin 1, 12, 13)       | 2.5KV            |

| ESD Voltage Protection, Human Body Model, (Pin 16)              | 1.0KV            |

| ESD Voltage Protection, Machine Model (except HV Pin)           | 250V             |

| Gate Output Current                                             | +500mA/-1200mA   |

## **Recommended Operating Conditions**

| Supply Voltage VCC                     | 10V ~ 29.5V   |

|----------------------------------------|---------------|

| VCC Capacitor                          | 47μF ~ 100μF  |

| HV Pin Resistor                        |               |

| FBCOMP Capacitor Value                 | 1nF ~10nF     |

| VOSENSE Capacitor Value                | 1nF ~10nF     |

| PFCAUX Pin Resistor                    | 10kΩ ~ 30kΩ   |

| PFCAUX Sink and Source Current Setting | 1mA           |

| Operating Ambient Temperature          | -40°C ~ 85°C  |

| Operating Junction Temperature Range   | -40°C ~ 125°C |

|                                        |               |

#### Note:

- 1. It's essential to connect COMP pin with a capacitor to filter out the undesired switching noise for stable operation.

- 2. Place the small signal components closed to IC pin as possible.

#### Caution:

Stress exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stress above Recommended Operating Conditions may affect device reliability.

### **Electrical Characteristics**

$(T_A = +25$ °C unless otherwise stated, VCC=15.0V)

| PARAMETER                               | CONDITI                         | ONS                  | SYM                   | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|---------------------------------|----------------------|-----------------------|------|------|------|-------|

| High-Voltage Supply (HV Pin             | )                               |                      |                       |      |      |      |       |

| High-Voltage Current Source             | VCC < PDR, VH                   | VCC < PDR, VHV = 80V |                       | 1.20 | 1.50 | 1.80 | mA    |

| for VCC Startup                         | VCC > PDR, VH                   | IV = 80V             | I <sub>HV3</sub>      | 2.00 | 3.00 | 4.00 | mA    |

| Off-State Leakage Current               | After UVLO(ON)<br>VHV = 500V    | ,                    | I <sub>HVOFF500</sub> |      |      | 32   | μА    |

| Line Voltage Detection (HV F            | Pin)                            |                      |                       |      |      |      |       |

| X-CAP Discharge Current*                |                                 |                      | I <sub>HVXCAP</sub>   |      | 3    |      | mA    |

| Brown-in Level                          |                                 | LD7791,<br>LD7791A   | V <sub>BNI</sub>      | 98   | 105  | 112  | V     |

|                                         |                                 | LD7791B              |                       |      | 102  |      |       |

| Brown-out Level                         |                                 |                      | $V_{BNO}$             | 89   | 95   | 101  | V     |

| Brown-in – Brown-Out Level*             |                                 | LD7791,<br>LD7791A   | V <sub>BNHYS</sub>    |      | 10   |      | V     |

|                                         |                                 | LD7791B              |                       |      | 7    |      |       |

| Brown-Out Debounce Time *               |                                 |                      | $T_{DBNO}$            | 500  | 570  |      | ms    |

| High Line Trip Level                    |                                 |                      | V <sub>HLINE</sub>    |      |      | 220  | V     |

| Low Line Trip Level                     |                                 |                      | V <sub>LLINE</sub>    | 184  |      |      | V     |

| High Line Threshold - Low<br>Line Level |                                 |                      | V <sub>LINHYS</sub>   | 5    |      |      | V     |

| Supply Voltage (VCC Pin)                |                                 |                      |                       |      |      |      |       |

| Halding Organist Dafana                 | VCC < UVLO (C                   | N)                   | I <sub>VCCST</sub>    |      | 150  |      | μА    |

| Holding Current Before UVLO (ON)        | VCC < UVLO (C<br>VLATCH = 0V    | N),                  | I <sub>VCCLCH</sub>   |      | 300  |      | μА    |

| 0 1 0                                   | VFBCOMP = 0V, PFC & Flyback OFF |                      | I <sub>VCCBST</sub>   |      |      | 1.3  | mA    |

| Operating Current                       | VFBCOMP = 3V, PFC & Flyback ON  |                      | I <sub>VCC3</sub>     |      |      | 2    | mA    |

| UVLO (OFF)                              | (-20°C ~125°C)                  |                      | V <sub>UVOFF</sub>    | 7.5  | 8.0  | 8.5  | V     |

| UVLO (ON)                               | (-20°C ~125°C)                  |                      | V <sub>UVON</sub>     | 17.0 | 18.0 | 19.0 | V     |

| VCC OVP Level                           |                                 |                      | V <sub>CCOVP</sub>    | 30.5 | 31.5 | 32.5 | V     |

| VCC OVP De-bounce Time*                 |                                 |                      | T <sub>DVCCOVP</sub>  |      | 64   |      | μS    |

| Power Down Reset Voltage (PDR)          |                                 |                      | PDR                   | 6    | 7    | 8    | V     |

| PARAMETER                                 | CONDITIONS                                                        |                    | SYM                    | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------|-------------------------------------------------------------------|--------------------|------------------------|-------|-------|-------|-------|

| PFC OFF & Open Loop Prote                 | ection Debounce                                                   | Timer Settir       | ng (CT Pin)            |       |       |       |       |

| OLD Dehouses Time*                        | CT=0.047μF, VF<br>VOLP, after star                                |                    | T <sub>DOLP</sub>      |       | 64    |       | ms    |

| OLP Debounce Time*                        | CT=0.047μF, VF<br>VOLP, at start-u                                |                    | T <sub>DOLPST</sub>    |       | 74    |       | ms    |

| FB Soft Start Time*                       | CT=0.047μF                                                        |                    | T <sub>FBSS</sub>      |       | 10    |       | ms    |

| VCC OSCP Debounce Time                    | CT=0.047µF, VFBCOMP > VOLP, VCC = UVLO (OFF) + 1V, after start-up |                    | T <sub>DOSCP</sub>     |       | 16    |       | ms    |

| PFC Turn-off Debounce                     | VFBCOMP < VPFC ON/OFF                                             | LD7791,<br>LD7791A | T <sub>DPFCOFF</sub>   |       | 1     |       | s     |

|                                           | , CT=0.047μF                                                      | LD7791B            |                        |       | 8     |       |       |

| External Latch (LATCH Pin)                | T                                                                 |                    |                        | 1     |       | ı     | 1     |

| LATCH Pin Source Current                  |                                                                   |                    | I <sub>LCH</sub>       | 75    | 80    | 85    | μΑ    |

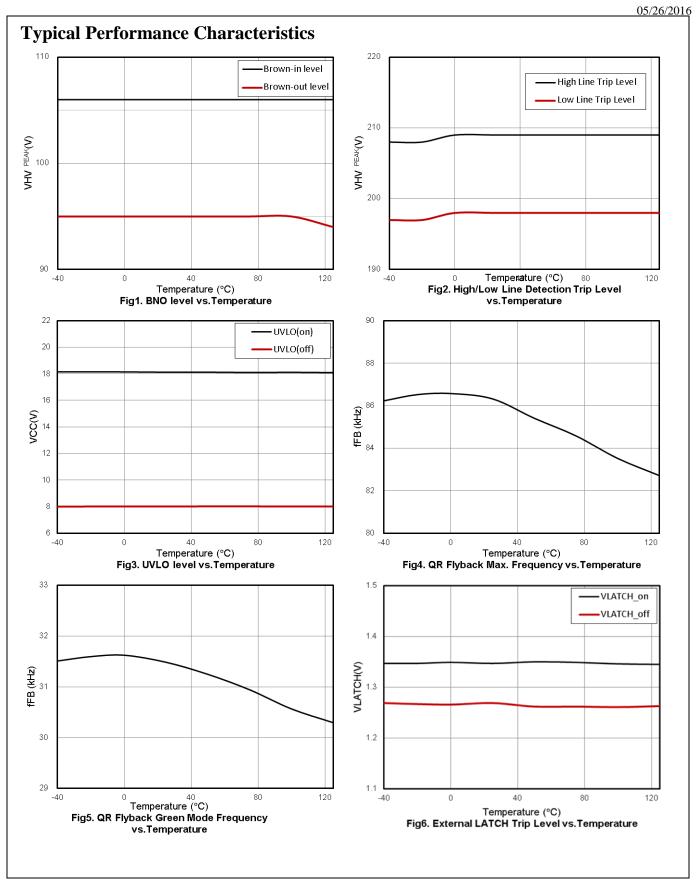

| Turn-On Trip Level                        |                                                                   |                    | V <sub>LATCHON</sub>   | 1.30  | 1.35  | 1.40  | V     |

| Turn-Off Trip Level                       |                                                                   |                    | V <sub>LATCHOFF</sub>  | 1.20  | 1.25  | 1.30  | V     |

| OTP LATCH pin de-bounce time              | Disable (High to Low)                                             |                    | T <sub>DLATCHOFF</sub> | 400   | 500   | 600   | μS    |

| On Chip OTP (Internal Thern               | nal Shutdown)                                                     |                    |                        |       |       |       |       |

| OTP Level *                               |                                                                   |                    | T <sub>SHUTDOWN</sub>  |       | 140   |       | °C    |

| OTP Hysteresis *                          |                                                                   |                    | T <sub>RESTART</sub>   |       | 40    |       | °C    |

| PFC Output Voltage Sensing                | (VOSENSE pin)                                                     |                    |                        |       |       |       |       |

| Reverence Input Voltage, V <sub>REF</sub> | (-20°C ~125°C)                                                    |                    | V <sub>FBREF</sub>     | 2.47  | 2.50  | 2.53  | V     |

|                                           |                                                                   |                    | $V_{PFCOVP}$           | 2.59  | 2.63  | 2.67  | V     |

| PFC OVP Trip Level                        | OVP Hysteresis                                                    |                    | V <sub>PFCOVPHYS</sub> | 0.115 | 0.130 | 0.145 | V     |

|                                           | Debounce time*                                                    |                    | T <sub>DPFCOVP</sub>   |       | 50    |       | μS    |

| Course Current of VOCENCE                 | VHV <sub>PEAK</sub> = 150V                                        |                    | I <sub>FOLBTLV</sub>   |       | 8     |       | μΑ    |

| Source Current of VOSENSE                 | VHV <sub>PEAK</sub> = 250V                                        |                    | I <sub>FOLBTHV</sub>   |       | 0.1   |       | μА    |

| Enable and Disable                        | PFC & Flyback Enable Threshold                                    |                    | V <sub>PFCEN</sub>     | 1.0   | 1.1   | 1.2   | V     |

| Threshold Voltage                         | PFC Disable The                                                   | reshold            | V <sub>PFCENL</sub>    | 0.8   | 0.9   | 1.0   | V     |

|                                           | Debounce Time                                                     | *                  | T <sub>DPFCEN</sub>    |       | 50    |       | μs    |

| VOSENSE Pull Down<br>Resistance           |                                                                   |                    | R <sub>VOSENSE</sub>   | 5     | 6     | 7     | ΜΩ    |

| PARAMETER                                    | CONDITIONS                       | SYM                   | MIN       | TYP                 | MAX       | UNITS |

|----------------------------------------------|----------------------------------|-----------------------|-----------|---------------------|-----------|-------|

| PFC Error Amplifier (PFCCO                   | MP Pin)                          |                       |           |                     |           |       |

| Transconductance                             |                                  | gm                    | 60        | 80                  | 100       | μmho  |

| Output Upper Clamp Voltage                   | VOSENSE = V <sub>REF</sub> -0.1V | V <sub>PCOMPMAX</sub> | 5.0       | 5.2                 | 5.4       | V     |

| Output Minimum Clamp<br>Voltage              |                                  | V <sub>РСОМРМІN</sub> | 0.85      | 0.90                | 0.95      | V     |

|                                              | Trip Level for PFCDRIVER Stop*   | V <sub>PCOMPOFF</sub> | 0.95      | 1.00                | 1.05      | V     |

| PFC Burst Mode                               | Trip Level for PFCDRIVER Start*  | V <sub>PCOMPON</sub>  | Threshold | for PFCDR<br>+ 50mV | IVER stop | V     |

| PFC Maximum On-Time                          |                                  |                       |           |                     |           |       |

| DEC May On Time                              | VHV <sub>PEAK</sub> = 150V       | T <sub>ONMAXPLV</sub> | 22        | 25                  | 28        | μS    |

| PFC Max. On-Time                             | VHV <sub>PEAK</sub> = 250V       | T <sub>ONMAXPHV</sub> | 7         | 8                   | 9         | μS    |

| PFC Minimum Off-Time                         |                                  |                       |           |                     |           |       |

| PFC Minimum Off-Time *                       |                                  | T <sub>POFFMIN</sub>  |           | 1                   |           | μS    |

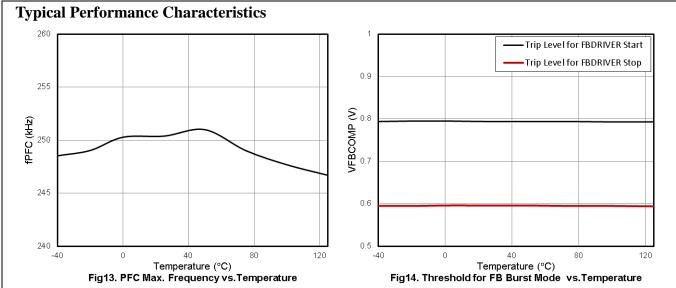

| PFC Maximum Frequency                        |                                  |                       |           |                     |           |       |

| PFC Maximum Frequency                        |                                  | F <sub>MAXPFC</sub>   | 225       | 250                 | 275       | kHz   |

| PFC Current Sensing (PFCS)                   | ENSE Pin)                        |                       |           |                     |           |       |

| Current Sense Input                          | VHV <sub>PEAK</sub> = 150V       | V <sub>PFCCSLV</sub>  | 0.47      | 0.52                | 0.57      | V     |

| Threshold Voltage                            | VHV <sub>PEAK</sub> = 250V       | V <sub>PFCCSHV</sub>  |           | 0.40                |           | V     |

| Leading Edge Blanking time                   |                                  | T <sub>LEBPFC</sub>   | 180       | 250                 | 320       | ns    |

| PFC Zero Current Detector (I                 | PFCAUX Pin)                      | 1                     | •         |                     |           |       |

| Upper Clamp Voltage                          | IPFCAUX = 3mA                    | $V_{PFCAUXUC}$        | 3.5       | 4.0                 | 4.5       | V     |

| PFC ZCD Trip Level                           |                                  | V <sub>PFCAUXH</sub>  | 0.15      | 0.20                | 0.25      | V     |

| Delay from PFCAUX to Output *                |                                  | T <sub>DPFCZCD</sub>  |           | 200                 |           | ns    |

| PFC ZCD Time Out                             | After PFCDRIVER Turn-off         | T <sub>TOPFC</sub>    | 40        | 50                  | 60        | μS    |

| PFC ON/OFF Control (PFCOI                    | NOFF pin)                        |                       |           |                     |           |       |

| Source Current for PFC OFF Threshold Setting |                                  | I <sub>PFCOFF</sub>   | 24.10     | 25.00               | 25.90     | μА    |

| Source Current for PFC ON Threshold Setting  |                                  | I <sub>PFCON</sub>    |           | 25.75               |           | μΑ    |

| PARAMETER                           | CONDITIO              | CONDITIONS         |                       | MIN           | TYP   | MAX   | UNITS  |

|-------------------------------------|-----------------------|--------------------|-----------------------|---------------|-------|-------|--------|

| Flyback Comp Pin (FBCOM             | /IP Pin)              |                    |                       |               |       |       |        |

| Short Circuit Current               | V <sub>COMP</sub> =0V |                    | I <sub>FBCOMPSC</sub> | 0.100         | 0.125 | 0.150 | mA     |

|                                     | Trip Level for        | LD7791,<br>LD7791A | V <sub>BSTONQR</sub>  | 0.7           | 0.8   | 0.9   | V      |

|                                     | FBDRIVER Start        | LD7791B            |                       | 1.0           | 1.1   | 1.2   |        |

| Flyback Burst Mode                  | Trip Level for        | LD7791,<br>LD7791A | V <sub>BSTOFFQR</sub> | 0.5           | 0.6   | 0.7   | V      |

|                                     | FBDRIVER Stop         | LD7791B            |                       | 0.8           | 0.9   | 1.0   |        |

| Heavy Load Trigger Level            |                       |                    | V <sub>IFBCSEN</sub>  | 2.8           | 2.9   | 3.0   | V      |

| Open Loop Voltage                   | FBCOMP pin ope        | n                  | $V_{FBC}$             | 5.2           | 5.4   | 5.6   | V      |

| Over Load Protection (FBC           | OMP Pin)              |                    |                       |               |       |       |        |

| OLP Trigger Level (VOLP)            |                       |                    | $V_{OLP}$             | 4.1           | 4.2   | 4.3   | V      |

| <b>Output Short Circuit Prote</b>   | ction                 |                    |                       |               |       |       |        |

| VCC OSCP Trigger Level *            | VFBCOMP > VOL         | .Р                 | V <sub>CCOSCP</sub>   | UVLO (OFF) +2 |       |       | V      |

| Flyback OVP (FBAUX pin)             |                       |                    |                       |               |       |       |        |

| OVP Trigger Current                 |                       |                    | I <sub>FBAUXOVP</sub> | 270           | 300   | 330   | μΑ     |

| Upper Clamp Voltage                 | IFBAUX = 0.3mA        |                    | $V_{FBAUXH}$          | 1.90          | 2.00  | 2.10  | V      |

| Debounce Cycle*                     |                       |                    | $T_{DFBAUXOVP}$       |               | 4     |       | FB PWM |

| FBAUX OVP Detection Blanking Time * | After FBDRIVER        | Turn-off           | $T_{DFBOVPDET}$       |               | 3     |       | μS     |

| Zero Current Detection (FE          | BAUX Pin)             |                    |                       |               |       |       |        |

| Lower Clamp Voltage                 | IFBAUX = -1mA         |                    | V <sub>FBAUXLC</sub>  | -0.3          |       | 0     | V      |

| Flyback ZCD Trip Level              |                       |                    | $V_{QRDLQR}$          |               | 50    |       | mV     |

| Flyback ZCD Delay Time *            |                       |                    | T <sub>DFBZCD</sub>   |               | 200   |       | ns     |

| Flyback ZCD Time Out1               | After Max. Frequency  |                    | T <sub>O1QR</sub>     | 4             | 5     | 6     | μS     |

| Minimum Flyback ZCD Time Out2       | After FBDRIVER        | Turn-off           | T <sub>O2QR</sub>     | 115           | 150   | 185   | μS     |

| ZCD Blanking Time                   | After FBDRIVER        | Turn-off           | T <sub>OFFMINQR</sub> |               | 3     |       | μS     |

| PARAMETER                             | CONDITIONS                                  | SYM                   | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|---------------------------------------------|-----------------------|------|------|------|-------|

| Oscillator for Switching Fred         | quency                                      |                       |      |      |      |       |

| Flyback Max. Frequency                |                                             | F <sub>MAXQR</sub>    | 78   | 85   | 92   | kHz   |

| Flyback Max. Frequency                |                                             | V                     |      | 2.2  |      | V     |

| Mode Threshold, V <sub>FBCOMP</sub> * |                                             | V <sub>FBCFMAX</sub>  |      | 2.2  |      | V     |

| Flyback Green Mode                    |                                             | _                     | 27   | 30   | 33   | kHz   |

| Frequency                             |                                             | F <sub>GREENQR</sub>  | 21   | 30   | 33   | KΠZ   |

| Flyback Green Mode                    |                                             | V                     |      | 4.0  |      | V     |

| Threshold, V <sub>FBCOMP</sub> *      |                                             | V <sub>FBCGREEN</sub> |      | 1.0  |      | V     |

| Flyback Maximum On Time               |                                             | T <sub>ONMAXQR</sub>  | 40   | 45   | 50   | μS    |

| Flyback Current Sensing (FE           | BSENSE Pin)                                 |                       |      |      |      |       |

| Threshold for Cycle by Cycle          | ( 0000 40500)                               |                       | 0.00 | 0.05 | 0.00 |       |

| Current Limit, Vcs(off)               | (-20°C ~125°C)                              | V <sub>OCQR</sub>     | 0.62 | 0.65 | 0.68 | V     |

| Leading Edge Blanking Time            |                                             | $T_{LEBQR}$           | 250  | 350  | 450  | ns    |

| OCP Compensation Current              | VHV <sub>PEAK</sub> = 250Vdc<br>FBCOMP = 3V | I <sub>FBCSHV</sub>   | 180  | 200  | 220  | μΑ    |

| Delay to Output*                      |                                             | T <sub>DCS</sub>      |      | 80   |      | ns    |

| PFC and Flyback Gate Drive            | Output (PFCDRIVER & FBDI                    | RIVER Pin)            |      |      |      | 1     |

| Output Low Level                      | VCC=15V, I <sub>SINK</sub> =100mA           | V <sub>OUTH1</sub>    | 0    |      | 1.5  | V     |

| Output High Level                     | VCC=15V, I <sub>SOURCE</sub> =100mA         | V <sub>OUTL</sub>     | 9.0  |      | VCC  | V     |

| Output High Level                     | VCC=9V, I <sub>SOURCE</sub> =2mA            | V <sub>OUTH2</sub>    | 8.5  |      | VCC  | V     |

| Output High Clamp Level               | VCC=17V                                     | V <sub>OUTCL</sub>    |      | 13   |      | V     |

| Rising Time *                         | VCC =15V, CL=2700pF                         | T <sub>OUTR</sub>     |      | 130  |      | ns    |

| Falling Time *                        | VCC =15V, CL=2700pF                         | T <sub>OUTF</sub>     |      | 45   |      | ns    |

#### Notes:

<sup>\*</sup>Guaranteed by design.

## **Application Information**

#### **Operation Overview**

As long as the green power requirement becomes a trend and the power saving is getting more and more important for the switching power supplies and switching adaptors, the traditional PWM controllers are not able to support such new requirements. Furthermore, the cost and size limitation force the PWM controllers to integrate more functions and reduce the external part counts. The LD7791 is ideal for these applications to provide an easy and cost effective solution. Its detailed features are described as below.

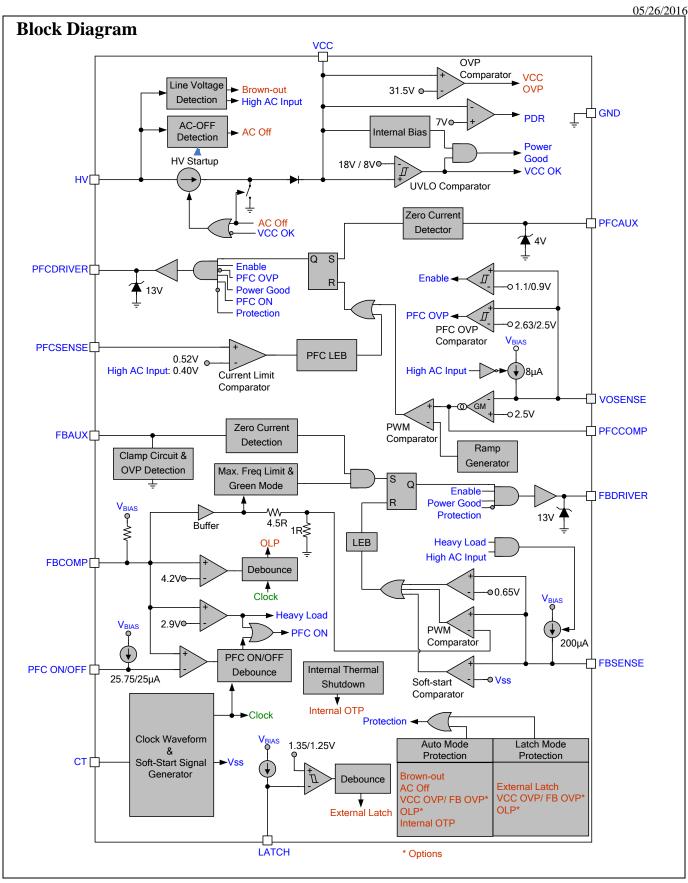

## Internal High-Voltage Startup Circuit and Under Voltage Lockout (UVLO)

The traditional circuit provides the startup current through a startup resistor to power up the PWM controller. However, it consumes too much power to meet the power saving requirement. In most cases, startup resistors carry larger resistance and take much time to start up.

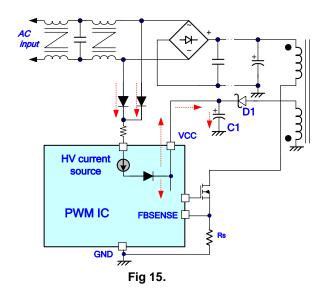

As shown in Fig 15, the LD7791 is implemented with a high-voltage startup circuit to minimize power loss. During the startup phase, the high-voltage current source sinks current from AC Line or Neutral to provide the startup current and charge the VCC capacitor C1 at the same time.

Please refer to Fig 16. If VCC is below PDR, the charge current is only 1.5mA and the lower charge current can protect IC if the VCC Pin is short to the GND. Once VCC voltage rises up to the UVLO(ON) threshold, HV pin will no longer charge the capacitor. On the contrary, it sends a gate-drive signal to draw supply current for VCC from the auxiliary winding of the transformer. That minimizes the power loss on the start-up circuit successfully.

An UVLO comparator is embedded to detect the voltage across VCC pin and ensure the supply voltage is high enough to power on the LD7791 in addition to driving the power MOSFET. As shown in Fig 16, the hysteresis is

provided to prevent the LD7791 from shutdown by the voltage dip during startup. The turn-on and turn-off threshold level are set at 18V and 8V respectively.

For better EMI performance, it's recommended to connect HV pin to the input terminals of bridge diode, as Fig 15.

VCC

UVLO(off)

PDR

HV Current

1.5mA

OmA (off)

VCC current

Holding

Current

("150uA)

Fig 16.

14

#### **Output Driver Stage**

The device builds a CMOS buffer respectively in the stages of PFC and Flyback, with typical 500mA/-1200mA driving capability, to drive the power MOSFET directly. The output voltage is fixed at 13V to protect the MOSFET gate even when the VCC voltage is over 13V.

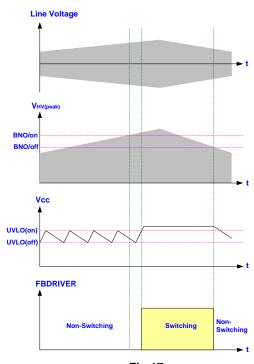

#### **Brown In/ Out Protection**

The LD7791 features brown-in / brown-out protection on HV pin. As the built-in comparator detects line voltage, it will turn off the controller to prevent any damages. In case of VHV < Brown-out Level, the output driver will be disabled even when VCC already reaches UVLO (ON). It therefore forces VCC hiccup between ULVO (on) and UVLO (OFF). Unless the line voltage is large enough and over Brown-in Level, the output driver will not start switching even if the next ULVO (on) is tripped. A hysteresis is designed to prevent false-triggering and damage to the external components during turn-on and turn-off phase. See Fig 17 for the operation.

Fig 17.

#### **High Line and Low Line Detection**

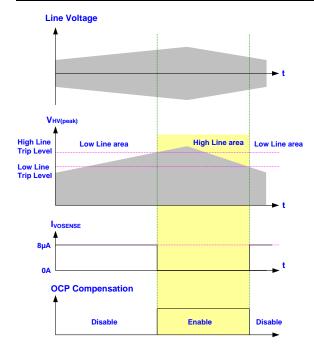

The HV pin can detect AC input level to control source current of VOSENSE Pin and OCP compensation logic. During AC input variations, the source current of VOSENSE and OCP compensation logic is as follows:

| VHV <sub>PEAK</sub> | Source Current of VOSENSE | OCP Comp. |

|---------------------|---------------------------|-----------|

| > 220V              | 0A                        | Enable    |

| < 184V              | 8μΑ                       | Disable   |

Fig 18.

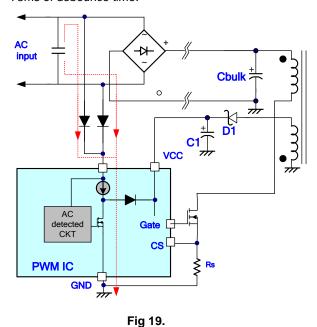

#### X-CAP Discharge Function

In general, a discharging resistor is placed across X-capacitor. To meet safety requirement, this component requires to be discharged in less than 1sec, that is,

$$\tau_{Discharge} = C_{X-Cap} \times R_{Discharge} \leq 1sec$$

The power loss of this resistor is in direct proportion to the square of input voltage. For example, if the input voltage is 264Vac and the discharging resistance is around  $2M\Omega$ ,

35mW, we can predict the power loss by the following equation.

$$P_{Loss} = \frac{V_{AC (RMS)}^{2}}{R_{Disch arge}}$$

To eliminate the significant power loss from this discharging resistor, the LD7791 applies the innovative patent technology to discharge X-CAP's energy through HV current source when AC line is disconnected. Fig 19 shows the operation.

By applying this technology, the system can easily pass the safety test without discharging resistor. It reduces power loss as well.

If it's unplugged, the AC voltage across X-CAP will still remain the same. The LD7791 detects HV pin to monitor the AC voltage across X-CAP. If AC voltage across X-CAP rises or falls beyond the limit of the threshold, under any load conditions, the HV scheme will sink constant current to the GND to discharge it in around 75ms of debounce time.

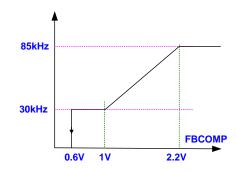

Flyback Green Mode and PFC Turn-off Control

The LD7791 uses maximum frequency limit scheme to control flyback switching frequency, and it depends on the level of FBCOMP voltage. When output loading is decreased, FBCOMP voltage becomes lower and the switch frequency can be reduced under the light load condition. This feature helps to enhance the efficiency in light load condition. The curve is shown as Fig 20.

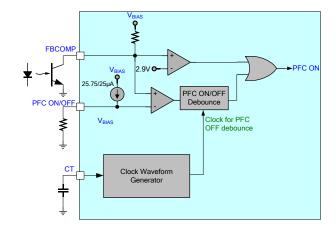

To meet the requirement of European 'EMC-directive', it's necessary to adopt a solution with PFC control. In order to enhance efficiency under light load, the LD7791 features PFC control and is able to shut down switching to reduce power consumption. As FBCOPM voltage falls below PFC ON/OFF voltage threshold, the PFC controller will stop PFCDRIVER switching until FBCOMP voltage resume its level. See Fig 21 for the block.

Fig 20. Max. Frequency Limit of Flyback

Fig 21.

#### **PFC Output Voltage Setting**

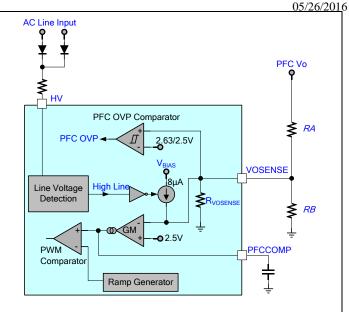

The LD7791 monitors the output voltage signal from the VOSENSE pin through a resistor divider pair of RA and RB. A transconductance amplifier is used to replace the conventional voltage amplifier. The output current of the amplifier changes according to the voltage difference of the inverting and non-inverting input of the amplifier. The output voltage of the amplifier is compared with the internal ramp signal to generate the turn-off signal. The current is flowed out of the VOSENSE Pin (8µA) during low line condition. The PFC output voltage is determined by the following relationship.

High Line:

PFC

$$V_0 = 2.5V \times (1 + \frac{RA}{RB//R_{VOSENSE}}) \cdots (1)$$

Low Line:

PFC V<sub>O</sub> =

$$(2.5V - 8\mu A \times RB//R_{VOSENSE})$$

$\times (\frac{RA}{RB//R_{VOSENSE}}) + 2.5V$  ....(2)

Please refer to the equation where RA and RB are values for top and bottom feedback resistor (as shown in the Fig 22).

Once the value of PFC  $V_O$  is determined, then substitutes the value of RA/RB obtaining from the formula (1) to (2) to get the RB value.

Fig 22.

#### **PFC Over Voltage Protection**

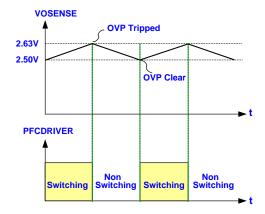

In order to prevent the bulk cap from being harmed due to overvoltage phenomenon during start-up, transient or fault conditions. The OVP is implemented on the VOSENSE pin. If the VOSENSE voltage rises over the OVP threshold of 2.63V, the output driver circuit will be shut down simultaneously to stop the switching of the power MOSFET until the VOSENSE voltage drops to 2.5V. Fig 23 shows its operation.

Fig 23.

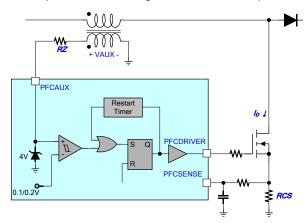

#### **PFC Zero Current Detection**

Fig 24 shows PFC Zero Current Detection (ZCD) block. As the auxiliary winding coupling with the inductor detects that the current over the boost inductor drops to zero, the ZCD block will switch on the external MOSFET. This feature allows transition-mode to be operated. If the voltage of the PFCAUX pin rises above 0.2V, the ZCD comparator will turn on the MOSFET. The PFCAUX pin is protected internally by 4V-high clamp and 0V-low clamp. The 50µs timer will generate a MOSFET turn-on signal if the output driver has being at low level over 50µs.

Fig 24.

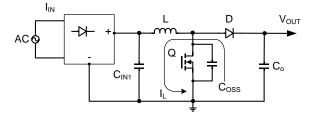

Fig 25 shows typical ZCD-related waveforms. Rz will produce some delay because of the parasitic capacitance on the PFCAUX pin. Before the switch turns on with delay, the stored charge of the  $C_{OSS}$  (MOSFET output capacitor) will be discharged to a small filter capacitor  $C_{IN1}$  with a bridge diode through the path indicated in Fig 26. So the input current  $I_{IN1}$  drains to zero at the time. Here, it's recommended to set source current of the PFCAUX pin around 1mA. Rz can be obtained from the below formula and it is also adjustable to control the turn-on timing of the switch.

$$R_Z = PFC \ Vo^{MAX} \times \frac{N_{AUX,PFC}}{N_{P,PFC}} \div 1mA$$

Fig 25.

Fig 26.

#### **PFC Current Sensing**

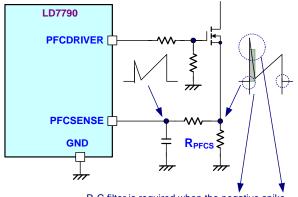

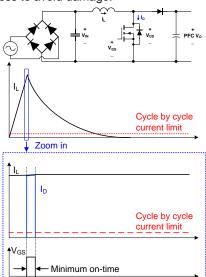

The LD7791 detects the PFC MOSFET current across the PFCSENSE pin to protect the MOSFET, by performing the cycle-by-cycle current limit. The maximum voltage threshold of the PFCSENSE pin is set at 0.52V. The MOSFET peak current can be obtained as below.

$$I_{PEAK(MAX)} = \frac{0.52V}{R_{PFCS}}$$

A 250ns leading-edge blanking (LEB) timer is built in the PFCSENSE pin to prevent the false-triggering caused by current spike.

However, the pulse width of the turn-on spike is determined according to the output power, circuit design and PCB layout. It is strongly recommended to adopt a smaller R-C filter for high power application to avoid the PFCSENSE pin being damaged by the negative turn-on spike.

R-C filter is required when the negative spike exceeds -0.3V or the total spike width is over 250nS LEB period.

Fig 27.

#### Flyback Voltage Feedback Loop

The voltage feedback signal is provided by the TL431 at the secondary side through the photo-coupler to the FBCOMP pin of the LD7791 and fed to the voltage divider with 1/5.5 ratio. That is,

$$V_{\text{FBSENSEPWM}_{\text{COMPARATOR}}} = \frac{V_{\text{FBCOMP}}}{5.5}$$

A pull-high resistor is embedded internally to optimize the external circuit.

#### **Flyback Burst Mode Control**

The output driver of the LD7791 can be disabled immediately by pulling FBCOMP pin voltage level below FBDRIVER Stop Trip Level. The disable-mode can be released when FBCOMP pin voltage level is pulled higher than FBDRIVER start trip level.

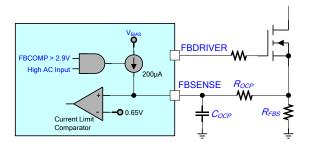

## Flyback Current Sensing & OCP Compensation Design Tip

The LD7791 features current mode of flyback control. It receives both current and voltage signal to form the control loop and achieve regulation. LD7791 detects the primary MOSFET current across FBSENSE pin for peak current mode and also limits the current cycle-by-cycle. The maximum voltage threshold of FBSENSE pin is set at 0.65V. Thus the MOSFET peak current can be calculated as:

$$I_{PEAK(MAX)} = \frac{0.65V}{R_{EBS}}$$

In general, the power converter provides various current signals to reflect the input voltage with propagation delay time. To compensate it, an offset voltage is added to the FBSENSE signal by an internal current source ( $200\mu A$ ) and an external resistor ( $R_{OCP}$ ) between the sense resistor ( $R_{FBS}$ ) and FBSENSE pin, as shown in Fig 28. The compensation current is only enabled when FBCOMP voltage is above 2.9V at high line condition. ROCP:  $220\Omega \sim 1 k\Omega$ ; COPC:  $47pF \sim 470pF$ .

As PFC behaves in current sensing, a 350nS leading-edge blanking (LEB) timer is incorporated in the input of FBSENSE pin to prevent false-triggering caused by current spike.

Fig 28.

#### **Protection Mode**

There are two kinds of protection modes in the LD7791.

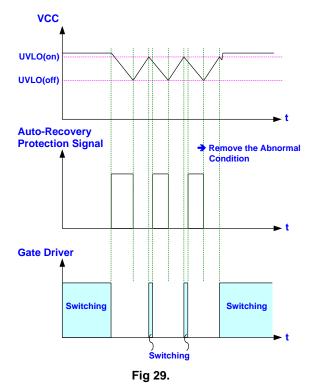

#### **Auto-Recovery Protection Mode**

As Auto-Recovery protection circuit latches the operation,

the gate output will switch for a short term as every time VCC rises back to UVLO(ON). It therefore forces the VCC hiccup between UVLO(ON) and UVLO(OFF). As soon as the fault condition is removed, the system will resume it operation right away. Fig 29 shows the operation.

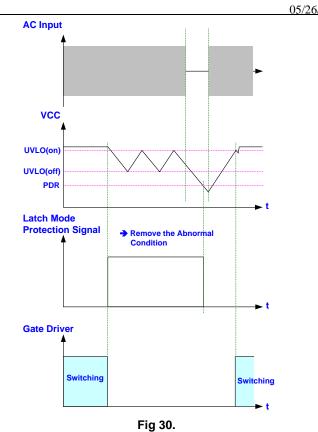

#### **Latch Protection Mode**

As Latch type protection circuit latches the operation, the gate output will remain in off-state even when the VCC reaches UVLO(ON). The system is unable to recover unless it is repowered to let VCC drop below Power Down Reset (PDR) and then ramps over UVLO(ON). Fig 30 shows the operation.

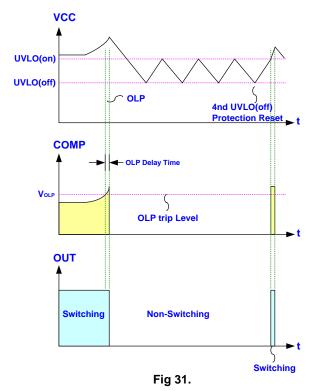

Over Load Protection (OLP)- Auto Recovery

To protect the circuit from being damaged at over-load condition, short or open loop condition, the LD7791 is implemented with smart OLP function. The LD7791 features auto recovery function. See Fig 31 for the waveform. In such fault condition, the feedback system will force the voltage loop to enter saturation and then pull high the voltage over FBCOMP pin (VFBCOMP). When VFBCOMP ramps up to the OLP tripped level (4.2V) for longer than the OLP delay time, the protection will be activated to turn off the output driver and stop the switching of power circuit. The OLP delay time is set by CT pin. It is to prevent the false triggering during the transient condition of power-on and turn-off.

A divide-4 counter is implemented to reduce the average power under OLP behavior. Whenever OLP is activated, the output is latched off and the divide-4 counter starts to count the number of UVLO(OFF). The protection mode

will not be released and the output will not be resumed until the 4th UVLO(off) level is tripped. With the protection mechanism, the average input power will be reduced, so that the component temperature and stress can be controlled in the safe operating area.

#### **Output Short Circuit Protection (OSCP)**

If the output of the system is short-circuited, Vo and VCC will drop immediately. Due to the operating of the voltage loop, FBCOMP voltage will be pulled high at the same time. If the situation continues to pull FBCOMP high over 4.2V for over 16ms and VCC drops below 10V, it will activate OSCP protection against damage and turn off the gate driver.

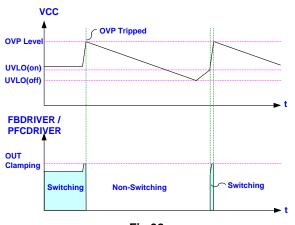

#### **OVP on VCC – Auto Recovery or Latch**

The maximum VCC rating of the LD7791 is about 32.5V. To protect the LD7791 in over-voltage condition, it is implemented with OVP function on VCC. Once VCC voltage rises over the OVP threshold, it will turn off the

output driver right away and be disable the power MOSFET until the UVLO(ON) is tripped.

The VCC OVP function is auto-recoverable or latch. Fig 32 shows auto-recovery mode operation.

Fig 32.

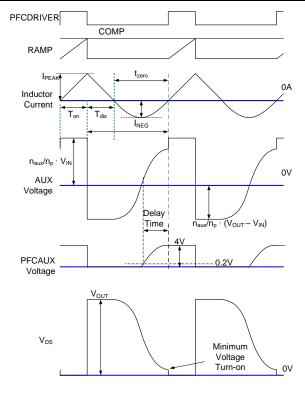

#### **Flyback Zero Current Detection**

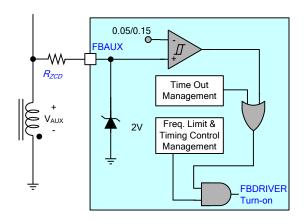

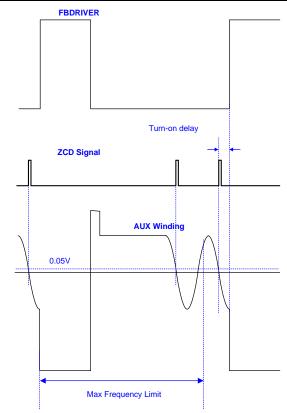

Fig 33 shows Flyback Zero Current Detection (ZCD) block. As PFC behaves in ZCD, as soon as the auxiliary winding coupled with the inductor detects that the current over the flyback transformer drops to zero, the ZCD block will switch on the external MOSFET. This feature enables Quasi-Resonant operation. The FBAUX uses falling edge to trigger ZCD to turn on FBDRIVER and the trigger level is 0.05V as shown in Fig 34. FBAUX pin is built-in with 2V-high and 0V-low clamp.

Fig 33.

Fig 34.

#### **OVP on FBAUX - Auto Recovery or Latch**

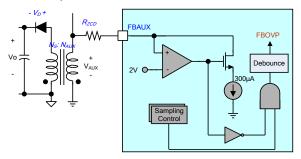

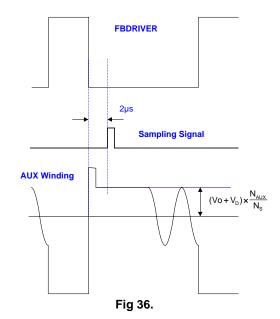

FBAUX also provides over voltage protection (OVP). An output overvoltage protection is implemented in the LD7791, as shown in Fig 35 and Fig 36. It senses the auxiliary winding voltage by the resistor,  $R_{ZCD}$ . The auxiliary winding voltage is reflected on the secondary winding and therefore the flat voltage on FBAUX pin is in proportion to the output voltage. The flat voltage can be transformed into a current signal. The sinking current of FBAUX is.

$$I_{FBAUX} = [(V_O + V_D) \times \frac{N_{AUX}}{N_S} - 2V] / R_{ZCD}$$

The LD7791 samples the signal after FBDRIVER turns off with 3 $\mu$ s delay to perform output over voltage protection. This 3 $\mu$ s delay time is used to ignore the voltage ringing from leakage inductance of PWM transformer. The sampled current level is compared with internal threshold current 300 $\mu$ A. If the sampled current exceeds the OVP

trip level, an internal counter will start to count the subsequent OVP events. The counter has been added to prevent incorrect OVP detection which might occur during ESD or lightning events. If 4 flyback PWM cycles of the subsequent OVP events are detected, the OVP circuit will switch the power MOSFET off.

Fig 35.

#### On-Chip OTP - Auto Recovery

An internal OTP circuit is embedded in the LD7791 to provide the worst-case protection. When the chip temperature rises over the trip OTP level, the output driver will be disabled until the chip is cooled down below the hysteresis temperature.

#### External Latch -Latch

The External Latch function is implemented to sense whether there is any hot-spot of power circuit like power

MOSFET or output rectifier. Once an over-temperature condition is detected, the OTP will be activated to shut down the LD7791.

Typically, the NTC is recommended to connect to LATCH pin. The NTC resistance will decrease as the device or surroundings stays in high temperature. The relationship is shown as below.

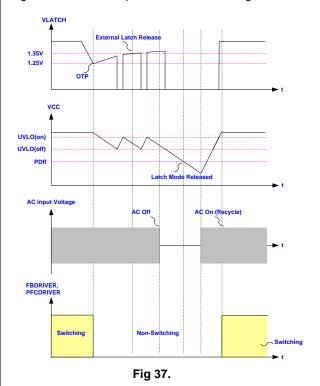

$$V_{LATCH} = 80\mu A \times R_{NTC}$$

When the formula,  $V_{LATCH} < Turn-off Trip (typ. 1.25V)$ , is established, it will trigger the protection to shut down the output driver and latch off the power supply. The LD7791 will remain latched unless the VCC drops below PDR (power down reset) and rise over UVLO(ON). It requires two conditions to restart the LD7791 successfully. Cool down the circuit so that the NTC resistance will increase and raise  $V_{LATCH}$  above 1.35V, then to plug in AC power again. The detailed operation is shown in Fig 37.

#### **Adjustable Timer on CT Pin**

Connect CT pin with an external capacitance to generate clock for timer. The OLP debounce, PFC Turn-off debounce and flyback Soft-start period are set according to the below table.

|                 |            | l           |                       |       |  |

|-----------------|------------|-------------|-----------------------|-------|--|

|                 | FB         | OLP         | PFC Turn-off Debounce |       |  |

| C <sub>CT</sub> | Soft-start | Debounce    |                       |       |  |

|                 | period     | period Time |                       | ince  |  |

|                 |            |             | LD7791,               | 0.475 |  |

| 22nF            | 4.6ms      | 30ms        | LD7791A               | 0.47s |  |

|                 |            |             | LD7791B               | 3.76s |  |

|                 |            |             | LD7791,               | 4.00- |  |

| 47nF            | 10.0ms     | 64ms        | LD7791A               | 1.00s |  |

|                 |            |             | LD7791B               | 8.00s |  |

|                 |            |             | LD7791,               | 4.45- |  |

| 68nF            | 14.0ms     | 93ms        | LD7791A               | 1.45s |  |

|                 |            |             | LD7791B               | 11.6s |  |

| 100nF           |            |             | LD7791,               | 0.40- |  |

|                 | 21.2ms     | 136ms       | LD7791A               | 2.13s |  |

|                 |            |             | LD7791B               | 17.0s |  |

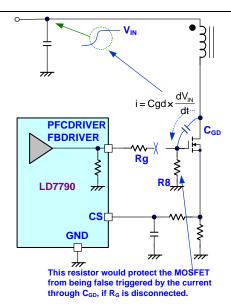

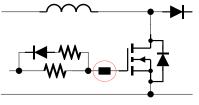

## Pull-Low Resistor on the Gate Pin of MOSFET

The LD7791 consists of an anti-floating resistor at PFCDRIVER and FBDRIVER pin to prevent the output driver in any abnormal condition which may false triggering MOSFET. Even so, we still recommend adding an external one at the MOSFET gate terminal to provide more protection in case of disconnection of gate resistor  $R_{\rm G}$  during power-on.

In such single-fault condition, as shown in Fig 38, the resistor R8 can provide a discharge path to prevent the MOSFET from being false-triggering by the current through the gate-to-drain capacitor  $C_{GD}$ . Therefore, the gate of MOSFET should be always pulled low and kept in the off-state as the gate resistor is disconnected or opened in any case.

Fig 38.

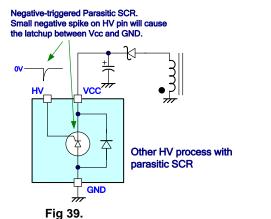

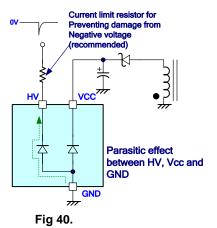

#### Protection Resistor on the HV Path

In some other Hi-V process and design, there may be a parasitic SCR to be formed between HV pins, VCC and GND. As shown in Fig 39, a small negative spike on the HV pin may trigger this parasitic SCR and cause latch-up between VCC and GND. It may damage the chip because of the equivalent short-circuit induced by such latch-up behavior.

Leadtrend's proprietary of Hi-V technology will eliminate parasitic SCR in the LD7791. Fig 40 shows the equivalent Hi-V structure circuit of the LD7791. The LD7791 is more capable to sustain negative voltage than similar products. However, a  $10 \text{K}\Omega$  resistor is recommended to be added in the Hi-V path to regard as a current limit resistor whenever a negative voltage is applied.

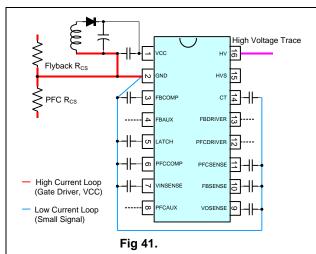

#### **PCB Layout Guideline**

The LD7791 consists of a pair of gate drivers. Here are some guide lines to layout the PCB for suppressing the noises caused from the effects between PFC and flyback. The PCB layout diagram is shown as Fig 41.

- Separate small signal current loop from gate driver or VCC current loop.

- Separate VCC current loop from PFC gate driver to minimize the effect from flyback ZCD.

- Minimize the trace length between the GND pin and the current sense resistor.

- 4. Be aware of routing the HV pin AWAY from the other traces so that it possesses high voltage.

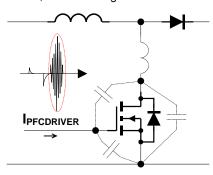

#### **Inrush Current of PFC**

During the period that AC power goes on/off fast, inrush current will flow through PFC choke if bulk capacitor voltage is lower than AC line voltage. Once PFC controller remains operation in such condition, large current will flow in PFC MOSFET during gate turn-on phase, shown as Fig 42. So, it's necessary to select a MOSFET of proper current stress to avoid damage.

Fig 42.

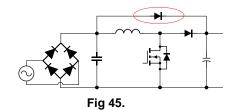

Under this condition, during MOSFET gate turn-on and turn-off period, some MOSFET will couple with the high frequency energy, generated from parasitic element as inrush current resonates into the controller. See Fig 43 for it. The gate driver of controller can be damaged by the external energy. A bead core is added in the gate driver

current loop to filter the high frequency voltage from damage, shown as Fig 44. Placing an extra by-pass diode here to limit inrush current of PFC choke helps to minimize the risk, shown as Fig 45.

Fig 43.

Fig 44.

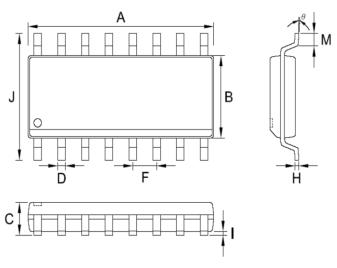

## Package Information SOP-16

| Symbols | Dimensions in Millimeters |        | Dimensions in Inch |       |

|---------|---------------------------|--------|--------------------|-------|

|         | MIN                       | MAX    | MIN                | MAX   |

| А       | 9.800                     | 10.010 | 0.386              | 0.394 |

| В       | 3.800                     | 4.000  | 0.150              | 0.157 |

| С       | 1.346                     | 1.753  | 0.053              | 0.069 |

| D       | 0.330                     | 0.510  | 0.013              | 0.020 |

| F       | 1.27 TYP.                 |        | 0.05 TYP.          |       |

| Н       | 0.178                     | 0.254  | 0.007              | 0.010 |

| I       | 0.100                     | 0.254  | 0.004              | 0.010 |

| J       | 5.790                     | 6.200  | 0.228              | 0.244 |

| M       | 0.380                     | 1.270  | 0.015              | 0.050 |

| θ       | 0°                        | 8°     | 0°                 | 8°    |

#### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

## **Revision History**

| Rev. | Date       | Change Nation                                                   |  |

|------|------------|-----------------------------------------------------------------|--|

| Rev. | Date       | Change Notice                                                   |  |

| 00   | 09/03/2014 | Original Specification.                                         |  |

| 01   | 03/03/2015 | Add LD7791B information                                         |  |

| 02   | 04/24/2015 | Spec $\theta_{JC}$ is added.                                    |  |

|      |            | Spec items are changed:                                         |  |

|      |            | The max power dissipation and junction temperature are changed. |  |

|      |            | 2. The typical value of t <sub>FBSS</sub> is changed.           |  |

|      |            | 3. The C <sub>CT</sub> Pin timer table is modified.             |  |

| 03   | 05/26/2016 | The block diagram is corrected.                                 |  |