# LF13006/LF13007 Digital Gain Set

## **General Description**

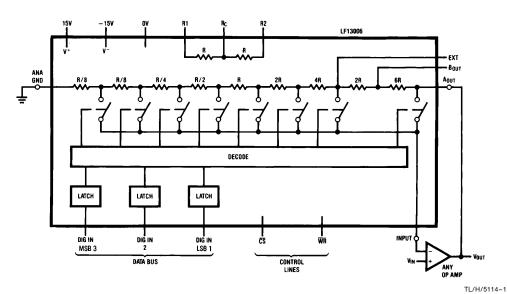

The LF13006 and LF13007 are precision digital gain sets used for accurately setting non-inverting op amp gains. Gains are set with a 3-bit digital word which can be latched in with  $\overline{\rm WR}$  and  $\overline{\rm CS}$  pins. All digital inputs are TTL and CMOS compatible.

The LF13006 shown below will set binary scaled gains of 1, 2, 4, 8, 16, 32, 64, and 128. The LF13007 will set gains of 1, 2, 5, 10, 20, 50, and 100 (a common attenuator sequence). In addition, both versions have several taps and two uncommitted matching resistors that allow customization of the gain.

The gains are set with precision thin film resistors. The low temperature coefficient of the thin film resistors and their excellent tracking result in gain ratios which are virtually independent of temperature.

The LF13006, LF13007 used in conjunction with an amplifier not only satisfies the need for a digitally programmable amplifier in microprocessor based systems, but is also useful for discrete applications, eliminating the need to find 0.5% resistors in the ratio of 100 to 1 which track each other over temperature.

#### **Features**

- TTL and CMOS compatible logic levels

- Microprocessor compatible

- Gain error 0.5% max

- Binary or scope knob gains

- $\blacksquare$  Wide supply range + 5V to  $\pm$  18V

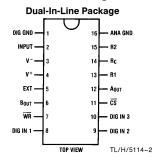

- Packaged in 16-pin DIP

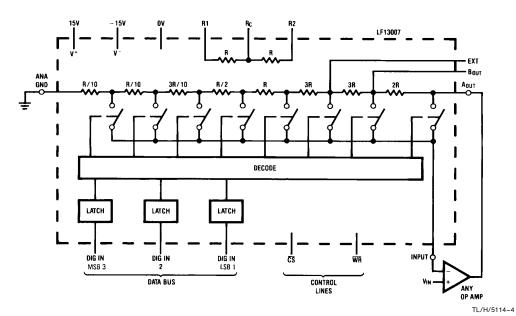

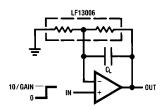

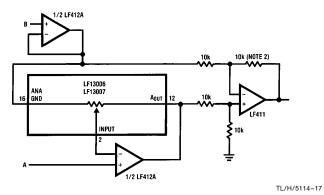

## **Block Diagram and Typical Application (LF13006)**

Note: R  $\simeq$  15 k $\Omega$

Order Number LF13006N or LF13007N See NS Package Number N16A

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

### **Operating Ratings** (Note 1)

Operating Temperature Range  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  Lead Temp. (Soldering, 10 seconds)  $260^{\circ}\text{C}$

## **Electrical Characteristics** (Note 2)

| Parameter                                | Conditions                                                 | Typ<br>(Note 3) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Units              |

|------------------------------------------|------------------------------------------------------------|-----------------|-----------------------------|-----------------------------|--------------------|

| Gain Error                               | $A_{OUT} = \pm 10V$<br>ANA GND = 0V<br>$I_{INPUT} < 10 nA$ | 0.3             | 0.5                         | 0.5                         | %(max)             |

| Gain Temperature Coefficient             | $A_{OUT} = \pm 10V$<br>ANA GND = 0V                        | 0.001           |                             |                             | %/°C               |

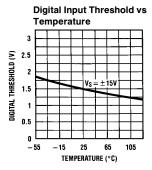

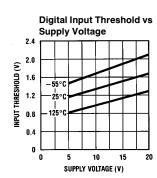

| Digital Input Voltage<br>Low<br>High     |                                                            | 1.4<br>1.6      | 0.8<br>2.0                  | 0.8<br>2.0                  | V(max)<br>V(min)   |

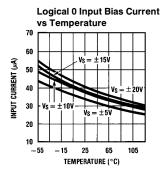

| Digital Input Current<br>Low<br>High     | V <sub>IL</sub> = 0V<br>V <sub>IH</sub> = 5V               | -38<br>0.0001   | -100<br>1                   | - 100<br>1                  | μΑ(max)<br>μΑ(max) |

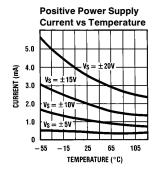

| Positive Power Supply Current            | All Logic Inputs Low                                       | 2               | 5                           | 5                           | mA(max)            |

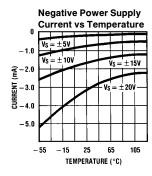

| Negative Power Supply Current            | All Logic Inputs Low                                       | -1.7            | -5                          | -5                          | mA(max)            |

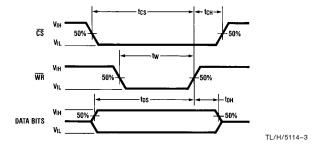

| Write Pulse Width, tW                    | $V_{IL}=0V, V_{IH}=5V$                                     |                 | 150                         |                             | ns(min)            |

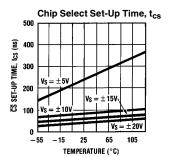

| Chip Select Set-Up Time, t <sub>CS</sub> | $V_{IL}=0V, V_{IH}=5V$                                     |                 | 250                         |                             | ns(min)            |

| Chip Select Hold Time, t <sub>CH</sub>   | $V_{IL}=0V, V_{IH}=5V$                                     |                 | 0                           |                             | ns(min)            |

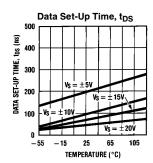

| DIG IN Set-Up Time, t <sub>DS</sub>      | V <sub>IL</sub> =0V, V <sub>IH</sub> =5V                   |                 | 150                         |                             | ns(min)            |

| DIG IN Hold Time, t <sub>DH</sub>        | V <sub>IL</sub> =0V, V <sub>IH</sub> =5V                   |                 | 60                          |                             | ns(min)            |

| Switching Time for Gain Change           | (Note 4)                                                   | 200             |                             |                             | ns(max)            |

| Switch On Resistance                     |                                                            | 3               |                             |                             | kΩ                 |

| Unit Resistance, R                       |                                                            | 15              | 12-18                       |                             | kΩ                 |

| R1 and R2 Mismatch                       |                                                            | 0.3             | 0.5                         | 0.5                         | %(max)             |

| R1/R2 Temperature Coefficient            |                                                            | 0.001           |                             |                             | %/°C               |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: Parameters are specified at  $V^+ = 15V$  and  $V^- = -15V$ . Min  $V^+$  to ground voltage is 5V. Min  $V^+$  to  $V^-$  voltage is 5V. Boldface numbers apply over full operating temperature ranges. All other numbers apply at  $T_A = T_1 = 25^{\circ}C$ .

Note 3: Typicals are at 25°C and represent most likely parametric norm.

Note 4: Guaranteed and 100% production tested.

Note 5: Guaranteed (but not 100% production tested) over the operating temperature. These limits are not used to calculate outgoing quality levels.

Note 6: Settling time for gain change is the switching time for gain change plus settling time (see section on Settling Time).

Note 7:  $\overline{\text{WR}}$  minimum high threshold voltage increases to 2.4V under the extreme conditions when all three digital inputs are simultaneously taken from 0V to 5V at a slew rate of greater than 500V/ $\mu$ S.

#### **GAIN TABLE**

| Digital Input |          |          | Gain             |                  |                  |                  |

|---------------|----------|----------|------------------|------------------|------------------|------------------|

|               |          |          | LF13006          |                  | LF13007          |                  |

| DIG in 3      | DIG in 2 | DIG in 1 | A <sub>OUT</sub> | B <sub>OUT</sub> | A <sub>OUT</sub> | B <sub>OUT</sub> |

| 0             | 0        | 0        | 1                | 1                | 1                | 1                |

| 0             | 0        | 1        | 2                | 1.25             | 1.25             | 1                |

| 0             | 1        | 0        | 4                | 2.5              | 2                | 1.6              |

| 0             | 1        | 1        | 8                | 5                | 5                | 4                |

| 1             | 0        | 0        | 16               | 10               | 10               | 8                |

| 1             | 0        | 1        | 32               | 20               | 20               | 16               |

| 1             | 1        | 0        | 64               | 40               | 50               | 40               |

| 1             | 1        | 1        | 128              | 80               | 100              | 80               |

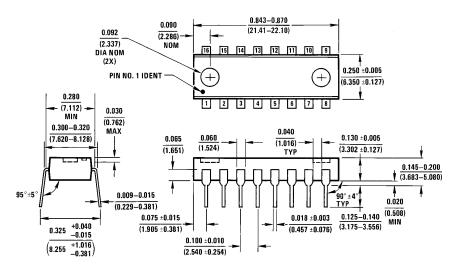

### **Connection Diagram**

# **Switching Waveforms**

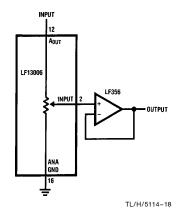

# **Block Diagram and Typical Application** (Continued) (LF13007)

Note: R  $\,\cong\,$  15 k $\Omega$

# **Typical Performance Characteristics**

TL/H/5114-5

# **Application Information**

#### FLOW-THROUGH OPERATION

THE LF13006, LF13007 can be operated with control lines  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  grounded. In this mode new data on the digital inputs will immediately set the new gain value. Input data cannot be latched in this mode.

#### INPUT CURRENT

Current flowing through the input (pin 2) due to bias current of the op amp will result in a gain error due to switch impedance. Normally this error is very small. For example, 10 nA of bias current flowing through 3 k $\Omega$  of switch resistance will result in an error of 30  $\mu V$  at the summing node. However, applications that have significant current flowing through the input must take this effect into account.

#### SETTLING TIME

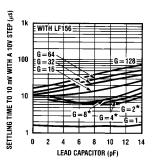

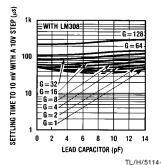

Settling time is a function of the particular op amp used with the LF13006/7 and the gain that is selected. It can be optimized and stability problems can be prevented through the use of a lead capacitor from the inverting input to the output of the amplifier. A lead capacitor is effective whenever the feedback around an amplifier is resistive, whether with discrete resistors or with the LF13006/7. It compensates for the feedback pole created by the parallel resistance and capacitance from the inverting input of the op amp to AC ground.

#### **Settling Time Test Circuit**

TL/H/5114-6

#### **Typical Settling Time Curves**

\* Unstable at C<sub>L</sub> less than 2 pF

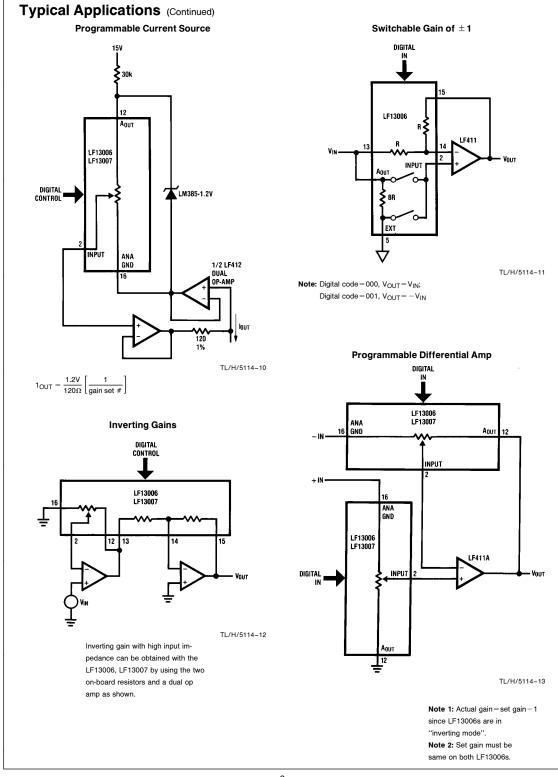

# **Typical Applications**

# Variable Capacitance Multiplier

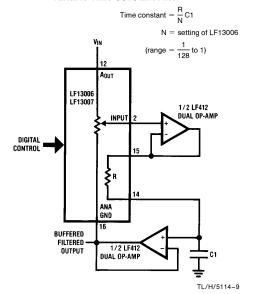

#### Variable Time Constant Filter

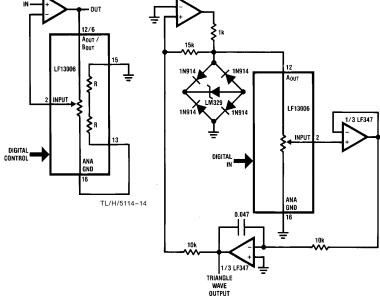

# One Octave per Bit Function Generator

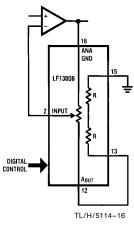

Variable Gains of Almost 1

TL/H/5114-15

|                  |                  | TL/H/5114–15 |       |

|------------------|------------------|--------------|-------|

| GAINS            |                  |              | GAINS |

| A <sub>OUT</sub> | B <sub>OUT</sub> |              | 9     |

| 1                | 1                |              | 1.8   |

| 1.8              | 1.2              |              | 1.29  |

| 3                | 2                |              | 1.125 |

| 4.5              | 3                |              | 1.059 |

| 6                | 4                |              | 1.029 |

| 7.2              | 4.8              |              |       |

| 8                | 5.33             |              | 1.014 |

| 8.47             | 5.65             |              | 1.007 |

|                  |                  |              |       |

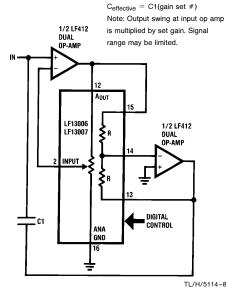

## Programmable Instrumentation Amp

# Attenuator (0 dB to -42 dB in 6 dB steps)

Note 1:  $V_{OUT} = N$  (A-B), N = set gain. Note 2: All 10k resistors 0.1% matched.

# Physical Dimensions inches (millimeters)

Molded Dual-In-Line Package (N)

Order Number LF13006N or LF13007N

NS Package Number N16A

N16A (REV E)

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408