# **FEATURES**

- 111 MHz Data Rate

- 12-bit Data and Coefficients

- On-board Memory for 256 Horizontal and 256 Vertical Coefficient Sets

- LF Interface<sup>™</sup> Allows All 512 Coefficient Sets to be Updated Within Vertical Blanking

- Selectable 12-bit Data Output with User-Defined Rounding and Limiting

- Seven 3K x 12-bit, Programmable Two-Mode Line Buffers

- 16 Horizontal Filter Taps

# DESCRIPTION

- 8 Vertical Filter Taps

- Two Operating Modes: Dimensionally Separate and Orthogonal

- Supports Interleaved Data Streams

- Horizontal Filter Supports Decimation up to 16:1 for Increasing Number of Filter Taps

- 3.3 Volt Power Supply

- 5 Volt Tolerant I/O

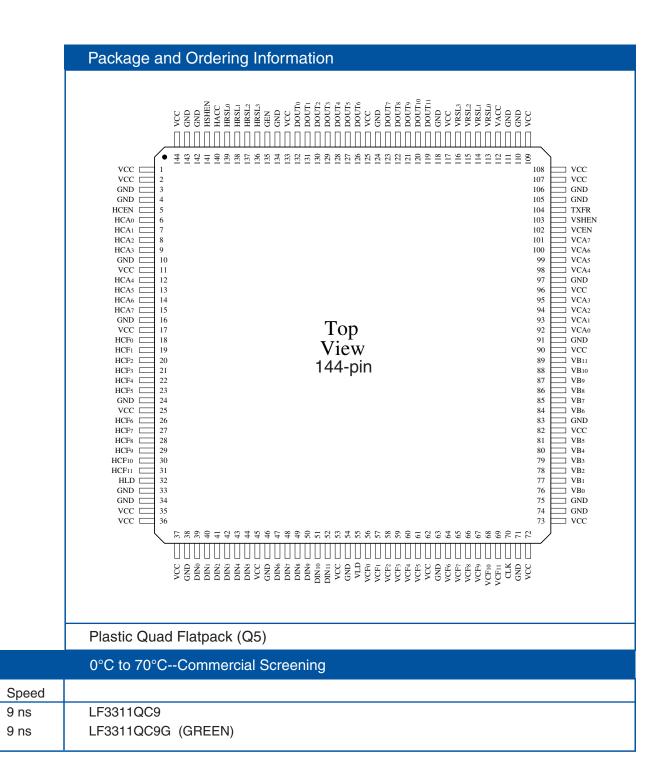

- 144 Lead PQFP

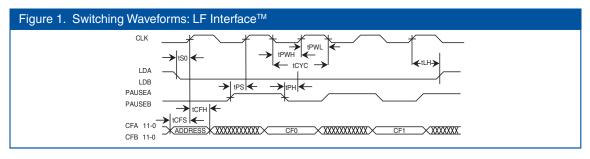

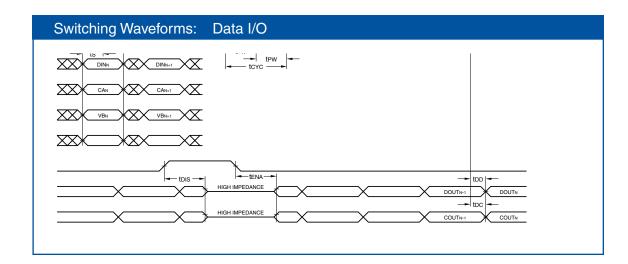

The LF3311 is an improved version of the LF3310 Horizontal/Vertical Digital Image Filter capable of operating at speeds of up to 111MHz. This improved speed will increase flexibility and performance. The added performance will enable you to use this device in more applications. For example, four interleaved data streams of 27MHz can now be processed within one device. The part is functionally identical to the LF3310 with the exception that the filter data path is specified to operate faster than the LF Control Interface. When operating the filter at speeds in excess of 90MHz, loading of coefficients via the LF Interface must be throttled to a maximum of 90MHz by asserting the PAUSE pin as required to allow sufficient setup time for the configuration data provided to the Figure 1 below demonstrates the switching waveforms of case 2, while the switching characteristics are shown in Table 1.

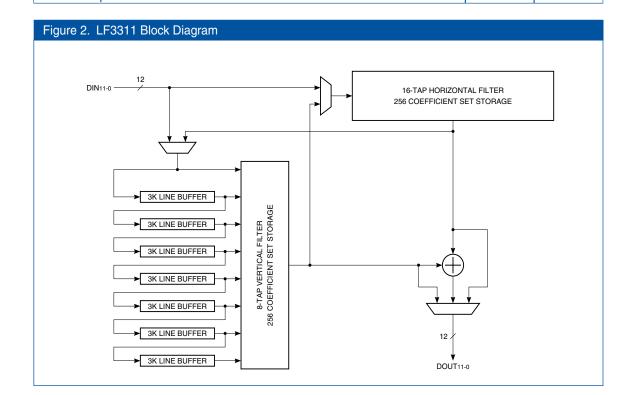

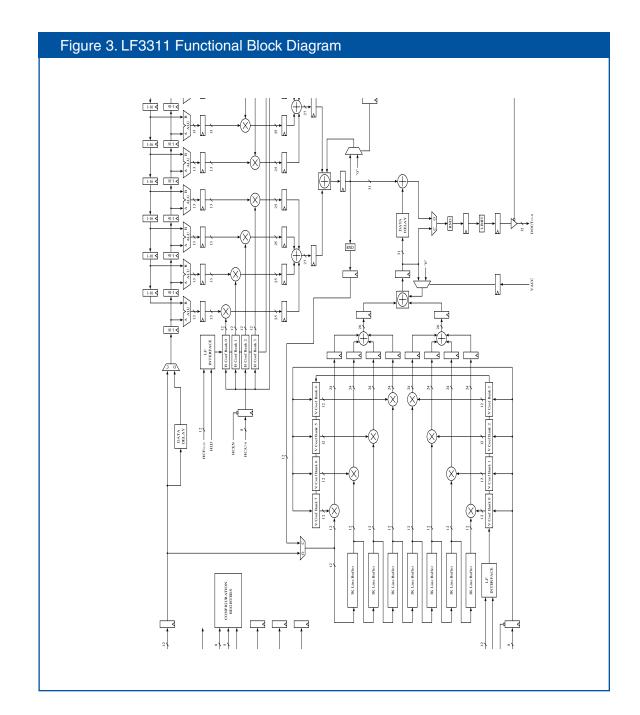

The LF3311 remains a two-dimensional digital image filter capable of filtering data at real-time video rates. The device contains both a horizontal and a vertical filter which may be cascaded or used concurrently for two-dimensional filtering. The input, coefficient, and output data are all 12-bits and in two's complement format. The horizontal filter is designed to take advantage of symmetric coefficient sets. When symmetric coefficient sets are used, the horizontal filter can be configured as a 16-tap FIR filter. When asymmetric coefficient sets are used, it can be configured as an 8-tap FIR filter. The vertical filter is an 8-tap FIR filter with all required line buffers contained on-chip. The line buffers can store video lines with lengths from 4 to 3076 pixels. Horizontal filter Interleave/Decimation Registers (I/D Registers) and the vertical filter line buffers allow interleaved data to be fed directly into the device and filtered without separating the data into individual data streams. The horizontal filter can handle a maximum of sixteen data sets interleaved together. The vertical filter can handle interleaved video lines which contain 3076 or less data values. The I/D Registers and horizontal accumulator facilitate using decimation to increase the number of filter taps in the horizontal filter. It will support a decimation factor of up to 16:1. The device has on-chip storage for 256 horizontal coefficient sets and 256 vertical coefficient sets. Each filter's coefficients are loaded independently of each other allowing one filter's coefficients to be updated without affecting the other filter's coefficients. In addition, a horizontal or vertical coefficient set can be updated independently from the other coefficient sets in the same filter.

| Table 1. Sv  | Table 1. Switching Characteristics          |            |                    |  |

|--------------|---------------------------------------------|------------|--------------------|--|

| Commerc      | cial Operating Range (0°C to <u>+</u> 70°C) |            |                    |  |

|              |                                             | 9 (ns) spe | 9 (ns) speed grade |  |

| Symbol       | Parameter                                   | MIN        | MAX                |  |

| tCYC         | Cycle Time                                  | 9          |                    |  |

| <b>t</b> PWL | Clock Pulse Width Low                       | 4          |                    |  |

| <b>t</b> PWH | Clock Pulse Width High                      | 4          |                    |  |

| tso          | Input Setup Time                            | 4          |                    |  |

| <b>t</b> S1  | Input Setup Time (xCEN, xRSL)               | 4          |                    |  |

| <b>t</b> H0  | Input Hold Time                             | 1          |                    |  |

| <b>t</b> H1  | Input Hold Time (xCEN, xRSL)                | 1.5        |                    |  |

| tD           | Output Delay                                |            | 8                  |  |

| tDIS         | Three-State Output Disable Delay            |            | 10                 |  |

| <b>t</b> ENA | Three-State Output Enable Delay             |            | 10                 |  |

| <b>t</b> CFS | Coefficient Input Setup Time                | 5          |                    |  |

| <b>t</b> CFH | Coefficient input Hold Time                 | 1.5        |                    |  |

| tls          | Load Setup Time                             | 4          |                    |  |

| tlh          | Load Hold Time                              | 1.5        |                    |  |

| <b>t</b> PS  | PAUSE Setup Time                            | 4          |                    |  |

| <b>t</b> PH  | PAUSE Hold time                             | 1.5        |                    |  |

#### **Functional Description**

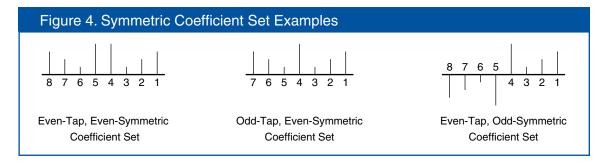

Horizontal Filter The horizontal filter is designed to filter a digital image in the horizontal dimension. This FIR filter can be configured to have as many as 16-taps when symmetric coefficient sets are used and 8-taps when asymmetric coefficient sets are used.

ALU

The ALUs double the number of filter taps available, when symmetric coefficient sets are used, by preadding data values which are then multiplied by a common coefficient (see Figure 4). The ALUs can perform two operations: A+B and B–A. Bit 0 of Configuration Register 0 determines the ALU operation. A+B is used with even-symmetric coefficient sets. B–A is used with odd-symmetric coefficient sets. Also, either the A or B operand may be set to 0. Bits 1 and 2 of Configuration Register 0 control the ALU inputs. A+0 or B+0 are used with asymmetric coefficient sets.

#### **I/D Registers**

The Interleave/Decimation Registers (I/D Registers) feed the ALU inputs. They allow the device to filter up to sixteen data sets interleaved into the same data stream without having to separate the data sets. The I/D Registers should be set to a length equal to the number of data sets interleaved together. For example, if two data sets are interleaved together, the I/D Registers should be set to a length of two. Bits 1 through 4 of Configuration Register 1 determine the I/D Register length.

The I/D Registers also facilitate using decimation to increase the number of filter taps. Decimation by N is accomplished by reading the horizontal filter's output once every N clock cycles. The device supports decimation up to 16:1. With no decimation, the maximum number of filter taps is sixteen. When decimating by N, the number of filter taps becomes 16N because there are N–1 clock cycles when the horizontal filter's output is not being read. The extra clock cycles are used to calculate more filter taps.

When decimating, the I/D Registers should be set to a length equal to the decimation factor. For example, when performing a 4:1 decimation, the I/D Registers should be set to a length of four. When not decimating or when only one data set (non-interleaved data) is fed into the device, the I/D Registers should be set to a length of one.

HSHEN enables or disables the loading of data into the forward and reverse I/D Registers when the device is in Dimensionally Separate Mode (see the HSHEN section for a full discussion). When in Orthogonal Mode, HSHEN also enables or disables the loading of data into the input register (DIN11-0) and the line buffers.

It is important to note that in Orthogonal Mode, either HSHEN or VSHEN can disable the loading of data into the input register (DIN11-0), I/D Registers, and line buffers. Both must be active to enable data loading in Orthogonal Mode.

#### **Functional Description**

#### I/D Register Data Path Control

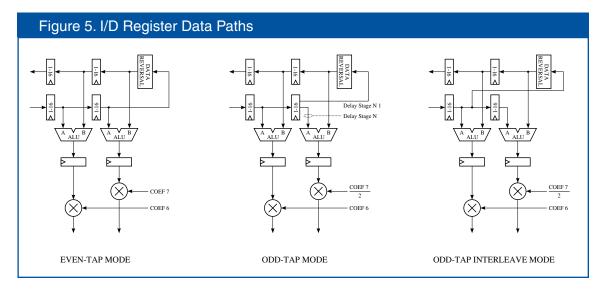

The multiplexer in the middle of the I/D Register data path controls how data is fed to the reverse data path. The forward data path contains the I/D Registers in which data flows from left to right in the block diagram in Figure 1. The reverse data path contains the I/D Registers in which data flows from right to left. When the filter is configured for an even number of taps, data from the last I/D Register in the forward data path is fed into the first I/D Register in the reverse data path (see Figure 5).

When the filter is configured for an odd number of taps, the data which will appear at the output of the last I/D Register in the forward data path on the next clock cycle is fed into the first I/D Register in the reverse data path. Bit 5 in Configuration Register 1 configures the filter for an even or odd number of taps. When interleaved data is fed through the device and an even tap filter is desired, the filter should be configured for an even number of taps (Bit 5 of CR1 set to "0") and the I/D Register length should match the number of data sets interleaved together. When interleaved data is to be fed through the device and an odd tap filter is desired, the filter should be set to Odd-Tap Interleave Mode. Bit 0 of Configuration Register 1 configures the filter for Odd-Tap Interleave Mode. When the filter is configured for Odd-Tap Interleave Mode, data from the next to last I/D Register in the forward data path is fed into the first I/D Register in the reverse data path.

When the filter is configured for an odd number of taps (interleaved or non-interleaved modes), the filter is structured such that the center data value is aligned simultaneously at the A and B inputs of the last ALU in the forward data path. In order to achieve the correct result, the user must divide the coefficient by two.

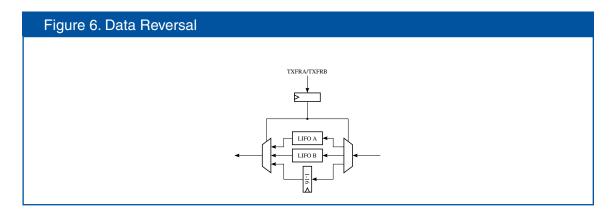

Data reversal Data reversal circuitry is placed after the multiplexer which routes data from the forward data path to the reverse data path (see Figure 6). When decimating, the data stream must be reversed in order for data to be properly aligned at the inputs of the ALUs. When data reversal is enabled, the circuitry uses a pair of LIFOs to reverse the order of the data sent to the reverse data path. When TXFR goes LOW, the LIFO sending data to the reverse data path becomes the LIFO receiving data from the forward data path becomes the LIFO sending data to the reverse data path. The device must see a HIGH to LOW transition of TXFR in order to switch LIFOs. If decimating by N, TXFR should go low once every N clock cycles. When data reversal is disabled, the circuitry functions like an I/D Register. When feeding interleaved data through the filter, data reversal should be disabled. Bit 6 of Configuration Register 1 enables or disables data reversal.

#### **Functional Description**

Horizontal Rounding

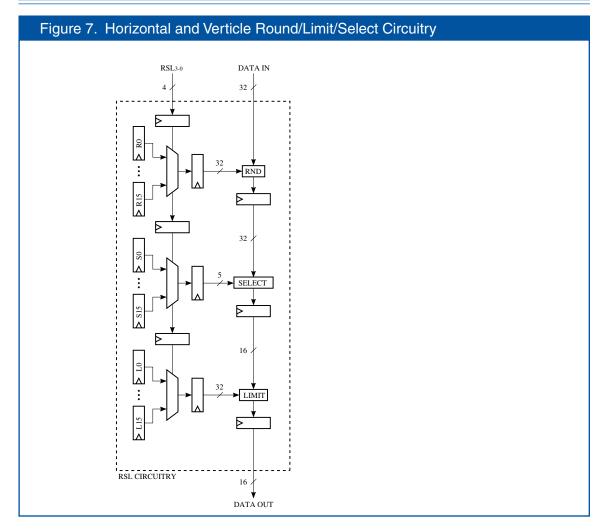

The horizontal filter output may be rounded by adding the contents of one of the sixteen horizontal round registers to the horizontal filter output Wide Output Mode in the Operating Modes section). All programming of the device is done through the Configuration Registers via the 16-bit Configuration/Control Interface. (see Figure 7). Each round register is 32-bits wide and user-programmable. This allows the filter's output to be rounded to any precision required. Since any 32-bit value may be programmed into the round registers, the device can support complex rounding algorithms as well as standard Half-LSB rounding. HRSL3-0 determines which of the sixteen horizontal round registers are used in the rounding operation. A value of 0 on HRSL3-0 selects horizontal round register 0. A value of 1 selects horizontal round register 1 and so on. HRSL3-0 may be changed every clock cycle if desired. This allows the rounding algorithm to be changed every clock cycle. This is useful when filtering interleaved data. If rounding is not desired, a round register should be loaded with 0 and selected as the register used for rounding. Round register loading is discussed in the LF Interface<sup>TM</sup> section.

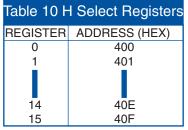

#### **Horizontal Select**

The word width of the horizontal filter output is 32-bits. However, only 12-bits may be sent to the filter output. The horizontal filter select circuitry determines which 12-bits are passed (see Table 20). The horizontal select registers control the horizontal select circuitry. There are sixteen horizontal select registers. Each select register is 5-bits wide and user-programmable. HRSL3-0 determines which of the sixteen horizontal select registers are used in the horizontal select circuitry. A value of 0 on HRSL3-0 selects horizontal select register 0. A value of 1 selects horizontal select register 1 and so on. HRSL3-0 may be changed every clock cycle if desired. This allows the 12-bit window to be changed every clock cycle. This is useful when filtering interleaved data. Select register loading is discussed in the LF Interface™ section.

Horizontal Limiting An output limiting function is provided for the output of the horizontal filter. The horizontal limit registers determine the valid range of output values when limiting is enabled (Bit 1 in Configuration Register 5). There are sixteen 24-bit horizontal limit registers. HRSL3-0 determines which horizontal limit register is used during the limit operation. A value of 0 on HRSL3-0 selects horizontal limit register 0. A value of 1 selects horizontal limit register 1 and so on. Each limit register contains both an upper and lower limit value. If the value fed to the limiting circuitry is less than the lower limit, the lower limit, the upper limit value is passed as the filter output. If the value fed to the limiting circuitry is greater than the upper limit, the upper limit value is passed as the filter output. HRSL3-0 may be changed every clock cycle if desired. This allows the limit range to be changed every clock cycle. This is useful when filtering interleaved data. When loading limit values into the device, the upper limit must be greater than the lower limit. Limit register loading is discussed in the LF Interface™ section.

# **Functional Description**

| Table 2. ( | Table 2. Configuration register 0 - Address 200H |                                         |  |

|------------|--------------------------------------------------|-----------------------------------------|--|

| BITS       | FUNCTION                                         | DESCRIPTION                             |  |

| 0          | ALU Mode                                         | 0 : A + B                               |  |

|            |                                                  | 1 : B – A                               |  |

| 1          | Pass A                                           | 0 : ALU Input A = 0                     |  |

|            |                                                  | 1 : ALU Input A = Forward Register Path |  |

| 2          | Pass B                                           | 0 : ALU Input B = 0                     |  |

|            |                                                  | 1 : ALU Input B = Reverse Register Path |  |

| 11-3       | Reserved                                         | Must be set to "0"                      |  |

#### Functional Description

**Vertical Filter**

The vertical filter is designed to filter a digital image in the vertical dimension. It is a FIR filter which can be configured to have as many as 8-taps.

# Line Buffers There are seven on-chip line buffers. The maximum delay length of each line buffer is 3076 cycles and the minimum is 4 cycles. Configuration Register 2 (CR2) determines the delay length of the line buffers. The line buffer length is equal to the value of CR2 plus 4. A value of 0 for CR2 sets the line buffer length to 4. A value of 3072 for CR2 sets the line buffer length to 3076. Any values for CR2 greater than 3072 are not valid.

The line buffers have two modes of operation: delay mode and recirculate mode. Bit 0 of Configuration Register 3 determines which mode the line buffers are in. In delay mode, the data input to the line buffer is delayed by an amount determined by CR2. In recirculate mode, the output of the line buffer is routed back to the input of the line buffer allowing the line buffer contents to be read multiple times. Bit 1 of Configuration Register 3 allows the line buffers to be loaded in parallel. When Bit 1 is "1", the input register (DIN11-0) loads all seven line buffers in parallel. This allows all the line buffers to be preloaded with data in the amount of time it normally takes to load a single line buffer. VSHEN enables or disables the loading of data into the line buffers when the device is in Dimensionally Separate Mode (see the VSHEN section for a full discussion). When in Orthogonal Mode, VSHEN also enables or disables the loading of data into the input register (DIN11-0) and the forward and reverse I/D It is important to note that in Orthogonal Mode, either HSHEN or VSHEN can disable the loading of data into the input register (DIN11-0), I/D Registers, and line buffers. Both must be active to enable data loading in Orthogonal Mode.

# Interleaved Data The vertical filter is capable of handling interleaved data. The number of data sets it can handle is determined by the number of data values contained in a video line. If the interleaved video line has 3076 data values or less, the vertical filter can handle it no matter how many data sets are interleaved together.

- Vertical Rounding The vertical filter output may be rounded by adding the contents of one of the sixteen vertical round registers to the vertical filter output (see Figure 7). Each round register is 32-bits wide and user-programmable. This allows the filter's output to be rounded to any precision required. Since any 32-bit value may be programmed into the round registers, the device can support complex rounding algorithms as well as standard Half-LSB rounding. VRSL3-0 determines which of the sixteen vertical round registers are used in the rounding operation. A value of 0 on VRSL3-0 selects vertical round register 0. A value of 1 selects vertical round register 1 and so on. VRSL3-0 may be changed every clock cycle if desired. This allows the rounding algorithm to be changed every clock cycle. This is useful when filtering interleaved data. If rounding is not desired, a round register should be loaded with 0 and selected as the register used for rounding. Round register loading is discussed in the LF Interface<sup>™</sup> section.

- Vertical Select The word width of the vertical filter output is 32-bits. However, only 12-bits may be sent to the filter output. The vertical filter select circuitry determines which 12-bits are passed (see Table 20). The vertical select registers control the vertical select circuitry. There are sixteen vertical select registers. Each select registers are used in the vertical select circuitry. A value of 0 on VRSL3-0 selects vertical select register 0. A value of 1 selects vertical select register 1 and so on. VRSL3-0 may be changed every clock cycle if desired. This allows the 12-bit window to be changed every clock cycle. This is useful when filtering interleaved data. Select register loading is discussed in the LF Interface™ section.

#### **Functional Description**

#### **Vertical Limiting**

An output limiting function is provided for the output of the vertical filter. The vertical limit registers determine the valid range of output values when limiting is enabled (Bit 0 in Configuration Register 5). There are sixteen 24-bit vertical limit registers. VRSL3-0 determines which vertical limit register is used during the limit operation. A value of 0 on VRSL3-0 selects vertical limit register 0. A value of 1 selects vertical limit register 1 and so on. Each limit register contains both an upper and lower limit value. If the value fed to the limiting circuitry is less than the lower limit, the lower limit value is passed as the filter output. If the value fed to the limiting circuitry is greater than the upper limit, the upper limit value is passed as the filter output. VRSL3-0 may be changed every clock cycle if desired. This allows the limit range to be changed every clock cycle. This is useful when filtering interleaved data. When loading limit values into the device, the upper limit must be greater than the lower limit. Limit register loading is discussed in the LF Interface<sup>™</sup> section.

| Table 3. Configu | Table 3. Configuration Register 1 - Address 201H |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BITS             | FUNCTION                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 0                | Odd-Tap Interleave Mode                          | 0 : Odd-Tap Interleave Mode Disabled<br>1 : Odd-Tap Interleave Mode Enabled                                                                                                                                                                                                                                                                                                  |  |  |  |

| 4-1              | I/D Register Length                              | 0000: 1 Register   0001: 2 Registers   0010: 3 Registers   0011: 4 Registers   0100: 5 Registers   0101: 6 Registers   0101: 7 Registers   0110: 7 Registers   0110: 7 Registers   1010: 9 Registers   1001: 10 Registers   1001: 10 Registers   1010: 11 Registers   1011: 12 Registers   1010: 13 Registers   1101: 14 Registers   1110: 15 Registers   1111: 16 Registers |  |  |  |

| 5                | Horizontal Tap Number                            | 0 : Even Number of Taps<br>1 : Odd Number of Taps                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6                | Horizontal Data Reversal                         | 0 : Data Reversal Enabled<br>1 : Data Reversal Disabled                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 11-7             | Reserved                                         | Must be set to "0"                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Table 4. Configuration Register 2 - Address 202H |                    |                                     |  |  |

|--------------------------------------------------|--------------------|-------------------------------------|--|--|

| BITS                                             | FUNCTION           | DESCRIPTION                         |  |  |

| 11-0                                             | Line Buffer Length | See Line Buffer Description Section |  |  |

| Table 5. Configuration Register 3 - Address 203H |                  |                      |  |

|--------------------------------------------------|------------------|----------------------|--|

| BITS                                             | FUNCTION         | DESCRIPTION          |  |

| 0                                                | Line Buffer Mode | 0 : Delay Mode       |  |

|                                                  |                  | 1 : Recirculate Mode |  |

| 1                                                | Line Buffer Load | 0 : Normal Load      |  |

|                                                  |                  | 1 : Parallel Load    |  |

| 11-2                                             | Reserved         | Must be set to "0"   |  |

# **Functional Description**

| Table 6. Configuration Register 4 - Adress 204H |                             |                                                |  |  |

|-------------------------------------------------|-----------------------------|------------------------------------------------|--|--|

| BITS                                            | FUNCTION                    | DESCRIPTION                                    |  |  |

| 0                                               | HV Filter Mode              | 0 : Orthogonal Mode                            |  |  |

|                                                 |                             | 1 : Dimensionally Separate                     |  |  |

| 1                                               | HV Direction                | 0 : Horizontal to Vertical                     |  |  |

|                                                 |                             | 1 : Vertical to Horizontal                     |  |  |

| 3-2                                             | Orthogonal Kernel Size      | 00 : 3-3 Kernel                                |  |  |

|                                                 |                             | 01 : 5-5 Kernel                                |  |  |

|                                                 |                             | 10 : 7-7 Kernel                                |  |  |

|                                                 |                             | 11 : Not Used                                  |  |  |

| 4                                               | Limit Register Load Control | 0 : Limit Registers Always Enabled             |  |  |

|                                                 |                             | 1 : Limit Registers Under Shift Enable Control |  |  |

| 11-5                                            | Reserved                    | Must be set to "0"                             |  |  |

| Table 7. Configuration Register 5 - Adress 205H |                         |                                  |  |

|-------------------------------------------------|-------------------------|----------------------------------|--|

| BITS                                            | FUNCTION                | DESCRIPTION                      |  |

| 0                                               | Vertical Limit Enable   | 0 : Vertical Limiting Disabled   |  |

|                                                 |                         | 1 : Vertical Limiting Enabled    |  |

| 1                                               | Horizontal Limit Enable | 0 : Horizontal Limiting Disabled |  |

|                                                 |                         | 1 : Horizontal Limiting Enabled  |  |

| 11-2                                            | Reserved                | Must be set to "0"               |  |

| Tab | Table 8. HCF/VCF11-9 Decode |   |                             |  |

|-----|-----------------------------|---|-----------------------------|--|

| 11  | 10                          | 9 | DESCRIPTION                 |  |

| 0   | 0                           | 0 | Coefficient Banks           |  |

| 0   | 0                           | 1 | Configuration Registers     |  |

| 0   | 1                           | 0 | Horizontal Select Registers |  |

| 0   | 1                           | 1 | Vertical Select Registers   |  |

| 1   | 0                           | 0 | Horizontal Round Registers  |  |

| 1   | 0                           | 1 | Vertical Round Registers    |  |

| 1   | 1                           | 0 | Horizontal Limit Registers  |  |

| 1   | 1                           | 1 | Vertical Limit Registers    |  |

| Table 9 H Round Registers |               | Т |

|---------------------------|---------------|---|

| REGISTER                  | ADDRESS (HEX) | F |

| 0                         | 800           | Γ |

| 1                         | 801           |   |

|                           |               |   |

| 14                        | 80E           |   |

| 15                        | 80F           |   |

|                           |               |   |

| Table 12 V Round Registers |               |  |

|----------------------------|---------------|--|

| REGISTER                   | ADDRESS (HEX) |  |

| 0                          | A00           |  |

| 1                          | A01           |  |

|                            |               |  |

| 14                         | A0E           |  |

| 15                         | A0F           |  |

| Table 13 V Select Registers |               |   |

|-----------------------------|---------------|---|

| REGISTER                    | ADDRESS (HEX) |   |

| 0                           | 600           |   |

| 1                           | 601           |   |

| 14<br>15                    | 60E<br>60E    |   |

| 15                          | 001           | L |

| Table 11 H Limit Registers |  |  |

|----------------------------|--|--|

| ADDRESS (HEX)              |  |  |

| C00                        |  |  |

| C01                        |  |  |

|                            |  |  |

| COE                        |  |  |

| C0F                        |  |  |

|                            |  |  |

| Table 14 | Table 14 V Limit Registers |  |  |  |  |  |

|----------|----------------------------|--|--|--|--|--|

| REGISTER | ADDRESS (HEX)              |  |  |  |  |  |

| 0        | E00                        |  |  |  |  |  |

| 1        | E01                        |  |  |  |  |  |

|          |                            |  |  |  |  |  |

| 14       | EOE                        |  |  |  |  |  |

| 15       | E0F                        |  |  |  |  |  |

#### **Functional Description**

CoefficientThe coefficient banks store the coefficients which feed into the multipliers in the horizontal and vertical<br/>filters. There is a separate bank for each multiplier. Each bank can hold 256 12-bit coefficients. The banks<br/>are loaded using an LF Interface™. There is a separate LF Interface™ for the horizontal and vertical banks.<br/>Coefficient bank loading is discussed in the LF Interface™ section.

Configuration and Control Registers The Configuration Registers determine how the HV Filter operates. Tables 2 through 7 show the formats of the six configuration registers. There are three types of control registers: round, select, and limit. There are sixteen round registers for the horizontal filter and sixteen for the vertical filter. Each register is 32-bits wide. HRSL3-0 and VRSL3-0 determine which horizontal and vertical round registers respectively are used for rounding.

There are sixteen select registers for the horizontal filter and sixteen for the vertical filter. Each register is 5-bits wide. HRSL3-0 and VRSL3-0 determine which horizontal and vertical select registers respectively are used in the select circuitry.

There are sixteen limit registers for the horizontal filter and sixteen for the vertical filter. Each register is 24-bits wide and stores both an upper and lower limit value. The lower limit is stored in bits 11-0 and the upper limit is stored in bits 23-12. HRSL3-0 and VRSL3-0 determine which horizontal and vertical limit registers respectively are used for limiting when limiting is enabled. Configuration and Control Register loading is discussed in the LF Interface<sup>™</sup> section.

LF Interface ™

#### **Functional Description**

The Horizontal and Vertical LF Interface<sup>™</sup> are used to load data into the horizontal and vertical coefficient banks respectively. They are also used to load data into the Configuration and Control Registers. The following section describes how the Horizontal LF Interface<sup>™</sup> works. The Horizontal and Vertical LF Interface<sup>™</sup> are identical in function. If HLD and HCF11-0 are replaced with VLD and VCF11-0, the following section will describe how the Vertical LF Interface<sup>™</sup> works.

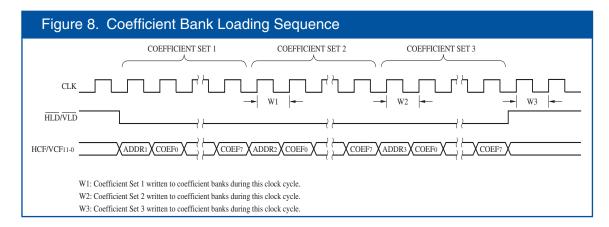

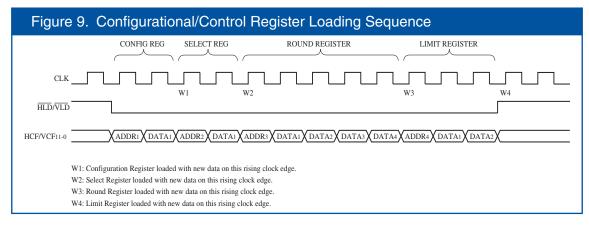

HLD is used to enable and disable the Horizontal LF Interface<sup>™</sup>. When HLD goes LOW, the Horizontal LF Interface<sup>™</sup> is enabled for data input. The first value fed into the interface on HCF11-0 is an address which determines what the interface is going to load. The three most significant bits (HCF11-9) determine if the LF Interface<sup>™</sup> will load coefficient banks or Configuration/Control Registers (see Table 8). The nine least significant bits (HCF8-0) are the address for whatever is to be loaded (see Tables 9-14). For example, to load address 15 of the horizontal coefficient banks, the first data value into the LF Interface<sup>™</sup> should be 00FH. To load horizontal limit register 10, the first data value should be COAH. The first address value should be loaded into the interface on the same clock cycle that latches the HIGH to LOW transition of HLD (see Figures 8 and 9).

The next value(s) loaded into the interface are the data value(s) which will be stored in the bank or register defined by the address value. When loading coefficient banks, the interface will expect eight values to be loaded into the device after the address value. The eight values are coefficients 0 through 7. When loading select or Configuration Registers, the interface will expect one value after the address value. When loading round registers, the interface will expect four values after the address value. When loading limit registers, the interface will expect two values after the address value. Figures 8 and 9 show the data loading sequences for the coefficient banks and Configuration/Control Registers.

#### **Functional Description**

#### LF Interface ™ Continued

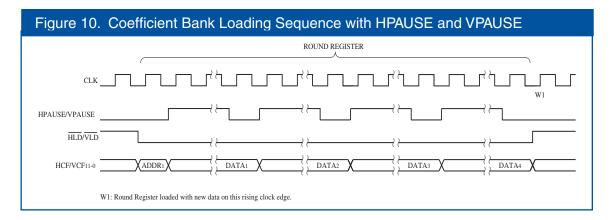

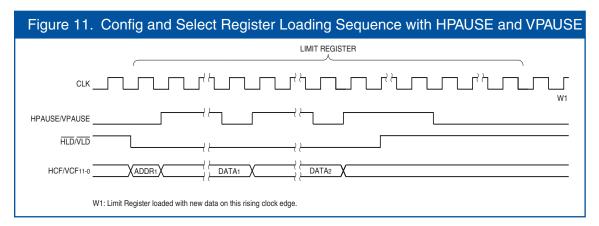

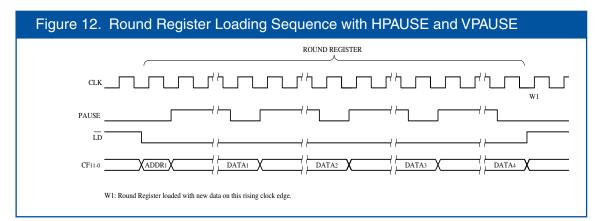

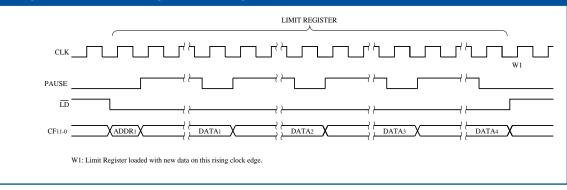

Both HPAUSE and VPAUSE allow the user to effectively slow the rate of data loading through the LF Interface<sup>™</sup>. When HPAUSE is HIGH, the LF Interface<sup>™</sup> affecting the data used for the Horizontal Filter is held until HPAUSE is returned to a LOW. When VPAUSE is HIGH, the LF Interface™ affecting the data used for the Vertical Filter is held until VPAUSE is returned to a LOW. Figures 10 through 13 display the effects of both HPAUSE and VPAUSE while loading coefficient and control data. Table 15 shows an example of loading data into the coefficient banks. The following data values are written into address 10 of coefficient banks 0 through 7: 210H, 543H, C76H, 9E3H, 701H, 832H, F20H, 143H. Table 16 shows an example of loading data into a Configuration Register. Data value 003H is written into Configuration Table 15 shows an example of loading data into the coefficient banks. The following data values are written into address 10 of coefficient banks 0 through 7: 210H, 543H, C76H, 9E3H, 701H, 832H, F20H, 143H. Table 16 shows an example of loading data into a Configuration Register. Data value 003H is written into Configuration Register 4. Table 17 shows an example of loading data into a round register. Data value 7683F4A2H is written into horizontal round register 12. Table 18 shows an example of loading data into a select register. Data value 00FH is loaded into horizontal select register 2. Table 19 shows an example of loading data into vertical limit register 7. Data value 390H is loaded as the lower limit and 743H is loaded as the upper limit. It takes 9S clock cycles to load S coefficient sets into the device. Therefore, it takes 2304 clock cycles to load all 256 coefficient sets. Assuming an 83 MHz clock rate, all 256 coefficient sets can be updated in 28.8 µs, which is well within vertical blanking time. It takes 5S or 3S clock cycles to load S round or limit registers respectively. Therefore, it takes 256 clock cycles to update all round and limit registers (both horizontal and vertical). Assuming an 83 MHz clock rate, all horizontal and vertical Round/Limit registers can be updated in 3.08 µs.

#### Figure 13. Round Register Loading Sequence with HPAUSE and VPAUSE

# Functional Description

| Table 15. Coe      | Table 15. Coefficient Bank Loading Format |         |        |        |        |        |        |        |        |        |        |        |

|--------------------|-------------------------------------------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|                    | H/VCF11                                   | H/VCF10 | H/VCF9 | H/VCF8 | H/VCF7 | H/VCF6 | H/VCF5 | H/VCF4 | H/VCF3 | H/VCF2 | H/VCF1 | H/VCF0 |

| 1st Word - Address | 0                                         | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 1      | 0      |

| 2nd Word - Bank 0  | 0                                         | 0       | 1      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      | 0      |

| 3rd Word - Bank 1  | 0                                         | 1       | 0      | 1      | 0      | 1      | 0      | 0      | 0      | 0      | 1      | 1      |

| 4th Word - Bank 2  | 1                                         | 1       | 0      | 0      | 0      | 1      | 1      | 1      | 0      | 1      | 1      | 0      |

| 5th Word - Bank 3  | 1                                         | 0       | 0      | 1      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 1      |

| 6th Word - Bank 4  | 0                                         | 1       | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      |

| 7th Word - Bank 5  | 1                                         | 0       | 0      | 0      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 0      |

| 8th Word - Bank 6  | 1                                         | 1       | 1      | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 0      | 0      |

| 9th Word - Bank 7  | 0                                         | 0       | 0      | 1      | 0      | 1      | 0      | 0      | 0      | 0      | 1      | 1      |

| Table 16. Cor      | Table 16. Configuration Register Loading Format |         |         |         |         |         |         |         |         |         |         |         |

|--------------------|-------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|                    | CFA/B11                                         | CFA/B10 | CFA/B 9 | CFA/B 8 | CFA/B 7 | CFA/B 6 | CFA/B 5 | CFA/B 4 | CFA/B 3 | CFA/B 2 | CFA/B 1 | CFA/B 0 |

| 1st Word - Address | 0                                               | 0       | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       |

| 2nd Word - Data    | 0                                               | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| Table 17. Round Register Loading Format |         |         |         |         |         |         |         |         |         |         |         |         |

|-----------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|                                         | CFA/B11 | CFA/B10 | CFA/B 9 | CFA/B 8 | CFA/B 7 | CFA/B 6 | CFA/B 5 | CFA/B 4 | CFA/B 3 | CFA/B 2 | CFA/B 1 | CFA/B 0 |

| 1st Word - Address                      | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 1       | 0       | 0       |

| 2nd Word - Data                         | R       | R       | R       | R       | 0       | 1       | 0       | 1       | 0       | 0       | 1       | 0       |

| 3rd Word - Data                         | R       | R       | R       | R       | 1       | 1       | 1       | 1       | 0       | 1       | 0       | 0       |

| 4th Word - Data                         | R       | R       | R       | R       | 1       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| 5th Word - Data                         | R       | R       | R       | R       | 0 **    | 1       | 1       | 1       | 0       | 1       | 1       | 0       |

| - | Table 18. Select Register Loading Format |         |         |         |         |         |         |         |         |         |         |         |         |

|---|------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|   |                                          | CFA/B11 | CFA/B10 | CFA/B 9 | CFA/B 8 | CFA/B 7 | CFA/B 6 | CFA/B 5 | CFA/B 4 | CFA/B 3 | CFA/B 2 | CFA/B 1 | CFA/B 0 |

|   | 1st Word - Address                       | 0       | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       |

|   | 2nd Word - Data                          | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 1       | 1       | 1       |

#### Table 19. Limit Register Loading Format

|                    | H/VCF11 | H/VCF10 | H/VCF9 | H/VCF8 | H/VCF7 | H/VCF6 | H/VCF5 | H/VCF4 | H/VCF3 | H/VCF2 | H/VCF1 | H/VCF0 |

|--------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 1st Word - Address | 1       | 1       | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      |

| 2nd Word - Data    | 0*      | 0       | 1      | 1      | 1      | 0      | 0      | 1      | 0      | 0      | 0      | 0      |

| 3rd Word - Data    | 0**     | 1       | 1      | 1      | 0      | 1      | 0      | 0      | 0      | 0      | 1      | 1      |

\* This bit represents the MSB of the Lower Limit.

\*\* This bit represents the MSB of the Upper Limit.

#### LF Interface ™ Continued

The coefficient banks and Configuration/Control Registers are not loaded with data until all data values for the specified address are loaded into the LF InterfaceTM. In other words, the coefficient banks are not written to until all eight coefficients have been loaded into the LF InterfaceTM. A round register is not written to until all four data values are loaded. After the last data value is loaded, the interface will expect a new address value on the next clock cycle. After the next address value is loaded, data loading will begin again as previously discussed. As long as data is loaded into the interface, HLD must remain LOW. After all desired coefficient banks and Configuration/Control Registers are loaded with data, the LF InterfaceTM must be disabled. This is done by setting HLD HIGH on the clock cycle after the clock cycle which latches the last data value. It is important that the LF InterfaceTM remain disabled when not loading data into it.

#### **Functional Description**

LF Interface ™ Continued The horizontal coefficient banks may only be loaded with the Horizontal LF InterfaceTM and the vertical coefficient banks may only be loaded with the Vertical LF InterfaceTM. The Configuration and Control Registers may be loaded with either the Horizontal or Vertical LF InterfacesTM. Since both LF InterfacesTM operate independently of each other, both LF InterfacesTM can load data into their respective coefficient banks at the same time. Or, one LF InterfaceTM can load the Configuration/Control Registers while the other loads it's respective coefficient banks. If both LF InterfacesTM are used to load a configuration or control register at the same time, the Vertical LF InterfaceTM will be given priority over the Horizontal LF InterfaceTM. For example, if the Horizontal LF InterfaceTM attempts to load a horizontal round register, the Vertical LF InterfaceTM will be allowed to load the round register while the Horizontal LF InterfaceTM will be allowed to load the Configuration Register. However, the Horizontal LF InterfaceTM will continue to function as if the write occurred.

#### **Operating Modes**

#### Dimensionally Seperate Mode

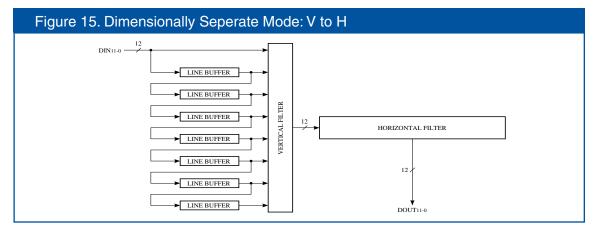

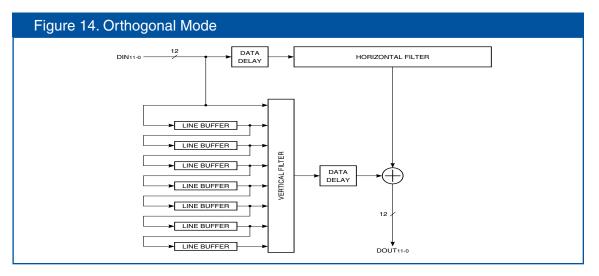

In Dimensionally Separate Mode, the horizontal and vertical filters are cascaded together to form a twodimensional image filter (see Figures 14 and 15). Bit 1 in Configuration Register 4 determines the cascade order. If this bit is set to "0", data on DIN11-0 is fed into the horizontal filter first. The horizontal filter then feeds data into the vertical filter. If this bit is set to "1", data on DIN11-0 is fed into the vertical filter first. The vertical filter then feeds data into the horizontal filter.

#### **Operating Modes**

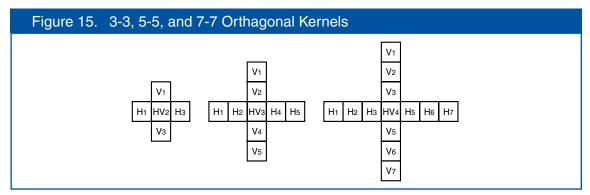

#### Orthogonal Mode

In Orthogonal Mode, the horizontal and vertical filters are used concurrently to implement an orthogonal kernel on the input data (see Figure 16). The HV Filter can handle kernel sizes of 3-3, 5-5, and 7-7 (see Figure 17). Data delay elements at the input of the horizontal filter and the output of the vertical filter are used to properly align data so that the orthogonal kernel is implemented correctly. The data delays are automatically set to the correct lengths based on the programmed length of the line buffers and the kernel size.

Kernel sizes of 3-3, 5-5, and 7-7 require that the horizontal filter's output be delayed by LB – 2, 2(LB) – 3, and 3(LB) - 4 clock cycles respectively before being added to the vertical filter's output (LB is the programmed line buffer length). The data delay at the input of the horizontal filter handles the LB, 2(LB), and 3(LB) delays. The data delay at the output of the vertical filter handles the -2, -3, and -4 delays. For example, if the line buffers are programmed for a length of 720 and a 5–5 kernel is selected, the horizontal filter input data delay will be 1440 clock cycles and the vertical filter output data delay will be 3 clock cycles.

It is important to note that the first 3, 5, or 7 multipliers of the horizontal and vertical filters must be used in Orthogonal Mode. If other multipliers are used, data from the horizontal and vertical filters will not line up correctly because the data delays are calculated assuming that the first 3, 5, or 7 multipliers are used. Also, the ALUs in the horizontal filter should be configured to accept data from the forward I/D Register path into ALU Input A and force ALU Input B to 0.

# Signal Definitions

| Power  | <i>Vcc and GND</i><br>+3.3 V power supply. All pins must be connected.                                                                                                                                                                                                                                                                                    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock  | <i>CLK — Master Clock</i><br>The rising edge of CLK strobes all enabled registers.                                                                                                                                                                                                                                                                        |

| Inputs | <i>DIN11-0 — Data Input</i><br>DIN11-0 is the 12-bit data input port to Filter A. In Dual Filter Mode, DIN11-0 can also be the 12-bit input port<br>to Filter B. Data is latched on the rising edge of clock.                                                                                                                                             |

|        | HCF11-0 — Horizontal Coefficient Input<br>HCF11-0 is used to load data into the horizontal coefficient banks and the Configuration/Control Registers.<br>Data present on HCF11-0 is latched into the Horizontal LF Interface <sup>™</sup> on the rising edge of CLK when HLD<br>is LOW (see the LF Interface <sup>™</sup> section for a full discussion). |

|        | HCA7-0 — Horizontal Coefficient Address<br>HCA7-0 determines which row of data in the horizontal coefficient banks is fed to the multipliers in the<br>horizontal filter. HCA7-0 is latched into the Horizontal Coefficient Address Register on the rising edge of<br>CLK when HCEN is LOW.                                                               |

|        | VCF11-0 — Vertical Coefficient Input<br>VCF11-0 is used to load data into the vertical coefficient banks and the Configuration/Control Registers.<br>Data present on VCF11-0 is latched into the Vertical LF Interface <sup>™</sup> on the rising edge of CLK when VLD is<br>LOW (see the LF Interface <sup>™</sup> section for a full discussion).       |

#### VCA7-0 — Vertical Coefficient Address

VCA7-0 determines which row of data in the vertical coefficient banks is fed to the multipliers in the vertical filter. VCA7-0 is latched into the Vertical Coefficient Address Register on the rising edge of CLK when VCEN is LOW.

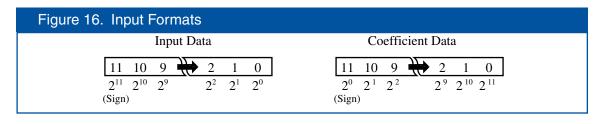

# Figure 17. Accumulator Output Formats Accumulator Output $31 \ 30 \ 29 \ 2 \ 1 \ 0$ $2^{20} \ 2^{19} \ 2^{18} \ 2^{9} \ 2^{10} \ 2^{11}$ (Sign)

# Signal Definitions

| Table 20. C | Output Fo | ormats |     |       |     |     |       |     |     |     |

|-------------|-----------|--------|-----|-------|-----|-----|-------|-----|-----|-----|

| SLCT4-0     | S15       | S14    | S13 |       | S8  | S7  |       | S2  | S1  | S0  |

| 00000       | F15       | F14    | F13 |       | F8  | F7  |       | F2  | F1  | F0  |

| 00001       | F16       | F15    | F14 |       | F9  | F8  |       | F3  | F2  | F1  |

| 00010       | F17       | F16    | F15 |       | F10 | F9  |       | F4  | F3  | F2  |

| •           | •         | •      | •   |       | •   | •   |       | •   | •   | •   |

| •           | •         | •      | •   |       | •   | •   |       | •   | •   | •   |

| •           | •         | •      | •   |       | •   | •   |       | •   | •   | •   |

| 01110       | F29       | F28    | F27 |       | F22 | F21 |       | F16 | F15 | F14 |

| 01111       | F30       | F29    | F28 |       | F23 | F22 |       | F17 | F16 | F15 |

| 10000       | F31       | F30    | F29 | • • • | F24 | F23 | • • • | F18 | F17 | F16 |

#### Outputs DOUT11-0 — Data Output

DOUT11-0 is the 12-bit registered data output port.

#### Controls HLD — Horizontal Coefficient Load

When HLD is LOW, data on HCF11-0 is latched into the Horizontal LF Interface<sup>™</sup> on the rising edge of CLK. When HLD is HIGH, data can not be latched into the Horizontal LF Interface<sup>™</sup>. When enabling the LF Interface<sup>™</sup> for data input, a HIGH to LOW transition of HLD is required in order for the input circuitry to function properly. Therefore, HLD must be set HIGH immediately after power up to ensure proper operation of the input circuitry (see the LF Interface<sup>™</sup> section for a full discussion).

#### HCEN — Horizontal Coefficient Address Enable

When HCEN is LOW, data on HCA7-0 is latched into the Horizontal Coefficient Address Register on the rising edge of CLK. When HCEN is HIGH, data on HCA7-0 is not latched and the register's contents will not be changed.

#### VLD — Vertical Coefficient Load

When VLD is LOW, data on VCF11-0 is latched into the Vertical LF Interface<sup>™</sup> on the rising edge of CLK. When VLD is HIGH, data can not be latched into the Vertical LF Interface<sup>™</sup>. When enabling the LF Interface<sup>™</sup> for data input, a HIGH to LOW transition of VLD is required in order for the input circuitry to function properly. Therefore, VLD must be set HIGH immediately after power up to ensure proper operation of the input circuitry (see the LF Interface<sup>™</sup> section for a full discussion).

#### VCEN — Vertical Coefficient Address Enable

When VCEN is LOW, data on VCA7-0 is latched into the Vertical Coefficient Address Register on the rising edge of CLK. When VCEN is HIGH, data on VCA7-0 is not latched and the register's contents will not be changed.

#### TXFR — Horizontal Filter LIFO Transfer Control

TXFR is used to change which LIFO in the data reversal circuitry sends data to the reverse data path and which LIFO receives data from the forward data path. When TXFR goes LOW, the LIFO sending data to the reverse data path becomes the LIFO receiving data from the forward data path, and the LIFO receiving data from the forward data path, and the LIFO receiving data from the forward data path. The device must see a HIGH to LOW transition of TXFR in order to switch LIFOs.

#### **Signal Definitions**

Controls Continued

#### n- HACC — Horizontal Accumulator Control

When HACC is HIGH, the horizontal accumulator is enabled for accumulation and the accumulator output register is disabled for loading. When HACC is LOW, no accumulation is performed and the accumulator output register is enabled for loading. HACC is latched on the rising edge of CLK.

#### VACC — Vertical Accumulator Control

When VACC is HIGH, the vertical accumulator is enabled for accumulation and the accumulator output register is disabled for loading. When VACC is LOW, no accumulation is performed and the accumulator output register is enabled for loading. VACC is latched on the rising edge of CLK.

#### HSHEN — Horizontal Shift Enable

HSHEN enables or disables the loading of data into the forward and reverse I/D Registers in the horizontal filter when the device is in Dimensionally Separate Mode. If the device is configured such that the horizontal filter feeds the vertical filter, HSHEN also enables or disables the loading of data into the input register (DIN11-0). If the device is configured such that the vertical filter feeds the horizontal filter and the vertical limit register is under shift control, HSHEN also enables or disables the loading of data into the vertical limit register in the vertical Round/Select/Limit circuitry. In Orthogonal Mode, HSHEN also enables or disables the loading of data into the vertical limit to note that in Orthogonal Mode, either HSHEN or VSHEN can disable data loading. Both must be active to enable data loading in Orthogonal Mode. Also in Orthogonal Mode, the horizontal and vertical limit registers can not be disabled.

When HSHEN is LOW, data is loaded into and shifted through the registers HSHEN controls and the forward and reverse I/D Registers on the rising edge of CLK. When HSHEN is HIGH, data is not loaded into or shifted through the registers HSHEN controls and the I/D Registers, and their contents will not be changed. HSHEN is latched on the rising edge of CLK.

#### VSHEN — Vertical Shift Enable

VSHEN enables or disables the loading of data into the line buffers in the vertical filter when the device is in Dimensionally Separate Mode. If the device is configured such that the vertical filter feeds the horizontal filter, VSHEN also enables or disables the loading of data into the input register (DIN11-0). If the device is configured such that the horizontal filter feeds the vertical filter and the horizontal limit register is under shift control, VSHEN also enables or disables the loading of data into the horizontal limit register in the horizontal filter feeds the vertical filter and the horizontal limit register is under shift control, VSHEN also enables or disables the loading of data into the horizontal limit register in the horizontal Round/Select/Limit circuitry. In Orthogonal Mode, VSHEN also enables or disables the loading of data into the input register (DIN11-0) and the forward and reverse I/D Registers in the horizontal filter. It is important to note that in Orthogonal Mode, either HSHEN or VSHEN can disable data loading. Both must be active to enable data loading in Orthogonal Mode. Also in Orthogonal Mode, the horizontal and vertical limit registers can not be disabled.

When VSHEN is LOW, data is loaded into and shifted through the registers VSHEN controls and the line buffers on the rising edge of CLK. When VSHEN is HIGH, data is not loaded into or shifted through the registers VSHEN controls and the line buffers, and their contents will not be changed. VSHEN is latched on the rising edge of CLK.

#### **Signal Definitions**

#### Controls Cont'd

#### d HRSL3-0 — Horizontal Round/Select/Limit Control

HRSL3-0 determines which of the sixteen user-programmable Round/Select/Limit registers (RSL registers) are used in the horizontal Round/Select/Limit circuitry (RSL circuitry). A value of 0 on HRSL3-0 selects RSL register 0. A value of 1 selects round/select/limit register 1 and so on. HRSL3-0 is latched on the rising edge of CLK (see the horizontal round, select, and v limit sections for a complete discussion).

#### VRSL3-0 — Vertical Round/Select/Limit Control

VRSL3-0 determines which of the sixteen user-programmable RSL registers are used in the vertical RSL circuitry. A value of 0 on VRSL3-0 selects RSL register 0. A value of 1 selects RSL register 1 and so on. VRSL3-0 is latched on the rising edge of CLK (see the vertical round, select, and limit sections for a complete discussion).

#### OE — Output Enable

When  $\overline{OE}$  is LOW, DOUT11-0 is enabled for output. When  $\overline{OE}$  is HIGH, DOUT11-0 is placed in a high-impedance state.

#### HPAUSE — LF InterfaceTM Pause

When HPAUSE is HIGH, the Horizontal LF Interface<sup>™</sup> loading sequence is halted until HPAUSE is returned to a LOW state. This effectively allows the user to load coefficients and Control Registers at a slower rate than the master clock (see the LF Interface<sup>™</sup> section for a full discussion).

#### VPAUSE — LF InterfaceTM Pause

When VPAUSE is HIGH, the Vertical LF Interface<sup>™</sup> loading sequence is halted until VPAUSE is returned to a LOW state. This effectively allows the user to load coefficients and Control Registers at a slower rate than the master clock (see the LF Interface<sup>™</sup> section for a full discussion).

# **Specifications**

| Maximum Ratings - Above which useful life may be impaired (Notes | 1,2,3,8)        |

|------------------------------------------------------------------|-----------------|

| Storage temperature                                              | –65°C to +150°C |

| Operating ambient temperature                                    | –55°C to +125°C |

| $VCC_{o}$ supply voltage with respect to ground                  | –0.5V to +4.5V  |

| Input signal with respect to ground                              | –0.5V to 5.5 V  |

| Signal applied to high impedance output                          | –0.5V to 5.5 V  |

| Output current into low outputs                                  | 25 mA           |

| Latchup current                                                  | > 400 mA        |

| ESD Classification (MIL-STD-883E METHOD 3015.7)                  | Class 3         |

| Operating Conditions - To meet specified electrical and switching characteristics |                             |                                                        |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| Mode                                                                              | Temperature Range (Ambient) | Supply Voltage                                         |  |  |  |  |  |  |

| Active Operation, Commercial                                                      | 0°C to +70°C                | $3.00'V \le VCC_{0} \le 3.60V$                         |  |  |  |  |  |  |

| Active Operation, Military                                                        | -55°C to +125°C             | $3.00 \text{V} \leq \text{VCC}_{0} \leq 3.60 \text{V}$ |  |  |  |  |  |  |

| Elect        | Electrical Characteristics - Over Operating Conditions (Note 4) |                                                         |     |     |             |      |  |  |  |  |

|--------------|-----------------------------------------------------------------|---------------------------------------------------------|-----|-----|-------------|------|--|--|--|--|

| Symbol       | Parameter                                                       | Test Condition                                          | Min | Тур | Мах         | Unit |  |  |  |  |

| <b>V</b> он  | Output High Voltage                                             | Vcc = Min., IOH = -4 mA                                 | 2.4 |     |             | V    |  |  |  |  |

| VOL          | Output Low Voltage                                              | <b>V</b> CC = Min., <b>I</b> OL = 8.0 mA                |     |     | 0.4         | V    |  |  |  |  |

| VIH          | Input High Voltage                                              |                                                         | 2.0 |     | 5.5         | V    |  |  |  |  |

| VIL          | Input Low Voltage                                               | (Note 3)                                                | 0.0 |     | 0.8         | V    |  |  |  |  |

| lix          | Input Current                                                   | Ground $\leq$ <b>V</b> IN $\leq$ <b>V</b> CC (Note 12)  |     |     | <u>+</u> 10 | μA   |  |  |  |  |

| loz          | Output Leakage Current                                          | Ground $\leq$ <b>V</b> OUT $\leq$ <b>V</b> CC (Note 12) |     |     | <u>+</u> 10 | μA   |  |  |  |  |

| ICC1         | VCC Current, Dynamic                                            | (Notes 5, 6)                                            |     |     | 250         | mA   |  |  |  |  |

| ICC2         | VCC Current, Quiescent                                          | (Note 7)                                                |     |     | 2           | mA   |  |  |  |  |

| CIN          | Input Capacitance                                               | <b>T</b> A = 25°C, f = 1 MHz                            |     |     | 10          | pF   |  |  |  |  |

| <b>C</b> ουτ | Output Capacitance                                              | <b>T</b> A = 25°C, f = 1 MHz                            |     |     | 10          | pF   |  |  |  |  |

#### Notes

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This device provides hard clamping of transient undershoot. Input levels below ground will be clamped beginning at -0.6V. The device can withstand indefinite operation with inputs or outputs in the range of -0.5V to +5.5V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

5. Supply current for a given application can be accurately approximated by:

| where | NCV <sup>2</sup> F | N = total number of device outputs<br>C = capacitive load per output |

|-------|--------------------|----------------------------------------------------------------------|

| where | 4                  | V = supply voltage<br>F = clock frequency                            |

6. Tested with outputs changing every cycle and no load, at a 40 MHz clock rate.

7. Tested with all inputs within 0.1 V of VCC or Ground, no load.

8. These parameters are guaranteed but not 100% tested.

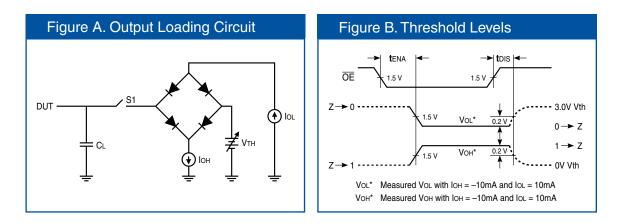

9. AC specifications are tested with input transition times less than 3ns, output reference levels of 1.5V (except tDIS test), and input levels of nominally 0 to 3.0V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

a. A 0.1  $\mu$ F ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

c. Input voltages on a test fixture should be adjusted to compensate for inductive ground and VCC noise to maintain required DUT input levels relative to the DUT ground pin.

10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

#### Notes

11. For the tENA test, the transition is measured to the 1.5V crossing point with datasheet loads. For the tDIs test, the transition is measured to the  $\pm 200$ mV level from the measured steady-state output voltage with  $\pm 10$ mA loads. The balancing voltage, VTH, is set at 3.0 V for Z-to-0 and 0-to-Z tests, and set at 0 V for Z-to-1 and 1-to-Z tests.

12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

LOGIC Devices Incorporated reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. LOGIC Devices does not assume any liability arising out of the application or use of any product or circuit described herein. In no event shall any liability exceed the purchase price of LOGIC Devices products. LOGIC Devices products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with LOGIC Devices. Furthermore, LOGIC Devices does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user.