# Preliminary Data Sheet January 1998

# microelectronics group

# LG1628AXA SONET/SDH 2.488 Gbits/s Transimpedance Amplifier

**Bell Labs Innovations**

**Lucent Technologies**

### Features

- High data rate: 2.5 Gbits/s

- High gain: 5.8 kΩ transimpedance

- Complementary 50 Ω outputs

- Low noise

- Ultrawide dynamic range

- Single –5.2 V ECL power supply

# **Applications**

- SONET/SDH receivers

- SONET/SDH test equipment

- Digital video transmission

# **Functional Description**

The Lucent Technologies Microelectronics Group LG1628AXA is a hybrid integrated circuit that combines the Lucent LG1628A gallium arsenide (GaAs) transimpedance amplifier chip with an external Si dual operational amplifier and necessary filtering to achieve an ultrawide dynamic range amplifier. The LG1628AXA is capable of handling input currents from 3  $\mu$ Aavg to 4 mAavg (patent pending). Amplifier operation is from a single –5.2 V power supply. The targeted transmission system is SONET OC-48 and SDH STM-16.

A complete receiver/regenerator can be constructed with an LG1628AXA followed by an LG1605 limiting amplifier and LG1600 clock and data regenerator.

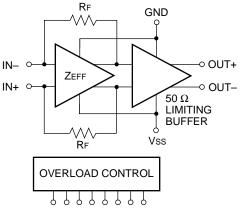

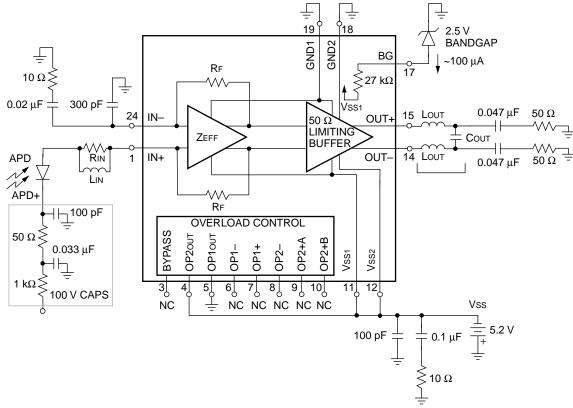

Figure 1 shows the block diagram of the LG1628AXA transimpedance amplifier. The amplifier consists of a 4.2 k $\Omega$  differential transimpedance stage followed by a limiting buffer that provides complementary 50  $\Omega$  outputs.

5-5329(F)

Figure 1. LG1628AXA Functional Diagram

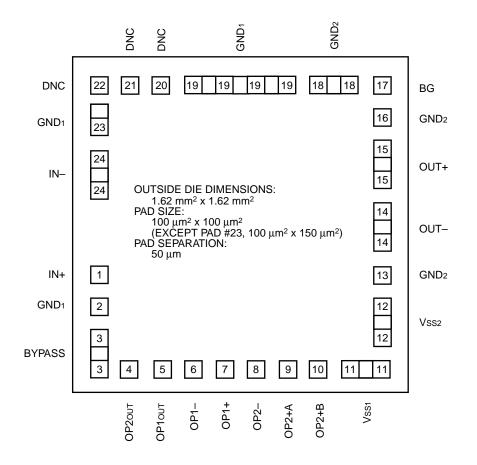

# **Die Pad Configuration**

The die pad configuration is shown in Figure 2.

Figure 2. Die Pad Configuration

5-5336(F)r.2

# Die Pad Configuration (continued)

The pad descriptions for the LG1628AXA are given in Table 1.

#### Table 1. Pad Descriptions

| Pad        | Symbol | Description                                                                                                                                                          |  |  |  |  |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1          | IN+    | Amplifier input; connect to detector anode, current should enter this node.                                                                                          |  |  |  |  |

| 2, 19, 23  | GND1   | Ground.                                                                                                                                                              |  |  |  |  |

| 3          | BYPASS | Connections between these nodes and an external dual op amp form the over-                                                                                           |  |  |  |  |

| 4          | OP2OUT | load control circuitry. See the test circuit in Figure 4 for wiring details.                                                                                         |  |  |  |  |

| 5          | OP1out | To operate the amplifier without overload control connect OP2OUT to VSS,<br>OP1OUT to GND, and leave BYPASS and the remaining op amp connections<br>open (Figure 5). |  |  |  |  |

| 6          | OP1-   |                                                                                                                                                                      |  |  |  |  |

| 7          | OP1+   | – open (rigure 3).                                                                                                                                                   |  |  |  |  |

| 8          | OP2–   |                                                                                                                                                                      |  |  |  |  |

| 9          | OP2+A  |                                                                                                                                                                      |  |  |  |  |

| 10         | OP2+B  |                                                                                                                                                                      |  |  |  |  |

| 11         | VSS1   | Supply voltage; –5.2 Vdc nominal.                                                                                                                                    |  |  |  |  |

| 12         | VSS2   | Supply voltage; –5.2 Vdc nominal.                                                                                                                                    |  |  |  |  |

| 13, 16, 18 | GND2   | Ground.                                                                                                                                                              |  |  |  |  |

| 14         | OUT–   | Inverted data output (produces low-level output for current entering IN+).                                                                                           |  |  |  |  |

| 15         | OUT+   | Noninverted data output (produces high-level output for current entering IN+).                                                                                       |  |  |  |  |

| 17         | BG     | Connection for external –2.5 Vdc voltage reference (typically use an Si band-<br>gap).                                                                               |  |  |  |  |

| 20, 21, 22 | DNC    | Do not connect; internal test point or reserved for future use.                                                                                                      |  |  |  |  |

| 24         | IN–    | Inverting input; must provide ac bypass to ground when using overload control.                                                                                       |  |  |  |  |

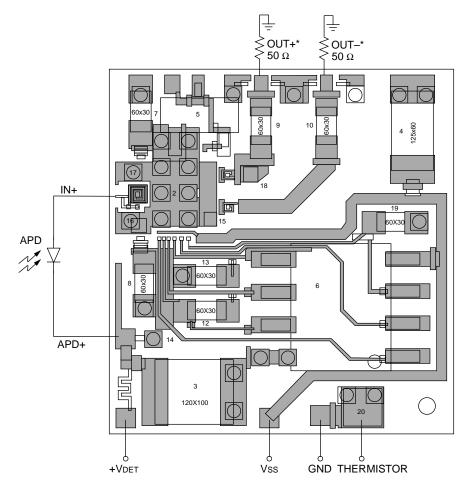

# **Typical Connections and Padout of the Hybrid Integrated Circuit**

5-5336(F).r3

\* OUT- is delayed approximately 25 ps with respect to OUT+ due to the longer microstrip line associated with OUT-. An extra delay should be added to OUT+ before connecting to the next circuit.

#### Figure 3. Typical Connections to the HIC (See Figure 4 for a Schematic of the Circuitry on the HIC.)

#### Table 2. HIC Pad Functional Description

| Symbol     | Description                                                                    |  |

|------------|--------------------------------------------------------------------------------|--|

| IN+        | Amplifier input; connect to detector anode, current should enter this node.    |  |

| APD+       | RF bypassed connection for the cathode of the APD.                             |  |

| +VDET      | APD power supply connection.                                                   |  |

| Vss        | Supply voltage; –5.2 Vdc nominal.                                              |  |

| GND        | Ground (back of HIC is also ground).                                           |  |

| Thermistor | Negative temperature coefficient thermistor for APD gain control.              |  |

| OUT+       | Noninverted data output (produces high-level output for current entering IN+). |  |

| OUT-       | Inverted data output (produces low-level output for current entering IN+).     |  |

# **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

#### **Table 3. Absolute Maximum Ratings**

| Parameter                   | Min | Max | Unit |

|-----------------------------|-----|-----|------|

| Supply Voltage Range (Vss)  | -7  | 0.5 | V    |

| Power Dissipation           | _   | 1   | W    |

| Voltage (all pins)          | 0.5 | Vss | V    |

| Storage Temperature Range   | -40 | 125 | °C   |

| Operating Temperature Range | 0   | 100 | °C   |

# **Recommended Operating Conditions**

#### Table 4. Recommended Operating Conditions

| Parameter           | Symbol | Min  | Max  | Unit |

|---------------------|--------|------|------|------|

| Ambient Temperature | TA     | 0    | 85   | °C   |

| Power Supply        | Vss    | -4.7 | -5.7 | V    |

# **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent Technologies Microelectronics Group employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters.

#### Table 5. ESD Threshold

| HBM ESD Threshold |         |  |  |

|-------------------|---------|--|--|

| Device            | Voltage |  |  |

| LG1628AXA         | >500 V  |  |  |

# **Electrical Characteristics**

| Parameter                                                                                                                                                            | Symbol      | Min  | Тур  | Max  | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|------|-------|

| Power Supply Voltage                                                                                                                                                 | Vss         | -5.7 | -5.2 | -4.7 | V     |

| Power Supply Current                                                                                                                                                 | Iss         | —    | 140  | _    | mA    |

| Effective Small-signal Transimpedance<br>(Single-ended input to either OUT+ or<br>OUT- each driving a 50 $\Omega$ load, differ-<br>ential gain is twice this value.) | Tz          | _    | 5.8  | _    | kΩ    |

| Small-signal Bandwidth                                                                                                                                               | BW          | 1.5  | 1.6  | —    | GHz   |

| Transimpedance Peaking                                                                                                                                               | Трк         | —    | 0    | 1    | dB    |

| Output Return Loss                                                                                                                                                   | <b>S</b> 22 | 10   | 15   | _    | dB    |

| Input Noise Current<br>(100 kHz—2.5 GHz)                                                                                                                             | INOISE      | _    | 300  | 350  | nArms |

| Operating Temperature Range                                                                                                                                          | Тор         | 0    | —    | 85   | °C    |

TA = 25 °C, VSS = -5.2 V, CDETECTOR = 0.5 pF, RLOAD = 50  $\Omega$ , unless otherwise indicated.

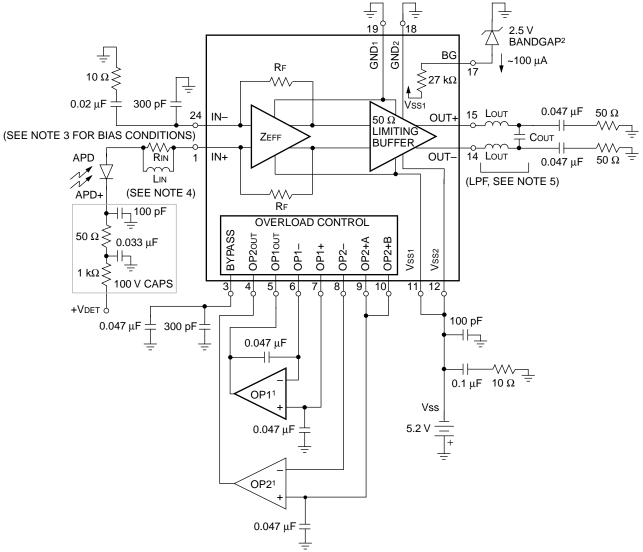

### **Test Circuit with Overload Control**

5-5335(F)r.1

- 1. Operational amplifiers OP1 and OP2 should have the following characteristics (suggested op amps are the LMC6082IM or OP291GS, both are available as dual op amps in an 8-pin SOIC package):

- a. Single 5 V supply operation.

- b. Maximum input offset voltage of 1 mV.

- d.High-level output to within 2 V of the positive rail.

- e.Gain bandwidth product ≥1.8 MHz.

- c. Low-level output includes negative rail.

- f. Large signal voltage gain ≥100 V/mV.

- 2. An on-chip 75 kΩ resistor to the negative supply is provided for biasing the voltage reference. Approximately 100 µA of current will be drawn. (Suggested bandgap reference is the LM4040BIM–2.5, available in an SOT-23 package.)

- 3. Node IN+ is nominally at -3.3 Vdc. APD supply voltage +Vdet should be adjusted appropriately.

- 4. RINLIN may be necessary to achieve stability depending on the physical arrangement of the APD and its associated electrical parasitics (series inductance and other resonances). The amplifier will be stable with a 0.5 pF detector capacitance in series with a 0.5 nH inductor, but packaged detectors usually do not behave so ideally at frequencies above a few gigahertz. A parallel RL network consisting of a 200 Ω resistor and a 6 nH inductor is provided on HIC and may be optionally used with a slight noise penalty. Good isolation from output to input is also essential for amplifier stability.

- 5. A low-pass filter is provided on the LG1628AXA HIC to reduce higher-frequency noise contributions (Butterworth N = 2, Zo = 50 and fc = 4.25 GHz, Lout = 2.65 nH, Cout = 0.5 pF).

#### Figure 4. Optical Receiver with Overload Control

# Test Circuit with Overload Control Disabled

5-5334(F)r.3

Note: Notes 2, 3, 4, and 5 from the previous page (Figure 4) apply to this drawing.

#### Figure 5. Optical Receiver with Overload Control Disabled

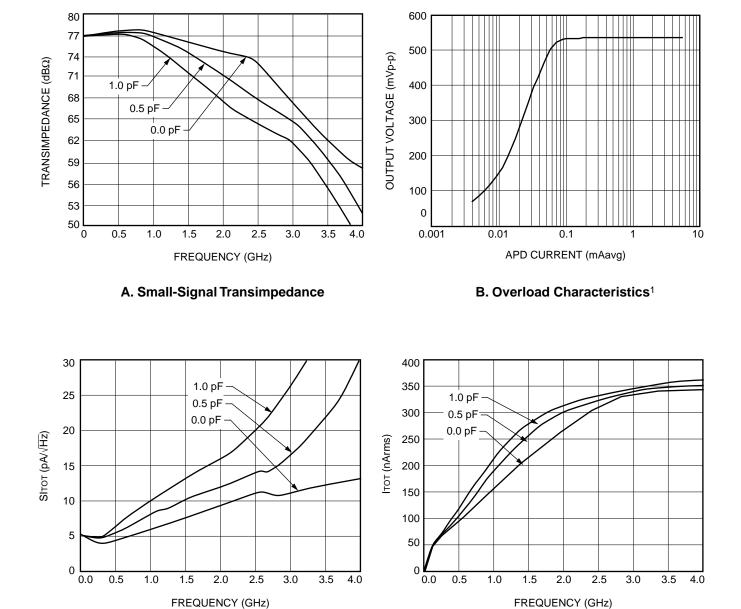

**Characteristic Curves** (at TA = 25 °C, Vss = -5.2 V, CDETECTOR = 0.0 pF, 0.5 pF, 1.0 pF, RLOAD = 50  $\Omega$ )

C. Input Spectral Noise Density

5-5330(F)r.1, 5-5331(F).ar2, 5-5332(F)r.2, 5-5333(F)r.2

**D. Total Input Noise Current**

1. >25 dB dynamic range requires an external Si dual operational amplifier. The detector polarity is such that current enters the LG1628A (i.e., the detector anode is connected to the LG1628A).

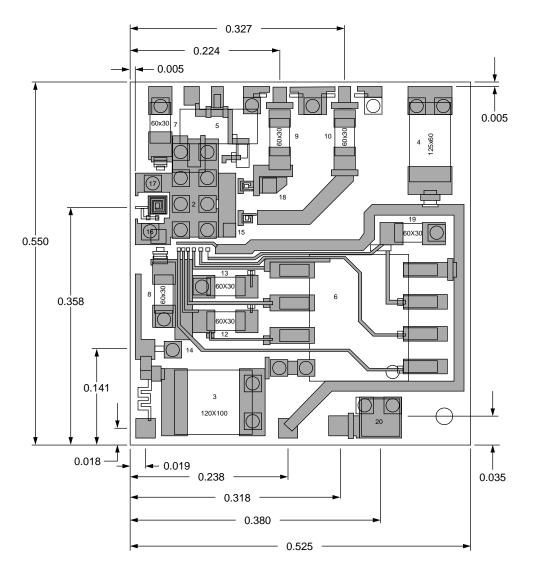

# **Dimensional Drawing of the Hybrid Integrated Circuit (HIC)**

Dimensions are in inches. Ceramic thickness is 0.025 inches.

5-5336(F).ar3

Figure 7. HIC Dimensions and Location of Bonding Pads

### **Ordering Information**

| Device Code | Package                                          | Temperature   | Comcode<br>(Ordering Number) |

|-------------|--------------------------------------------------|---------------|------------------------------|

| LG1628AXA   | Hybrid Integrated Circuit<br>Differential Output | 0 °C to 85 °C | 107791469                    |

| LG1628BXA*  | Hybrid Integrated Circuit<br>Single-ended Output | 0 °C to 85 °C | 108052085                    |

\* Second output on BXA is terminated through to ground 50  $\Omega$  on hybrid.

Notes

For additional information, contact your Microelectronics Group Account Manager or the following: INTERNET: http://www.lucent.com/micro docmaster@micro.lucent.com E-MAIL: U.S.A.: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495 JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 1189 324 299, FAX (44) 1189 328 148 Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Bracknell), FRANCE: (33) 1 41 45 77 00 (Paris), SWEDEN: (46) 8 600 7070 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki), ITALY: (39) 2 6601 1800 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1998 Lucent Technologies Inc. All Rights Reserved Printed in U.S.A.

microelectronics group

Bell Labs Innovation

January 1998 DS97-156FCE