# LGT8F08A/04A/02A/01A

# 高性能低功耗 8 位 FLASH 微控制器

编程手册

LOGICGreen Technologies Shenzhen, CHINA 2012-1-11 MBX: biz@mcugreen.com

www.mcugreen.com

# 产品特件

#### 高性能, 低功耗的 8 位 MVR8X 微处理内核

#### 先进的 RISC 构架

- 3级流水线设计

- 131条指令,大多数指令执行时间为单个时钟周期

- 32 个 8 位通用工作寄存器

- 工作于 16MHz 时性能高达 16MIPS

- 单周期的硬件乘法器(8x8)

#### 非易失性程序和数据存储器

- 8/4/2/1K 字节系统内可编程 FLASH

- 数据保护功能

- 504 字节数据 FLASH, 支持字节读写(EEPROM)

- 256/512 字节片内 SRAM

- 独立的用户数据区实现系统配置功能

#### SWD 双线调试接口

- 支持扩展的片内在线调试功能

- 通过 SWD 接口实现对 FLASH, EEPROM, 系统配置区的编程

#### 外设特点

- 8 通道 10bit 250KSPS 模数转换器(ADC)

- 2 通道模拟比较器,支持 ADC 通道输入功能

- 一个具有独立预分频和比较器功能的8位定时器/计数器

- 一个具有预分频器, 比较器功能和捕捉功能的 **16** 位定时器/计数器

- 三通道 PWM 脉宽调制控制器

- 可编程的串行 USART

- 可工作于主/从模式的 SPI 串行接口

- 可编程看门狗定时器

- 最多 25 个可编程 I/O (LGT8F08A)

#### 特殊的处理器特点

- 每个芯片具有独立的 32 位 GUID

- 具有掉电保护功能的片内 POR

- ±1%精度 16MHz 内部低温漂 RC 振荡器

- 片内/片外中断源

- 1KHz 低功耗 RC 实现更低的待机功耗

- 4种睡眠模式,内部电源设计实现 uA 级待机功耗,可通过外部 专用 I/O 或内部 1KHz RC 唤醒

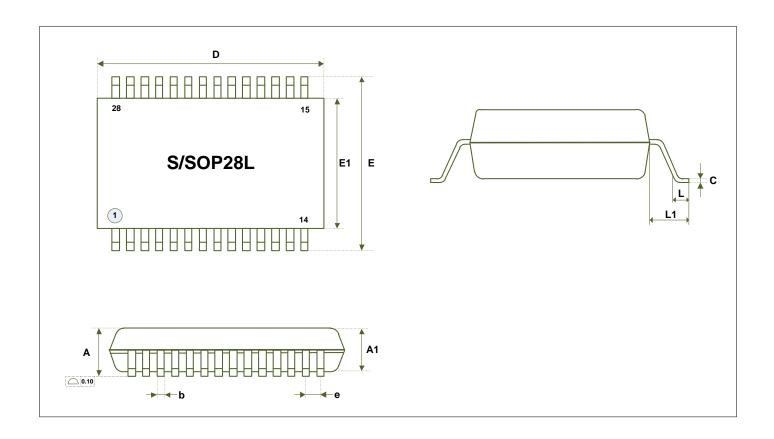

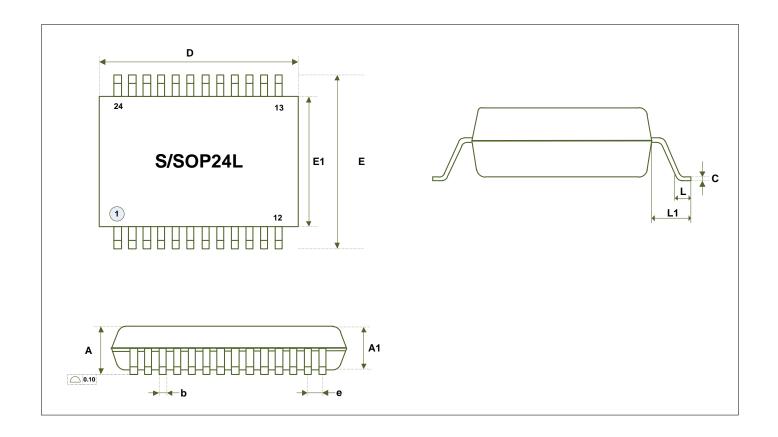

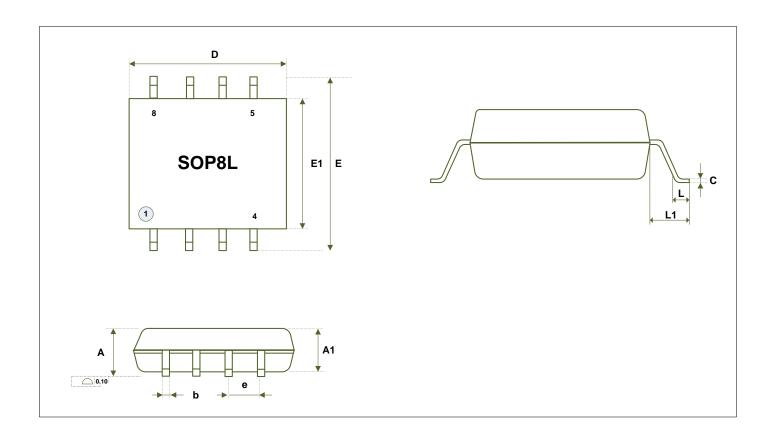

#### 封装类型

- SOP28L/SOP24L/SOP20L/SOP14L/SOP8L

#### 工作电压

- 1.8V ~ 3.6V

### 速度等级

- 0 ~ 16MHz @1.8V ~ 3.0V

- 0 ~ 25MHz @3.0V ~ 3.6V

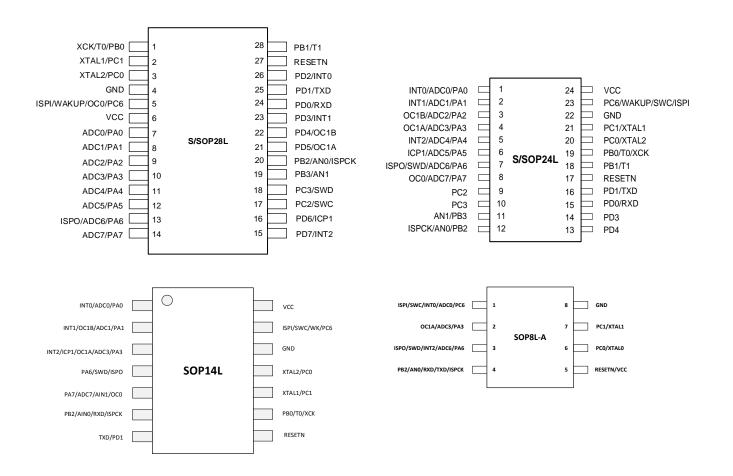

# 引脚配置

#### S/SOP 类型封装定义

### 注意事项:

- 1. 对于 S/SOP24L 封装的 LGT8F08A 系列, PC2/3 以及 PD3/4 只能作为输出 I/O

- 2. SOP8L-A 在以 S/SOP24L 为基础封装,功能配置和 S/SOP24 一致。其中 SOP8L-A 的一些引脚是 S/SOP24L 中几个引脚封装 到一起的结果。下面表格说明 SOP8L 和 S/SOP24L 引脚直接的对应关系,请在使用时特别注意:

| SOP8L-A | S/SOP24L              |

|---------|-----------------------|

| PIN1    | PIN1 + PIN23          |

| PIN3    | PIN5 + PIN7           |

| PIN4    | PIN12 + PIN15 + PIN16 |

| PIN5    | PIN17                 |

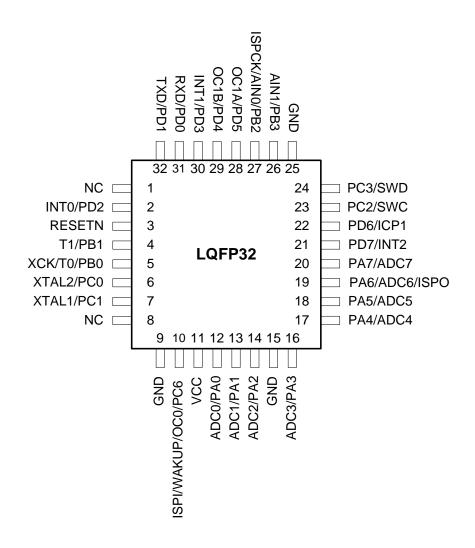

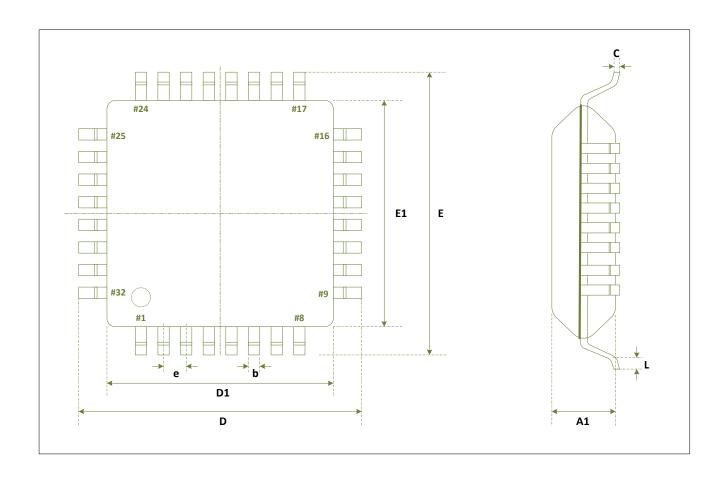

#### LQFP32 封装定义

# 引脚说明

| 端口                | 功能说明                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| VCC               | 3.3V 电源输入                                                                                                                   |

| GND               | 地                                                                                                                           |

| 端口 A (PA7PA0)     | 端口 A 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 A 处于高阻状态。 |

| 端口 B (PB3PB0)     | 端口 B 为 4 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。                                                                 |

| 端口 C (PC6,PC3PC0) | 端口 C 为 5 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 C 处于高阻状态。 |

| 端口 D (PD7PD0)     | 端口 D 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。                              |

| RESETN            | 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。持续时间小于门限间的脉冲不能保证可靠复位                                                                         |

| XTAL1             | 反向振荡放大器与片内时钟操作电路的输入端                                                                                                        |

| XTAL2             | 反向振荡放大器的输出端                                                                                                                 |

| ADC7ADC0          | 0~VCC模拟 ADC输入,当使用模拟输入功能时,对应的 PA端口应该设置为输入高阻,关闭上拉电阻,避免数字模块对模拟输入的干扰。                                                           |

| AN1AN0            | 0~VCC 模拟比较器外部输入,当使用外部模拟比较器输入时,对应的 PB3/PB2 端口应设置<br>为输入高阻,关闭上拉电阻,避免数字模块对模拟输入产生干扰。                                            |

| SWD               | 双线串行调试接口数据线                                                                                                                 |

| SWC               | 双线串行调试接口时钟线                                                                                                                 |

|                   | 用户可以通过寄存器配置或全局配置位关闭 SWD 接口                                                                                                  |

| TXD               | UART 数据输出引脚,同步 UART 模式 (SPI) 数据输出                                                                                           |

| RXD               | UART 数据输入引脚,同步 UART 模式 (SPI) 数据输入                                                                                           |

| XCK               | 同步 UART 模式(SPI)时钟,主模式为时钟输出,从模式为时钟输入。                                                                                        |

| T1                | 定时器 1 的外部时钟输入                                                                                                               |

| ICP1              | 定时器 1 输入俘获                                                                                                                  |

| OC1B              | 定时器 1 比较器 A 输出(PWM 输出)                                                                                                      |

| OC1A              | 定时器 1 比较器 B 输出(PWN 输出)                                                                                                      |

| T0                | 定时器 0 外部时钟输入                                                                                                                |

| OC0               | 定制器 0 比较器输出(PWM 输出)                                                                                                         |

| INT1INT0          | 外部中断输入                                                                                                                      |

| WAKUP             | 掉电模式下的专用唤醒引脚<br>ISD 绝积粉据绘》引脚                                                                                                |

| ISPI              | ISP 编程数据输入引脚                                                                                                                |

| ISPO<br>ISPCK     | ISP 编程数据输出引脚 ISP 编程时钟                                                                                                       |

| ISPUN             | ISP 編程刊刊 ISP 需要与 RESETN 复位输入一同配合工作, 拉低 RESETN 进入 ISP 模式                                                                     |

|                   | 拉高 RESETN 后,ISP 模块被禁止,系统进入正常工作模式                                                                                            |

|                   |                                                                                                                             |

# 重要说明

### 关于工程样片的不同

LGT8F0XA 系列第一版 LGT8F08A-16C 为前期工程样片,封装为 SOP28L。该工程样片与其他所有 LGT8F0XA 后续型号之间有一点使用上的差别,主要是外部晶振 I/O 的控制寄存器定义不同,请参考"系统时钟与功耗管理"章节中关于 PMCR 寄存器定义中对 OSCMEN 控制位的描述。

#### 关于SBIC/SBIS 指令的使用

由于 LGT8F0XA 的 I/O 端口为异步设计,所以可靠的使用方法是首先把端口的数据读入到内部寄存器,然后根据寄存器的值进行后续处理。所以不建议直接在端口寄存器上使用 SBIC/SBIS 指令。汇编模式下,用户可以使用 SBRC/SBRS 指令代替 SBIC/SBIS 指令。对于基于 C语言的应用,请参考"通用 I/O端口"章节中关于"I/O应用注意事项"的说明。

### 关于堆栈指针的初始化

LGT8F08A/04A 系列内部包含 512 字节 SRAM, 地址映射为 0x100~0x2FF

LGT8F02A/01A 系列内部包含 256 字节 SRAM, 地址映射为 0x100~0x1FF

用户需要注意在程序运行前正确的初始化内部堆栈指针寄存器(SP)。对于 LGT8F08A/04A 系列,使用 M164 兼容模式编译程序,SP 指针默认初始化为 0x4FF,这个值对于 LGT8F08A/04A 通用有效,内部偏移地址会保证 SP 指针指向 SRAM 的最高地址处,用户可以使用这种默认设置。对于 LGT8F02A/01A,需要用户使用程序代码或配置编译环境的方式正确的初始化 SP 指针到有效的 SRAM 空间。

### 关于I/O 端口的复位状态

LGT8F0XA 系列 I/O 端口在复位阶段都默认为 GPIO 功能,全部复位为输入状态,并关闭内部上拉电阻。需要用户注意的是 PB0 (只针对 S/SOP28/24/20 封装) 在复位过程中作为 ISP 的片选引脚,内部上拉是打开的。

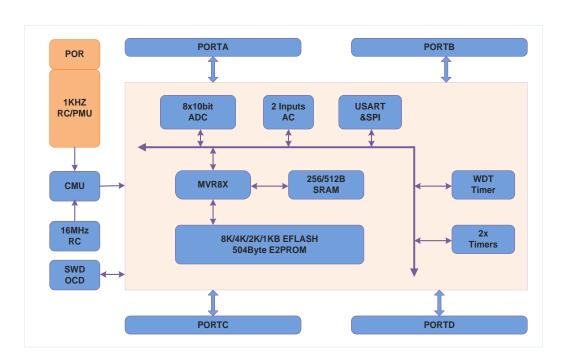

# 系统概述

LGT8F0XA 是基于增强的 8 位低功耗 MVR8X RISC 三级流水线构架设计。由于其先进的指令集以及单时钟周期指令执行时间, LGT8F0XA 的数据吞吐率高达 1MIPS/MHz,从而可以平衡系统在功耗和处理速度之间的矛盾。关于 MVR8X RISC 构架的更多细节,请参考本文档 MVR8X 内核介绍部分。

LGT8F0XA 引入的独特的电源设计方法,从而在系统待机功耗方面比同类产品有更加优异的表现,系统中为低功耗设计集成一个内部 1KHz RC 振荡器和电源管理模块,能够在系统空闲的时候由软件选择进入待机模式,在最高级别的待机模式下,电源管理系统将关闭系统工作电源,仅保持 1KHz RC 和电源管理模块的工作,从而实现微安级的待机功耗。

LGT8F0XA 基于 EFLASH 工艺设计,可以提供 8K/4K/2K/1K 四种不同的型号供选择,LGT8F0XA 集成了 504 字节内部数据 FLASH 以及 EEPROM 控制器单元,实现一个更加简易的 EEPROM 访问接口。同时 LGT8F0XA 也集成了 256/512 字节的 SRAM,可以让用户在实现不同应用时有更多的灵活性。

Figure3: 系统构架图

#### MVR8X 内核

MVR8X内核具有丰富的指令集和 32 个通用工作寄存器,其中R26~R31可组合为三个16位通用寄存器 X/Y/Z。 MVR8X内部集成一个单周期的 8X8 乘法器,可以胜任简单的数据运算;MVR8X针对中断响应进行了特别的优化,可以在中断发生后 3 个周期内进入中断服务程序,中断完成后,仅需 2 个周期便可从中断返回。MVR8X同时也对 I/O 控制系统进行了更大的优化,并具有针对 I/O 直接操作的指令,可以仅仅使用一条指令,一个周期完成对单个 I/O 或一组 I/O 的读、写操作,这些特点使得 MVR8X构架的 MCU 比同类型任何 MCU 更加适合控制类的应用。MVR8X内核实现了片上调试功能,用户可以通过双线 SWD接口以及专用的 USB调试器,配合业界成熟的开发环境,轻松的实现产品的研发与调试。

#### 存储单元

LGT8F0XA 系列 MCU 最多集成了 8KB EFLASH,504 字节的数据 FLASH,可以实现 E2PROM 功能。用户可通过 ISP 在线编程工具实现对 FLASH 的读写访问。LGT8F0XA 中集成了 E2PROM 接口控制逻辑,用户可以像访问 SRAM 一样访问 E2PROM 功能,提高了读写以及擦除操作的效率,同时也减少了实现 E2PROM 功能所需的代码量。

#### 数据保护

LGT8F0XA 实现为保护用户程序代码实现了接口加密功能,用户在编程完成后,可以通过设置 LOCK 位,禁止 ISP 以及 SWD 接口访问 EFLASH 以及 E2PROM 的功能,LOCK 位禁止 ISP 后,必须通过整片擦除操作才能恢复 FLASH 以及 E2PROM 区域的读写操作。

#### 时钟源

LGT8F0XA 内部集成了一个低温漂,误差±1%的 16MHz RC 振荡器,配合内部分频器,可以为系统运行提供 16MHz, 8MHz, 4MHz, 2MHz, 1MHz 最低至 125K的 8 种运行频率,满足不同应用的需求,节省了外部晶振。同时内部也集成了一个低功耗的 1KHz RC 振荡器,可以在低功耗模式下维持系统的工作,用户可选择关闭 16MHz RC 振荡器,这样可以在系统运行的同时,得到更低的功耗。对于特殊的需求,LGT8F0XA 也支持外部晶振,这样用户可以禁用内部 16MHz RC 振荡器,完全依赖外部晶振工作。

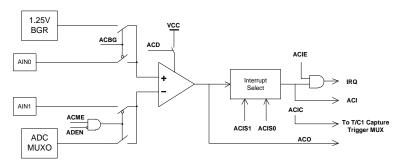

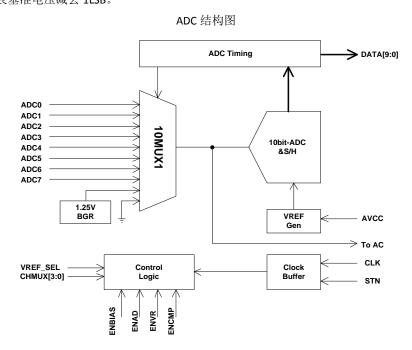

### 模数转换器 模拟比较器

LGT8F0XA 全系列都集成了一个 10bit 250KSPS 采用率的 SAR-ADC 模数转换器,通过配置内部的 ADC 转换控制器,可以实现非常灵活的自动触发转换功能。LGT8F0XA 全系列内部也实现了一个两通道的模拟比较器,可以高速精准的判断两路模拟输入电压的细微差别,对一些需要快速电压检测的电路十分有效。LGT8F0XA 内部有一个 1.25V 的参考电压源,可以为 SAR-ADC 以及模拟比较器提供内部参考输入。模拟比较器的输入可以为两路专用的外部输入,也可以来自 SAR-ADC 的模拟输入,这样可以十分方便的实现对两通道模拟比较器的更多通道扩展,满足更为复杂的应用。

# 串行控制器 SPI 控制器

LGT8F0XA USART是一个通用的串行控制器,支持通用的PC串口协议,可以通过串口实现与PC以及其他UART 外设之间的通讯,USART同时也支持并行模式,在并行模式下,用户可以实现SPI协议,通过相关的寄存器配置,选择并行模式下的SPI工作于主模式或从模式。通过SPI接口,用户可以实现对更多外设的兼容。

### 定时器 PWM

LGT8F0XA 实现两个多功能定时器,分别具有独立的定时预分频器,可以保证两个定时器的同时独立工作。定时计数器宽度分别为 8 位,16 位;可以满足不同的应用需求。定时器实现了通用的输入俘获,比较器输入等功能。通过对定时器的配置,可以轻松的实现三路 PWM 脉宽调制输出。为实现 PWM 相关的控制器算法提供了更加实用的解决方案。

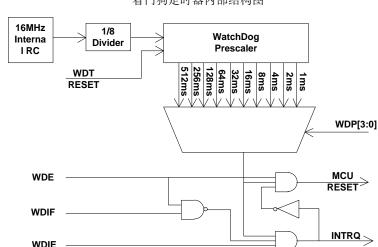

# 看门狗 定时器

LGT8F0XA WDT 是一个 16 位宽的看门狗专用定时器,可以通过预分频实现从 1ms 到 512ms 的宽范围复位间隔 宽度。MVR8X 内核实现了一个专门用于 WDT 复位的 WDR 指令,用户可以使用 WDR 指令方便的进行'喂狗'操作。

#### 可编程 I/O

LGT8F0XA的端口中除去 2 个电源引脚,所有的其他 I/O 都可以工作在 GPIO 模式下,配合 MVR8X 独有的高效 I/O 操作指令,可以让用户用更少的代码,实现复杂的设计,这是其他同类 MCU 所不具备的。

LGT8F0XA 具有一整套编程与系统开发工具,包括: C 语言编译器,宏汇编,程序调试器/软件仿真器,以及评估版。

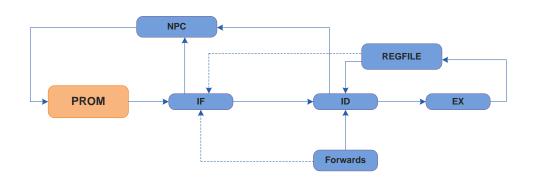

# MVR8X 内核简介

本节从总体上讨论 MVR8X 内核的结构。CPU 的主要任务是保证程序的正确执行。因此它必须能够访问存储器、执行运算、控制外设以及处理中断。MVR8X 构架基于优化的 3 级流水线结构,在中断响应,跳转指令效率上有相当优秀的表现,MVR8X 流水线也针对程序空间以及数据空间的访问上做了更多的优化,保证了 90%以上的指令可以在一个周期完成,大部分常用的跳转,程序调用,以及所有的存储空间访问指令,也都是在一个周期内完成。而其他少数条件跳转指令也仅仅是最多在两个周期内完成。整体性能上,在同等频率下,MVR8X 内核比基于 1T C51 构架的 MCU 在执行效率上高出 90%以上。具体指令的执行周期信息,请参考本资料相关部分。

Figure 3. MVR8X 结构图

MVR8X

为了获得最高的性能以及并行性, MVR8X 采用了哈佛结构,具有独立的数据和程序总线。CPU 在执行一条指令的同时读取下一条指令。这个概念实现了指令的单时钟周期运行。程序存储器是可以在线编程的 FLASH。

快速访问寄存器文件包括 32 个 8 位通用工作寄存器,访问时间为一个时钟周期。从而实现了单时钟周期的 ALU 操作。在典型的 ALU 操作中,两个位于寄存器文件中的操作数同时被访问,然后执行运算,结果再被送回到寄存器文件。整个过程仅需一个时钟周期。寄存器文件里有 6 个寄存器可以组合为 3 个 16 位的间接寻址寄存器指针以寻址整个数据空间,实现高效的地址运算。其中一个指针还可以作为程序存储器查询表的地址指针。这些附加的功能寄存器即为 16 位的 X、Y、Z 寄存器。

ALU 支持寄存器之间以及寄存器和常数之间的算术和逻辑运算。ALU 也可以执行单寄存器操作。运算完成之后 状态寄存器的内容得到更新以反映操作结果。

程序流程通过有/无条件的跳转指令和调用指令控制,从而直接寻址整个程序空间。大多数指令长度为 16 位,亦即每个程序存储器地址都包含一条 16 位或 32 位的指令。

在中断和调用子程序时返回地址的程序计数器(PC)保存于堆栈之中。堆栈位于内部数据 SRAM,因此其深度仅受限于 SRAM 的大小。在系统初始化过程中,用户首先要初始化堆栈指针寄存器 SP。这个寄存器位于 I/O 空间,可以进行读写访问。数据 SRAM 支持 5 种不同的寻址模式。

中断系统由位于 I/O 空间的控制寄存器和一个位于状态寄存器中的全局中断使能位构成。 所有的中断在中断向量表中都有独立的向量,中断优先级与中断向量在向量表中的位置对应,向量地址越低, 中断优先级越高。

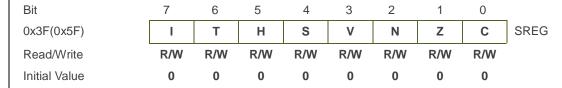

# 状态寄存器 (SREG)

状态寄存器保存了最新的算术运算指

令的执行结果。这个信息可用于程序的流程控制以及条件执行。状态寄存器的值在 ALU 操作之后更新。

进入中断之后, 状态寄存器并不会自动保存, 这个工作必须由软件完成。

#### MVR8X 状态寄存器 - SREG

#### Bit7-I:全局中断使能

全局中断使能后,MVR8X 内核才能接收并处理中断。各个模块独立的中断使能用于控制各个模块的中断请求功能。当全局中断清零后,所有的中断将不会被系统响应。中断被响应后,全局中断使能位(I)将被硬件自动清除。在执行 RETI 指令后,全局中断使能被自动置位,从而可以顺利的响应其他中断请求。I 位也可以使用 SEI 与 CLI 指令进行控制,具体请参考指令集相关介绍。

#### Bit6 - T: 位拷贝存储

位拷贝指令 BLD (Bit LoaD) 以及 BST (Bit Store)使用 T 位作为操作目标。可以使用 BST 将任意通用寄存器中的某一位拷贝到 T 位,也可以将 T 位拷贝到任意通用寄存器中的指定位 (BLD)。

#### Bit5 – H: 半进位标志

H标志指示某些算术操作的半进位状态,半进位在BCD运算中非常有用,请参考具体指令中的说明。

#### Bit4 – S: 符号位, S = N ⊕ V

符号位是负数位与二进制补码溢出位的异或值。

#### Bit3 - V: 二进制补码溢出位

二进制补码溢出用于支持二进制补码运算。请参考指令集描述部分。

#### Bit2 - N: 负数标志

负数标志指示了一个算术或逻辑运算的结果为负数。

#### Bit1 - Z: 零标志

Z标志指示了算术或逻辑运算的结果为零。请参考指令集描述部分。

### Bit0 - C: 进位标志

C表示指示算术或逻辑运算中产生了进位或借位操作。请参考指令集描述部分。

# 通用寄存器 (R0~R31)

MVR8X 内核对通用寄存器文件做了特殊优化。为获得需要的性能和灵活性,寄存器文件被设计为支持以下几种访问类型:

输出一个8位操作数和输入一个8位的运算结果

输出两个8位操作数和输入一个8位的运算结果

输出两个8位操作数和输入一个16位的运算结果

输出一个 16 位的操作数和一个 16 位的运算结果

MVR8X CPU 通用寄存器文件结构:

| 7   | 0 |      | Addr.   |

|-----|---|------|---------|

| R0  |   | 0x00 |         |

| R1  |   | 0x01 |         |

|     |   |      |         |

| R13 |   | 0x0D |         |

| R14 |   | 0x0E |         |

| R15 |   | 0x0F |         |

| R16 |   | 0x10 |         |

| R17 |   | 0x11 |         |

|     |   |      |         |

| R26 |   | 0x1A | X寄存器低地址 |

| R27 |   | 0x1B | X寄存器高地址 |

| R28 |   | 0x1C | Y寄存器低地址 |

| R29 |   | 0x1D | Y寄存器高地址 |

| R30 |   | 0x1E | Z寄存器低地址 |

| R31 |   | 0x1F | Z寄存器高地址 |

通用 寄存器文件

大部分操作寄存器文件的指令都可以访问到所有的寄存器,而且这些指令大部分都是单周期指令。 如上图所示,每个寄存器都被关联到一个数据内存地址,并映射到数据空间的开始 32 个位置。这种组织方式给访问通用寄存器提供了灵活的方式,可以使用 X-, Y-以及 Z-指令可以作为索引访问任意寄存器。

寄存器 R26..R31 可以两两组合为一个 16 位的地址指针寄存器,可用作间接寻址所有的数据空间。这三个间接寄存器的 X,Y 以及 Z 的定义如下:

|      | 15    | XH    |   | XL        | 0 |

|------|-------|-------|---|-----------|---|

| X寄存器 | 7     |       | 0 | 7         | 0 |

|      | R27(0 | )x1B) |   | R26(0x1A) |   |

|      |       |       |   |           |   |

|      | 15    | YH    |   | YL        | 0 |

| Y寄存器 | 7     |       | 0 | 7         | 0 |

|      | R29(0 | )x1D) |   | R28(0x1C) |   |

|      | 4.5   | 71.1  |   | 71        | 0 |

|      | 15    | ZH    |   | ZL        | 0 |

| Z寄存器 | 7     |       | 0 | 7         | 0 |

|      | R31(0 | )x1F) |   | R30(0x1E) |   |

不同的寻址模式使用 X/Y/Z 作为偏移地址,支持访问后地址的自动偏移增加,自动递增以及自动递减。 具体实现细节,请参考不同的指令集部分。

#### 堆栈指针(SP)

堆栈主要用于保持临时数据,局部变量以及中断和子程序调用的返回地址。必须注意的是,堆栈指针被设计为从高地址向低地址递减的模式。堆栈指针(SP)总是指向堆栈的顶端。堆栈指针指向数据空间(SRAM)。

位于 SRAM 空间的堆栈必须在所有子程序和中断之前正确的初始化。初始的 SP 指针总是指向 SRAM 的最后一个可用地址。请参考内存分布部分的定义。

Table: 堆栈指针操作指令

| 指令    | 堆栈指针 | 操作描述   |  |  |

|-------|------|--------|--|--|

| PUSH  | 减一   | 数据压栈   |  |  |

| CALL  | 减二   | 返回地址压栈 |  |  |

| ICALL |      |        |  |  |

| RCALL |      |        |  |  |

| POP   | 加一   | 数据出栈   |  |  |

| RET   | 加二   | 返回地址出栈 |  |  |

| RETI  |      |        |  |  |

MVR8X 堆栈指针由两个位于 I/O 空间的 10 位寄存器构成。SP 指针的有效位数与实际的实现有关。某些 MVR8X 实现的 MCU 只含有非常小的 SRAM, 因此只有 SPL 是有效的。在这种情况下,SPH 寄存器实际上并不存在。

#### SPH 与 SPL - 堆栈指针的高低位寄存器

Bit 15 14 13 12 11 10 9 8 SPH 0x3E(0x5E) SP9 SP8 ---SP1 0x3D(0x5D) SP7 SP6 SP5 SP4 SP3 SP2 SP0 SPL 6 5 3 2 1 0 R/W R R R R R R R Read/Write R/W R/W R/W R/W R/W R/W R/W R/W 0 0 0 0 0 0 0 1 Initial Value 1 1 1 1 1 1 1

Table: LGT8F0XA 系列堆栈指针有效位数:

| 设备       | 堆栈指针大小  |

|----------|---------|

| LGT8F01A | SP[8:0] |

| LGT8F02A | SP[8:0] |

| LGT8F04A | SP[9:0] |

| LGT8F08A | SP[9:0] |

#### 关于堆栈指针初始化的说明:

LGT8F08A/04A 系列, 初始化 SP 寄存器在 0x100~0x2FF 以内的有效空间;

LGT8F02A/01A 系列, 初始化 SP 寄存器到 0x100~0x1FF 以内的有效地址空间。

对于 LGT8F08A/04A, 内部 SRAM 为 512 字节,映射到从 0x100 开始的数据存储空间。使用 M164 兼容模式编译代码时, SP 默认初始化为 0x4FF, 这个默认值对 LGT8F08A/04A 一样有效,内部的地址偏移机制会把 SP 准确定位到 SRAM 的最高地址上。但对于 LGT8F02A/01A,需要用户正确配置 SP 指针。

#### 复位与中断处理

MVR8X 支持 22 种不同的中断源,这些中断以及复位向量分别对应于程序空间的向量地址。大部分中断都对应一个单独的使能控制,这些控制位并连同全局中断使能置位后, MVR8X 内核才能响应相应的中断请求。

程序空间的最低地址默认定义为复位以及其他中断的向量地址空间。完整的向量地址分配,请参考中断控制器描述部分。中断向量地址的位置,也同时决定了中断响应的优先级。向量地址越低,中断的优先级就会越高。因此复位(RESET)具有最高的优先级,然后是外部中断 0 (INTO)。

中断发生后,全局中断使能位(I位)被硬件自动清零。之后的中断将不在被响应。用户可以在中断服务程序中打开全局使能位,从而实现中断嵌套。所有的中断都可以被嵌套。执行中断返回指令(RETI),将会同时置位全局使能位,从而可以继续响应其他中断。

中断基本上分为两种模式。第一种为事件触发,设置中断标志位。对于这些中断,程序计数器(PC)直接指向向量地址,执行该地址处的中断服务程序。响应中断后,硬件自动清除中断标志位。中断标志位也可以通过软件写 1 清除。如果发生中断的同时,中断不能被立刻响应,中断标志将会保持,直到中断得到响应,或者被用户通过软件主动清除。同样,如果中断发生的同时,全局中断被清除,中断标志位也将继续保持,直到全局使能被置位后,中断得到响应。同时发生的中断,将依据他们的优先级被先后执行。

第二种中断为状态中断,只要中断条件成立,中断就将一直保持。此类中断不需要相应的标志位。如果在中断被使能前中断条件消失, 中断将不会被响应。当 MVR8X 从中断中返回后,通常会执行一条或几条指令, 然后才会响应中断请求。

需要注意的是,状态寄存器并不会在中断响应的过程中被自动保存和恢复。这个工作必须由软件完成。

当用户使用 CLI 指令禁止中断响应,中断将会被立即禁止,即使是与 CLI 同时发生的中断也将无法得到响应。下面的程序例子描述如何在编程 EEPROM 时禁止中断产生的干扰。

#### 汇编代码样例

in r16, SREG ; store SREG value

cli ; disable interrupts during timed sequence

**sbi** EECR, EEMPE ; start EEPROM write

sbi EECR, EEPE

**out** SREG, r16 ; restore SREG value (I-bit)

#### C语言代码

char cSREG;

cSREG = SREG; /\* store SREG value \*/

/\* disable interrupts during timed sequence \*/

disable interrupt();

EECR |= (1<<EEMPE); /\* start EEPROM write \*/

EECR |= (1<<EEPE);

SREG = cSREG; /\* restore SREG value (I-bit) \*/

#### 中断响应时间

当使用 SEI 指令使能中断, SEI 之后的指令将会被首先执行, 然后中断才会得到响应。

当中断使能打开后,中断将会在最多 4 个周期内被响应。四个周期后,中断向量执行的指令进入执行期。中断服务程序开始执行。在这四个周期内,当前程序地址 PC 将会被压入堆栈。中断向量一般为一条跳转指令,跳转指令一般为 1 或 2 个周期。如果中断发生在 MCU 处于休眠模式,中断将首先唤醒 MCU,然后才能响应响应的中断,因此中断响应时间将会增加 3 个周期。从中断服务返回需要 2 个周期。在这两个周期内,返回地址从堆栈中弹出,堆栈指针加 2,全局中断使能位被硬件自动置位。

# 内存分配

本章主要介绍 LGT8F0XA 系列 MCU 的不同存储空间。MVR8X 结构包含了两种内存空间, 数据存储空间以及程序存储空间。另外 LGT8F0XA 系列也包含了一个 504 字节的数据 FLASH,支持字节读写功能,无需用户擦除管理,用户存放需要掉电保持的持久性 数据。所有这三种存储空间都是线性的

# 程序存储内存

**系统可编程 FLASH** │ LGT8F0XA 包含 8K/4K/2K/1K 字节的片上系统可编程 FLASH 存储器。用于存储系统程序。所有的 MVR8X 指令 为 16 或 32 位宽, FLASH 的数据宽度统一为 x16 位宽。

> FLASH 存储器的使用寿命为至少 20,000 次擦写周期。LGT8F0XA 系列程序计数器分别为 13/12/11/10 位,可以 寻址到 8K/4K/2K/1K 的空间范围。FLASH 空间可以通过 ISP 接口(SPI)和在线调试接口(SWD)进行编程和 读取操作。LGT8KF0XA 也支持通过用户程序编程内部 FLASH,用户可以通过这个功能实现自定义的在线编程 和在线程序升级功能。

0x0000 LGT8F01A 1Kbytes 0x03FF 0x0400 LGT8F02A 2Kbytes 0x07FF 0x0800 LGT8F04A 4Kbytes 0x0FFF 0x0C00 LGT8F08A 8Kbytes 0x1FFF

程序存储空间

LGT8F0XA 系列均包含了 504 字节的数据 FLASH, 用于保存用户数据。LGT8F0XA 内部实现了一个专用的 EEPROM 控制器,用于管理这部分数据空间。通过这个专用的控制器,可以实现基于字节的读写访问,从而节 省了大量的管理代码。详细操作细节,请参考 EEPROM 相关章节。

独立地址空间

通过专用控制器访问

504 字节

数据 FLASH

# 256/512BSRAM 数据存储空间

LGT8F0XA 系列是一种复杂微控制器,集成了可以通过 IN/OUT 指令访问的外设控制器。这部分包括了 I/O 空间 的最低 64 字节范围。对于从 0x60 到 0xFF 之间的扩展 I/O 空间,被分配到数据存储空间,只能通过 ST/STS/STD 以及 LD/LDS/LDD 指令访问。

数据存储空间包含了寄存器文件,I/O 空间,扩展 I/O 空间以及内部 SRAM。开始的 32 个字节映射了 MVR8X 内 部的 32 个通用寄存器, 然后是 64 字节的标准 I/O 空间, 160 字节的扩展 I/O 空间, 最后是 256/512 字节的内部 数据 SRAM 空间。

程序可以通过 5 中不同的寻址方式访问数据存储空间:直接寻址,带偏移的间接寻址,间接寻址,带预递减的间接寻址以及支持访问后地址递增的间接寻址模式。在通用寄存器中,寄存器 R26 到 R31 可用于间接寻址的地址指针寄存器。

直接寻址可以寻址到全部的地址空间。

带偏移的间接寻址模式支持从基地址开始的63个地址控制,基地址通过Y或Z寄存器指定。

当使用支持访问前地址递减或访问后地址递增的寄存器间接寻址模式时,地址指令寄存器 X,Y 或 Z 将自动发生递增或递减。

LGT8F0XA 数据空间分布:

#### 数据存储空间

|                | 1               |

|----------------|-----------------|

| 32 个通用寄存器      | 0x0000 ~ 0x001F |

| 64 I/O 寄存器     | 0x0020 ~ 0x005F |

| 160 扩展 I/O 寄存器 | 0x0060 ~ 0x00FF |

|                | 0x0100          |

| 256/512 字节     |                 |

| 内部 SRAM 空间     |                 |

|                | 0x01FF/0x02FF   |

### EEPROM 数据存储 空间

LGT8F0XA 系列均包含了 504 字节的数据 EFLASH。配合内部的专用 EEPROM 控制器,实现了基于字节访问的 EEPROM 功能。内部 EEPROM 控制器针对用户的写操作进行了优化,可以避免不必要的重写和多余的擦除操作,极大的提高了写操作的平均速度和使用寿命。配合 EEPROM 内部的写均衡机制,可以将数据 FLASH 的使用寿命平均提高 2~3 倍以上。

用户也可以通过专用 ISP 通道(SPI 接口), 串行在线调试接口(SWD)对这部分区域进行访问,具体细节请参考相关章节。软件可以通过 I/O 空间访问 EEPROM 控制器,从而实现对 EEPROM 空间的读写。细节请参考下面的寄存器描述部分。为了防止误操作,对 EEPROM 空间的访问需要遵循一个特定的时序。细节请参 EEPROM 控制寄存器。当对 EEPROM 进行读写访问时,MVR8X 内核将处于待机状态。读写操作结束后,CPU 在 2 个系统时钟后继续运行,执行待机前的指令。

I/0 空间

LGT8F0XA 包含两种 I/O 空间。标准 I/O 空间以及扩展 I/O 空间。细节请参考寄存器定义部分。

所有外设控制器的寄存器都被分配到 I/O 空间。所有的 I/O 地址都可以使用 LD/LDS/LDD 以及 ST/STS/STD 指令访问,以及在这些 I/O 寄存器与 32 个通用寄存器之间传递数据。地址从 0x00 到 0x1F 范围内的 I/O 寄存器支持位访问指令 SBI/CBI。这些寄存器的中的某一位也可以使用 SBIS/SBIC 指令检测,控制程序执行流程。当使用 IN/OUT 指令访问时,必须使用 0x00~0x3F 作为目标地址。当使用 LD/ST 指令访问 I/O 寄存器控制时,必须加上 0x20 的基地址。此基地址为 I/O 空间在数据存储空间的映射基地址。从 0x60 开始到 0xFF 之间的扩展 I/O 空间,被系统映射到数据空间,因此只能够通过 ST/STS/STD 以及 LD/LDS/LDD 指令访问。

#### 寄存器描述

#### EEARH/EEARL - EEPROM/EFLASH 地址寄存器

| Bit           | 15    | 14    | 13    | 12     | 11     | 10     | 9     | 8     |       |

|---------------|-------|-------|-------|--------|--------|--------|-------|-------|-------|

| 0x22(0x42)    | -     | -     | -     | EEAR12 | EEAR11 | EERA10 | EEAR9 | EEAR8 | EEARH |

| 0x21(0x41)    | EEAR7 | EEAR6 | EEAR5 | EEAR4  | EEAR3  | EEAR2  | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4      | 3      | 2      | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R/W    | R/W    | R/W    | R/W   | R/W   |       |

| Read/Wille    | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0      | 0      | 0      | 0     | 0     |       |

| miliai value  | 0     | 0     | 0     | 0      | 0      | 0      | 0     | 0     |       |

#### Bit 15:13 - Reserved

这些位在 LGT8F0XA 系列 MCU 中并没有使用, 读返回零, 写操作无任何意义。

#### Bit 12:0 - EEAR[12:0]: EEPROM 地址寄存器

LGT8F0XA 系列中包含 504 字节的 EEPROM 空间,因此只有 EEAR[8:0]实际用于访问 EEPROM 数据空间。 EEAR[12:0]只用于通过 EEPROM 控制器接口访问程序 FLASH 空间。无论是访问 EEPROM 还是访问程序空间,这里指定的地址均为以字节寻址的地址值。

### EEDR - EEPROM/EFLASH 数据寄存器

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 0x20(0x40)    | MSB |     |     |     |     |     |     | LSB | EEDR |

| Read/Write    | R/W | _    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### Bit 7:0 - EEDR[7:0]: EEPROM/EFLASH 数据寄存器

EEPROM 空间是以字节为单位读写访问,所以对于 EEPROM 空间的访问,这里存放了读写操作的字节数据。 FLASH 空间是以双字节(16 位)为单位访问,当通过 EEPROM 控制器接口访问 FLASH 空间时,这里存放读写数据的低字节部分。高字节部分请参考 EEDHR 寄存器定义。

#### EECR - EEPROM/EFLASH 控制寄存器

| Bit           | 7     | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|---------------|-------|---|-------|-------|-------|-------|------|------|------|

| 0x1F(0x3F)    | EEPM2 | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write    | R/W   | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| Initial Value | 0     | 0 | 0     | 0     | 0     | 0     | 0    | 0    |      |

#### Bit 7 - EEPM2: FLASH 访问使能位

EEPM2 用于使能访问程序空间的控制逻辑。软件可以通过设置此位,实现通过 EEPROM 控制器对 FLASH 空间 进行读/写/擦除操作。需要注意的是对 FLASH 空间的读写操作是以双字节为单位,擦除操作是以页为单位。FLASH 空间的页面大小为 256x16。

Bit 6 - Reserved: 保留位

Bit [5:4] - EEPM[1:0]: FLASH 操作模式控制位

这两位只在 EEPM2 设置为 1 的前提下才会起作用。用于控制对 FLASH 空间的操作模式。

EEPM 模式定义如下:

| EEPM1 | EEPM0 | 操作模式                            |  |  |  |

|-------|-------|---------------------------------|--|--|--|

| 0     | 4     | FLASH 空间页擦除操作,页定制由 EEAR[12:9]指定 |  |  |  |

| 0     | 1     | EEAR[8:0]需设置为全零。                |  |  |  |

| 4     | 0     | FLASH 空间编程操作,编程以双字节为单位,编程地址由    |  |  |  |

| ı     | 0     | EEAR[12:1]指定,数据通过 EEDR/EEDHR 指定 |  |  |  |

| 其他配置  |       | FLASH 空间读操作,读操作是以字为单位,读地址由      |  |  |  |

| 共他    | 比直.   | EEAR[12:1]指定。数据存放在 EEDR/EEDHR   |  |  |  |

Bit 3 - EERIE: EEPROM/EFLASH 控制器就绪中断使能

设置 EERIE 位将使能 EEPROM/EFLASH 控制器准备就绪中断请求。清除此位将禁止就绪中断请求。控制器检测到 EEPE 为零后,将会产生一个持续的 EEPROM/EFLASH 控制器就绪中断请求。

#### Bit2 - EEMPE: EEPROM/EFLASH 编程时序使能控制

EEMPE 用于产生一个 EEPROM/EFLASH 编程时序使能控制。当 EEMPE 被设置后,必须在之后的四个周期内设置 EEPE 位,同时清除 EEMPE 位,数据才能被正确的编程。因此 EEPROM/EFLASH 编程应该满足下面列出的时序,否则将不会产生任何动作。

- 1. 等待 EEPE 清零 (EEPROM/EFLASH 就绪)

- 2. 写入编程目标地址到 EEAR (可选)

- 3. 写入数据到 EEDR/EEDHR (可选)

- 4. EEMPE 写 1,同时 EEPE 清零

- 5. 在 EEMPE 写入之后的四个系统时钟内,置位 EEPE

需要特别注意的是, 在以上操作的 4 和 5 过程中,如果发生了中断,将导致编程无效。因为中断将破坏四个周期的时序约束。所以建议在进行步骤 4 和 5 时,关闭全局中断使能。

当编程操作完成后,EEPE 位将会被硬件自动清零。用户可以通过查询此位的状态,决定是否可以继续下一次写操作。在对 EEPROM/EFLASH操作的过程中,CPU 将处于待机状态。

#### Bit 0 - EERE: EEPROM/EFLASH 读使能

当地址被设置到 EEAR 寄存器后,通过设置 EERE 位为 1 启动 EEPROM/EFLASH 读操作。在读操作的过程中, CPU 处于待机模式。由于 EEPROM 与程序空间公用数据总线, 所以读数据将会在写 EERE 寄存器后 2 个周期有效。软件需要在 EERE 置位后插入至少两个 NOP 后, 才能正确的读到数据。

下面将给出通过 EEPROM 控制器访问 EEPROM 空间的代码示例。假设用户在操作之前关闭了全局中断使能。

| EEPROM 读操作汇编代码                                 |                                     |  |  |  |  |  |  |

|------------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| EEPROM_read:                                   | ; Start eeprom read by writing EERE |  |  |  |  |  |  |

| ; Wait for completion of previous write        | sbi eecr,eere                       |  |  |  |  |  |  |

| sbic EECR,EEPE                                 | nop                                 |  |  |  |  |  |  |

| rjmp EEPROM_read                               | nop                                 |  |  |  |  |  |  |

| ; Set up address (r18:r17) in address register | ; Read data from Data Register      |  |  |  |  |  |  |

| out EEARH, r18                                 | <b>in</b> r16,EEDR                  |  |  |  |  |  |  |

| out EEARL, r17                                 | ret                                 |  |  |  |  |  |  |

```

unsigned char EEPROM_read(unsigned int uiAddress)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE));

/* Set up address register */

EEAR = uiAddress;

/* Start eeprom read by writing EERE */

EECR | = (1<<EERE);

__nop(); __nop();

/* Return data from Data Register */

return EEDR;

}

```

```

EEPROM 编程操作汇编代码

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR, r16

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

ret

EEPROM 编程操作 C语言代码

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

/* Wait for completion of previous write */

while(EECR & (1<<EEPE));

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR |= (1<<EEMPE);

/* Start eeprom write by setting EEPE */

EECR |= (1<<EEPE);

```

特别提醒: 当使用 C 语言编程的时候,需要注意编译器的优化级别。保证在 EEMPE 和 EEPE 之间的四个系统周期限制。可以通过反汇编,查看 EEMPE 与 EEPE 之间的指令周期数。

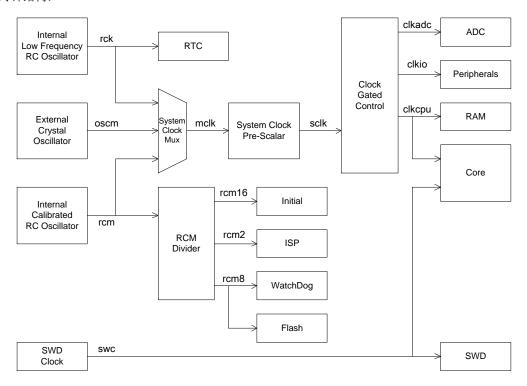

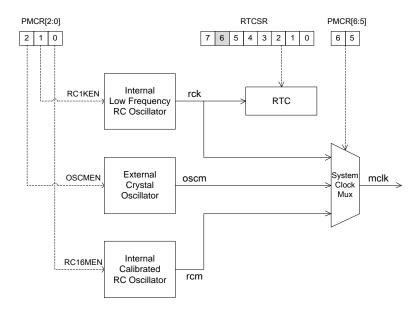

# 系统时钟与功耗管理

本章主要介绍 LGT8F0XA 系列 MCU 的时钟分布以及时钟管理。LGT8F0XA 支持多种时钟源,但并不是所有的时钟都需要同时工作。为了节省功耗,不需要的时钟模块可以通过寄存器关闭。

LGT8F0XA 系统时钟结构:

#### 时钟概述

CPU 时钟(clkcpu)主要用于驱动 MVR8X 内核以及内部 SRAM。MVR8X 内核组成包含了通用寄存器文件,状态寄存器,以及存放堆栈的 SRAM。当系统进入休眠模式后,CPU 时钟将被关闭,CPU 将处于待机模式。

I/O 时钟(clkio)用于驱动所有的 I/O 外设。比如定时器,SPI/USART 控制器,以及 ADC 控制器接口逻辑。I/O 时钟也用于外部中断模块。但是有些外部中断模式工作于异步模式,这样可以确保 I/O 时钟关闭后仍然可以检测到中断请求。不同的 I/O 外设也配有单独的时钟控制寄存器,可以在不需要相关模块时关闭该 I/O 模块的工作时钟。

FLASH 编程时钟(clkflash)。因为 FLASH 编程需要相对精确的时序,系统使用内部可校准 RC 振荡器时钟的 8 分 频作为 FLASH 读写工作时钟。由于内部 RC 振荡器校准之后可以达到 1%的精度,其低温漂效应以及与外部工作电压无关的特性,保证了在各种条件下 FLASH 的正常操作。

ADC 时钟(clkadc)为 ADC 控制器接口提供工作时钟。ADC 独立的时钟控制可以实现在关闭 CPU 时钟和 I/O 时钟后 ADC 仍然可以继续工作,从而减小了系统对 ADC 模块的噪声干扰。这种工作机制可以提高 ADC 转换的精度。

RTC 时钟(rck)。LGT8F0XA 系列内部均集成了一个 128Hz 左右 RC 振荡器,可以在系统掉电的情况下继续工作。 RTC 内部包含了一个 24 位的计数器,可用于实现更长时间的计时/计数应用。此 RTC 也可以用于掉电模式的唤醒工作。内部低频 RC 振荡器时钟也可以作为系统工作时钟。

时钟源

LGT8F0XA 系列 MCU 主要支持三种时钟源,分别为内部可校准 RC 振荡器,内部低频 RC 振荡器以及外部晶振时钟。对于大部分应用,内部可校准 RC 提供 16MHz 的精准时钟,配合内部的系统时钟预分频器,可以产生从 16MHz 到 125KHz 一共 8 种频率,基本上能满足大部分应用。从而节省了外部晶振。在一些对频率特征有特殊要求的应用,LGT8F0XA 也支持外部晶振,给系统工作带来更大的灵活性。

不同时钟源的切换可以通过系统功耗管理控制寄存器实现(PMCR)。 具体细节请参考先关章节。

系统上电后,默认情况下,LGT8F0XA工作于内部可校准RC振荡器的两分频,一般情况下为8MHz左右。系统启动后,软件可以通过相关的时钟控制寄存器,选择合适的时钟源以及时钟频率。

另外需要注意, 外部晶振 XTAL1/XTAL2 是与 PC0/PC1 复用的,在配置选择外部晶振工作前,需要软件保证 PC0/1 的为输入状态,并禁用 PC0/1 上的上拉电阻。同样,如果要使用 PC0/PC1 的 GPIO 功能,也需要首先禁止外部晶振。具体细节请参考寄存器定义部分。

时钟源控制结构如下图所示:

重要提醒:系统上电后,内部可校准 RC 振荡器处于工作状态。内部低频率 RC 以及外部晶振 I/O 处于关闭状态。用户在切换主时钟源之前,必须首先开启切换的目标时钟源。等待时钟稳定后,才可以执行切换时钟的操作。各种时钟源的启动时间,请参考如下列表:

| . 4 . 1            | DC > C > C > C > C > C > C > C > C > C > |

|--------------------|------------------------------------------|

| 时钟源                | 启动时间                                     |

| 内部低频 RC 振荡器        | 1ms                                      |

| 内部可校准 16MHz RC 振荡器 | 10us                                     |

| 外部晶振 I/O           | -                                        |

时钟源模块启动时间:

#### 睡眠模式

LGT8F0XA 共有 4 种睡眠模式,包括空闲模式,ADC 噪声抑制模式,掉电模式和断电模式。下面分别进行说明。空闲模式: 当设置 SMOD 为 0 时,执行 SLEEP 指令将使 MCU 进入空闲模式。在此模式下,CPU 停止运行,而 USART/USPI,AC,ADC,TC0,TC1,WDT,外部中断,电平改变中断和中断系统继续工作。这个休眠模式停止了 clkcpu 和 clkflash,其他时钟继续工作。所有中断均可以唤醒 MCU。

ADC 噪声抑制模式: 当设置 SMOD 为 1 时,执行 SLEEP 指令将使 MCU 进入 ADC 噪声抑制模式。在此模式下,CPU 停止运行,USART/USPI,AC, TC0, TC1 等外设停止工作,而 ADC, WDT, 外部中断,电平改变中断和中断系统继续工作。此模式提高了 ADC 的噪声环境,使得转换精度提高。当 ADC 使能时,进入此模式将自动启动一次 AD 转换。这个休眠模式停止了 clkio,clkcpu 和 clkflash,其他时钟继续工作。ADC 中断,看门狗复位,外部中断,电平改变中断均可以唤醒 MCU。

掉电模式: 当设置 SMOD 为 2 时,执行 SLEEP 指令将使 MCU 进入掉电模式。在此模式下,CPU 停止运行,USART/USPI, AC, ADC, TC0, TC1 等外设停止工作,而 WDT, 外部中断,电平改变中断和中断系统继续工作。这个休眠模式停止了 clkadc, clkio, clkcpu 和 clkflash, 其他时钟继续工作。看门狗复位,外部中断,电平改变中断均可以唤醒 MCU。

断电模式: 当设置 POWOFF 位为"1"时,将使 MCU 进入断电模式。在此模式下,只有实时时钟模块继续工作,其它模块均关断电源,此模式下系统功耗进入最低。外部引脚 PC6 和 RTC 计数溢出可以唤醒系统。

| ["衣刀"]的睡椒(挨丸 ["的伯勒的")的 大人 类醛物 |        |          |       |        |     |                |     |     |                     |            |

|-------------------------------|--------|----------|-------|--------|-----|----------------|-----|-----|---------------------|------------|

|                               |        | 工作       | 时钟    |        | 唤醒源 |                |     |     |                     |            |

| 睡眠模式                          | clkcpu | clkflash | clkio | clkadc | rtc | INTn<br>PCINTn | WDT | ADC | USART<br>USPI<br>TC | PC6<br>RTC |

| 空闲模式                          |        |          | √     | 4      |     | 4              | 4   | 4   | 4                   |            |

| ADC 噪声抑制                      |        |          |       | ,      |     | ,              | 1   | ,   |                     |            |

| 模式                            |        |          |       | √      |     | √              | ~   | √   |                     |            |

| 掉电模式                          |        |          |       |        |     | 4              | 4   |     |                     |            |

| 断电模式                          |        |          |       |        | 1   |                |     |     |                     | ٧          |

下表为不同睡眠模式下的活动时钟以及唤醒源

#### 寄存器定义

#### PMCR - 功耗管理控制寄存器

| 地址: 0xF2 |           |        | 初始值: 0x11                                       |                           |  |  |

|----------|-----------|--------|-------------------------------------------------|---------------------------|--|--|

| Bit      | Name      | R/W    | Description                                     |                           |  |  |

| 7        | -         | -      | 保留位                                             |                           |  |  |

|          |           |        | 低频 RC 选择控制位,                                    |                           |  |  |

| 6        | LFEN      | R/W    | 当设置 LFEN 位为"1"时,选择内部低频 RC 时钟为系统工作时钟。            |                           |  |  |

|          |           |        | 当设置 LFEN 位为"0"时,依据 EXTMSEL 位来选择系统工作时钟。          |                           |  |  |

|          |           |        | 外部晶振选择控制位,                                      |                           |  |  |

| 5        | EVEN ACEL | D //4/ | 当设置 EXTMSEL 位为"1"且 LFEN 为"0"时,选择外部晶振为系统工作时钟。    |                           |  |  |

| 5        | EXTMSEL   | R/W    | 当设置 EXTMSEL 位为"0"且 LFEN 为"0"时,选择内部 16MHz 晶振为系统工 |                           |  |  |

|          |           |        | 作时钟。                                            |                           |  |  |

|          | CFDS      | R/W    | I/O 驱动强度配置位                                     |                           |  |  |

|          |           |        |                                                 | 低电平输出电流: 5.4mA,最大可到 7.4mA |  |  |

| 4        |           |        | 高电平输出电流: 7.8mA,最大可到 12.9mA                      |                           |  |  |

|          |           |        | 低电平输出电流: 10.7mA,最大可到 14.7mA                     |                           |  |  |

|          |           |        | 1<br>高电平输出电流: 15.6mA,最大可到 25.8mA                |                           |  |  |

| 3        | -         | -      | 保留位                                             |                           |  |  |

| 2        | OCCMEN    | D/M    | 工程样品 LGT8F08A-16C, 为 0 时,禁用外部晶振,默认为 0           |                           |  |  |

| 2        | OSCMEN    | R/W    | 其他所有 LGT8F0XA 型号,为 1 时,禁用外部晶振, 默认为 0            |                           |  |  |

| 1        | RC1KEN    | R/W    | 内部低频 RC 振荡器使能控制                                 |                           |  |  |

| 0        | RC16MEN   | R/W    | 内部 16MHz 振荡器使能控制                                |                           |  |  |

# CLKPR - 主时钟预分频寄存器

| 地址: 0x | ĸ61        |     | 初始值                                                                        | : 0x01                                     |   |     |  |

|--------|------------|-----|----------------------------------------------------------------------------|--------------------------------------------|---|-----|--|

| Bit    | Name       | R/W | Description                                                                |                                            |   |     |  |

| 7      | CLKPCE     | R/W | 时钟分频改变使能位<br>改变时钟分频之前,必须先设置此位,软件必须在设置此位之后的<br>4 个系统周期内改变时钟分频设置,否则设置将不会产生作用 |                                            |   |     |  |

| 6:3    | -          | -   | 保留位                                                                        |                                            |   |     |  |

| 2:0    | CLKPS[2:0] | R/W | 预分频<br>CLKPS2<br>0<br>0<br>0<br>1<br>1                                     | 分频系数<br>1<br>2<br>4<br>8<br>16<br>32<br>64 |   |     |  |

|        |            |     | 1                                                                          | 1                                          | 1 | 128 |  |

# OSCCAL - RC 精调控制寄存器

| 地址: | 0x66       |        | 初始值: 0x11                                                                                  |  |  |

|-----|------------|--------|--------------------------------------------------------------------------------------------|--|--|

| Bit | Name       | R/W    | Description                                                                                |  |  |

| 7   | -          | -      | 保留位                                                                                        |  |  |

|     |            |        | Pad 复位功能选择,只在 14 脚和 8 脚封装时有效                                                               |  |  |

| 6   | PRESETN    | R/W    | 当设置 PRESETN 位为"1"时,复用复位功能的引脚使能复位功能。                                                        |  |  |

|     |            |        | 当设置 PRESETN 位为"0"时,复用复位功能的引脚禁止复位功能。                                                        |  |  |

|     |            |        | 16MHz RC 精调控制位                                                                             |  |  |

|     |            |        | 片内 16MHz 晶振的精调过程:                                                                          |  |  |

|     |            |        | 1) 测量 16MHz 晶振的输出时钟频率 Fm,可通过测量 PWM 波形                                                      |  |  |

|     |            |        | 的频率来计算系统时钟的频率,默认设置下系统时钟为 16MHz 晶                                                           |  |  |

|     |            |        | 振输出时钟的二分频,并且晶振的可调参数 RCCAL = 0x0;                                                           |  |  |

| 5:0 | RCCAL[5:0] | D /\A/ | 2) 比较 Fm 和目标时钟频率 Ft (如 16MHz),若相等则晶振参数                                                     |  |  |

| 5.0 |            | R/W    | 不用调整即保持 RCCAL 值不变,若 Fm > Ft 进入步骤 3),若                                                      |  |  |

|     |            |        | Fm < Ft 进入步骤 4);                                                                           |  |  |

|     |            |        | 3) 当 Fm > Ft,取 F <sub>LSB</sub> = 1% * Fm,Y = (Fm - Ft)/F <sub>LSB</sub> ,Z = 64 -         |  |  |

|     |            |        | ROUND(Y);                                                                                  |  |  |

|     |            |        | 4) 当 Fm < Ft, 取 F <sub>LSB</sub> = 1% * Fm, Y = (Ft – Fm)/F <sub>LSB</sub> , Z = ROUND(Y); |  |  |

|     |            |        | 5) 计算出的 Z 值即为晶振精调参数,把 Z 值写入 RCCAL 即可。                                                      |  |  |

# PRR - 省电控制寄存器

| 地址: 0)       | (64        |        | 初始值: 0x00                                 |

|--------------|------------|--------|-------------------------------------------|

| Bit Name R/W |            | R/W    | Description                               |

| 7:6          | -          | -      | 保留位                                       |

|              |            |        | TCO 省电使能控制位                               |

|              |            |        | 当设置 PRTC0 位为"1"时,关闭 TC0 相应模块的工作时钟。当不      |

| 5            | PRTC0      | R/W    | 需要使用 TCO 模块时置位 PRTCO 来减少不必要的功耗。           |

|              |            |        | 当设置 PRTCO 位为"0"时,打开 TCO 相应模块的工作时钟。启用      |

|              |            |        | TCO 正常工作前必须先清零 PRTCO 位来开启时钟。              |

| 4            | -          | -      | 保留位                                       |

|              |            |        | TC1 省电使能控制位                               |

|              |            |        | 当设置 PRTC1 位为"1"时,关闭 TC1 相应模块的工作时钟。当不      |

| 3            | PRTC1      | R/W    | 需要使用 TC1 模块时置位 PRTC1 来减少不必要的功耗。           |

|              |            |        | 当设置 PRTC1 位为"0"时,打开 TC1 相应模块的工作时钟。启用      |

|              |            |        | TC1 正常工作前必须先清零 PRTC1 位来开启时钟。              |

| 2            | -          | -      | 保留位                                       |

|              |            |        | USART 省电使能控制位                             |

|              |            |        | 当设置 PRUSART 位为"1"时,关闭 USART/USPI 相应模块的工作时 |

| 1            | PRUSART    | R/W    | 钟。当不需要使用 USART/USPI 模块时置位 PRUSART 来减少不必要  |

| _            | 11105/1111 | 1,, 11 | 的功耗。                                      |

|              |            |        | 当设置 PRADC 位为"0"时,打开 USART/USPI 相应模块的工作时钟。 |

|              |            |        | 启用 USART/USPI 正常工作前必须先清零 PRUSART 位来开启时钟。  |

|              |            |        | ADC 省电使能控制位                               |

|              |            |        | 当设置 PRADC 位为"1"时,关闭 ADC 相应模块的工作时钟。当不      |

| 0            | PRADC      | R/W    | 需要使用 ADC 模块时先清零 ADC 使能位再置位 PRADC 来减少不必    |

|              |            | .,,    | 要的功耗。                                     |

|              |            |        | 当设置 PRADC 位为"0"时,打开 ADC 相应模块的工作时钟。启用      |

|              |            |        | ADC 正常工作前必须先清零 PRADC 位来开启时钟。              |

### SMCR - 睡眠模式控制寄存器

|        | KENDUNGULA 11 M |     |           |             |       |            |  |  |  |

|--------|-----------------|-----|-----------|-------------|-------|------------|--|--|--|

| 地址: 0: | x33             |     | 初始值: 0x00 |             |       |            |  |  |  |

| Bit    | Name            | R/W | Descripti | Description |       |            |  |  |  |

| 7:4    | -               | -   | 保留位       | 保留位         |       |            |  |  |  |

|        |                 |     | 睡眠模式      | 泛控制位        |       |            |  |  |  |

|        | SMOD[2:0]       | R/W | SMOD2     | SMOD1       | SMOD0 | 睡眠模式       |  |  |  |

|        |                 |     | 0         | 0           | 0     | 空闲模式       |  |  |  |

|        |                 |     | 0         | 0           | 1     | ADC 噪声抑制模式 |  |  |  |

| 2.1    |                 |     | 0         | 1           | 0     | 掉电模式       |  |  |  |

| 3:1    |                 |     | 0         | 1           | 1     | 保留         |  |  |  |

|        |                 |     | 1         | 0           | 0     | 保留         |  |  |  |

|        |                 |     | 1         | 0           | 1     | 保留         |  |  |  |

|        |                 |     | 1         | 1           | 0     | 保留         |  |  |  |

|        |                 |     | 1         | 1           | 1     | 保留         |  |  |  |

| SMCR - 睡眠模式控制寄存器(接上页) |    |     |                                                                                                                                                                      |  |  |  |

|-----------------------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 地址: 0x33              |    |     | 初始值: 0x00                                                                                                                                                            |  |  |  |

| Bit Name R/W          |    |     | Description                                                                                                                                                          |  |  |  |

| 0                     | SE | R/W | 睡眠使能控制位<br>当设置 SE 位为"1"时,使能睡眠模式,执行 SLEEP 指令 CPU 将<br>按照 SMOD 的设置进入相应的睡眠模式。为了防止 CPU 误入睡眠<br>模式,建议在即将执行 SLEEP 指令前置位 SE 并在系统唤醒之后立<br>即清除 SE 位。<br>当设置 SE 位为"0"时,禁止睡眠模式。 |  |  |  |

# RTCSR - RTC 控制和状态寄存器

|              | RTCSR - RTC 控制和状态奇仔器 |     |                                                |  |  |  |  |

|--------------|----------------------|-----|------------------------------------------------|--|--|--|--|

| 地址: 0x       | D0                   |     | 默认值: 0x80                                      |  |  |  |  |

| Bit Name R/W |                      | R/W | 描述                                             |  |  |  |  |

| 7            | WREN                 | R/W | 写使能标志位。                                        |  |  |  |  |

|              |                      |     | 当 WREN 位为"1"时,允许 CPU 写 RTCSR 寄存器。              |  |  |  |  |

|              |                      |     | 当 WREN 位为"0"时,写 RTCSR 寄存器操作失效。                 |  |  |  |  |

|              |                      |     | CPU 配置 RTCSR 寄存器之前最好先读取 WREN 位的状态。             |  |  |  |  |

| 6:5          | -                    | -   | 保留。                                            |  |  |  |  |

| 4            | LOAD                 | R/W | 加载使能控制位。                                       |  |  |  |  |

|              |                      |     | 当设置LOAD位为"1"时,RTC计数器加载计数最大值寄存器RTCTOPH,         |  |  |  |  |

|              |                      |     | RTCTOPM 和 RTCTOPL 的数值。加载完毕后,硬件自动清理 LOAD 位。     |  |  |  |  |

| 3            | PWEN                 | R/W | 外部引脚唤醒使能控制位。                                   |  |  |  |  |

|              |                      |     | 当设置 PWEN 位为"1"时,外部引脚唤醒功能被使能。系统工作在              |  |  |  |  |

|              |                      |     | Power Off 模式下,可通过外部引脚和 RTC 计数溢出来唤醒。使用外         |  |  |  |  |

|              |                      |     | 部引脚来唤醒时,需要保持 PC6 为高电平并持续超过 500us。              |  |  |  |  |

|              |                      |     | 当设置 PWEN 位为"0"时,外部引脚唤醒功能被禁止。                   |  |  |  |  |

| 2            | CWEN                 | R/W | 计数溢出唤醒使能控制位。                                   |  |  |  |  |

|              |                      |     | 当设置 CWEN 位为"1"时,计数溢出唤醒功能被使能。系统工作在              |  |  |  |  |

|              |                      |     | Power Off 模式下,可通过外部引脚和 RTC 计数溢出来唤醒。使用计         |  |  |  |  |

|              |                      |     | 数溢出来唤醒时,CPU 须预设计数最大值并使能计数,当计数到最小               |  |  |  |  |

|              |                      |     | 值发生溢出即可唤醒系统。                                   |  |  |  |  |

|              |                      |     | 当设置 CWEN 位为"0"时,计数溢出唤醒功能被禁止。                   |  |  |  |  |

| 1            | CEN                  | R/W | 计数使能控制位。                                       |  |  |  |  |

|              |                      |     | 当设置 CEN 位为"1"时,RTC 开始计数。                       |  |  |  |  |

|              |                      |     | 当设置 CEN 位为"0"时,RTC 停止计数。                       |  |  |  |  |

| 0            | POWOFF               | R/W | Power Off 使能控制位。                               |  |  |  |  |

|              |                      |     | 当 CPU 写 POWOFF 位为"1"时,系统进入 Power Off 模式,只有 RTC |  |  |  |  |

|              |                      |     | 模块工作,系统功耗最低。Power Off 模式下,可通过外部引脚和 RTC         |  |  |  |  |

|              |                      |     | 计数溢出来唤醒。系统唤醒后 CPU 须清零 POWOFF 位。                |  |  |  |  |

|              |                      |     |                                                |  |  |  |  |

### MCUCR - MCU 控制寄存器

| 地址: 0>       | ά35  |                                 | 初始值: 0x00                              |

|--------------|------|---------------------------------|----------------------------------------|

| Bit Name R/W |      | R/W                             | Description                            |

|              |      |                                 | SWD 串行调试接口禁止控制位                        |

|              |      |                                 | 当设置 SWDD 位为"1"时,禁止 SWD 串行调试接口。         |

|              |      |                                 | 当设置 SWDD 位为"0"时,使能 SWD 串行调试接口。         |

|              |      |                                 | 为了避免无意的禁止或使能 SWD 接口,必须通过下面的时序来改        |

|              |      |                                 | 变 SWDD 位:软件必须在 4 个时钟周期内将期望的数值两次写入      |

| 7            | SWDD | R/W                             | SWDD 位。调试过程中,请避免置位 SWDD 位。             |

|              |      |                                 | SWD 调试接口与两个通用 I/O 复用,如果用户需要使用这两个 I/O,  |

|              |      |                                 | 需要设置 SWDD 为 1,禁止 SWD 调试接口。禁止 SWD 接口后,芯 |

|              |      | 片将无法正常调试,用户需要在设计时考虑这两个I/O的功能分配, |                                        |

|              |      |                                 | 建议将最简单的功能分配到这里,保证其他重要功能可以进行正常          |

|              |      |                                 | 的调试。                                   |

| 6:5          | -    | -                               | 保留位                                    |

|              |      |                                 | 上拉禁止控制位                                |

| 4            | DUD  | D /\A/                          | 当设置 PUD 位为"1"时,禁止端口上拉。                 |

| 4            | PUD  | R/W                             | 当设置 PUD 位为"0",且端口寄存器的设置满足上拉条件时(DDxn    |

|              |      |                                 | = 0,PORTxn = 1),使能端口上拉。                |

| 3:0          | -    | -                               | 保留位                                    |

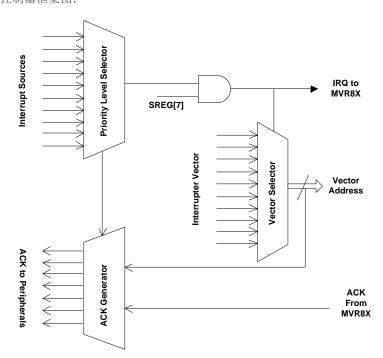

# 中断管理

本章主要介绍 LGT8F0XA 系列 MCU 的中断资源以及中断管理机制。MVR8X 内核对中断响应机制做了专门的优化,使得 MVR8X 内核能够在 4 个周期之内执行中断服务程序。中断返回指令也仅需 2 个周期。MVR8X 中断优先级与中断向量地址分布相对应,中断地址越低,中断优先级就越高。系统复位后,MVR8X 从 0x0000 地址开始执行复位向量代码,复位中断拥有最高优先级。

#### 中断向量

MVR8X 内核包含了一个专用的中断管理器,用于管理不同优先级别的中断响应,产生最终的中断向量,并在中断得到响应后产生响应的中断应答信号。外设在收到中断应答信号后,硬件自动清除中断标志位。 MVR8X 内核中断控制器框架图:

LG8F0XA 系列 MCU 内外共 22 个中断源,各个中断源有独立的中断使能控制位。用户需要在开启外设的中断功能前,根据中断向量地址,初始化中断服务子程序。与子程序调用类似,系统在响应中断后,程序计数器指向中断向量地址,从该地址取出将要执行的向量代码。于此同时,MVR8X 内核将被中断的程序地址压入系统堆栈。因此,软件需要提前初始化堆栈指针,否则中断程序将不能正确的返回。

用户在配置完外设中断后,必须打开 MVR8X 状态寄存器中的全局中断使能控制位,内核才能够正确的响应中断。 MVR8X 内核各个中断向量之间地址间隔 2 个字节,一般用户需要在此地址放置一个远跳转指令(JMP), 跳转到真正的中断服务子程序。具体细节请参考本章下面提供的示例代码部分。

MVR8X 内核中断设计为支持无限制中断嵌套。在中断请求得到响应后,全局中断使能被硬件自动关闭,从而禁止响应之后的中断请求。用户可以通过在中断服务程序中设置状态寄存器中的全局中断使能位,重新让 MVR8X 内核响应新的中断请求。中断嵌套不仅仅会影响中断服务的执行时间,也会对堆栈产生影响,用户需要在使用中断嵌套功能时特别注意。

# 中断向量地址分配

### 复位与中断向量表

|        | <b>交</b> 座习了朝内重秋 |           |                         |  |  |  |  |  |  |

|--------|------------------|-----------|-------------------------|--|--|--|--|--|--|

| Vector | Program          | Source    | Interrupt Definition    |  |  |  |  |  |  |

| No     | Address          |           |                         |  |  |  |  |  |  |

| 1      | 0x0000           | RESET     | 外部复位,上电复位,看门狗复位,JTAG 调试 |  |  |  |  |  |  |

| '      | 00000            | RESET     | 复位以及软件复位                |  |  |  |  |  |  |

| 2      | 0x0002           | INT0      | 外部中断请求 0                |  |  |  |  |  |  |

| 3      | 0x0004           | INT1      | 外部中断请求 1                |  |  |  |  |  |  |

| 4      | 0x0006           | INT2      | 外部中断请求 2                |  |  |  |  |  |  |

| 5      | 0x0008           | PCINT0    | I/O 电平变化中断请求 0          |  |  |  |  |  |  |

| 6      | 0x000A           | PCINT1    | I/O 电平变化中断请求 1          |  |  |  |  |  |  |

| 7      | 0x000C           | PCINT2    | I/O 电平变化中断请求 2          |  |  |  |  |  |  |

| 8      | 0x000E           | PCINT3    | I/O 电平变化中断请求 3          |  |  |  |  |  |  |

| 9      | 0x0010           | WDT_INTR  | 看门狗定时器溢出中断              |  |  |  |  |  |  |

|        |                  | 向量 10     | ~12 保留不用                |  |  |  |  |  |  |

| 13     | 0x0018           | ICF1_INTR | 定时器 1 输入俘获中断            |  |  |  |  |  |  |

| 14     | 0x001A           | OCA1_INTR | 定时器 1 比较器 A 匹配中断        |  |  |  |  |  |  |

| 15     | 0x001C           | OCB1_INTR | 定时器 1 比较器 B 匹配中断        |  |  |  |  |  |  |

| 16     | 0x001E           | TOV1_INTR | 定时器 1 溢出中断              |  |  |  |  |  |  |

| 17     | 0x0020           | OC0_INTR  | 定时器 0 比较器匹配中断           |  |  |  |  |  |  |

|        |                  | 向量 ′      | 18 保留不用                 |  |  |  |  |  |  |

| 19     | 0x0024           | TOV0_INTR | 定时器 0 溢出中断              |  |  |  |  |  |  |

|        |                  | 向量 2      | 20 保留不用                 |  |  |  |  |  |  |

| 21     | 0x0028           | RXC0_INTR | USART 接收完成中断            |  |  |  |  |  |  |

| 22     | 0x002A           | UDR0_INTR | USART 数据寄存器空            |  |  |  |  |  |  |

| 23     | 0x002C           | TXC0_INTR | USART 发送完成中断            |  |  |  |  |  |  |

| 24     | 0x002E           | ACP_INTR  | 比较器中断请求                 |  |  |  |  |  |  |

| 25     | 0x0030           | ADC_INTR  | ADC 转换完成中断请求            |  |  |  |  |  |  |

| 26     | 0x0032           | EEP_INTR  | EEPROM 就绪               |  |  |  |  |  |  |

|        |                  | 向量 2      | 27 保留不用                 |  |  |  |  |  |  |

| 28     | 0x0036           | RTC_INTR  | 实时定时器中断请求               |  |  |  |  |  |  |

### 中断向量初始化程序代码示例

| Address | Labels | Code |        | Comments |

|---------|--------|------|--------|----------|

| 0x0000  | -      | Jmp  | RESET  | ;RESET   |

| 0x0002  |        | Jmp  | INT0   | ;IRQ0    |

| 0x0004  |        | Jmp  | INT1   | ;IRQ1    |

| 0x0006  |        | Jmp  | INT2   | ;IRQ2    |

| 0x0008  |        | Jmp  | PCINT0 | ;PCINT0  |

| 0x000A  |        | Jmp  | PCINT1 | ;PCINT1  |

| 0x000C  |        | Jmp  | PCINT2 | ;PCINT2  |

中断向量初始化程序代码示例(接上页)

| Address | Labels | Code | <b>切始化程序代码示例(接上</b> | Comments                     |

|---------|--------|------|---------------------|------------------------------|

| 0x000E  |        | Jmp  | PCINT3              | ;PCINT3                      |

| 0x0010  |        | Jmp  | WDT                 | ;Watch dog Timeout           |

|         |        | .DB  | 0, 0, 0             | ;Reserved                    |

| 0x0018  |        | Jmp  | ICF1                | ;Timer1 Input Capture        |

| 0x001A  |        | Jmp  | COM1A               | ;Timer1 CompareA             |

| 0x001C  |        | Jmp  | COM1B               | ;Timer1 CompareB             |

| 0x001E  |        | Jmp  | TOV1                | ;Timer1 Overflow             |

| 0x0020  |        | Jmp  | OC0                 | ;Timer0 Compare              |

| 0x0022  |        | .DB  | 0                   | ;Reserved                    |

| 0x0024  |        | Jmp  | TOV0                | ;Timer0 Overflow             |

| 0x0026  |        | .DB  | 0                   | ;Reserved                    |

| 0x0028  |        | Jmp  | RXC0                | ;USART RX Complete           |

| 0x002A  |        | Jmp  | UDR0                | ;USART UDR Empty             |

| 0x002C  |        | Jmp  | TXC0                | ;USART TX Complete           |

| 0x002E  |        | Jmp  | ACP                 | ;Analog Compare              |

| 0x0030  |        | Jmp  | ADC                 | ;ADC Convert Complete        |

| 0x0032  |        | Jmp  | EEP                 | ;EEPROM Ready                |

| 0x0034  |        | .DB  | 0                   | ; Reserved                   |

| 0x0036  |        | Jmp  | RTC                 | ;RTC Underflow               |

|         |        |      |                     |                              |

|         | RESET: | Ldi  | R16, high(RAMEND)   | ;Main program start          |

|         |        | Out  | SPH, r16            | ;Set Stack pointer to top of |

|         |        | Ldi  | R16, low(RAMEND)    | ;RAM                         |

|         |        | Out  | SPL, r16            |                              |

|         |        | SEI  |                     | ;Enable interrupts           |

|         |        |      |                     |                              |

# 通用 1/0 端口

本章介绍 LGT8F0XA 系列的可编程通用 I/O 资源,LGT8F0XA 系列最大封装为 SOP28L,除去电源、地以及外部复位专用引脚外,其余 I/O 均可作为通用 I/O 使用。系统上电后,所有 I/O 默认配置为通用 I/O 模式。用户使能外设功能后,相应的 I/O 将会被外设专用的功能所替代。 MVR8X 内核从指令上对 I/O 控制做了深入的优化,仅需一条指令即可改变任意一个 I/O 的输出状态,仅需一条指令即可根据当前端口的状态进行程序流程控制。这些针对 I/O 的优化,使得 LGT8F0XA 系列 MCU 非常适用于控制类应用,减少了程序代码,提高的效率。这是其他同类 MCU 无法相比的。

概述

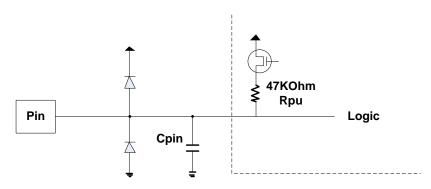

LGT8F0XA 系列所有的端口,当用作通用 I/O 时,支持**单周期读-改-写**操作。可以使用 SBI/CBI 指令在不改变其他任何端口状态的情况下,修改某一个 I/O 的状态(包括方向和驱动)。这种特性同样适用于修改单个端口的输出和上拉电阻(配置为输入)。端口的驱动能力可以根据应用配置为强驱动或弱驱动。在配置为强驱动时,端口可以驱动高达 15mA 的电流,可直接用于驱动 LED。所有的端口都具有典型值为 47KOhm 的可编程上拉电阻,这个电阻的值会随着供电电压略有变化。所有的 I/O 均支持施密特触发输入,提高了系统抗干扰的能力。

端口等效功能示意图:

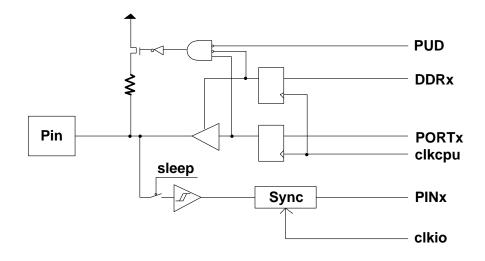

LGT8F0XA 系列 MCU 最多包含 4 组通用可编程 I/O,分被位 PA、PB、PC 以及 PD。每组 I/O 有三个专用寄存器用于控制端口驱动,读取端口状态。这三个寄存器被分配到 I/O 空间的最低地址开始,因此可以使用指令集中的位操作指令。这三个寄存器分别为:端口输出数据寄存器 – PORTx,端口方向寄存器- DDRx,以及端口数据寄存器 – PINx,(x = A/B/C/D)。 其中端口数据寄存器 PINx 为只读寄存器,实时反映端口电平的变化。另外,系统还设有一个全局的上拉禁止控制位 – PUD,PUD 位于 MCUCR 寄存器。用户设置此位为 1 后,所有端口的上拉电阻将被强制关闭。

端口驱动结构图

#### 端口配置

LGT8F0XA 系列 MCU 的每个通用可编程端口均为双向端口。每个端口对应三个寄存器位: DDRxn、PORTxn 以及 PINxn。寄存器细节请参考寄存器描述部分。DDRxn 通过 DDRx 寄存器访问,PORTxn 通过 PORTx 寄存器访问,PINxn 通过寄存器 PINx 访问。(x=A/B/C/D, n=0/1/2/3/4/5/6/7)。

DDRxn 用于控制端口的方向。当 DDRxn 为设置为 1, Pxn 端口将被配置为输出端口。如果 DDRxn 设置为 0, Pxn 端口将被配置为输入端口。

当 Pxn 被设置为输入端口后,PORTxn 写 1 将打开端口的上拉电阻。可以通过将 PORTxn 清零或将端口设为输出将上拉电阻关闭。系统上电复位后,所有端口均默认为输入三态,输出高阻。

当端口 Pxn 被配置为输出端口, PORTxn 位写 1 将端口驱动为高电平;将 PORTxn 清零将端口驱动为低电平。

当用户需要改变端口的输入输出状态时,需要特别注意,需要首先设置端口的输入输出状态(DDRx),然后修改端口的驱动(PORTx)。否则将会在端口上产生一个窄的脉冲,对系统电路造成干扰。

在配置端口的上拉电阻时,也会遇到同样的问题,用户需要在配置好端口的输入输出状态后,才能改变其他端口的控制。

| DDRxn | PORTxn | PUD | I/O 方向 | 上拉电阻 | 说明        |

|-------|--------|-----|--------|------|-----------|

| 0     | 0      | X   | 输入     | 关闭   | 三态(Hi-Z)  |

| 0     | 1      | 0   | 输入     | 打开   | 扇入        |

| 0     | 1      | 1   | 输入     | 关闭   | 三态(Hi-Z)  |

| 1     | 0      | Х   | 输出     | 关闭   | 输出低(扇入电流) |

| 1     | 1      | Х   | 输出     | 关闭   | 输出高(扇出电流) |

无论 DDRxn 的设置如何,端口的状态都可以通过 PINx 寄存器读出。PINx 上的同步器仅在 I/O 时钟的下降沿对信号进行了锁存,使得 PINx 能够及时的反映 PORTx 的设置以及端口的状态更新。

端口在设置了PORTx后,可以在下一个周期及时的读到端口的状态变化,而不需要任何的等待周期。

端口配置实例代码:

### 汇编代码实例

..

; Define pull-ups and set outputs high

; Define directions for port pins

ldi r17, (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0)

ldi r16,(1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0)

out PORTB, r16

out DDRB, r17

; Read port pins

in r16, PINB

---

#### C语言代码实例

```

unsigned char i;

```

/\* Define pull-ups and set outputs high and directions for port pins \*/

DDRB = (1 << DDB3)|(1 << DDB2)|(1 << DDB1)|(1 << DDB0);

PORTB = (1 << PB7)|(1 << PB6)|(1 << PB1)|(1 << PB0);

/\* Read port pins \*/

i = PINB;

#### I/O 应用注意事项

对于没有使用的引脚,建议给这些引脚一个确定的电平。及时我们在系统处于休眠模式时,内部关闭的这些引脚的输入使能,但是浮空的引脚仍然会在系统处于其他模式时产生漏电。

最简单的方法是打开这些引脚的内部上拉电阻。在系统上电或复位过程中,内部上拉的关闭的,如果用户需要在系统上电时仍然保持较低的功耗,建议使用外部的上拉或下拉。直接将不使用的引脚接到 VCC 或 GND 上的做法是不建议的,因为不正确的引脚配置可能会产生非常大的电流,导致芯片功能损坏。

SWD 双线调试接口默认为使能状态,建议用户在最终产品中,通过设置 MCUCR 寄存器中的 SWDD 位关闭 SWD 调试功能,以避免外部不可预知的干扰。

考虑到软件能够及时获得端口信号的变化, PINA/B/C/D 输入为异步设计,直接反应端口的状态。但这样的做法也同时带来了一些信号同步的问题。建议用户在直接使用端口状态进行程序流程控制时,采用必要的软件滤波算法。 同时也避免直接使用 PINA/B/C/D 寄存器的值进行程序流程控制,而是首先使用 IN 指令将其读到内部寄存器,然后使用寄存器的值作后续处理。下面将给出建议的使用端口作为程序流程控制的代码

#### 汇编代码实例

#### Label:

in r16, PINA

; Skip if PINA[1] is clear, avoid to use **sbic** directly

**sbrc** r16, 1

; Skip if PINA[1] is set, avoid to use sbis directly

**sbrs** r16,1

.....

#### C语言代码实例

```

\textbf{volatile unsigned } \textbf{char pv; } / \texttt{*} \textbf{volatile is necessary to disable optimize on `pv' *} / \texttt{*}

```

/\* wait until PINA[1] is set \*/

do {

pv = PINA;

} while ((pv&0x2) != 0x02); /\* avoid to use while(PINA&0x2) \*/

端口功能复用

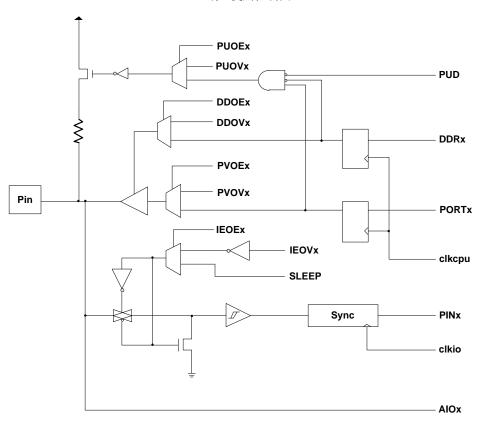

LGT8F0XA 系列微处理器的大部分引脚都具有多重功能。下图说明了端口功能与对应的控制信号之间的关系。并不是所有的复用控制信号都会出现在全部的端口上,下图只是用来简单的说明 LGT8F0XA 系列微处理器的端口一般关系。

端口复用控制图

下面的表格概况了端口复用控制信号的具体功能。这些复用控制信号由控制器内部自动产生。用户在正确的配置功能模块后,相应的端口复用控制就会生效。

# 端口复用功能控制信号的描述

| 信号    | 功能       | 描述                                      |

|-------|----------|-----------------------------------------|

| PUOE  | 上拉重载使能   | 当 PUOE 置位时,上拉使能由 PUOV 控制。               |

| POUE  |          | 当 PUOE 清零时,上拉使能由{DDRxn, PORTxn, PUD}控制。 |

|       | 上拉重载值    | 若 PUOE 置位,当 PUOV 置位时,上拉使能;当 PUOV 清      |

| PUOV  |          | <b>零时,上拉禁止。</b>                         |

|       |          | 若 PUOE 清零,PUOV 的值无效。                    |

| DDOE  | 数据方向重载使能 | 当 DDOE 置位时,数据方向由 DDOV 控制。               |

| DDOE  |          | 当 DDOE 清零时,数据方向由 DDRxn 控制。              |

|       | 数据方向重载值  | 若 DDOE 置位,当 DDOV 置位时,数据方向为输出;当 DDOV     |

| DDOV  |          | 清零时,数据方向为输入。                            |

|       |          | 若 DDOE 清零时,DDOV 的值无效。                   |

| PVOE  | 端口数据重载使能 | 当 PVOE 置位时,端口数据由 PVOV 控制。               |

| T VOL |          | 当 PVOE 清零时,端口数据由 PORTxn 控制。             |

|       | 端口数据重载值  | 若 PVOE 置位,当 PVOV 置位时,端口数据为高;当 PVOV      |

| PVOV  |          | 清零时,端口数据为低。                             |

|       |          | 若 PVOE 清零,PVOV 的值无效。                    |

|       | 输入使能重载使能 | 当 IEOE 置位时,输入使能由 IEOV 控制。               |

| IEOE  |          | 当 IEOE 清零时,输入使能由 MCU 的状态(睡眠与否) 控        |

|       |          | 制。                                      |

| IEOV  | 输入使能重载值  | 若 IEOE 置位,当 IEOV 置位时,输入使能;当 IEOV 清零时,   |

| ILOV  |          | 输入禁止。                                   |

| DI    | 数字输入     | 复用功能的数字输入。                              |

| AIO   | 模拟输入输出   | 模拟输入输出。信号直接与引脚相连,可用作双向端口。               |

# 端口A引脚复用功能的控制PA3-PA0

| 信号   | PA3/ADC3/PCINT3  | PA2/ADC2/PCINT2  | PA1/ADC1/PCINT1  | PA0/ADC0/PCINT0  |

|------|------------------|------------------|------------------|------------------|

| PUOE | 0                | 0                | 0                | 0                |

| PUOV | 0                | 0                | 0                | 0                |

| DDOE | 0                | 0                | 0                | 0                |

| DDOV | 0                | 0                | 0                | 0                |

| PVOE | 0                | 0                | 0                | 0                |

| PVOV | 0                | 0                | 0                | 0                |

| IEOE | PCIEO & PCINT3 & | PCIEO & PCINT2 & | PCIEO & PCINT1 & | PCIEO & PCINTO & |

| IEOE | ~ADC3D           | ~ADC2D           | ~ADC1D           | ~ADC0D           |

| IEOV | 1                | 1                | 1                | 1                |

| DI   | PCINT3           | PCINT2           | PCINT1           | PCINT0           |

| AIO  | ADC3             | ADC2             | ADC1             | ADC0             |

# 端口A引脚复用功能的控制PA7-PA4

| 信号   | PA7/ADC7/PCINT7  | PA6/ADC6/PCINT6  | PA5/ADC5/PCINT5  | PA4/ADC4/PCINT4  |

|------|------------------|------------------|------------------|------------------|

| PUOE | 0                | 0                | 0                | 0                |

| PUOV | 0                | 0                | 0                | 0                |

| DDOE | 0                | 0                | 0                | 0                |

| DDOV | 0                | 0                | 0                | 0                |

| PVOE | 0                | 0                | 0                | 0                |

| PVOV | 0                | 0                | 0                | 0                |

| IEOE | PCIEO & PCINT7 & | PCIEO & PCINT6 & | PCIEO & PCINT5 & | PCIEO & PCINT4 & |

|      | ~ADC7D           | ~ADC6D           | ~ADC5D           | ~ADC4D           |

| IEOV | 1                | 1                | 1                | 1                |

| DI   | PCINT7           | PCINT6           | PCINT5           | PCINT4           |

| AIO  | ADC7             | ADC6             | ADC5             | ADC4             |

# 端口B引脚复用功能的控制PB3-PB0

| 信号   | PB3/AIN1/PCINT11  | PB2/AIN0/PCINT10  | PB1/ PCINT9      | PBO/ PCINT8      |

|------|-------------------|-------------------|------------------|------------------|

| PUOE | 0                 | 0                 | 0                | 0                |

| PUOV | 0                 | 0                 | 0                | 0                |

| DDOE | 0                 | 0                 | 0                | 0                |

| DDOV | 0                 | 0                 | 0                | 0                |

| PVOE | 0                 | 0                 | 0                | XCKO_EN          |

| PVOV | 0                 | 0                 | 0                | хско             |

| IEOE | PCIE1 & PCINT11 & | PCIE1 & PCINT10 & | PCIE1 & PCINT9 + | PCIE1 & PCINT8 + |

|      | ~AIN1D            | ~AIN0D            | EXT1_EN          | EXTO_EN +        |

|      |                   |                   |                  | XCKI_EN          |

| IEOV | 1                 | 1                 | 1                | 1                |

| DI   | PCINT11           | PCINT10           | PCINT9/T1        | PCINT8/T0/XCKI   |

| AIO  | AIN1              | AIN0              | -                | -                |

# 端口 C 引脚复用功能的控制 PC3-PC0

| 信号   | PC3/ PCINT19      | PC2/ PCINT18    | PC1/ PCINT17      | PCO/ PCINT16      |

|------|-------------------|-----------------|-------------------|-------------------|

| PUOE | SWD_EN            | SWD_EN          | 0                 | 0                 |

| PUOV | 1                 | 0               | 0                 | 0                 |

| DDOE | SWD_EN            | SWD_EN          | 0                 | 0                 |

| DDOV | ~SWDO             | 0               | 0                 | 0                 |

| PVOE | SWD_EN            | 0               | 0                 | 0                 |

| PVOV | 0                 | 0               | 0                 | 0                 |

| IEOE | PCIE2 & PCINT19 + | PCIE2 & PCINT18 | PCIE2 & PCINT17 & | PCIE2 & PCINT16 & |

|      | SWD_EN            |                 | ~OSCM_EN          | ~OSCM_EN          |

# 端口 C 引脚复用功能的控制 PC3-PC0 (接上页)

| IEOV | 1       | 1       | 1       | 1       |

|------|---------|---------|---------|---------|

| DI   | PCINT19 | PCINT18 | PCINT17 | PCINT16 |

|      | SWDI    | SWCI    |         |         |

| AIO  | -       | -       | XTAL2   | XTAL1   |

# 端口 C 引脚复用功能的控制 PC6

| 信号   | PC6/ PCINT22      |

|------|-------------------|

| PUOE | 0                 |

| PUOV | 0                 |

| DDOE | 0                 |

| DDOV | 0                 |

| PVOE | OCO_EN            |

| PVOV | OC0               |

| IEOE | PCIE2 & PCINT22 + |

|      | WAKUP_EN          |

| IEOV | 1                 |

| DI   | PCINT22           |

|      | WAKUP             |

| AIO  | -                 |

# 端口 D 引脚复用功能的控制 PD3-PD0

| 信号   | PD3/PCINT27       | PD2/PCINT26       | PD1/PCINT25     | PD0/PCINT24       |

|------|-------------------|-------------------|-----------------|-------------------|

| PUOE | 0                 | 0                 | TXEN            | RXEN              |

| PUOV | 0                 | 0                 | 0               | PORTD0 & ~PUD     |

| DDOE | 0                 | 0                 | TXEN            | RXEN              |

| DDOV | 0                 | 0                 | 1               | 0                 |

| PVOE | 0                 | 0                 | TXEN            | 0                 |

| PVOV | 0                 | 0                 | TXD             | 0                 |

| IEOE | PCIE0 & PCINT27 + | PCIE0 & PCINT26 + | PCIEO & PCINT25 | PCIE0 & PCINT24 + |

|      | EINT1_EN          | EINTO_EN          |                 | RXEN              |

|      |                   |                   |                 |                   |

| IEOV | 1                 | 1                 | 1               | 1                 |

| DI   | PCINT27           | PCINT26           | PCINT25         | PCINT24           |

|      | INT1              | INTO              |                 | RXD               |

| AIO  | -                 | -                 | -               | -                 |

# 端口 D 引脚复用功能的控制 PD7-PD4

| 信号   | PD7/ PCINT31      | PD6/PCINT30       | PD5/PCINT29     | PD4/PCINT28     |

|------|-------------------|-------------------|-----------------|-----------------|

| PUOE | 0                 | 0                 | 0               | 0               |

| PUOV | 0                 | 0                 | 0               | 0               |

| DDOE | 0                 | 0                 | 0               | 0               |

| DDOV | 0                 | 0                 | 0               | 0               |

| PVOE | 0                 | 0                 | OC1A_EN         | OC1B_EN         |

| PVOV | 0                 | 0                 | OC1A            | OC1B            |

| IEOE | PCIEO & PCINT31 + | PCIE0 & PCINT30 + | PCIEO & PCINT29 | PCIEO & PCINT28 |

|      | EINT2_EN          | ICP1_EN           |                 |                 |

| IEOV | 1                 | 1                 | 1               | 1               |

| DI   | PCINT31           | PCINT30           | PCINT29         | PCINT28         |

|      | INT2              | ICP1              |                 |                 |

| AIO  | -                 | -                 | -               | -               |

#### 寄存器定义

#### PORTA - 端口 A 驱动输出寄存器

| ţ | 地址: 0x02 |            |     | 默认值: 0x00    |

|---|----------|------------|-----|--------------|

|   | Bit      | Name W/R   |     | 描述           |

|   | 7:0      | PORTA[7:0] | W/R | A 组端口输出驱动寄存器 |

## DDRA - 端口A输入/输出方向控制寄存器

| 地址: | 0x01      |     | 默认值: 0x00        |

|-----|-----------|-----|------------------|

| Bit | Name      | W/R | 描述               |

| 7:0 | DDRA[7:0] | W/R | 控制 A 组端口的输入、输出方向 |

#### PINA - 端口A 输入寄存器

| 地址: | 0x00      |     | 默认值: N/A       |

|-----|-----------|-----|----------------|

| Bit | Name      | W/R | 描述             |

| 7:0 | PINA[7:0] | W/R | 直接反应端口 A 的电平状态 |

## PORTB - 端口B 驱动输出寄存器

| 地址: | 0x05       |     | 默认值: 0x00           |

|-----|------------|-----|---------------------|

| Bit | Name       | W/R | 描述                  |

| 3:0 | PORTB[3:0] | W/R | B 组端口输出驱动寄存器        |

| 7:4 | PORTB[7:4] | -   | 端口 B 位 4 位端口,此处为保留位 |

## DDRB - 端口B输入/输出方向控制寄存器

| 地址:( | 0x04      |     | 默认值: 0x00           |

|------|-----------|-----|---------------------|

| Bit  | Name      | W/R | 描述                  |

| 3:0  | DDRB[3:0] | W/R | 控制B组端口的输入、输出方向      |

| 7:4  | DDRB[7:4] | -   | 端口 B 位 4 位端口,此处为保留位 |

## PINB - 端口B 输入寄存器

| 地址: | 0x03      |     | 默认值: N/A            |

|-----|-----------|-----|---------------------|

| Bit | Name      | W/R | 描述                  |

| 3:0 | PINB[3:0] | W/R | 直接反应端口 B 的电平状态      |

| 7:4 | PINB[7:4] | -   | 端口 B 位 4 位端口,此处为保留位 |

### PORTC - 端口 C 驱动输出寄存器

| 地址: | 0x08       |     | 默认值: 0x00       |

|-----|------------|-----|-----------------|

| Bit | Name       | W/R | 描述              |

| 3:0 | PORTC[3:0] | W/R | C组端口输出驱动寄存器     |

| 5:4 | PORTC[5:4] | -   | 保留位             |

| 6   | PORTC[6]   | W/R | C 组端口 6 输出驱动寄存器 |

| 7   | PORTC[7]   | -   | 保留位             |

## DDRC-端口C驱动输出寄存器

| 地址: | 0x07      |     | 默认值: 0x00          |

|-----|-----------|-----|--------------------|

| Bit | Name      | W/R | 描述                 |

| 3:0 | DDRC[3:0] | W/R | C 组端口输入/输出方向寄存器    |

| 5:4 | DDRC[5:4] | -   | 保留位                |

| 6   | DDRC[6]   | W/R | C 组端口 6 输入/输出方向寄存器 |

| 7   | DDRC[7]   | -   | 保留位                |

## PINC - 端口 C 驱动输出寄存器

| 地址: | 0x06      |     | 默认值: N/A      |

|-----|-----------|-----|---------------|

| Bit | Name      | W/R | 描述            |

| 3:0 | PINC[3:0] | W/R | C组端口输入寄存器     |

| 5:4 | PINC[5:4] | -   | 保留位           |

| 6   | PINC[6]   | W/R | C 组端口 6 输入寄存器 |

| 7   | PINC[7]   | -   | 保留位           |

## PORTD - 端口D 驱动输出寄存器

| t | 地址: 0x05 |            |     | 默认值: 0x00    |

|---|----------|------------|-----|--------------|

|   | Bit      | Name       | W/R | 描述           |

|   | 7:0      | PORTD[7:0] | W/R | D 组端口输出驱动寄存器 |

## DDRD - 端口 D 输入/输出方向控制寄存器

| 地址: | 0x04      |     | 默认值: 0x00        |

|-----|-----------|-----|------------------|

| Bit | Name      | W/R | 描述               |

| 7:0 | DDRD[7:0] | W/R | 控制 D 组端口的输入、输出方向 |

## PIND - 端口D 输入寄存器

| 地址: | 0x03      |     | 默认值: N/A       |

|-----|-----------|-----|----------------|

| Bit | Name      | W/R | 描述             |

| 7:0 | PIND[7:0] | W/R | 直接反应端口 D 的电平状态 |

# 通用同步/异步串行收发器(USART)

#### 主要特点

- 全双工操作(独立的串行接收和发送寄存器)

- 异步或同步操作

- 主机或从机操作

- 高精度的波特率发生器

- 支持 5, 6, 7, 8, 或 9 个数据位和 1, 或 2 个停止位

- 硬件支持的奇偶产生和校验机制

- 数据讨谏检测

- 帧错误检测

- 噪声滤波,包括错误的起始位检测以及数字低通滤波器

- 三个独立的中断,包括:发送结束中断,发送数据寄存器空中断,以及接收结束中断

- 多处理器通信模式

- 倍速异步通信模式

#### 综计

当设置 UCSRC 的 UMSEL1 位为 "0"时,使能 USART 工作模式。USART 占用 USPI 的资源,主要包括三个部分:时钟发生器,发送器和接收器。控制和状态寄存器由这三个部分共享。时钟发生器由波特率发生器和同步从机操作模式下外部输入时钟的同步逻辑组成。XCK 引脚只用于同步传输模式。发送器包括一个写数据缓冲器,串行移位寄存器,奇偶发生器以及处理不同帧格式所需的控制逻辑。写数据缓冲器允许连续发送数据而不会在数据帧之间引入延迟。接收器具有时钟和数据恢复单元,用于异步数据的接收。除了恢复单元,接收器还包括奇偶校验,控制逻辑,串行移位寄存器和一个两级接收缓冲器 UDR。接收器支持与发送器相同的帧格式,而且可以检测帧错误,数据过速和奇偶校验错误。

## 时钟发生器

时钟产生逻辑为发送器和接收器产生基础时钟。USART 支持 4 种模式的时钟: 正常的异步模式, 倍速的异步模式, 主机同步模式, 以及从机同步模式。USCRC 的 UMSELO 位用于选择同步或异步模式。USCRA 的 U2X 位控制异步模式下的倍速使能。仅在同步模式下有效的 XCK 引脚的数据方向寄存器(与 IO 复用)决定了时钟源是由内部产生(主机模式)还是外部产生(从机模式)。

### 波特率发生器

波特率寄存器 UBRR 和降序计数器连接在一起作为 USART 的可编程的预分频器或波特率发生器。降序计数器工作在系统时钟( $f_{sys}$ )下,当其计数到零或 UBRRL 寄存器被写时,会自动加载 UBRR 寄存器的值。当计数到零时产生一个时钟,该时钟作为波特率发生器的输出时钟,频率为  $f_{sys}$ /(UBRR+1)。

下表给出了各种工作模式下计算波特率(位/秒)以及 UBRR 值的公式。

| 工作模式   | 波特率计算公式(1)                     | UBRR 值计算公式                     |

|--------|--------------------------------|--------------------------------|

| 异步正常模式 | $BAUD = f_{sys}/(16*(UBRR+1))$ | UBRR = $f_{sys}/(16*BAUD) - 1$ |

| 异步倍速模式 | BAUD = $f_{sys}/(8*(UBRR+1))$  | UBRR = $f_{sys}/(8*BAUD) - 1$  |

| 同步主机模式 | $BAUD = f_{sys}/(2*(UBRR+1))$  | UBRR = $f_{sys}/(2*BAUD) - 1$  |

#### 说明:

- 1. 波特率定义为每秒的位传输速度(bps);

- 2. BUAD 为波特率, f<sub>svs</sub> 为系统时钟, UBRR 为波特率寄存器 UBRRH 和 UBRRL 的组合值。

倍速工作模式

通过设定 UCSRA 寄存器的 U2X 位可以是传输速率加倍,该位只在异步工作模式下有效,同步工作模式下置该位为"0"。

设置该位将会把波特率分频器的分频值减半,有效地加倍异步通信的传输速率。在这种情况下,接收器只使用一半的采样数来对数据进行采样及时钟恢复,因此需要更精准的波特率设置和系统时钟。发送器则没有变化。

外部时钟

同步从机操作模式由外部时钟驱动。外部时钟经过同步寄存器和边沿检测器之后才被发送器和接收器使用,这一过程会引入两个系统时钟的延时,因此外部 XCK 的最大时钟频率由以下公式限制:

$$f_{XCK} < f_{sys}/4$$

要注意 fsys 有系统时钟的稳定性决定,为了防止因频率漂移而丢失数据,建议保留足够的裕量。

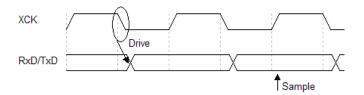

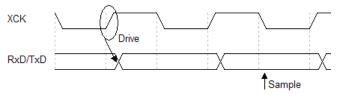

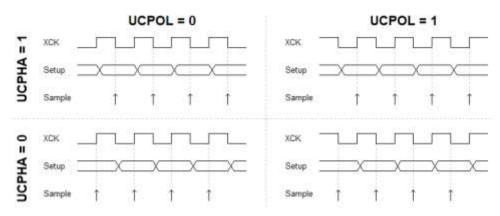

同步时钟操作

同步模式下,XCK 引脚被用于时钟输入(从机模式)或时钟输出(主机模式)。时钟的边沿与数据采样和数据变化关系的基本规律是:对数据输入端(RXD)采样所使用的时钟沿与数据输出端变化所使用的时钟沿是相反的。

UCPOL = 1

UCPOL = 0

同步模式下的 XCK 时序

如上图所示,当 UCPOL 值为"1"时,在 XCK 的下降沿改变数据输出,在 XCK 的上升沿进行数据采样;当 UCPOL 值为"0"时,在 XCK 的上升沿改变数据输出,在 XCK 的下降沿进行数据采样。

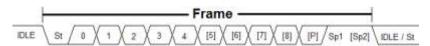

帧格式

- 一个串行数据帧由数据字加上同步位(起始位和停止位)以及用于纠错的奇偶校验位构成。USART 接受以下 30 种组合的数据帧格式:

- 1 个起始位

- 5、6、7、8或9个数据位

- 无校验位、奇校验位或偶校验位

- 1 或 2 个停止位

数据帧以起始位开始,紧接着是数据字的最低位,接着是其它数据位,以数据字的最高位结束,最多成功传输 9 位数据。如果使能了校验,校验位将紧接着数据字,最后是停止位。当一个完整的数据帧传输后,可以立即传输下一个新的数据帧,或者使传输线处于空闲(高电平)状态。下图为可能的数据帧结构,方括号中的位是可选的。

说明:

- 1) IDLE 通信线 (RxD 或 TxD) 上没有数据传输,线路空闲时必须为高电平

- 2) St 起始位,总是为低电平

- 3) 0-8 数据位

4) P 校验位,

奇校验或偶校验

5) Sp 停止位,总是为高电平

数据帧的结构由 UCSRB 和 UCSRC 寄存器中的 UCSZ[2:0]、UPM[1:0]和 USBS 设定。接收与发送使用相同的设置。设置的任何改变都可能破坏正在进行的数据传输。其中,UCSZ[2:0]确定了数据帧的数据位数,UPM[1:0]用于使能和确定校验的类型,USBS 设置帧有一位或两位结束位。接收器会忽略第二个停止位,因此帧错误只在第一个结束位为"0"时被检测到。

校验位计算

校验位的计算是对数据的各个位进行异或运算。如果选择了奇校验,则异或结果还需要取反。校验位与数据位的 关系如下:

$\begin{aligned} P_{even} &= d_{n-1} \oplus ... \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 0 \\ P_{odd} &= d_{n-1} \oplus ... \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 1 \end{aligned}$

说明:

- 1) Peven 偶校验结果

- 2) Podd 奇校验结果

- 3) d<sub>n</sub> 第 n 个数据位

USART 初始化

进行通信之前首先要对 USART 进行初始化。初始化过程通常包括波特率的设定,帧结构的设定,以及根据需要使能接收器或发送器。对于中断驱动的 USART 操作,在初始化时要清零全局中断标志并禁止 USART 的所有中断。在进行重新初始化比如改变波特率或帧结构时,必须确保没有数据传输。TXC 标志位可以用来检测发送器是否完成了所有传输,RXC 标志位可以用来检测接收缓冲器中是否还有数据未被读出。如果 TXC 标志位用作此用途,在每次发送数据之前(写 UDR 寄存器之前)必须清零 TXC 标志位。

发送器

置位 UCSRB 寄存器的 TXEN 位将使能 USART 的数据发送。使能后 TxD 引脚的通用 IO 功能即被 USART 功能所取代,成为发送器的串行输出。发送数据之前要设置好波特率、工作模式与帧格式。如果使用同步发送模式,施加于 XCK 引脚上的时钟信号即为数据发送的时钟。

发送5到8位数据的帧

将需要发送的数据加载到发送缓冲器中来启动数据发送。CPU 通过写 UDR 寄存器来加载数据。当发送移位寄存器可以发送新一帧数据的时候,缓冲器中的数据将转移到移位寄存器中。当移位寄存器处于空闲状态(没有正在进行的数据传输),或者前一帧数据的最后一个停止位发送完毕,它将加载新的数据。一旦移位寄存器加载了新的数据,它将按照既定的设置传输一个完整的帧。

发送9位数据的帧

如果发送 9 位数据的帧,应先将数据的第 9 位写入寄存器 UCSRB 的 TXB8 位,然后再将低 8 位数据写入发送数据寄存器 UDR。第 9 位数据在多机通信中用于表示地址帧,在同步通信中可以用于协议处理。

发送奇偶校验位

奇偶校验产生电路为串行数据帧生成相应的校验位。当校验位使能时(UPM1=1),发送控制逻辑电路会在数据字的最后一位与第一个停止位之间插入奇偶校验位。

发送标志位与中断 处理 USART 发送器有两个标志位: USART 数据寄存器空标志 UDRE 和传输结束标志 TXC,两个标志位都可以产生中断。数据寄存器空标志 UDRE 用来表示发送缓冲器是否可以写入一个新的数据。该位在发送缓冲器空时被置"1",满时被置"0"。当 UDRE 位为"1"时,CPU 可以往数据寄存器 UDR 写入新的数据,反之则不能。

当 UCSRB 寄存器中的数据寄存器空中断使能位 UDRIE 为"1"时,只要 UDRE 被置位(且全局中断使能),就将产生 USART 数据寄存器空中断请求。对寄存器 UDR 执行写操作将清零 UDRE。当采用中断方式传输数据时,在数据寄存器空中断服务程序中必须写入一个新的数据到 UDR 以清零 UDRE,或者是禁止数据寄存器空中断。否则一旦该中断服务程序结束,一个新的中断将再次产生。

禁止发送器

整个数据帧被移出发送移位寄存器,同时发送寄存器中又没有新的数据时,发送结束标志 TXC 将被置位。当 UCSRB 上的发送结束中断使能位 TXCIE(且全局中断使能)置"1"时,随着 TXC 标志位被置位,USART 发送结束中断将被执行。一旦进入中断服务程序,TXC 标志位即被自动清零,CPU 也可以对该位写"1"来清零。

接收器

当 TXEN 清零后,只有等所有的数据都发送完成以后发送器才能够真正禁止,即发送移位寄存器与发送缓冲寄存器中都没有要传送的数据。发送器禁止以后,TxD 引脚恢复其通用 IO 功能。

置位 UCSRB 寄存器的接收允许位 (RXEN)即可启动 USART 接收器。使能后 RxD 引脚的通用 IO 功能被 USART 功能 所取代,成为接收器的串行输入口。进行数据接收之前首先要设置好波特率、操作模式及帧格式。如果使用同步接收模式,XCK 引脚上的时钟被用为传输时钟。

接收5到8位数据的帧

一旦接收器检测到一个有效的起始位,便开始接受数据。起始位后的每一位数据都将以所设定的波特率或 XCK 时钟来进行接收,直到收到一帧数据的第一个停止位,第二个停止位会被接收器忽略。接收到的每一位数据被送入接收移位寄存器,收到第一个停止位以后,接收器置位位于 UCSRA 寄存器的接收数据完成标志 RXC 位,并把移位寄存器中完整的数据帧转移到接收缓冲器中,CPU 通过读取 UDR 寄存器就可以获得接收到的数据。

接收 9 位数据的帧

如果设定了9位数据的数据帧,在从UDR 读取低8位数据之前必须首先读取寄存器 UCSRB的 RXB8位来获得第9位数据。这个规则同样适用于状态标志位FE、DOR以及PE。读取UDR存储单元会改变接收缓冲器的状态,进而改变同样存储于缓冲器中的TXB8、FE、DOR及PE位。

接收结束及中断

USART 接收器有一个标志位:接收结束标志 RXC,用来表明接收缓冲器中是否有未被读出的数据。当接收缓冲器中有未被读出的数据时,此位为"1",反之为"0"。如果接收器被禁止,接收缓冲器会被刷新,RXC 也会被清零。置位 UCSRB 的接收结束中断使能位 RXCIE 后,只要 RXC 标志被置位(且全局中断被使能),就会产生 USART 接收结束中断。使用中断方式进行数据接收时,数据接收结束中断服务程序必须从 UDR 读取数据来清零 RXC 标志,否则只要中断处理程序一结束,一个新的中断就会产生。

接收器错误标志

USART 接收器有三个错误标志: 帧错误 FE、数据溢出 DOR 及奇偶校验错误 PE。它们都位于 UCSRA 寄存器。错误标志与数据帧一起保存在接收缓冲器当中。所有的错误标志都不能产生中断。

帧错误标志 FE 表明存储在接收缓冲器中的下一个可读帧的第一个停止位的状态。停止位正确(值为"1")则 FE 标志为"0",否则 FE 标志为"1"。这个标志可用来检测同步丢失、传输中断,也可用于协议处理。

数据溢出标志 DOR 表明由于接收缓冲器满造成了数据丢失。当接收缓冲器为满,接收移位寄存器中已有数据,若此时检测到一个新的起始位,数据溢出就产生了。DOR 标志被置位即表明在最近一次读取 UDR 和下一次读取 UDR 之间丢失了一个或多个数据帧。当数据帧成功地从移位寄存器转入接收缓冲器后,DOR 标志被清零。 奇偶校验错标志 PE 表明接收缓冲器中的下一帧数据在接收时有奇偶错误。如果不使能奇偶校验,PE 被清零。

奇偶校验器

置位奇偶校验模式位 UPM1 将启动奇偶校验器。校验的模式(偶校验或奇校验)由 UPM0 决定。奇偶校验使能后,校验器将计算输入数据的奇偶并把结果与数据帧的奇偶位进行比较。校验结果将与数据和停止位一起存储在接收缓冲器中。CPU 通过读取 PE 位来检查接收的帧当中是否有奇偶错误。如果下一个从接收缓冲器中读出的数据有奇偶错误,并且奇偶校验使能,则 UPE 被置位,一直有效到接收缓冲器 UDR 被读取。

禁止接收器

与发送器相比,禁止接收器即刻起作用。正在接收的数据将丢失。禁止接收器(RXEN 清零)后,接收器将不再占用 RxD 引脚,接收缓冲器也会被刷新。

异步数据接收

USART 有一个时钟恢复单元和数据恢复单元来处理异步数据接收。时钟恢复逻辑用于同步从 RxD 引脚输入的异步串行数据和内部的波特率时钟。数据恢复逻辑用于采集数据,并通过低通滤波器过滤所输入的每一位数据,从而提高接收器的抗干扰性能。异步接收的工作范围依赖于内部波特率时钟的精度、帧输入的速率及一帧所包含的数据位数。

异步工作范围

接收器的工作范围依赖于接收到的数据速率与内部波特率之间的不匹配程度。如果发送器以过快或过慢的比特率传输数据,或者接收器内部产生的波特率没有相同的频率,那么接收器就无法与起始位同步。为了确保接收器不会错过下一帧起始位的采样,数据输入速率和内部接收器波特率不能相差太大,用它们之间的比值来描述波特率的误差范围。下面两个表格分别给出了普通模式下和倍速模式下容许的最大波特率误差范围。

| 数据位+奇偶位长度和 | 最大误差范围(%) | 推荐误差范围(%) |

|------------|-----------|-----------|

| 5          | +6.7/-6.8 | $\pm 3.0$ |

| 6          | +5.8/-5.9 | ±2.5      |

| 7          | +5.1/-5.2 | ±2.0      |

| 8          | +4.6/-4.5 | ±3.0      |

| 9          | +4.1/-4.2 | ±1.5      |

| 10         | +3.8/-3.8 | ±1.5      |

#### 倍速模式下最大接收器波特率误差范围

| 数据位+奇偶位长度和 | 最大误差范围(%) | 推荐误差范围(%) |

|------------|-----------|-----------|

| 5          | +5.7/-5.9 | ±2.5      |

| 6          | +4.9/-5.1 | ±2.0      |

| 7          | +4.4/-4.5 | ±1.5      |

| 8          | +3.9/-4.0 | ±1.5      |