© 1995 National Semiconductor Corporation TL/K/5558

RRD-B30M115/Printed in U. S. A.

| Absolute Maximum Ra                                                                                                    | tings                                |                                                                                                                                                                      |                                   |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| If Military/Aerospace specified d<br>please contact the National S<br>Office/Distributors for availability<br>(Note 5) | emiconductor Sales                   | Peak Output Current (50 ms pulse), $I_{O(Pk)}$<br>Output Short Circuit Duration<br>(within rated power dissipation,<br>$R_{SC} = 0.35\Omega$ , $T_A = 25^{\circ}C$ ) | ) 5A<br>Continuous                |

| Supply Voltage, VS                                                                                                     | $\pm$ 22V                            | Operating Temperature Range, T <sub>A</sub>                                                                                                                          |                                   |

| Power Dissipation at $T_A = 25^{\circ}$ C, $P_D$<br>Derate linearly at 25°C/W to zero                                  | 5W<br>at 150°C,                      | LH0101AC, LH0101C<br>LH0101A, LH0101                                                                                                                                 | −25°C to +85°C<br>−55°C to +125°C |

| Power Dissipation at $T_C = 25^{\circ}C$<br>Derate linearly at 2°C/W to zero a                                         | 62W<br>t 150°C                       | Storage Temperature Range, T <sub>STG</sub><br>Maximum Junction Temperature, T <sub>J</sub>                                                                          | −65°C to +150°C<br>150°C          |

| Differential Input Voltage, V <sub>IN</sub>                                                                            | $\pm$ 40V but $< \pm$ V <sub>S</sub> | Lead Temperature (Soldering <10 sec.)                                                                                                                                | 260°C                             |

| Input Voltage Range, V <sub>CM</sub>                                                                                   | $\pm$ 20V but $<\pm$ V_S             | ESD rating to be determined.                                                                                                                                         |                                   |

| Thermal Resistance—                                                                                                    |                                      | -                                                                                                                                                                    |                                   |

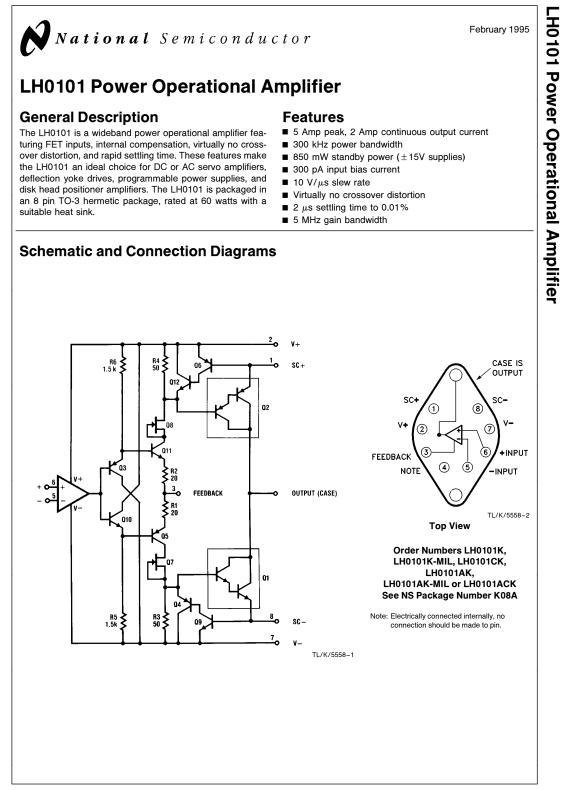

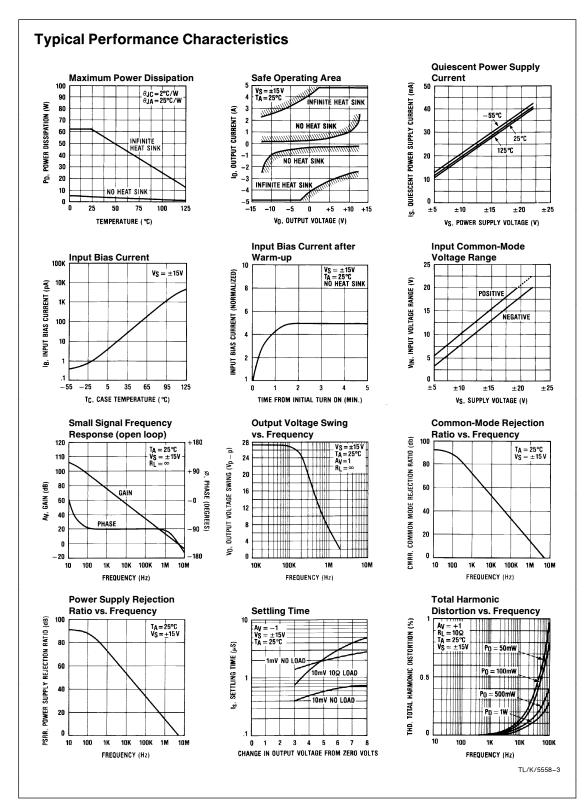

See Typical Performance Characteristics

| DC Electrical Characteristics (Note 1) $V_S = \pm 15V$ , $T_A = 25^{\circ}C$ unless otherwise noted |

|-----------------------------------------------------------------------------------------------------|

| Symbol                            | Parameter                                                  | C                                      | Conditions         |            | LH0101AC<br>LH0101A |       |     | LH0101C<br>LH0101 |       |      | Units |

|-----------------------------------|------------------------------------------------------------|----------------------------------------|--------------------|------------|---------------------|-------|-----|-------------------|-------|------|-------|

|                                   |                                                            |                                        |                    |            | Min                 | Тур   | Max | Min               | Тур   | Max  |       |

| V <sub>OS</sub>                   | Input Offset Voltage                                       |                                        |                    |            |                     | 1     | 3   |                   | 5     | 10   | mV    |

|                                   |                                                            | $T_{MIN} \leq T_{A} \leq T_{MAX}$      |                    |            | 7                   |       |     | 15                |       |      |       |

| ΔV <sub>OS</sub> /ΔP <sub>D</sub> | Change in<br>Input Offset Voltage<br>with Dissipated Power | (Note 2)                               |                    |            |                     | 150   |     |                   | 300   |      | μV/W  |

| ΔV <sub>OS</sub> /ΔT              | Change in<br>Input Offset Voltage<br>with Temperature      | $V_{CM} = 0$                           |                    |            |                     | 10    |     |                   | 10    |      | μV/°C |

| IB                                | Input Bias Current                                         |                                        |                    |            |                     |       | 300 |                   |       | 1000 | pА    |

|                                   |                                                            |                                        | TA < THANK         | LH0101C/AC |                     |       | 60  |                   |       | 60   | nA    |

|                                   |                                                            |                                        | ·A = ·MAA          | LH0101/A   |                     |       | 300 |                   |       | 1000 |       |

| I <sub>OS</sub>                   | Input Offset Current                                       |                                        |                    |            |                     |       | 75  |                   |       | 250  | pА    |

|                                   |                                                            |                                        | $T_A \leq T_{MAX}$ | LH0101C/AC |                     |       | 15  |                   |       | 15   | nA    |

|                                   |                                                            |                                        |                    | LH0101/A   |                     |       | 75  |                   |       | 250  |       |

| A <sub>VOL</sub>                  | Large Signal<br>Voltage Gain                               | $V_O = \pm 10V R_L = 10\Omega$         |                    |            | 50                  | 200   |     | 50                | 200   |      | V/mV  |

| VO                                | Output Voltage Swing                                       | $R_{SC} = 0$                           | $R_L = 100\Omega$  |            | ±12                 | ±12.5 |     | ±12               | ±12.5 |      |       |

|                                   |                                                            | $A_V = +1$                             | $R_L = 10\Omega$   |            | ±11.25              | ±11.6 |     | ±11.25            | ±11.6 |      | v     |

|                                   |                                                            | Note 3                                 | $R_L = 5\Omega$    |            | ±10.5               | ±11   |     | ±10.5             | ±11   |      |       |

| CMRR                              | Common Mode<br>Rejection Ratio                             | $\Delta V_{IN} = \pm 10V$              |                    |            | 85                  | 100   |     | 85                | 100   |      | dB    |

| PSRR                              | Power Supply<br>Rejection Ratio                            | $\Delta V_{S} = \pm 5 V$ to $\pm 15 V$ |                    |            | 85                  | 100   |     | 85                | 100   |      |       |

| IS                                | Quiescent Supply<br>Current                                |                                        |                    |            |                     | 28    | 35  |                   | 28    | 35   | mA    |

|                                   |                                                            |                                        |                    |            |                     |       |     |                   |       |      |       |

| Symbol                          | Parameter                              | Conditions                         |             | LH0101<br>LH0101A |       | LH0101C<br>LH0101AC |     |       | Units |      |

|---------------------------------|----------------------------------------|------------------------------------|-------------|-------------------|-------|---------------------|-----|-------|-------|------|

|                                 |                                        |                                    |             | Min               | Тур   | Max                 | Min | Тур   | Max   |      |

| e <sub>n</sub>                  | Equivalent Input<br>Noise Voltage      | f = 1 kHz                          |             |                   | 25    |                     |     | 25    |       | nV√H |

| C <sub>IN</sub>                 | Input Capacitance                      | f = 1 MHz                          |             |                   | 3.0   |                     |     | 3.0   |       | pF   |

|                                 | Power Bandwidth, -3 dB                 |                                    |             |                   | 300   |                     |     | 300   |       | kHz  |

| SR                              | Slew Rate                              | $R_L = 10\Omega$                   |             | 7.5<br>(Note 4)   | 10    |                     |     | 10    |       | V/μ: |

| t <sub>r</sub> , t <sub>f</sub> | Small Signal Rise or<br>Fall Time      | Π <u></u> 1032                     | $A_V = + 1$ |                   | 200   |                     |     | 200   |       | ns   |

|                                 | Small Signal Overshoot                 |                                    |             |                   | 10    |                     |     | 10    |       | %    |

| GBW                             | Gain-Bandwidth Product                 | R <sub>I</sub> = ∞                 |             | 4.0<br>(Note 4)   | 5.0   |                     |     | 5.0   |       | MHz  |

| t <sub>s</sub>                  | Large Signal Settling<br>Time to 0.01% | η <u></u> – ω                      |             |                   | 2.0   |                     |     | 2.0   |       | μs   |

| THD                             | Total Harmonic Distortion              | $P_0 = 10W, f$<br>$R_L = 10\Omega$ | = 1 kHz     |                   | 0.008 |                     |     | 0.008 |       | %    |

Note 1: Specification is at  $T_A = 25^{\circ}$ C. Actual values at operating temperature may differ from the  $T_A = 25^{\circ}$ C value. When supply voltages are ±15V, quiescent operating junction temperature will rise approximately 20°C without heat sinking. Accordingly, V<sub>OS</sub> may change 0.5 mV and I<sub>B</sub> and I<sub>OS</sub> will change significantly during warm-ups. Refer to the I<sub>B</sub> vs. temperature and power dissipation graphs for expected values. Power supply voltage is ±15V. Temperature tests are made only at extremes.

Note 2: Change in offset voltage with dissipated power is due entirely to average device temperature rise and not to differential thermal feedback effects. Test is performed without any heat sink.

Note 3: At light loads, the output swing may be limited by the second stage rather than the output stage. See the application section under "Output swing enhancement" for hints on how to obtain extended operation.

Note 4: These parameters are sample tested to 10% LTPD.

Note 5: Refer to RETS0101AK for the LH0101AK military specifications and RETS0101K for the LH0101K military specifications.

# **Application Hints**

# Input Voltages

The LH0101 operational amplifier contains JFET input devices which exhibit high reverse breakdown voltages from gate to source or drain. This eliminates the need for input clamp diodes, so that high differential input voltages may be applied without a large increase in input current. However, neither input voltage should be allowed to exceed the negative supply as the resultant high current flow may destroy the unit.

Exceeding the negative common-mode limit on either input will cause a reversal of the phase to the output and force the amplifier output to the corresponding high or low state. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

These amplifiers will operate with the common-mode input voltage equal to the positive supply. In fact, the common-mode voltage may exceed the positive supply by approximately 100 mV, independent of supply voltage and over the full operating temperature range. The positive supply may therefore be used as a reference on an input as, for example, in a supply current monitor and/or limiter.

With the LH0101 there is a temptation to remove the bias current compensation resistor normally used on the non-inverting input of a summing amplifier. Direct connection of the inputs to ground or a low-impedance voltage source is not recommended with supply voltages greater than 3V. The potential problem involves loss of one supply which can cause excessive current in the second supply. Destruction of the IC could result if the current to the inputs of the device is not limited to less than 100 mA or if there is much more than 1  $\mu F$  bypass on the supply buss.

Although difficulties can be largely avoided by installing clamp diodes across the supply lines on every PC board, a conservative design would include enough resistance in the input lead to limit current to 10 mA if the input lead is pulled to either supply by internal currents. This precaution is by no means limited to the LH0101.

# Layout Considerations

When working with circuitry capable of resolving pico-ampere level signals, leakage currents in circuitry external to the op amp can significantly degrade performance. High quality insulation is a must (KeI-F and Teflon rate high). Proper cleaning of all insulating surfaces to remove fluxes and other residues is also required. This includes the IC package as well as sockets and printed circuit boards. When operating in high humidity environments or near 0°C, some form of surface coating may be necessary to provide a moisture barrier.

The effects of board leakage can be minimized by encircling the input circuitry with a conductive guard ring operated at a potential close to that of the inputs.

Electrostatic shielding of high impedance circuitry is advisable.

Error voltages can also be generated in the external circuitry. Thermocouples formed between dissimilar metals can cause hundreds of microvolts of error in the presence of temperature gradients.

Since the LH0101 can deliver large output currents, careful attention should be paid to power supply, power supply bypassing and load currents. Incorrect grounding of signal inputs and load can cause significant errors.

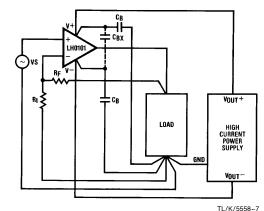

Every attempt should be made to achieve a single point ground system as shown in the figure below.

FIGURE 1. Single-Point Grounding

Bypass capacitor  $C_{BX}$  should be used if the lead lengths of bypass capacitors  $C_B$  are long. If a single point ground system is not possible, keep signal, load, and power supply from intermingling as much as possible. For further information on proper grounding techniques refer to "Grounding and Shielding Techniques in Instrumentation" by Morrison, and "Noise Reduction Techniques in Electronic Systems" by Ott (both published by John Wiley and Sons).

Leads or PC board traces to the supply pins, short-circuit current limit pins, and the output pin must be substantial enough to handle the high currents that the LH0101 is capable of producing.

## Short Circuit Current Limiting

Should current limiting of the output not be necessary, SC+ should be shorted to V+ and SC- should be shorted to V-. Remember that the short circuit current limit is dependent upon the total resistance seen between the supply and current limit pins. This total resistance includes the desired resistor plus leads, PC Board traces, and solder joints.\* Assuming a zero TCR current limit resistor, typical temperature coefficient of the short circuit current will be approximately .3%/°C.

\*Short circuit current will be limited to approximately U.B.

# Application Hints (Continued)

# **Thermal Resistance**

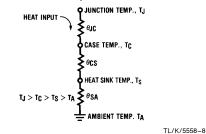

The thermal resistance between two points of a conductive system is expressed as:

$$\theta_{12} = \frac{\mathsf{T}_1 - \mathsf{T}_2}{\mathsf{P}_{\mathsf{D}}} \,^{\circ}\mathsf{C}/\mathsf{W}$$

where subscript order indicates the direction of heat flow. A simplified heat transfer circuit for a cased semiconductor and heat sink system is shown in the figure below.

The circuit is valid only if the system is in thermal equilibrium (constant heat flow) and there are, indeed, single specific temperatures T<sub>J</sub>, T<sub>C</sub> and T<sub>S</sub> (no temperature distribution in junction, case, or heat sink). Nevertheless, this is a reasonable approximation of actual performance.

### FIGURE 2. Semiconductor-Heat Sink Thermal Circuit

The junction-to-case thermal resistance  $\theta_{JC}$  specified in the data sheet depends upon the material and size of the package, die size and thickness, and quality of the die bond to the case or lead frame. The case-to-heat sink thermal resistance  $\theta_{CS}$  depends on the mounting of the device to the heat sink and upon the area and quality of the contact surface. Typical  $\theta_{CS}$  for a TO-3 package is 0.5 to 0.7°C/W, and 0.3 to 0.5°C/W using silicone grease.

The heat sink to ambient thermal resistance  $\theta_{SA}$  depends on the quality of the heat sink and the ambient conditions. Cooling is normally required to maintain the worst case operating junction temperature  $T_J$  of the device below the specified maximum value  $T_{J(MAX)}.\ T_J$  can be calculated from known operating conditions. Rewriting the above equation, we find:

$$\theta_{JA} = \frac{T_J - T_A}{P_D} \circ C/W$$

$$T_J = T_A + P_D \theta_{JA} \circ C$$

Where: P<sub>D</sub>  $(V_S - V_{OUT})I_{OUT} + |V + - (V -)|I_Q$  for a DC Signal

$\theta_{JA} = \theta_{JC} + \theta_{CS} + \theta_{SA}$  and  $V_S =$  Supply Voltage  $\theta_{JC}$  for the LH0101 is about 2°C/W.

### Stability and Compensation

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize "pickup" and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input device (usually the inverting input) to ac ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time consistant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

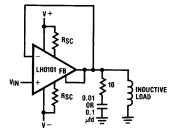

Some inductive loads may cause output stage oscillation. A .01  $\mu$ F ceramic capacitor in series with a 10 $\Omega$  resistor from the output to ground will usually remedy this situation.

TL/K/5558-9 FIGURE 3. Driving Inductive Loads

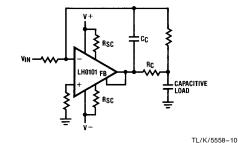

Capacitive loads may be compensated for by traditional techniques. (See "Operational Amplifiers: Theory and Practice" by Roberge, published by Wiley):

FIGURE 4. R<sub>C</sub> and C<sub>C</sub> Selected to Compensate for Capacitive Load

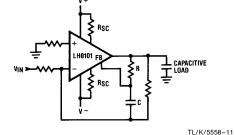

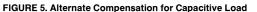

A similar but alternative technique may be used for the LH0101:

# Application Hints (Continued)

# **Output Swing Enhancement**

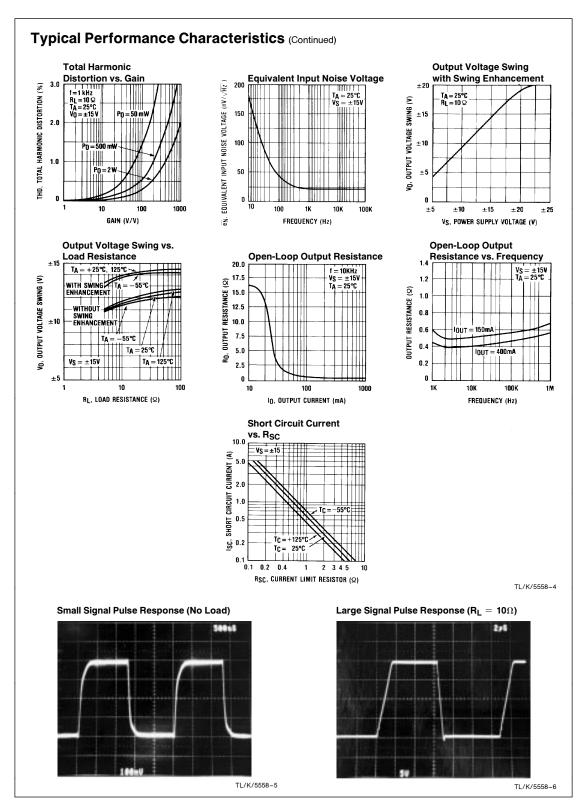

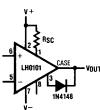

When the feedback pin is connected directly to the output, the output voltage swing is limited by the driver stage and not by output saturation. Output swing can be increased as shown by taking gain in the output stage as shown in High Power Voltage Follower with Swing Enhancement below. Whenever gain is taken in the output stage, as in swing enhancement, either the output stage, or the entire op amp must be appropriately compensated to account for the additional loop gain.

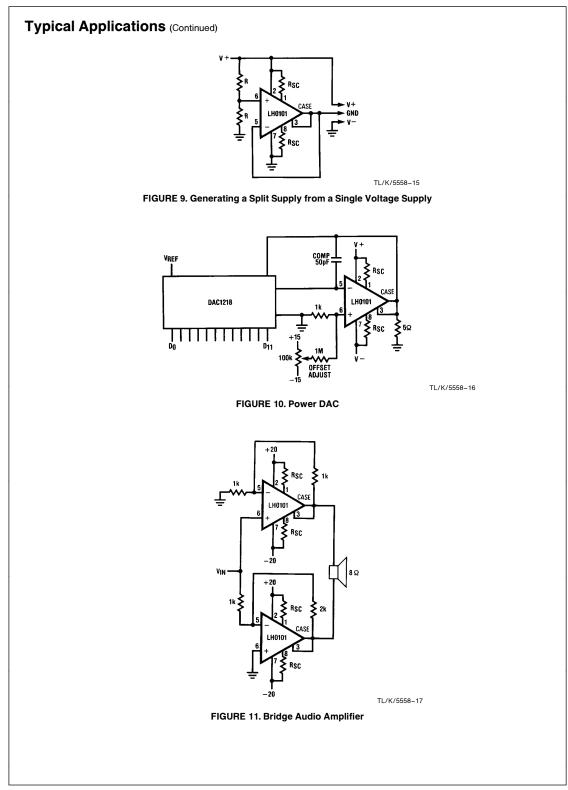

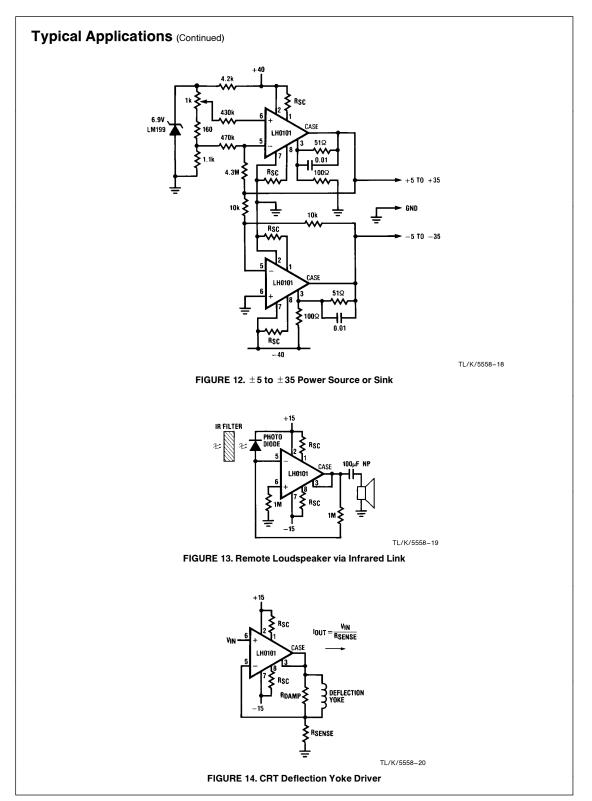

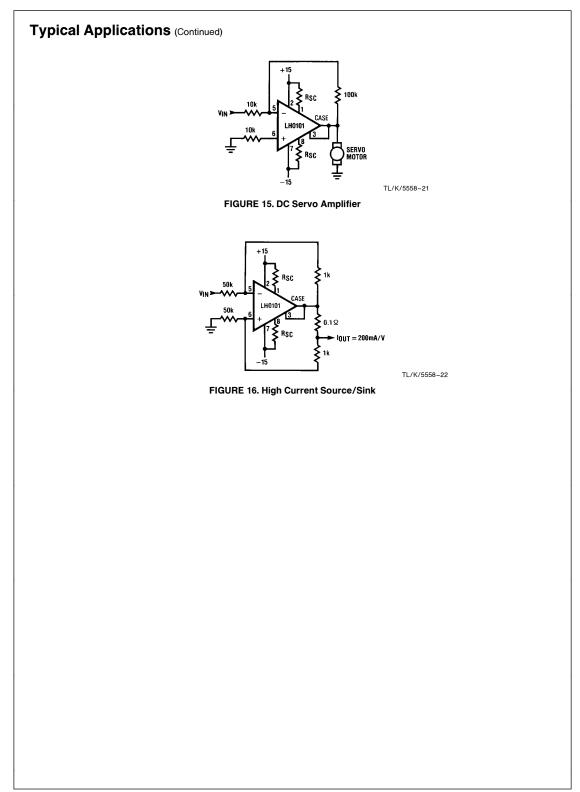

# **Typical Applications**

See AN261 for more information.

#

FIGURE 6. High Power Voltage Follower

TL/K/5558-12

### **Output Resistance**

The open loop output resistance of the LH0101 is a function of the load current. No load output resistance is approximately 10 $\Omega$ . This decreases to under 1 $\Omega$  for load currents exceeding 100 mA.

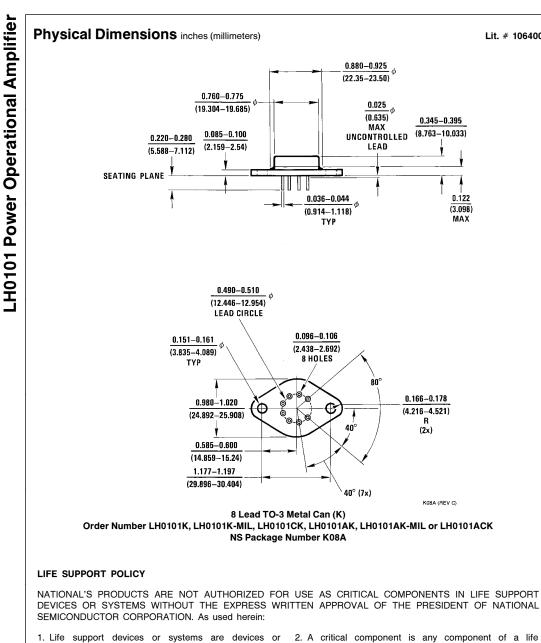

Following is a partial list of sockets and heat dissipators for use with the LH0101. National assumes no responsibility for their quality or availability. 8-Lead TO-3 Hardware

### SOCKETS

Keystone 4626 or 4627 Robinson Nugent 0002011 Azimuth 6028 (test socket)

# HEAT SINKS

Thermalloy 2266B (35°C/W) IERC LAIC3B4CB IERC HP1-TO3-33CB (7°C/W) AAVID 5791B **MICA WASHERS**

# Keystone 4658

AAVID Engineering 30 Cook Court Laconla, New Hampshire 03246 Azimuth Electronics 2377 S. El Camino Real San Clemente, CA 92572 IERC 135 W. Magnolia Blvd. Burbank, CA 91502 Keystone Electronics Corp. 49 Bleecker St. New York, NY 10012 Robinson Nugent Inc. 800 E. 8th St. New Albany, IN 47150 Thermalloy P.O. Box 34829 Dallas, TX 75234

systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Lit. # 106400

0.122

(3.098)

MAX

| National Semiconductor<br>Corporation National Semiconductor<br>Europe   1111 West Bardin Road<br>Arlington, TX 76017<br>Tel: 1(800) 737-7018 National Semiconductor<br>Europe   Fax: (+49) 0-180-530 85 86<br>Email: cniwge@itevm2.nsc.com   Fax: (1600) 737-7018 Deutsch Tel: (+49) 0-180-532 85 86<br>English Tel: (+49) 0-180-532 78 32<br>Français Tel: (+49) 0-180-532 416 80 | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tel: (852) 2737-1600<br>Fax: (852) 2737-1600 | National Semiconductor<br>Japan Ltd.<br>Tel: 81-043-299-2309<br>Fax: 81-043-299-2408 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.