# LM101A/LH2101A General Purpose Operational Amplifier

# Features

- Input offset voltage 0.7 mV

- Input bias current 30 nA

- Input offset current 1.5 nA

- Full frequency compensation 30pF

- Supply voltage  $\pm 5.0$ V to  $\pm 20$ V

# Description

The LM101A/LH2101A is a general purpose high performance operational amplifier fabricated monolithically on a silicon chip by an advanced epitaxial process. The LH2101A consists of two LM101A ICs in one 16-lead DIP. The units may be fully compensated with the addition of a 30 pF capacitor stabilizing the circuit for all feedback configurations including capacitive loads.

The device may be operated as a comparator with a differential input as high as 30V. Used as a comparator the output can be clamped at any desired level to make it compatible with logic circuits.

The LM101A and LH2101A operate over the full military temperature range from -55°C to +125°C.

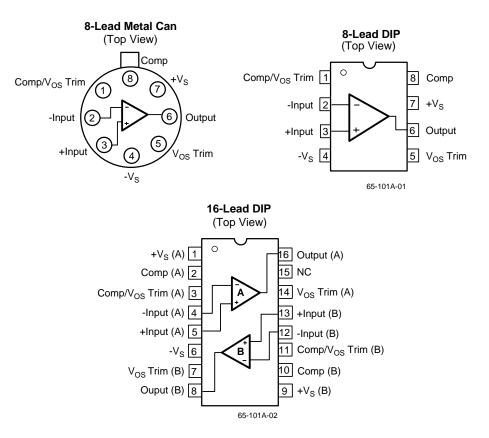

# **Pin Assignments**

# **Absolute Maximum Ratings**

| Parameter                                  | Min. | Max.       | Units |  |

|--------------------------------------------|------|------------|-------|--|

| Supply Voltage                             |      | ±22        | V     |  |

| Differential Input Voltage                 |      | 30         | V     |  |

| Input Voltage <sup>1</sup>                 |      | ±15        | V     |  |

| Output Short-Circuit Duration <sup>2</sup> |      | Indefinite |       |  |

| Storage Temperature Range                  | -65  | +150       | °C    |  |

| Operating Temperature Range                | -55  | +125       | °C    |  |

| Lead Soldering Temperature (60 sec)        |      | +300       | °C    |  |

Notes:

1. For supply voltages less than ±15V, the absolute maximum input voltage is equal to the supply voltage.

2. Observe package thermal characteristics.

# **Thermal Characteristics**

| Parameter                                   | 8-Lead<br>Ceramic<br>DIP | 8-Lead<br>TO-99<br>Metal Can | 16-Lead<br>Ceramic<br>DIP |

|---------------------------------------------|--------------------------|------------------------------|---------------------------|

| Maximum Junction Temperature                | +175°C                   | +175°C                       | +175°C                    |

| Maximum P <sub>D</sub> T <sub>A</sub> <50°C | 833 mW                   | 658 mW                       | 1042 mW                   |

| Thermal Resistance, $\theta_{JC}$           | 45°C/W                   | 50°C/W                       | 60°C/W                    |

| Thermal Resistance, θJA                     | 150°C/W                  | 190°C/W                      | 120°C/W                   |

| For T <sub>A</sub> > 50°C Derate at         | 8.33 mW/°C               | 5.26 mW/°C                   | 8.33 mW/°C                |

# **Electrical Characteristics**

C = 30pF;  $\pm 5.0V \le V_S \le \pm 20V$ ;  $-55^{\circ}C \le T_A \le \pm 125^{\circ}C$  unless otherwise specified

|                                    |                                                                                  | LM1  | 101A/LH2101 A |      |       |

|------------------------------------|----------------------------------------------------------------------------------|------|---------------|------|-------|

| Parameters                         | Test Conditions                                                                  | Min. | Тур.          | Max. | Units |

| Input Offset Voltage               | T <sub>A</sub> = +25°C, R <sub>S</sub> ≤ 50 kΩ                                   |      | 0.7           | 2.0  | mV    |

| Input Offset Current               | TA = +25°C                                                                       |      | 1.5           | 10   | nA    |

| Input Bias Current                 | $T_A = +25^{\circ}C$                                                             |      | 30            | 75   | nA    |

| Input Resistance                   | T <sub>A</sub> = +25°C                                                           | 1.5  | 4.0           |      | MΩ    |

| Supply Current                     | TA = +25°C VS = ±20V                                                             |      | 1.8           | 3.0  | mA    |

| Large Signal Voltage Gain          | $T_{A} = +25^{\circ}C, V_{S} = \pm 15V$ $V_{OUT} = \pm 10V, R_{L} \ge 2 K\Omega$ | 50   | 160           |      | V/mV  |

| Input Offset Voltage               | Rs ≤ 50 KΩ                                                                       |      |               | 3.0  | mV    |

| Average Input Offset Voltage Drift | Rs ≤ 50 KΩ                                                                       |      | 3.0           | 15   | μV/°C |

| Input Offset Current               |                                                                                  |      |               | 20   | nA    |

| Average Input Offset Current Drift | +25°C ≤ T <sub>A</sub> +125°C                                                    |      | 0.01          | 0.1  | nA/°C |

|                                    | -55°C ≤ TA +25°C                                                                 |      | 0.02          | 0.2  | 1     |

| Input Bias Current                 |                                                                                  |      |               | 100  | nA    |

| Supply Current                     | TA = +125°C, VS = ±20V                                                           |      | 1.2           | 2.5  | mA    |

| Large Signal Voltage Gain          | $V_S = \pm 15V$<br>$V_{OUT} = \pm 10V, R_L \ge 2 K\Omega$                        | 25   |               |      | V/mV  |

| Output Voltage Swing               | $V_S = \pm 15V$ , $R_L = 10 \text{ K}\Omega$                                     | ±12  | ±14           |      | V     |

|                                    | RL = 2 KΩ                                                                        | ±10  | ±13           |      | 1     |

| Input Voltage Range                | $V_{S} = \pm 20V$                                                                | ±15  |               |      | V     |

| Common Mode Rejection Ratio        | Rs ≤ 50 KΩ                                                                       | 80   | 96            |      | dB    |

| Power Supply Rejection Ratio       | Rs ≤ 50 KΩ                                                                       | 80   | 96            |      | dB    |

# **Typical Performance Characteristics**

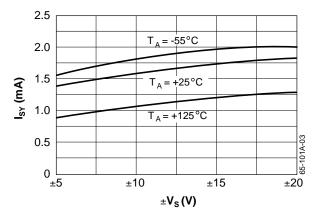

Figure 1. Supply Current vs. Supply Voltage

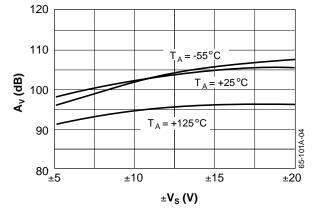

Figure 2. Voltage Gain vs. Supply Voltage

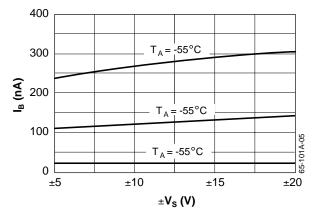

Figure 3. Input Bias Current vs. Supply Voltage

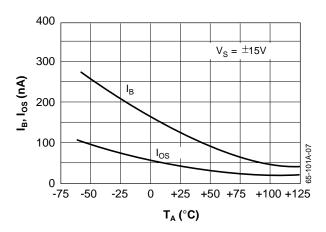

Figure 5. Input Bias, Offset Current vs. Temperature

Figure 4. Current Limiting Output Voltage vs. Output Current

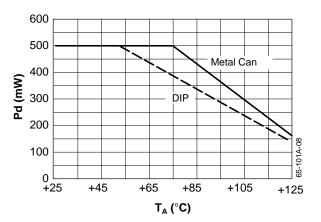

Figure 6. Maximum Power Dissipation vs. Temperature

# Typical Performance Characteristics (continued)

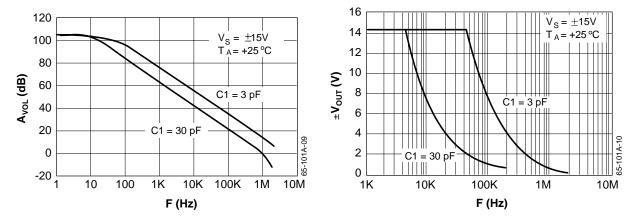

Figure 7. Open Loop Gain vs. Frequency

Figure 8. Output Voltage Swing vs. Frequency

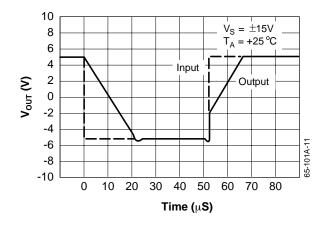

Figure 9. Follower Large Signal Pulse Response Output Voltage vs. Time

# **Typical Applications**

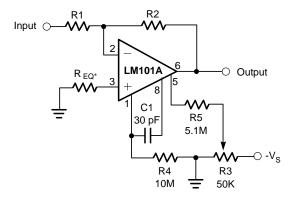

\*May be zero or equal to parallel combination of R1 and R2 for minimum offset. 65-101A-12

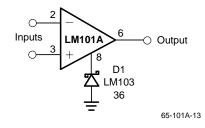

Figure 11. Voltage Comparator for Driving DTL or TTL ICs

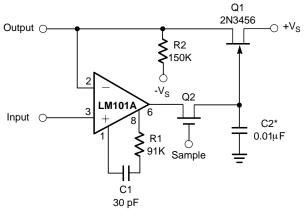

\*Polycarbonate dielectric capacitor

Figure 12. Low Drift Sample and Hold

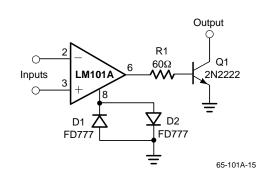

65-101A-14

Figure 13. Voltage Comparator for Driving RTL Logic or High Current Driver

### **Mechanical Dimensions**

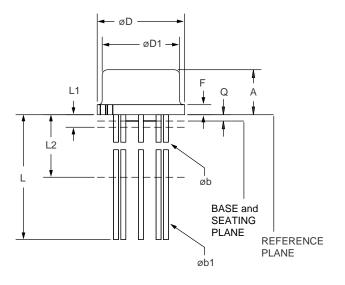

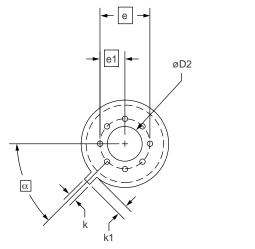

### 8-Lead TO-99 Metal Can

| Symbol | Inches   |         | Millimeters |       | Notes |

|--------|----------|---------|-------------|-------|-------|

| Symbol | Min.     | Max.    | Min.        | Max.  | Notes |

| А      | .165     | .185    | 4.19        | 4.70  |       |

| øb     | .016     | .019    | .41         | .48   | 1, 5  |

| øb1    | .016     | .021    | .41         | .53   | 1, 5  |

| øD     | .335     | .375    | 8.51        | 9.52  |       |

| øD1    | .305     | .335    | 7.75        | 8.51  |       |

| øD2    | .110     | .160    | 2.79        | 4.06  |       |

| е      | .200 BSC |         | 5.08 BSC    |       |       |

| e1     | .100     | BSC     | 2.54        | BSC   |       |

| F      | -        | .040    | —           | 1.02  |       |

| k      | .027     | .034    | .69         | .86   |       |

| k1     | .027     | .045    | .69         | 1.14  | 2     |

| L      | .500     | .750    | 12.70       | 19.05 | 1     |

| L1     | _        | .050    | _           | 1.27  | 1     |

| L2     | .250     | —       | 6.35        | —     | 1     |

| Q      | .010     | .045    | .25         | 1.14  |       |

| α      | 45°      | 45° BSC |             | BSC   |       |

- 1. (All leads) øb applies between L1 & L2. øb1 applies between L2 & .500 (12.70mm) from the reference plane. Diameter is uncontrolled in L1 & beyond .500 (12.70mm) from the reference plane.

- 2. Measured from the maximum diameter of the product.

- 3. Leads having a maximum diameter .019 (.48mm) measured in gauging plane, .054 (1.37mm) +.001 (.03mm) -.000 (.00mm) below the reference plane of the product shall be within .007 (.18mm) of their true position relative to a maximum width tab.

- 4. The product may be measured by direct methods or by gauge.

- 5. All leads increase maximum limit by .003 (.08mm) when lead finish is applied.

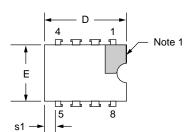

# Mechanical Dimensions (continued)

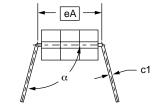

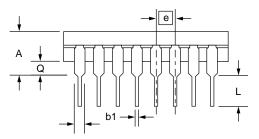

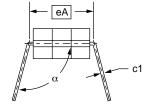

#### 8-Lead Ceramic DIP

| Symbol | Inc      | hes  | Millimeters |       | Notes |

|--------|----------|------|-------------|-------|-------|

| Symbol | Min.     | Max. | Min.        | Max.  | Notes |

| А      | _        | .200 | _           | 5.08  |       |

| b1     | .014     | .023 | .36         | .58   | 8     |

| b2     | .045     | .065 | 1.14        | 1.65  | 2, 8  |

| c1     | .008     | .015 | .20         | .38   | 8     |

| D      | _        | .405 | _           | 10.29 | 4     |

| Е      | .220     | .310 | 5.59        | 7.87  | 4     |

| е      | .100 BSC |      | 2.54        | BSC   | 5, 9  |

| eA     | .300     | BSC  | 7.62 BSC    |       | 7     |

| L      | .125     | .200 | 3.18        | 5.08  |       |

| Q      | .015     | .060 | .38         | 1.52  | 3     |

| s1     | .005     | _    | .13         | _     | 6     |

| α      | 90°      | 105° | 90°         | 105°  |       |

- 1. Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023 (.58mm) for leads number 1, 4, 5 and 8 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within ±.010 (.25mm) of its exact longitudinal position relative to pins 1 and 8.

- 6. Applies to all four corners (leads number 1, 4, 5, and 8).

- 7. "eA" shall be measured at the center of the lead bends or at the centerline of the leads when " $\alpha$ " is 90°.

- 8. All leads Increase maximum limit by .003 (.08mm) measured at the center of the flat, when lead finish applied.

- 9. Six spaces.

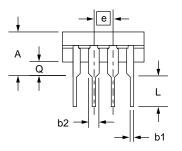

# Mechanical Dimensions (continued)

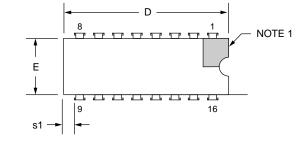

### **16-Lead Ceramic DIP**

| Symbol | Inches |      | Millimeters |       | Notes |

|--------|--------|------|-------------|-------|-------|

| Symbol | Min.   | Max. | Min.        | Max.  | Notes |

| А      |        | .200 | _           | 5.08  |       |

| b1     | .014   | .023 | .36         | .58   | 8     |

| b2     | .050   | .065 | 1.27        | 1.65  | 2     |

| c1     | .008   | .015 | .20         | .38   | 8     |

| D      | .745   | .840 | 18.92       | 21.33 | 4     |

| E      | .220   | .310 | 5.59        | 7.87  | 4     |

| е      | .100   | BSC  | 2.54 BSC    |       | 5, 9  |

| eA     | .300   | BSC  | 7.62 BSC    |       | 7     |

| L      | .115   | .160 | 2.92        | 4.06  |       |

| Q      | .015   | .060 | .38         | 1.52  | 3     |

| s1     | .005   | —    | .13         | _     | 6     |

| α      | 90°    | 105° | 90°         | 105°  |       |

- 1. Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023 (.58mm) for leads number 1, 8, 9 and 16 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within ±.010 (.25mm) of its exact longitudinal position relative to pins 1 and 16.

- 6. Applies to all four corners (leads number 1, 8, 9, and 16).

- 7. "eA" shall be measured at the center of the lead bends or at the centerline of the leads when " $\alpha$ " is 90°.

- 8. All leads Increase maximum limit by .003 (.08mm) measured at the center of the flat, when lead finish applied.

- 9. Fourteen spaces.

# **Ordering Information**

|               |                     | Operating<br>Temperature |

|---------------|---------------------|--------------------------|

| Part Number   | Package             | Range                    |

| LM101AD       | 8-Lead Ceramic DIP  | -55°C to +125°C          |

| LM101AD/883B  | 8-Lead Ceramic DIP  | -55°C to +125°C          |

| LM101AT       | 8-Lead Metal Can    | -55°C to +125°C          |

| LM101AT/883B  | 8-Lead Metal Can    | -55°C to +125°C          |

| LH2101AD      | 16-Lead Ceramic DIP | -55°C to +1 25°C         |

| LH2101AD/883B | 16-Lead Ceramic DIP | -55°C to +125°C          |

Notes:

1. /883B suffix denotes Mil-Std-883. Level B processing.

2. Contact a Fairchild Semiconductor sales office or representative for ordering information on special package/ temperature range combinations.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com