# LH77790B Embedded Microcontroller User's Guide

SHARP reserves the right to make changes in specifications described herein at any time and without notice in order to improve design or reliability. SHARP does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied. SHARP assumes no responsibility for damage caused by misuse or improper use of devices.

#### LIFE SUPPORT POLICY

SHARP components should not be used in medical devices with life support functions, safety equipment (or similar applications where component failure would result in loss of life or physical harm), aerospace equipment, telecommunication equipment (trunk lines) or nuclear power control equipment. Contact a SHARP representative or sales office before using SHARP devices for any applications other than those recommended by SHARP.

#### LIMITED WARRANTY

Sharp warrants to its Customer that the Products will be free from defects in material and workmanship under normal use and service for a period of one year from the date of invoice. Customer's exclusive remedy for breach of this warranty is that Sharp will either (i) repair or replace, at its option, any Product which fails during the warranty period because of such defect (if Customer promptly reported the failure to Sharp in writing) or, (ii) if Sharp is unable to repair or replace, refund the purchase price of the Product upon its return to Sharp. This warranty does not apply to any Product which has been subjected to misuse, abnormal service or handling, or which has been altered or modified in design or construction, or which has been serviced or repaired by anyone other than Sharp. The warranties set forth herein are in lieu of, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will Sharp be liable, or in any way responsible, for any incidental or consequential economic or property damage.

The above warranty is also extended to Customers of Sharp authorized distributors with the following exception: reports of failures of Products during the warranty period and return of Products that were purchased from an authorized distributor must be made through the distributor. In case Sharp is unable to repair or replace such Products, refunds will be issued to the distributor in the amount of distributor cost.

Trademark Advanced RISC Machines, United Kingdom.

LH77790B Embedded Microcontroller Preliminary User's Guide Version 1.0 © 1999 Copyright SHARP Microelectronics of the Americas. Printed and Bound in USA. Reference No. SMA99099

# **Table of Contents**

| Chapter 1 Overview                      |                 |

|-----------------------------------------|-----------------|

| Introduction                            | 1- <sup>-</sup> |

| Features                                |                 |

| Development Environment                 | 1-              |

| Block Diagram                           | 1-4             |

| Convention                              | 1-4             |

| Accessing Registers                     | 1-4             |

| Chapter 2 Pin Descriptions              |                 |

| Chapter 3 ARM7DI Core                   |                 |

| Introduction                            | 3-              |

| Features                                | 3-              |

| Block Diagram                           | 3-2             |

| Chapter 4 On-chip Memory                |                 |

| Introduction                            | 4-              |

| Cache                                   |                 |

| Features                                |                 |

| Register Map                            |                 |

| General Operation                       |                 |

| Register Description                    |                 |

| Cache Mode                              |                 |

| SRAM Mode                               |                 |

| Flush Mode                              | 4-              |

| Invalidate Mode                         |                 |

| Local SRAM                              |                 |

| Features                                |                 |

| Register Map                            |                 |

| General Operation                       |                 |

| Register Description                    |                 |

| Chapter 5 Memory & Peripheral Interface |                 |

| Introduction                            | 5- <sup>-</sup> |

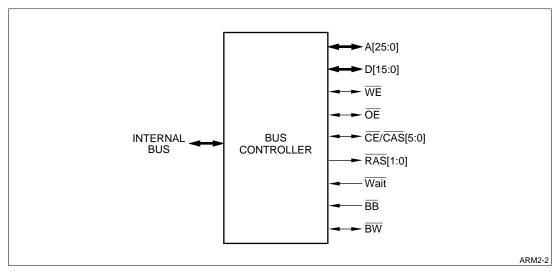

| Features                                |                 |

| Block Diagram                           |                 |

| Register Map                            |                 |

| Upon Reset                              |                 |

| General Operation                       |                 |

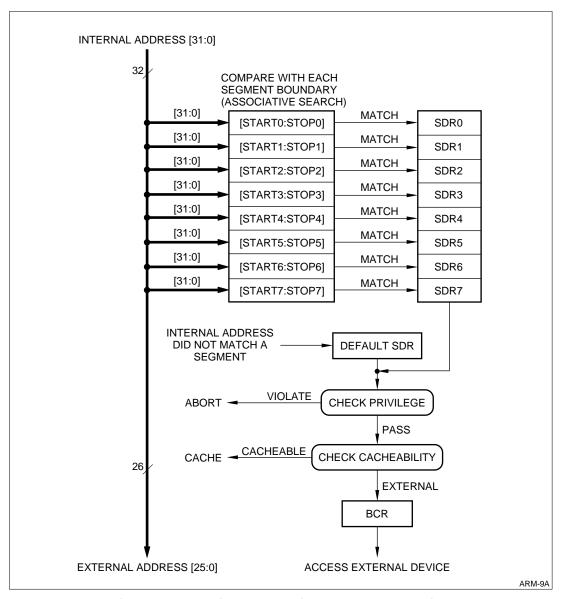

| Memory Management                       |                 |

| Logical to Physical Mapping             |                 |

| Memory Segments                         |                 |

| Memory Banks                            |                 |

| Register Description                     | 5-8  |

|------------------------------------------|------|

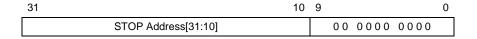

| START and STOP Registers (STARTn, STOPn) | 5-8  |

| Example                                  | 5-8  |

| Segment Descriptor Registers (SDRn)      | 5-9  |

| System/User Privileges                   | 5-10 |

| Cacheability                             | 5-10 |

| Half-Word Mode (HW)                      | 5-10 |

| Bank Selection                           | 5-11 |

| Reset Value                              | 5-11 |

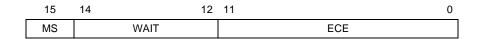

| Bank Control Registers (BCRn)            | 5-11 |

| BCR0 - BCR5                              |      |

| MS                                       |      |

| WAIT                                     | 5-12 |

| ECE                                      |      |

| BCR6a and BCR7a                          |      |

| MS                                       |      |

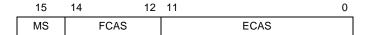

| FCAS                                     |      |

| ECAS                                     |      |

| BCR6b and BCR7b                          |      |

| DRAM Refresh Register (DRR)              |      |

| Example 1                                |      |

| Example 2                                |      |

| DRAM Controller                          |      |

| DRAM Access Mode                         |      |

| DRAM Page Size                           |      |

| DRAM Address Bus Multiplex               |      |

| Memory Cycles Calculation                |      |

| Definition                               |      |

| On-chip (Local) SRAM                     |      |

| External Memory Devices                  |      |

| Non-DRAM (SRAM, ROM, EPROM, Flash)       |      |

| DRAM Normal Mode                         |      |

| Page Mode                                |      |

| <u> </u>                                 |      |

| Memory Cycle Diagrams                    | 5-23 |

| Chapter 6 Clock & Power Management       |      |

| Introduction                             | 6-1  |

| Features                                 | 6-1  |

| Block Diagram                            | 6-2  |

| Register Map                             | 6-2  |

| Power Modes                              | 6-3  |

| Active Mode                              | 6-3  |

| Standby Mode                             | 6-3  |

| Sleep Mode                               | 6-4  |

| Stop Mode                                | 6-4  |

| XCLKDIS Output                           | 6-4  |

| CPMU Registers                                 | 6-5  |

|------------------------------------------------|------|

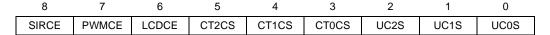

| Peripheral Clock Select Register (PCSR)        | 6-5  |

| UARTO Clock Control Register (U0CCR)           | 6-6  |

| UART1 Clock Control Register (U1CCR)           | 6-7  |

| UART2 Clock Control Register (U2CCR)           | 6-8  |

| Counter/Timer0 Clock Control Register (CT0CCR) | 6-9  |

| Counter/Timer1 Clock Control Register (CT1CCR) | 6-10 |

| Counter/Timer2 Clock Control Register (CT2CCR) | 6-11 |

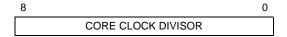

| Core Clock Control Register (CCCR)             | 6-12 |

| Chapter 7 UART                                 |      |

| Introduction                                   | 7-1  |

| Features                                       | 7-1  |

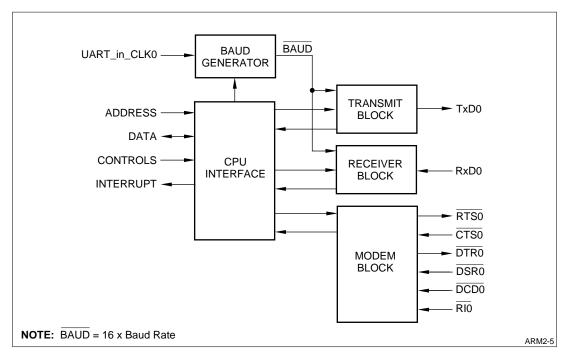

| Block Diagram                                  | 7-2  |

| Upon Reset                                     | 7-2  |

| General Operation                              | 7-2  |

| Baud Generator                                 | 7-2  |

| Transmitter                                    | 7-3  |

| Receiver                                       | 7-3  |

| Modem Controller                               | 7-3  |

| Modem Signals                                  | 7-3  |

| External Interface                             | 7-4  |

| Register Map                                   |      |

| UARTs Registers                                |      |

| Register Description                           |      |

| Receiver Buffer Register (RBR)                 |      |

| Transmit Holding Register (THR)                |      |

| Interrupt Enable Register (IER)                |      |

| Interrupt Identification Register (IIR)        |      |

| Line Control Register (LCR)                    |      |

| Modem Control Register (MCR)                   |      |

| Line Status Register (LSR)                     |      |

| Modem Status Register (MSR)                    |      |

| Scratch Pad Register (SCR)                     |      |

| Divisor Latches (DLL, DLM) - Read/Write        |      |

| UARTs Input Clock                              | 7-14 |

| Chapter 8 Serial Infrared (SIR) Interface      |      |

| Introduction                                   |      |

| Features                                       |      |

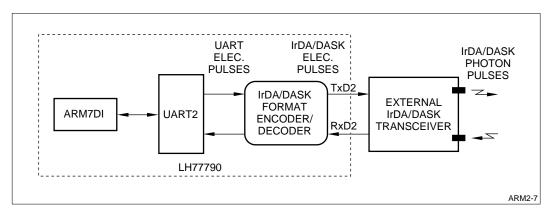

| Block Diagram                                  |      |

| External Interface                             |      |

| Register Map                                   |      |

| General Operation                              |      |

| IrDA Mode                                      |      |

| DASK Mode                                      |      |

| I I A R T Mode                                 | Q_/  |

| Register Description                             | 8-7  |

|--------------------------------------------------|------|

| SIR Control Register (SIR_CTLR)                  | 8-7  |

| IrDA Clock                                       | 8-7  |

| DASK Clocks                                      | 8-7  |

| Power Management Mode                            | 8-7  |

| Chapter 9 Pulse Width Modulator (PWM)            |      |

| Introduction                                     | 9-1  |

| PWM Definition                                   | 9-1  |

| Features                                         | 9-2  |

| PWM Applications                                 | 9-2  |

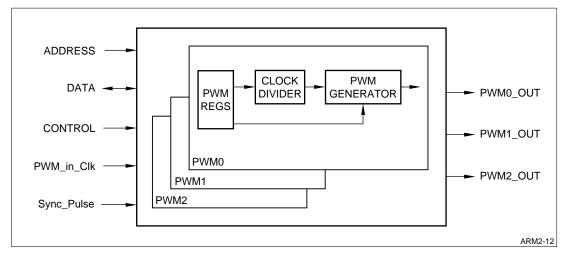

| Functional Block Diagram                         | 9-3  |

| External Interface                               | 9-3  |

| Register Map                                     | 9-4  |

| General Operation                                | 9-5  |

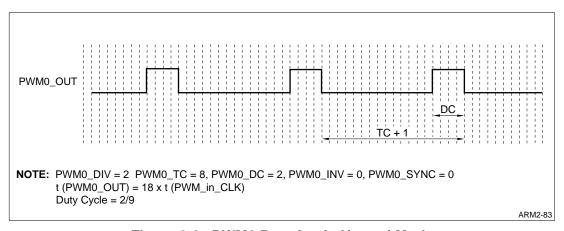

| Normal Mode                                      | 9-5  |

| Example:                                         | 9-5  |

| Synchronous Mode                                 | 9-6  |

| Example:                                         | 9-7  |

| Power Management                                 | 9-7  |

| Status During Reset                              | 9-8  |

| PWM Pulse Frequency and Duty Cycle               | 9-8  |

| Example                                          | 9-8  |

| Register Description                             |      |

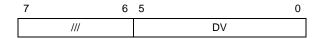

| Clock Divider Registers [PWMn_DIV (n = 0, 1, 2)] |      |

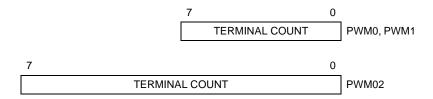

| Terminal Count Registers [PWMn_TC (n = 0, 1, 2)] |      |

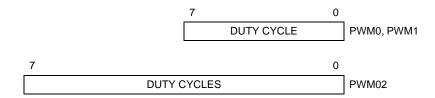

| Duty Cycle Registers [PWMn_DC (n = 0, 1, 2)]     |      |

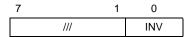

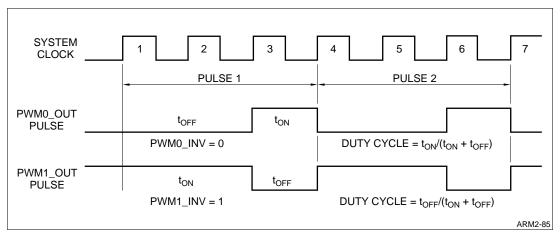

| Output Invert Registers [PWMn_INV (n = 0, 1, 2)] |      |

| Enable Registers [PWMn_ENB (n = 0, 1, 2)]        |      |

| Synchronous Registers [PWMn_SYNC (n = 0, 1, 2)]  |      |

| PWM Connection to On-Chip Counter/Timers         |      |

| PWM Programming Examples                         |      |

| (1) Static Programming (PWM is not running)      |      |

| Assumption                                       |      |

| (2) Dynamic Programming (PWM is running)         |      |

| Assumption:                                      |      |

| (3) Synchronous Mode Programming                 |      |

| Assumptions:                                     |      |

| (4) Synchronous Mode Programming                 |      |

| Assumptions:                                     |      |

| Programming Rules (n = 0, 1, 2, A)               | 9-16 |

| Chapter 10 LCD Controller                        |      |

| Introduction                                     |      |

| Features                                         |      |

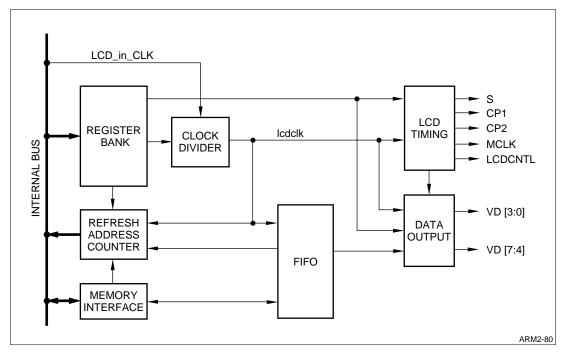

| Block Diagram                                    |      |

| External Interface                               | 10-2 |

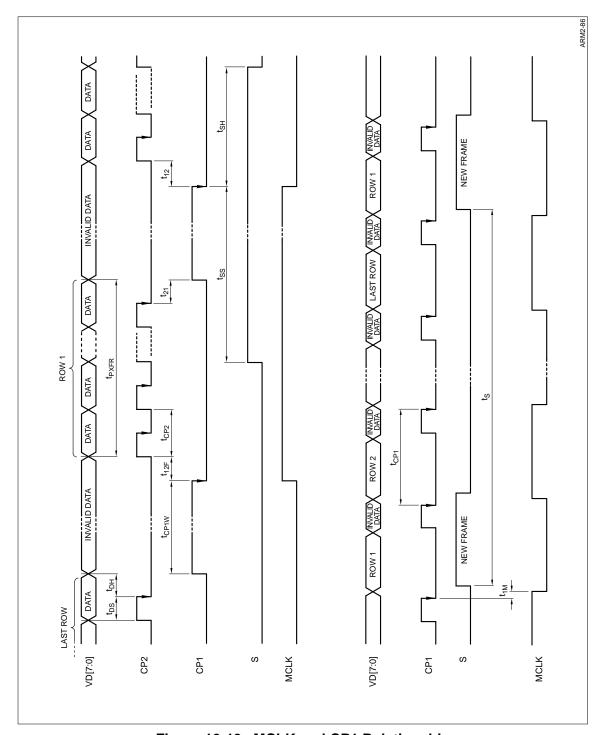

| LCD Panel Signals Description                                    | 10-3  |

|------------------------------------------------------------------|-------|

| VD[7:0]                                                          | 10-3  |

| CP2                                                              | 10-4  |

| CP1                                                              | 10-4  |

| S                                                                | 10-4  |

| MCLK                                                             | 10-4  |

| LCDCNTL                                                          | 10-5  |

| Register MAP                                                     | 10-5  |

| Description of Registers                                         | 10-6  |

| Mode Register (LCD_MODE)                                         | 10-6  |

| Bit 7 – DISP                                                     | 10-6  |

| Bit 6 – REV                                                      | 10-6  |

| Bit 5 – SCAN                                                     | 10-6  |

| Bit 4 – OR                                                       | 10-7  |

| Bit 3 – GRAY                                                     | 10-7  |

| Bit 2 - XSIZE                                                    | 10-7  |

| Bit 1 - LCDC                                                     | 10-8  |

| Bit 0 – LCDA                                                     | 10-8  |

| LCD_MODE Register Summary                                        | 10-9  |

| Line Display Byte Count Register (LCD_BC)                        | 10-10 |

| Example – 320 pixel wide display                                 | 10-11 |

| Example - 24 pixel wide display                                  | 10-11 |

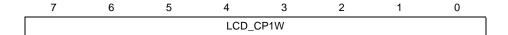

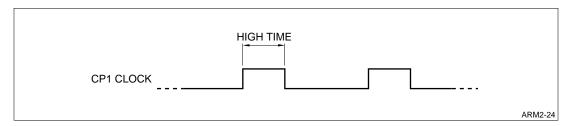

| Line Pulse Width Register (LCD_CP1W)                             | 10-12 |

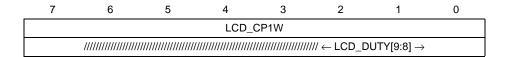

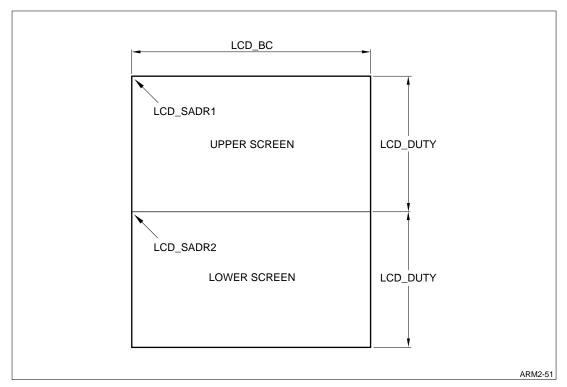

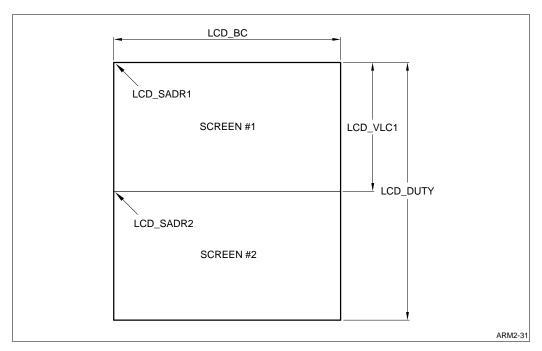

| Duty Cycle Registers (LCD_DUTY)                                  | 10-13 |

| Examples                                                         | 10-14 |

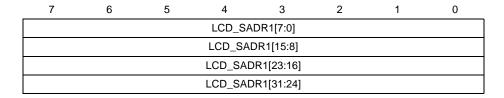

| Screen #1 Frame Buffer Start Address Registers (LCD_SADR1[31:0]) | 10-15 |

| Screen #2 Frame Buffer Start Address Registers (LCD_SADR2)       | 10-16 |

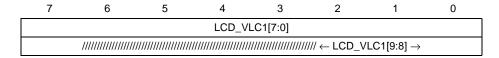

| Screen #1 Vertical Line Count Registers (LCD_VLC1)               | 10-17 |

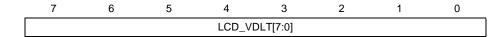

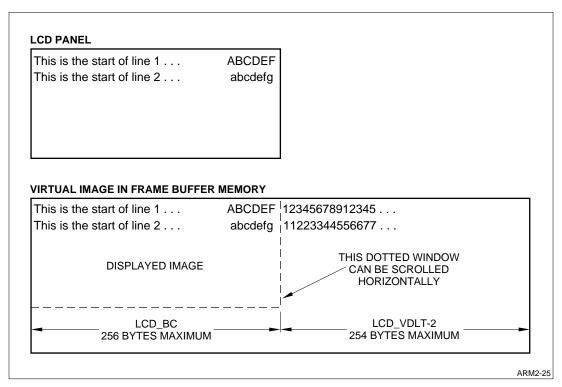

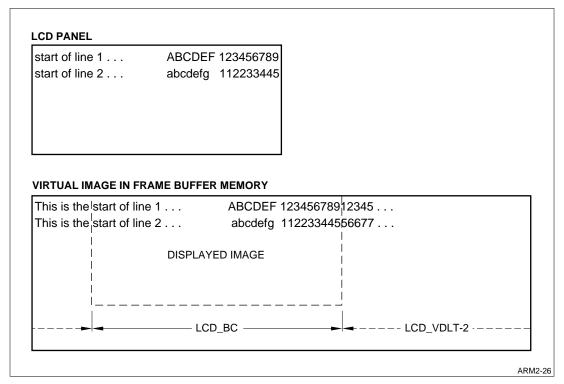

| Virtual Display Delta Register (LCD_VDLT)                        | 10-18 |

| Example 1                                                        | 10-19 |

| Example 2                                                        | 10-20 |

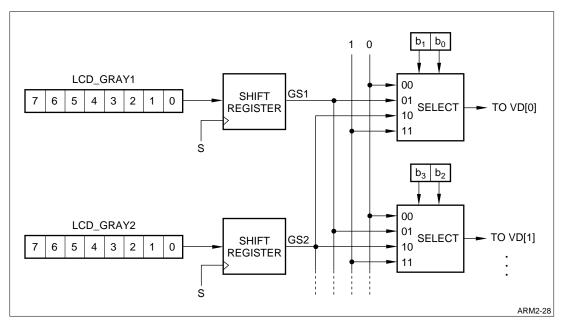

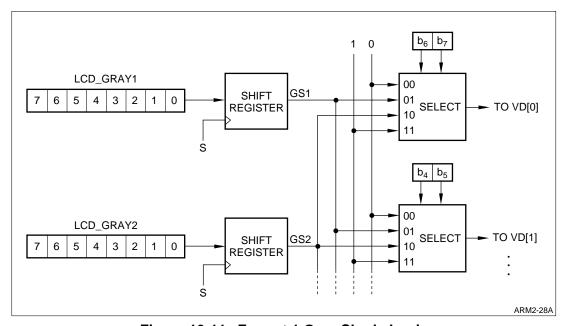

| Gray Shade Registers (LCD_GRAY1, LCD_GRAY2)                      | 10-20 |

| Example 1                                                        | 10-22 |

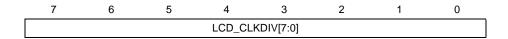

| Clock Frequency Divider (LCD_CLKDIV)                             | 10-23 |

| Example 2                                                        | 10-23 |

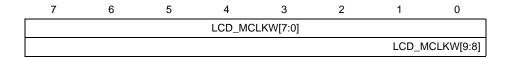

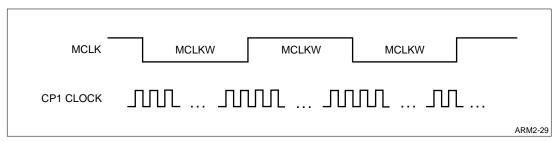

| MCLK Width (LCD_MCLKW)                                           | 10-24 |

| LCD Bit Control (LCD_BITCTL)                                     | 10-25 |

| Example                                                          | 10-25 |

| Shift Operations on the Displayed Data                           | 10-27 |

| Color Support                                                    | 10-28 |

| Basic Timing                                                     | 10-28 |

| Timing Equations                                                 | 10-29 |

| Frama Bata Calculations                                          | 10.20 |

| Programming Examples                           | 10-33 |

|------------------------------------------------|-------|

| Mode 1a                                        | 10-33 |

| LCD_MODE                                       | 10-33 |

| LCD_BC                                         | 10-33 |

| LCD_DUTY                                       | 10-33 |

| LCD_CLK                                        | 10-33 |

| LCD_CP1W                                       | 10-34 |

| Mode 1a Results                                | 10-34 |

| Mode 1b                                        | 10-35 |

| Mode 1b Results                                | 10-35 |

| Mode 2                                         | 10-36 |

| Mode 2 Results                                 | 10-36 |

| Mode 3a                                        | 10-37 |

| Mode 3a Results                                | 10-37 |

| Mode 3b                                        | 10-38 |

| Mode 3b Results                                | 10-38 |

| Mode 4                                         | 10-39 |

| Mode 4 Results                                 | 10-39 |

| Mode 5                                         | 10-40 |

| Mode 5 Results                                 | 10-40 |

| Mode 6                                         | 10-41 |

| Mode 6 Results                                 | 10-41 |

| Passive Color Panel Example                    | 10-42 |

| 01 ( 44.0 ( 57)                                |       |

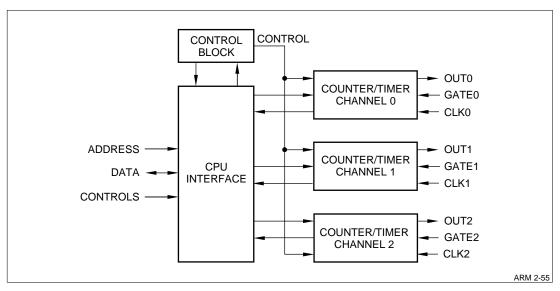

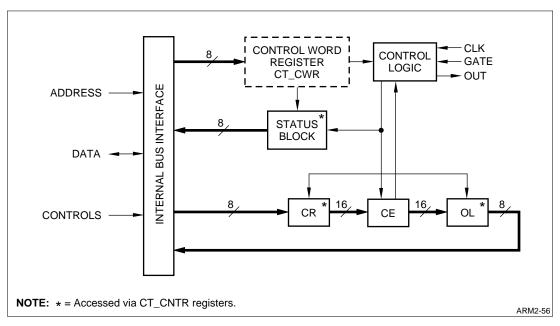

| Chapter 11 Counters/Timers                     |       |

| Introduction                                   |       |

| Features                                       |       |

| Block Diagram                                  |       |

| Internal Diagram                               |       |

| External Interface                             |       |

| Register Map                                   |       |

| General Operation                              |       |

| Register Description                           |       |

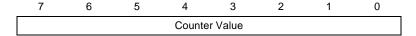

| Count Registers (CT_CNTR0, CT_CNTR1, CT_CNTR2) |       |

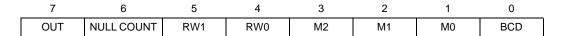

| Control Word Register (CT_CWR)                 |       |

| Write Operations                               |       |

| Read Operations                                |       |

| Simple Read Operation                          |       |

| Counter Latch Command                          | 11-5  |

| ReadBack Command                               | 11-6  |

| Counter/Timer Clocks                           | 11-8  |

| O 1   T' O - 1 -                               | 44.0  |

| Counter/Timer Modes                                         | 11-8  |

|-------------------------------------------------------------|-------|

| Counter/Timer Mode Diagrams                                 |       |

| Mode 0: Interrupt on Terminal Count                         |       |

| Mode 1: Hardware Retriggerable One-shot                     |       |

| Mode 2: Rate Generator                                      |       |

| Mode 3: Square Wave Generator                               |       |

| Mode 4: Software Triggered Strobe                           |       |

| Mode 5: Hardware Triggered Strobe                           |       |

| Mode Summary                                                |       |

| Chapter 12 Watchdog Timer                                   |       |

| Introduction                                                | 12-1  |

| Features                                                    | 12-1  |

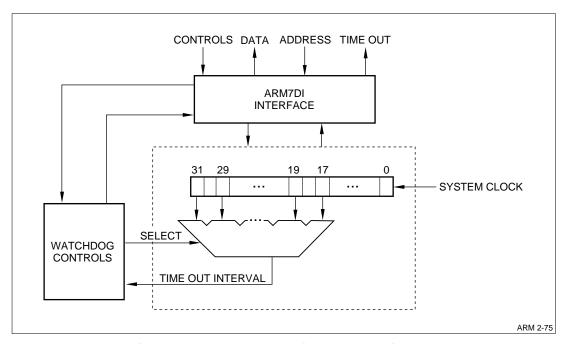

| Block Diagram                                               | 12-1  |

| Register Map                                                | 12-2  |

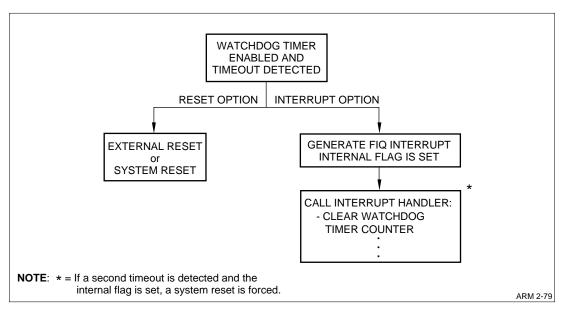

| General Operation                                           | 12-2  |

| Register Description                                        | 12-3  |

| Watchdog Control Register (WDCTLR)                          | 12-3  |

| Watchdog Counter Register (WDCNTR)                          | 12-4  |

| Protection Mechanism                                        | 12-4  |

| 01 ( 40 D                                                   |       |

| Chapter 13 Program Peripheral Interface (PPI)               | 40.4  |

| Introduction                                                |       |

| Applications                                                |       |

| Features                                                    | 13-1  |

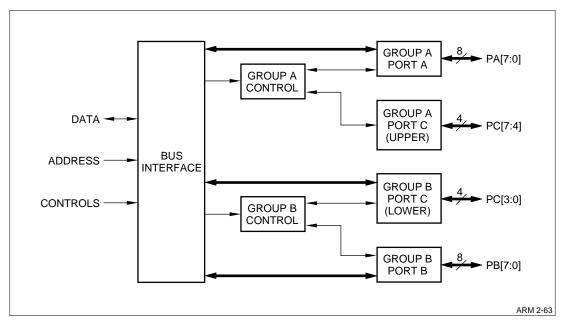

| Block Diagram                                               | 10.0  |

| External Interface                                          |       |

| Register Map                                                |       |

| Upon Reset                                                  |       |

| Ports A, B, and C                                           |       |

| Register Description                                        |       |

| PPI Control Register (PPI_CTLR)                             |       |

| Definition of Bits[6:0] in MODE Selection (Bit[7] = 1)      |       |

| Definition of Bits[6:0] in Set/Reset of Port C (Bit[7] = 0) |       |

| Interrupt Control                                           |       |

| Operating Modes                                             |       |

| MODE Selection                                              | 13-6  |

| MODE 0 – Basic                                              | 13-7  |

| MODE 1 (Strobed)                                            | 13-10 |

| MODE 1 Input Control Signal Definitions                     |       |

| (Group A and Group B)                                       | 13-11 |

| MODE 1 Output Control Signal Definition                     |       |

| (Group A and Group B)                                       | 13-13 |

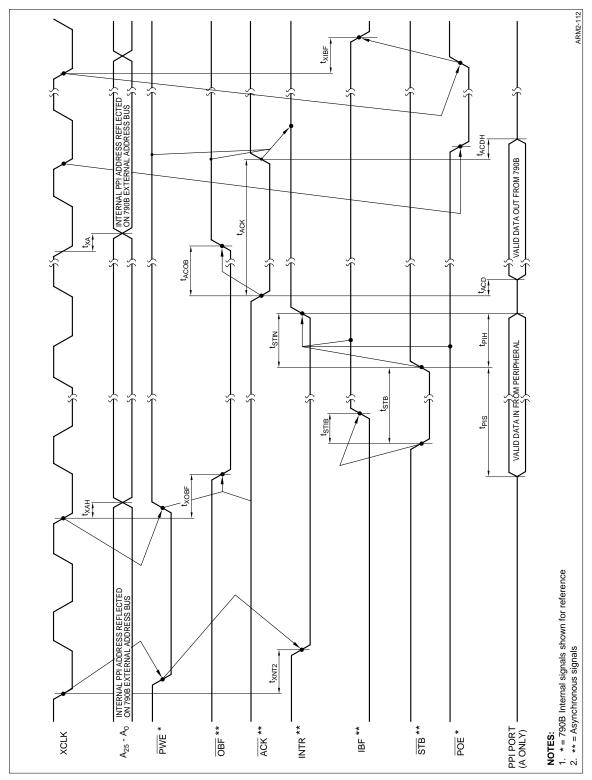

| MODE 2 – Strobed Bi-Directional (Port A Only)               | 13-15 |

| MODE 2 Bidirectional Control Signal Definition              |       |

| MODE Definition Summary                                     |       |

| Dort Miles                                                  | 10.10 |

| Reading/Writing Port C                        | 13-19 |

|-----------------------------------------------|-------|

| MODE 0                                        | 13-20 |

| Port C Function                               | 13-20 |

| Read Operation                                | 13-20 |

| Write Operation (Normal)                      |       |

| Write Operation (Set/Reset)                   |       |

| MODE 1                                        |       |

| Port C Function                               |       |

| Read Operation                                |       |

| Write Operation                               |       |

| MODE 2                                        |       |

| Port C Function                               |       |

| Read Operation                                |       |

| Write Operation                               |       |

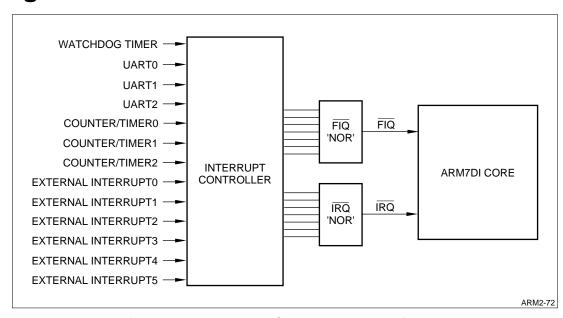

| Chapter 14 Interrupt Controller               |       |

| Introduction                                  | 1.1.1 |

| Features                                      |       |

| Block Diagram                                 |       |

| <u> </u>                                      |       |

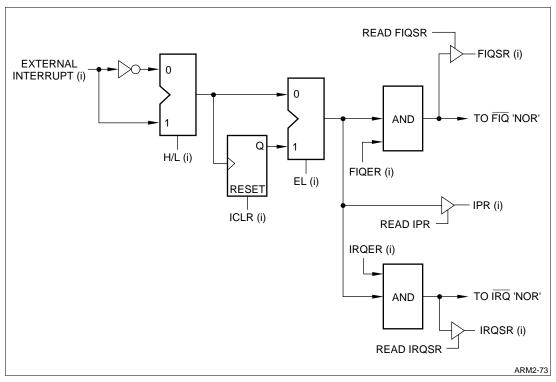

| Internal Diagram                              |       |

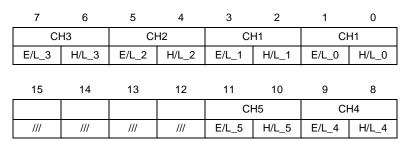

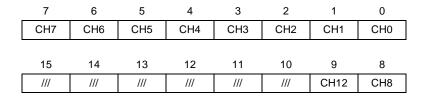

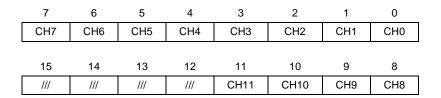

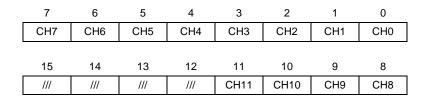

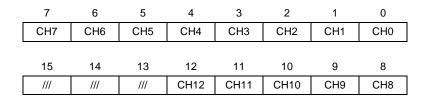

| Register Map Interrupt Channel Assignment     |       |

| •                                             |       |

| General Operation                             |       |

| Register Description                          |       |

| Interrupt Configuration Registers (ICR0/ICR1) |       |

| ICR0                                          |       |

| ICR1                                          |       |

| Interrupt Clear Register (ICLR)               |       |

| IRQ interrupt Enable Register (IRQER)         |       |

| FIQ Interrupt Enable Register (FIQER) The FIQ |       |

| IRQ Status Register (IRQSR)                   |       |

| FIQ Status Register (FIQSR)                   |       |

| Interrupt Polling Register (IPR)              |       |

| Priority                                      |       |

| Exceptions                                    | 14-9  |

| Chapter 15 I/O Configuration                  |       |

| Introduction                                  |       |

| Register Map                                  |       |

| Register Description                          |       |

| Input/Output Configuration Register (IOCR)    | 15-1  |

| Chapter 16 Reset                              |       |

| Introduction                                  |       |

| External Reset Source                         |       |

| Watchdog Timer                                |       |

| Software Controlled Reset                     |       |

| ITAG Reset                                    | 16-2  |

| Chapter 17 Identification Register |      |

|------------------------------------|------|

| Introduction                       | 17-1 |

| Register Map                       | 17-1 |

| Register Description               | 17-2 |

| Identification Register (IDR)      | 17-2 |

| Chapter 18 Debug Interface         |      |

| Introduction                       | 18-1 |

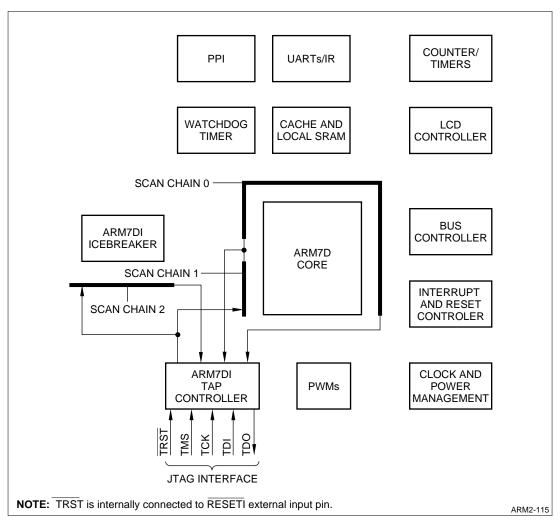

| Block Diagram                      | 18-1 |

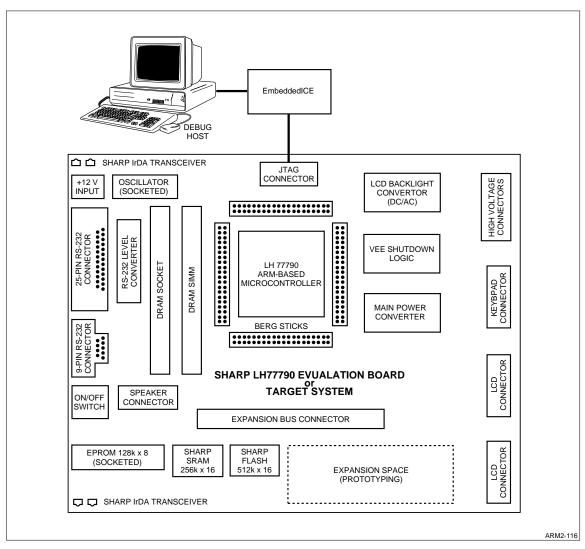

| General Operation                  | 18-2 |

| Pull-up Resistors                  | 18-3 |

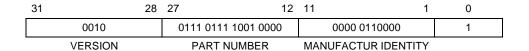

| Device Identification Code         | 18-3 |

| JTAG Reset                         | 18-3 |

| Chapter 19 Memory Map and          |      |

| Register Summary                   |      |

| Memory Map                         | 19-1 |

| System Configuration Region        | 19-3 |

| Internal Peripherals Region        |      |

| Cache Region                       |      |

| Local SRAM Region                  |      |

| Register Summary                   | 19-4 |

| Chapter 20 Package Specifications  |      |

| Ordering Information               | 20-3 |

| Chapter 21 Sharp Sales Offices     |      |

# **List of Figures**

| LH77790B Block Diagram                                    | 1-4           |

|-----------------------------------------------------------|---------------|

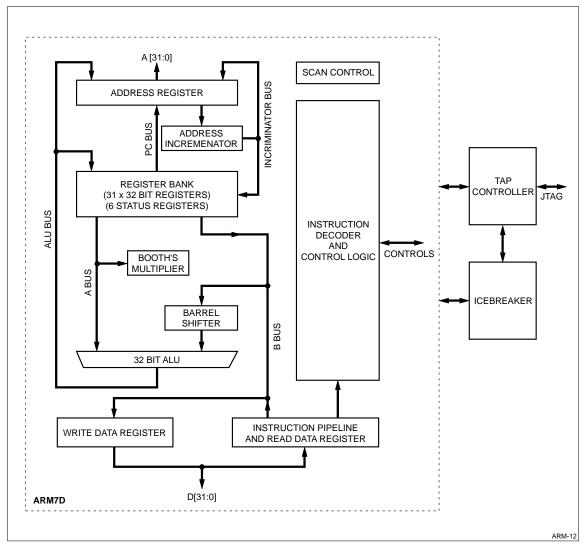

| ARM7DI Core Block Diagram                                 | 3-2           |

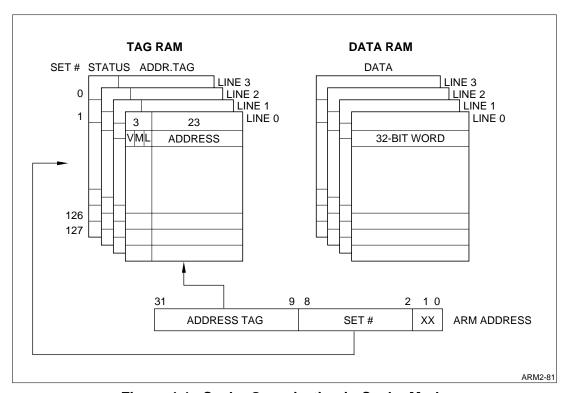

| Cache Organization in Cache Mode                          | 4-3           |

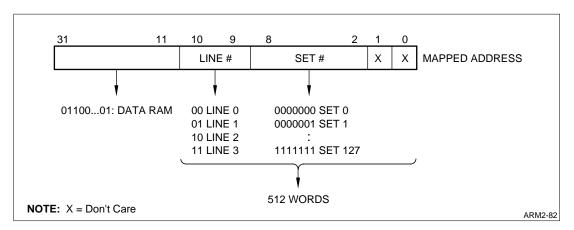

| Cache Mapping in SRAM Mode                                | 4-4           |

| Memory and Peripheral Interface Block Diagram             | 5-2           |

| Logical to Physical Address Mapping                       | 5-6           |

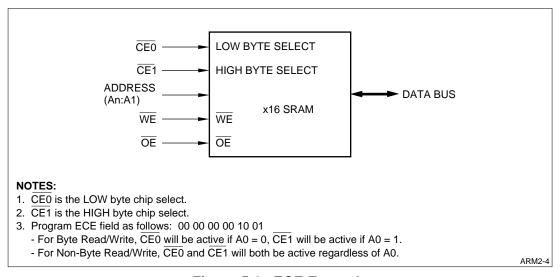

| ECE Example                                               |               |

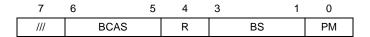

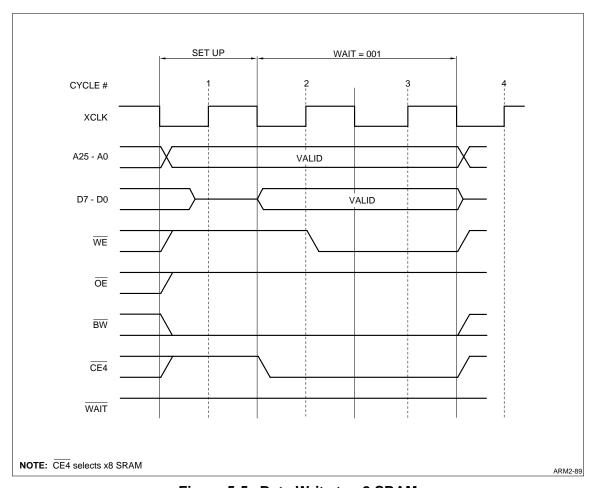

| Byte Read from x8 SRAM                                    |               |

| Byte Write to x8 SRAM                                     |               |

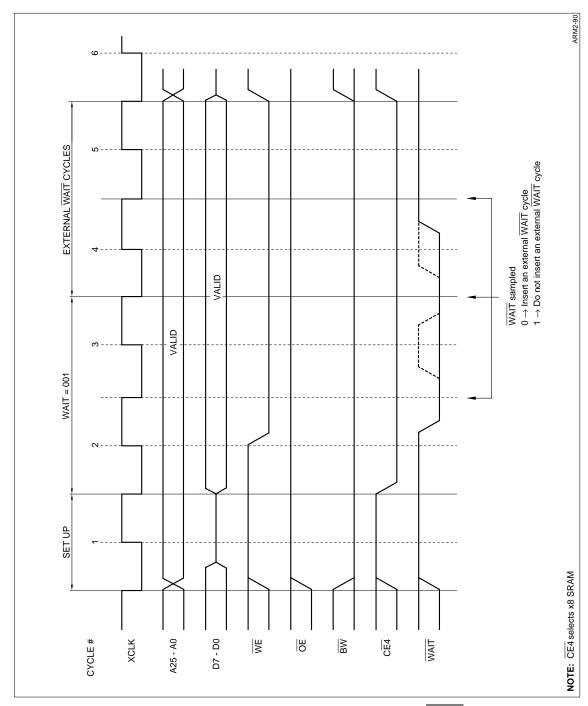

| Byte Write to x8 SRAM with External WAIT Cycles           | 5-2           |

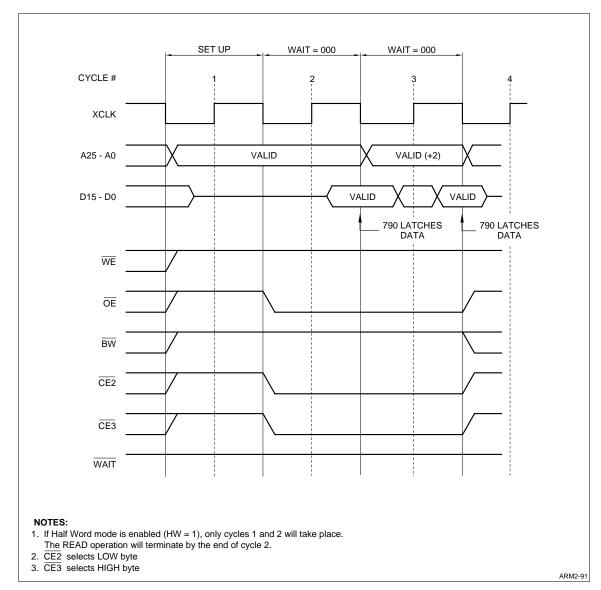

| Word Read to x16 SRAM                                     | 5-26          |

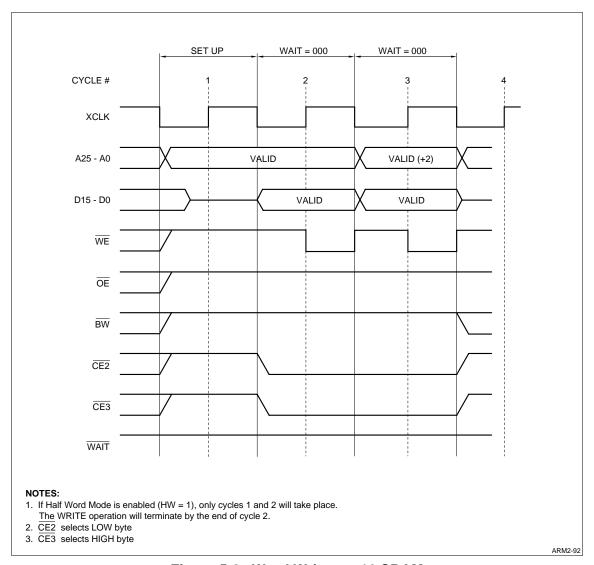

| Word Write to x16 SRAM                                    |               |

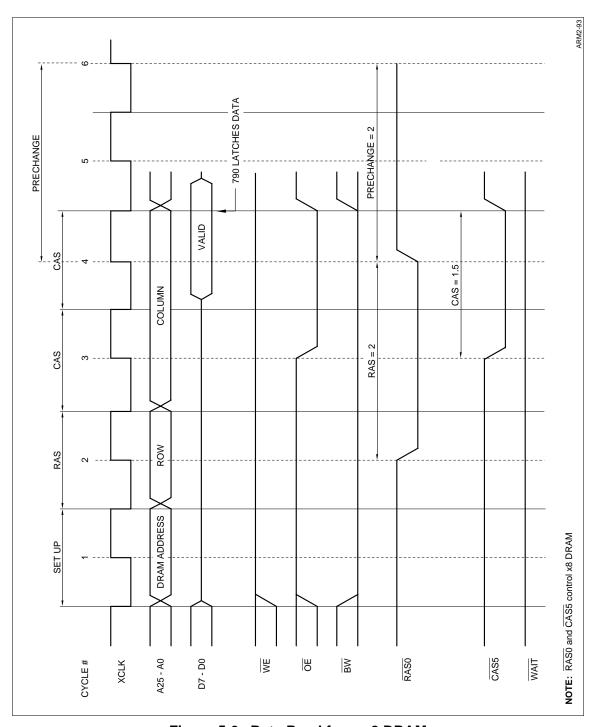

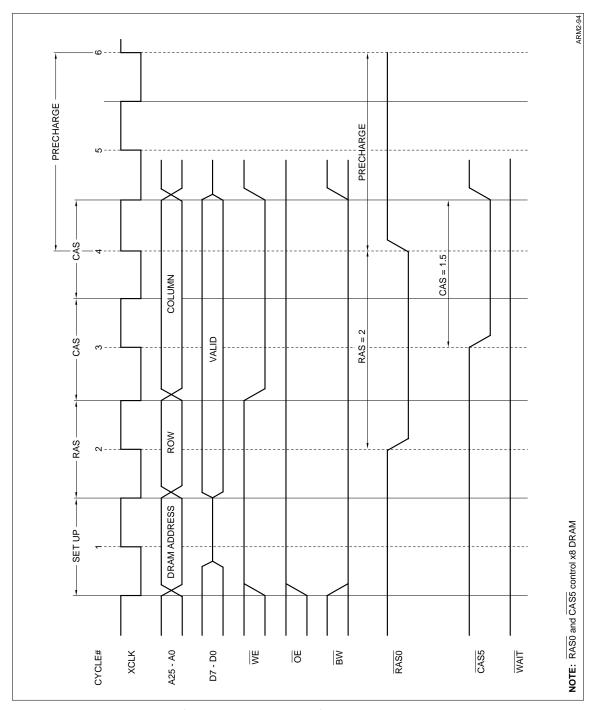

| Byte Read from x8 DRAM                                    |               |

| Byte Write to x8 DRAM                                     |               |

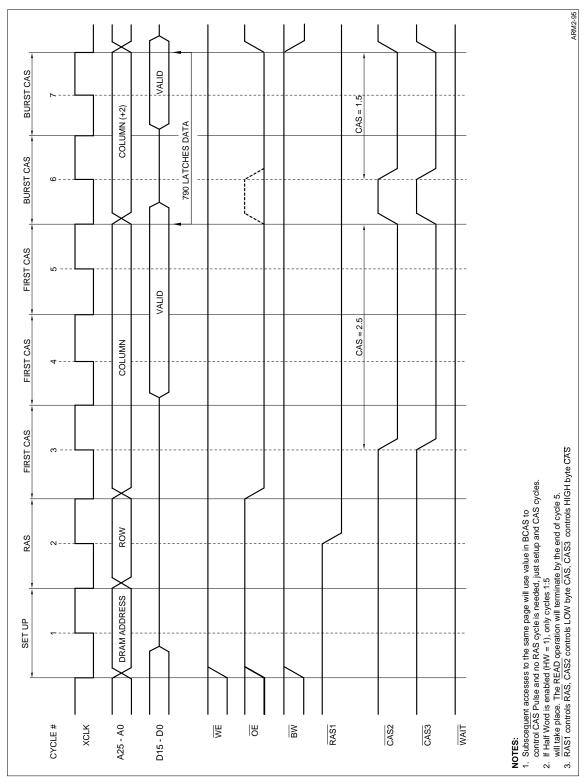

| Word Read from x16 DRAM Page Mode (FCAS = 010, BCAS = 01) |               |

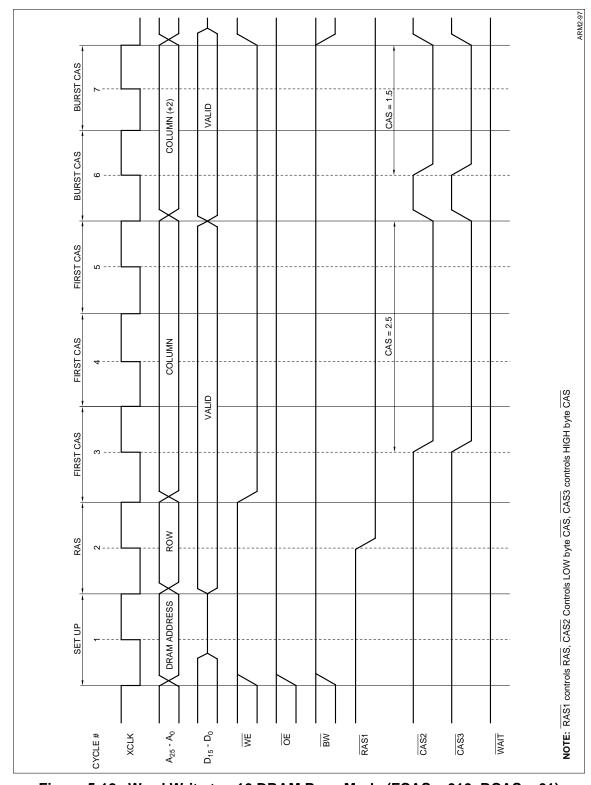

| Word Write to x16 DRAM Page Mode (FCAS = 010, BCAS = 01)  | 5-3´          |

| Word Write to x8 DRAM Page Mode (FCAS = 010, BCAS = 01)   |               |

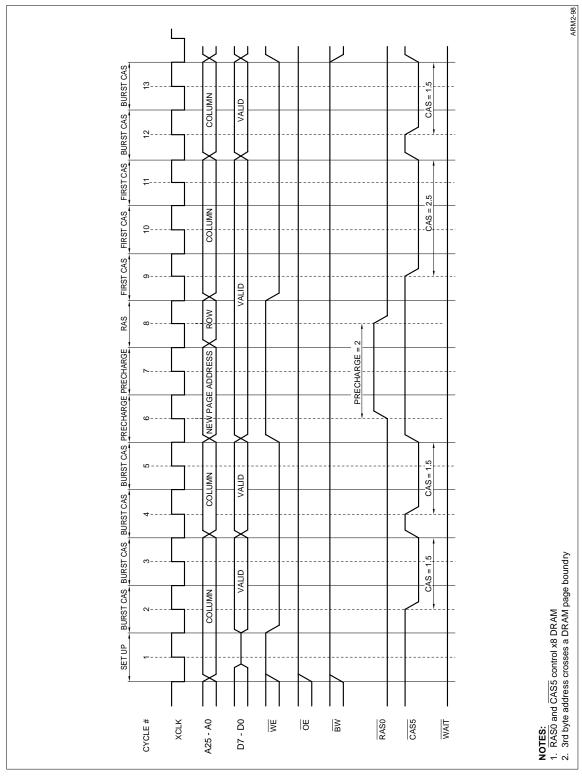

| DRAM Page Boundary Crossing                               |               |

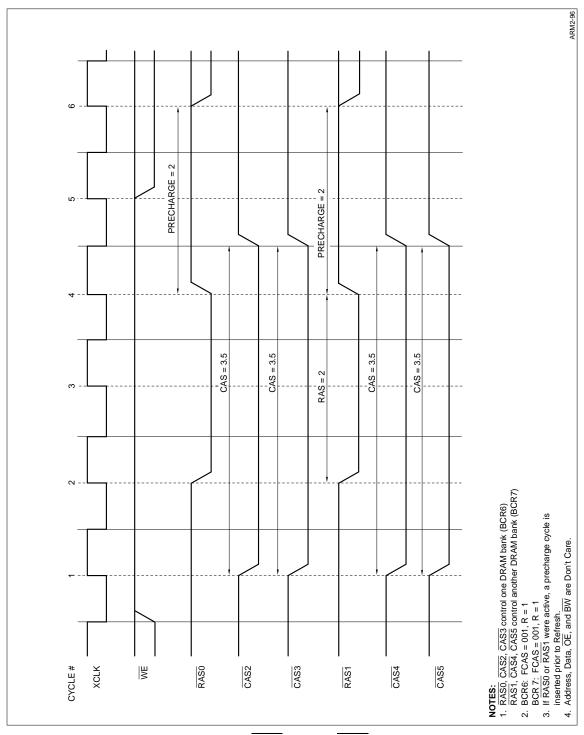

| DRAM CAS Before RAS Refresh Cycle                         |               |

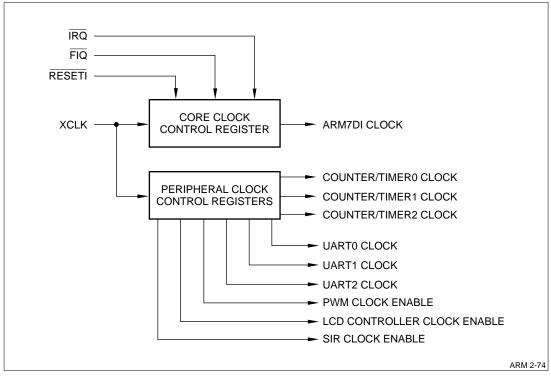

| Clock and Power Management Unit Block Diagram             |               |

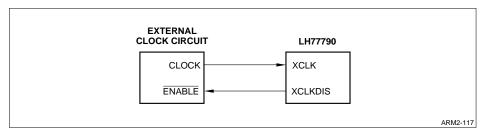

| External Clock Circuitry Example                          |               |

| UART0 Block Diagram                                       |               |

| SIR Interface Example                                     |               |

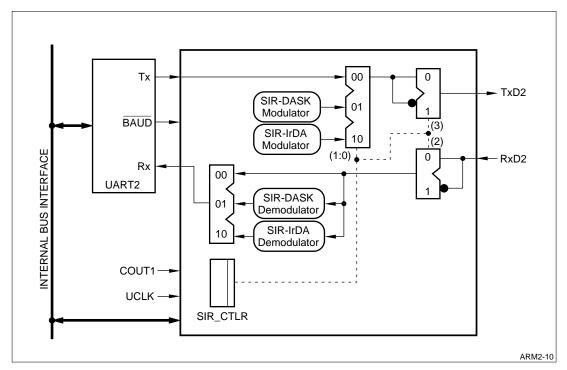

| SIR Block Diagram                                         |               |

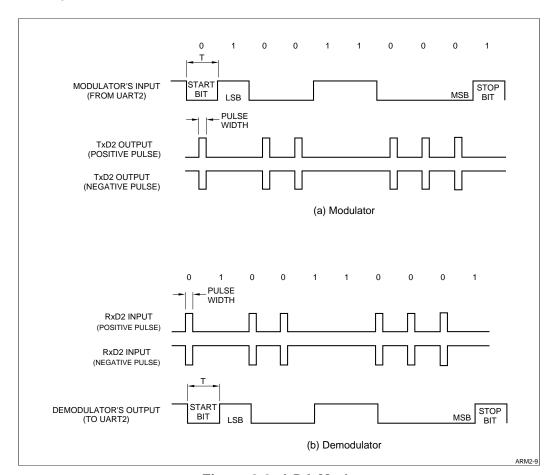

| IrDA Mode                                                 |               |

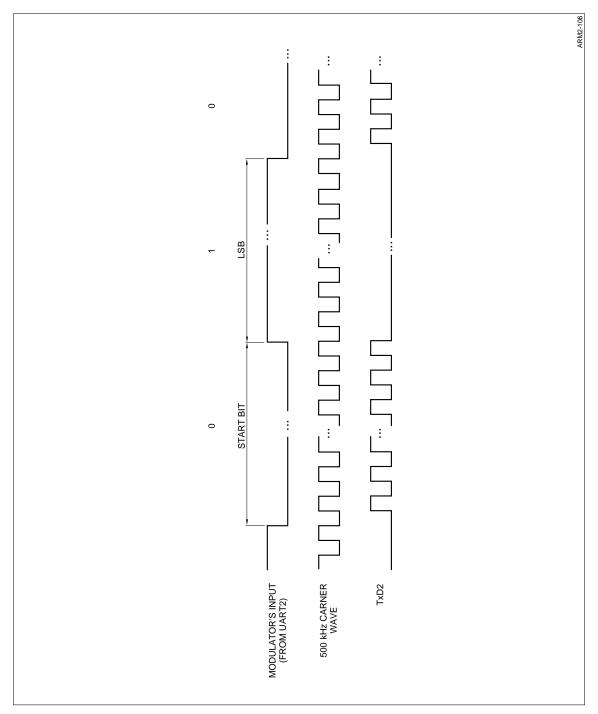

| DASK Mode: Modulator                                      |               |

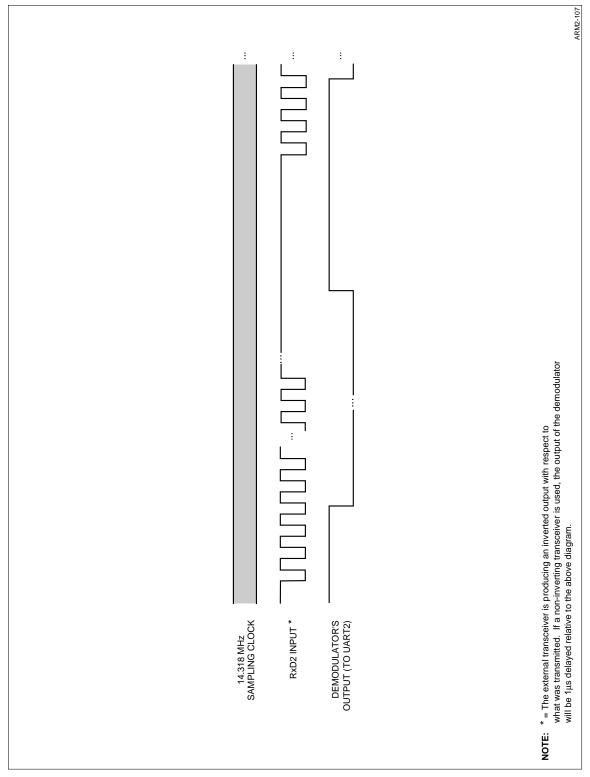

| Dask Mode: Demodulator                                    |               |

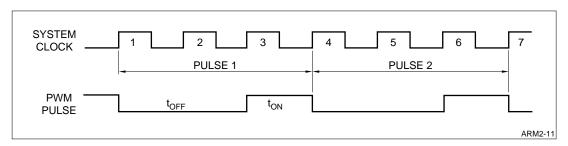

| PWM Timing Diagram                                        |               |

| Functional Block Diagram                                  |               |

| PWM0 Running in Normal Mode                               |               |

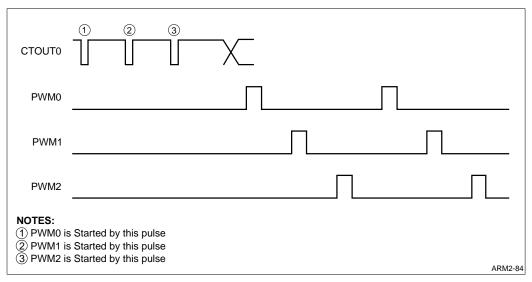

| PWM0, PWM1, PWM2 Running in Synchronous Mode              |               |

| PWMn_INV Example                                          |               |

| Block Diagram                                             |               |

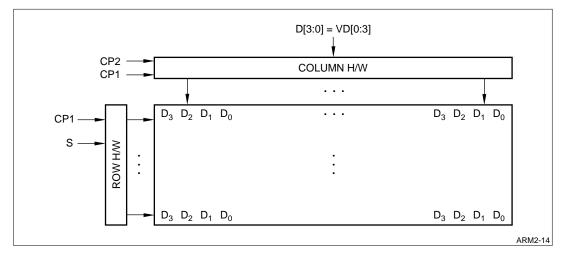

| Single Scan Mode 4-Bit Transfer                           |               |

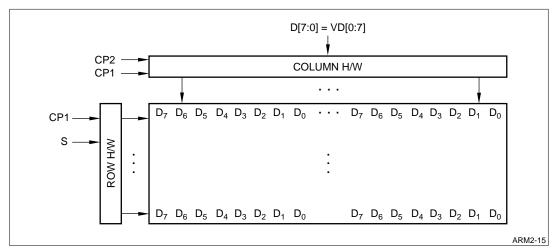

| Single Scan Mode 8-Bit Transfer                           |               |

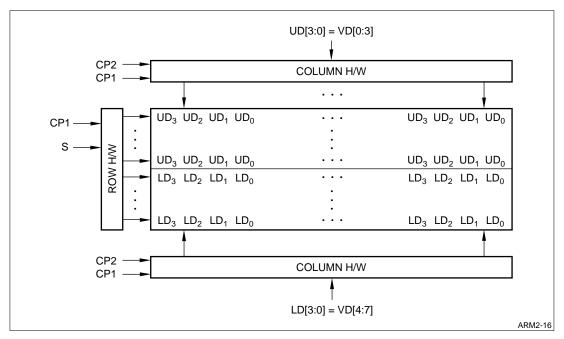

| Dual Scan Mode (Always 4-Bit Transfer)                    |               |

| CP1 Clock Pulse High Time                                 |               |

| LCD Panel in Dual Mode                                    |               |

| LCD Panel in Division Mode                                |               |

| LCD Panel Before Scrolling                                |               |

| LCD Panel After Scrolling                                 |               |

| Format 0 Gray Shade Logic                                 |               |

| Format 1 Gray Shade Logic                                 |               |

| MCLK and CP1 Relationship                                 |               |

| MCLK and CP1 Relationship                                 | 10-3 <i>′</i> |

| Three Channel Counter/Timer Block Diagram                       | 11-2  |

|-----------------------------------------------------------------|-------|

| Internal Diagram                                                | 11-2  |

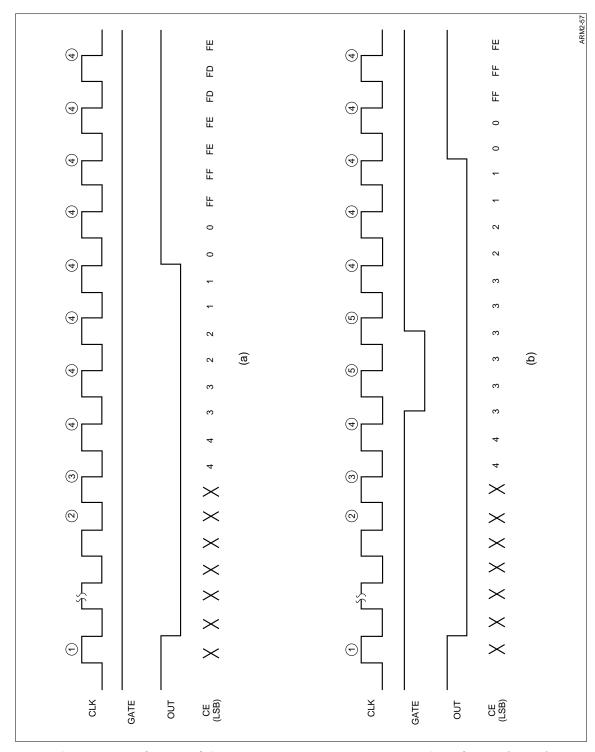

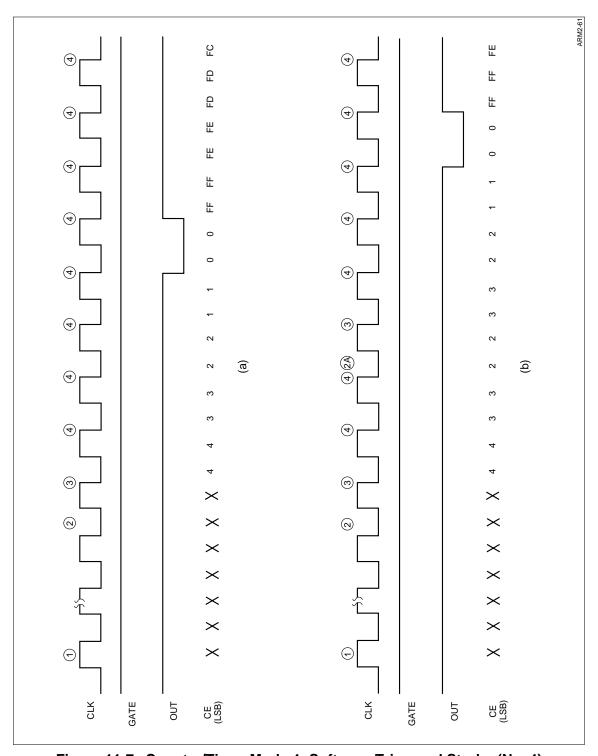

| Counter/Timer Mode 0: Interrupt On Terminal Count (N = 4)       | 11-10 |

| Counter/Timer Mode 1: Hardware Retriggerable One-shot (N = 4)   | 11-12 |

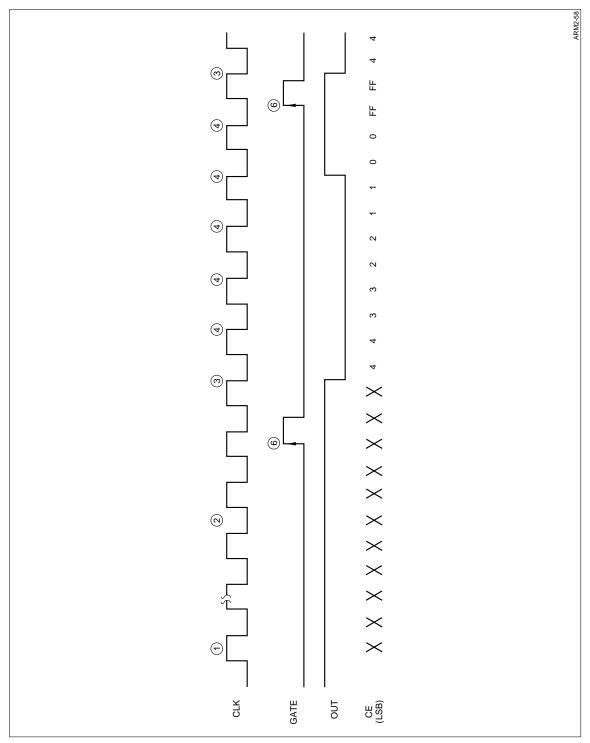

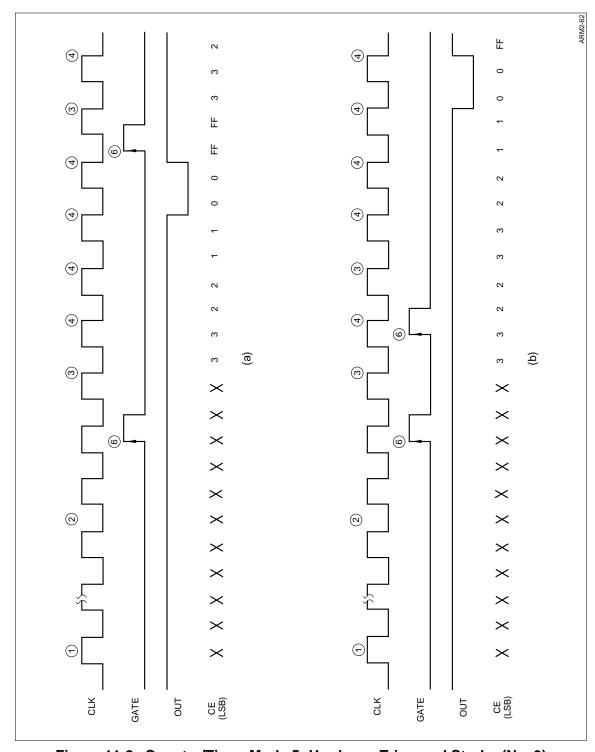

| Counter/Timer Mode 2: Rate Generator (N = 3)                    |       |

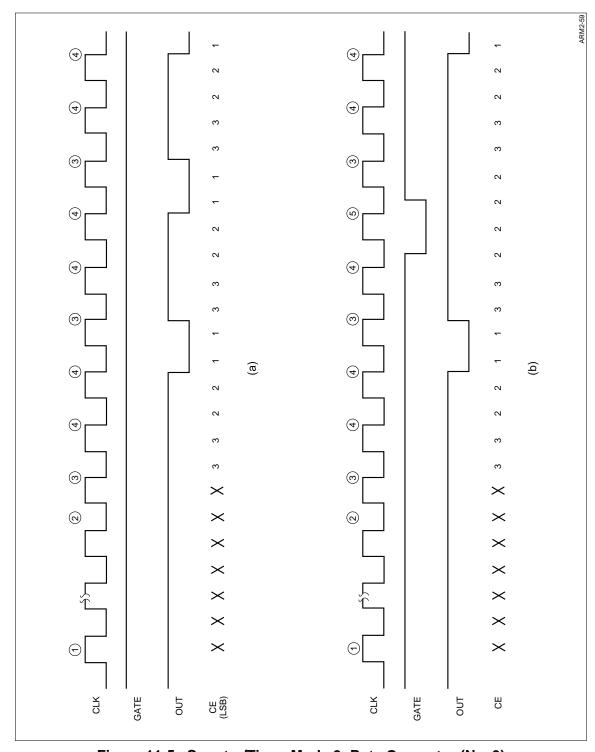

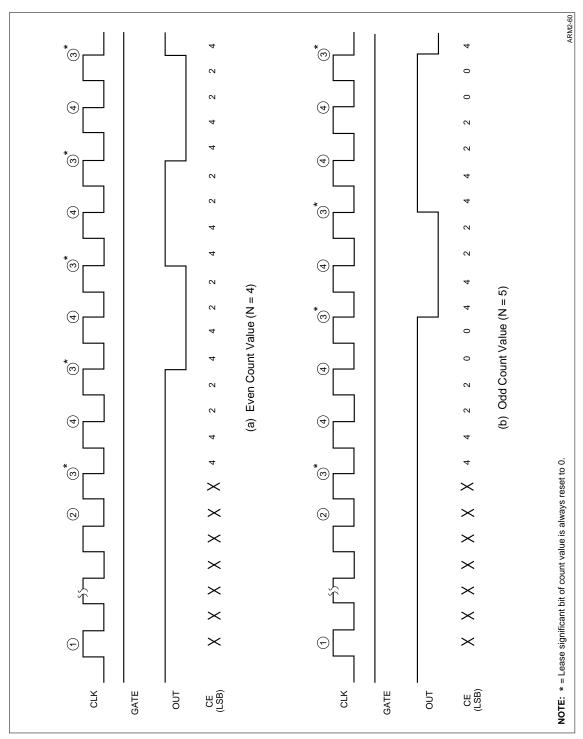

| Counter/Timer Mode 3: Square Wave Generator                     | 11-15 |

| Counter/Timer Mode 4: Software Triggered Strobe (N = 4)         | 11-16 |

| Counter/Timer Mode 5: Hardware Triggered Strobe (N = 3)         |       |

| Watchdog Timer Block Diagram                                    | 12-1  |

| Watchdog Timer Action Flow                                      | 12-2  |

| Programmable Peripheral Interface (PPI) Block Diagram           | 13-2  |

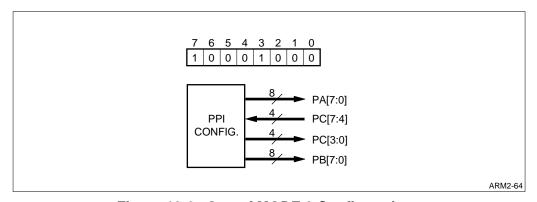

| One of MODE 0 Configurations                                    | 13-7  |

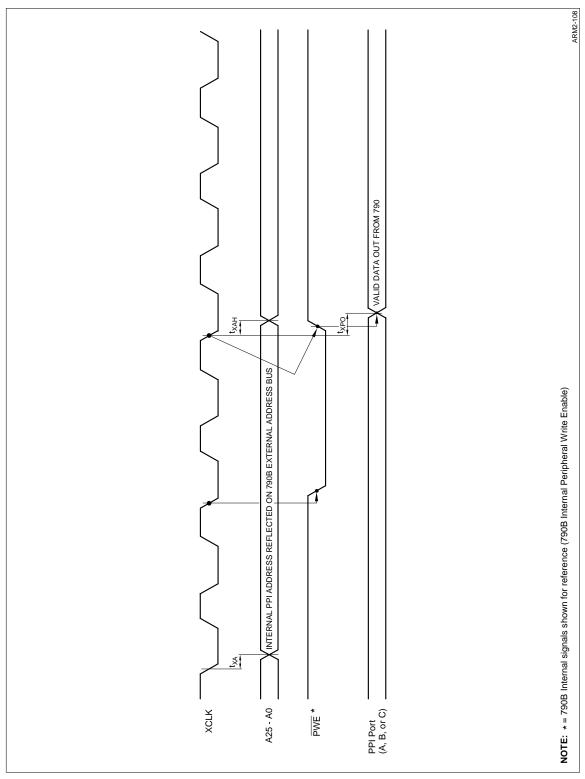

| MODE 0 Output Timing                                            | 13-8  |

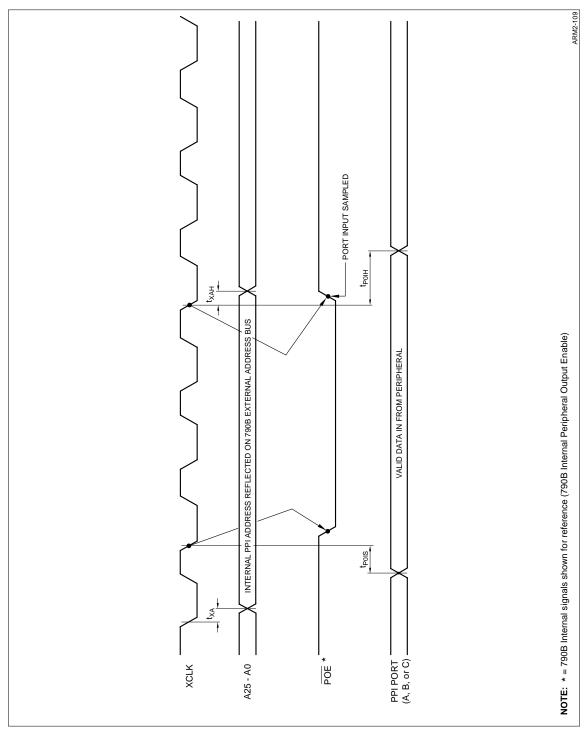

| MODE 0, Input Timing                                            | 13-9  |

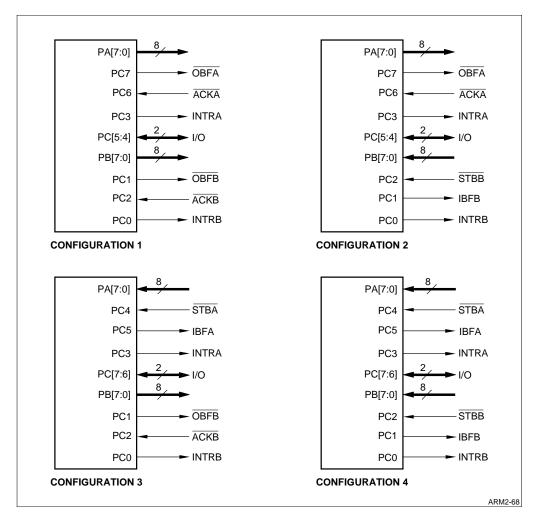

| MODE 1 Port Configurations                                      | 13-10 |

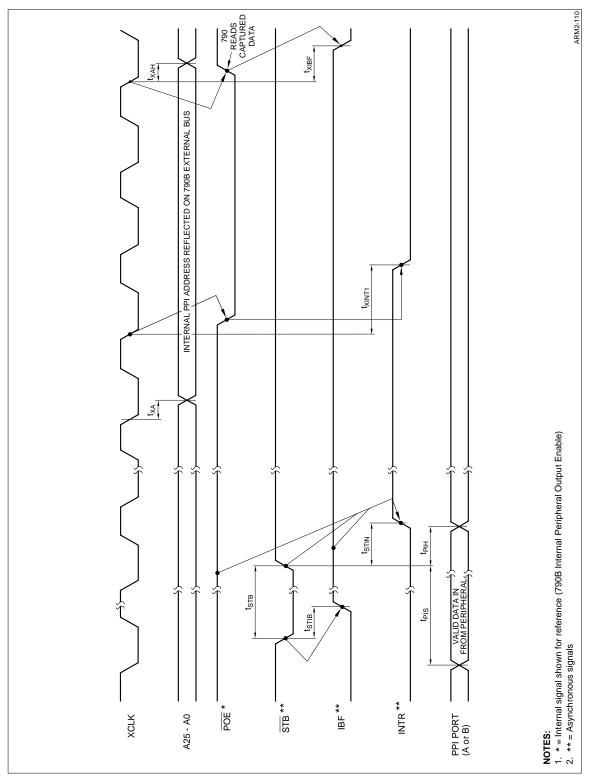

| MODE 1, Input Timing                                            | 13-12 |

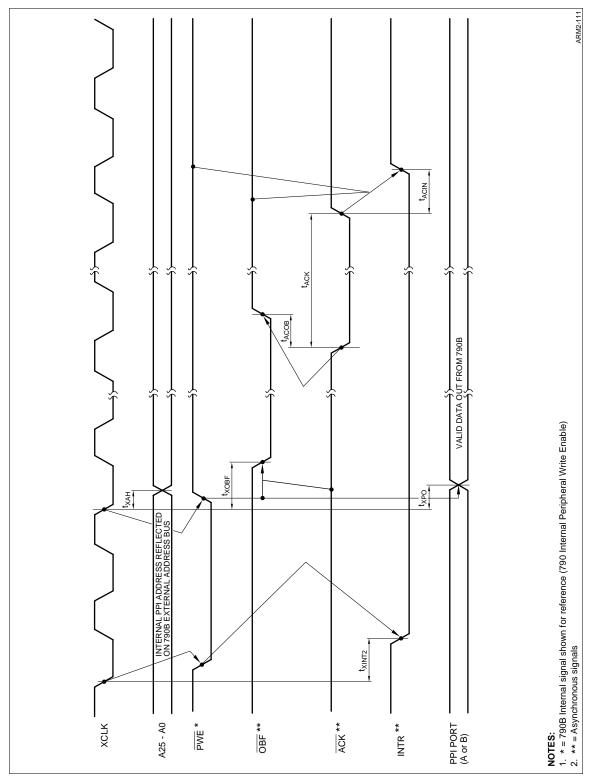

| MODE 1, Output Timing                                           | 13-14 |

| MODE 2 Port Configurations                                      | 13-15 |

| MODE 2, Bi-Direction Timing                                     | 13-17 |

| Interrupt Controller Block Diagram                              | 14-1  |

| Channel (i) Interrupt Flow                                      | 14-2  |

| LH77790B Scan Chains                                            | 18-1  |

| LH77790B Target System Connection to ARM's EmbeddedICE via JTAG | 18-2  |

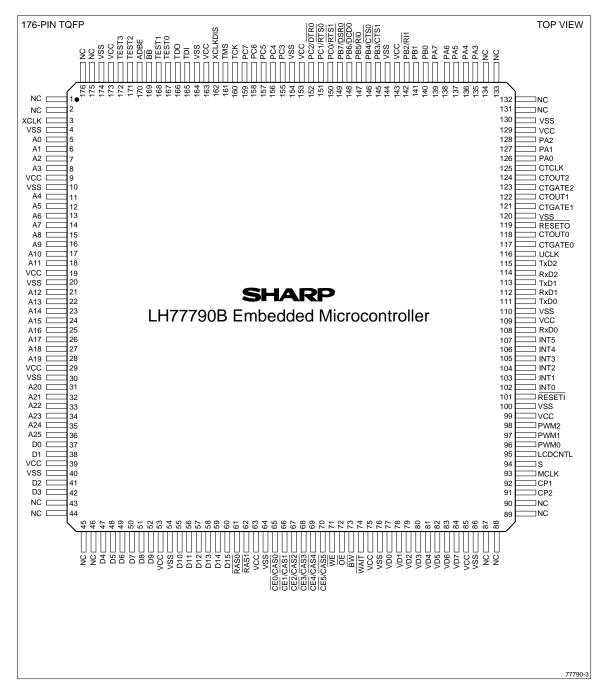

| LH77790B 176-Pin TQFP (Thin Quad Flat Pack) Pin Assignment      | 20-1  |

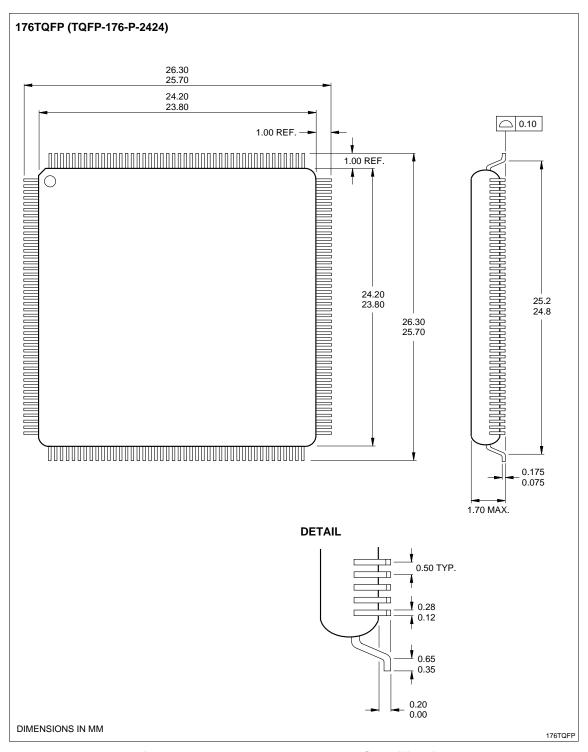

| LH77790B Package Specification                                  | 20-2  |

# **List of Tables**

| Pin Descriptions                         | 2-1  |

|------------------------------------------|------|

| Pinout                                   | 2-4  |

| Cache Register Offset                    | 4-1  |

| CCR Fields                               |      |

| Cache Status Bits                        |      |

| Cache Mapping in SRAM Mode               | 4-5  |

| Local SRAM Register Offset               | 4-6  |

| LSCR Fields                              | 4-7  |

| Memory Segment Registers                 | 5-3  |

| Bank Configuration Register              | 5-4  |

| SDR, START and STOP Association          | 5-7  |

| SDR Fields                               | 5-9  |

| BCR0 - BCR5 Fields                       |      |

| External SRAM Width                      | 5-12 |

| BCR6a - BCR7a Fields                     | 5-13 |

| External DRAM Width                      |      |

| Activation of CE/CAS and BW              | 5-14 |

| BCR6b - BCR7b Fields                     | 5-15 |

| DRAM Page Size                           | 5-17 |

| Address Bus Multiples for x8 DRAMs       |      |

| Address Bus Multiples for x16 DRAMs      | 5-19 |

| On-chip (Local) SRAM Memory Cycles       | 5-20 |

| Number of Transfers per Memory Access    |      |

| Normal Mode DRAM Cycle Parameters        | 5-22 |

| Page Mode DRAM Cycle Parameter           | 5-22 |

| CPMU Register Offset                     |      |

| LH77790B Power Modes                     | 6-3  |

| PCSR Fields                              |      |

| UART0 Clock Frequency                    | 6-6  |

| UART1 Clock Frequency                    | 6-7  |

| UART2 Clock Frequency                    | 6-8  |

| Counter/Timer0 Clock Frequency           | 6-9  |

| Clock/Timer1 Clock Frequency             |      |

| Counter/Timer2 Clock Frequency           |      |

| CPU Clock Frequency                      |      |

| UART External Interface                  |      |

| UART0 Register Map                       |      |

| UART1 Register Map                       |      |

| UART2 Register Map                       |      |

| Summary of UART Registers                |      |

| IER Fields                               |      |

| Interrupt Identification Bit Description |      |

| LCR Fields                               |      |

| MCR Fields                               |      |

| LSR Fields                               | 7-11 |

| MSR Fields                                                             | 7-12  |

|------------------------------------------------------------------------|-------|

| BAUD Generation                                                        | 7-13  |

| Baud Rate Division                                                     | 7-14  |

| SIR External Interface                                                 | 8-2   |

| SIR Register Offset                                                    | 8-2   |

| SIR_CTLR Fields                                                        | 8-7   |

| PWM Frequency Range                                                    | 9-1   |

| PWM External Interface                                                 |       |

| PWM Register Map                                                       | 9-4   |

| Synchronous Mode                                                       | 9-6   |

| PWMn_DIV Fields                                                        | 9-9   |

| PWMn_DIV Update                                                        |       |

| PWMn_TC Update                                                         | 9-10  |

| PWMn_DC Update                                                         | 9-11  |

| PWMn_INV Fields                                                        | 9-12  |

| PWMn_INV Update                                                        | 9-12  |

| PWMn_ENB Fields                                                        | 9-13  |

| PWMn_SYNC Fields                                                       |       |

| Static Programming Steps                                               |       |

| Dynamic Programming Steps                                              | 9-14  |

| Synchronous Mode Programming Steps                                     | 9-15  |

| Synchronous Mode Programming Steps                                     |       |

| LCD Panel Interface Signals                                            |       |

| LCD Display Data                                                       |       |

| LCD Controller Register Map                                            |       |

| LCD_MODE, DISP Bit                                                     |       |

| LCD_MODE, REV Bit                                                      | 10-6  |

| LCD_MODE, SCAN Bit                                                     |       |

| LCD_MODE, OR Bit                                                       |       |

| LCD_MODE, GRAY Bit                                                     | 10-7  |

| LCD_MODE, XSIZE                                                        |       |

| Transfer Size                                                          |       |

| LCD_MODE, LCDC                                                         |       |

| LCD_MODE, LCDA                                                         |       |

| LCD_MODE Register Summary                                              |       |

| LCD Controller Display Modes                                           |       |

| Relation Between LCD_BC and the Number of Display Pixels               |       |

| Padded Frame Buffer Example                                            |       |

| Line Pulse Width                                                       |       |

| Relation Between (LCD_DUTY) and Number of CP1 Pulses Per Frame         | 10-13 |

| Relationship between Screen #1 and Display Modes                       |       |

| Relationship Between Screen #2 and Display Modes                       |       |

| Relationship Between (LCD_VLC1) and Screen No. 1 Lines                 |       |

| Relationship Between LCD_VDLT and Address Difference                   |       |

| Relationship between Frame Buffer Byte, (x, y) Pair and LCD Bit Format |       |

| Four Gray Shades                                                       |       |

| Example of Pixel 1 State in Gray Scale Mode                            | 10-22 |

| Relationship Between LCD_CLKDIV and Divisor Value  | 10-23 |

|----------------------------------------------------|-------|

| Relationship Between LCD_MCLKW and CP1             | 10-24 |

| LCD_BITCTL, LBC Bit                                | 10-25 |

| Frame Buffers in Main Memory                       | 10-25 |

| Frame Buffer 1 After Shift Operation               | 10-27 |

| Passive Color Frame Buffer (RGB/Pixel)             | 10-28 |

| Parameter Description                              | 10-29 |

| tPXFR, tCPIW and tCP2 Parameters                   | 10-30 |

| Other LCD Timing Parameters                        | 10-30 |

| 790B Max. Frame Rates for VGA/HVGA/QVGA LCD Panels | 10-32 |

| LCD Specifications (e.g. Sharp's LM32P07)          | 10-33 |

| LCD Register's Value in Mode 1a Example            | 10-34 |

| LCD Specifications (e.g. Epson's EG9013F-NZ-1)     | 10-35 |

| LCD Register's Value in Mode 1b Example            | 10-35 |

| LCD Specifications (e.g. Sharp's LM32P07)          | 10-36 |

| LCD Register's Value in Mode 2 Example             | 10-36 |

| LCD Specifications (e.g. Sharp's LM32P07)          | 10-37 |

| LCD Register's Value in Mode 2 Example             | 10-37 |

| LCD Specifications                                 | 10-38 |

| LCD Register's Value in Mode 3b Example            | 10-38 |

| LCD Specifications (e.g. Sharp's LM32P07)          | 10-39 |

| LCD Register's Value in Mode 4 Example             | 10-39 |

| LCD Specifications (e.g. Sharp's LM64K101)         | 10-40 |

| LCD Register's Value in Mode 5 Example             | 10-40 |

| LCD Specifications                                 | 10-41 |

| LCD Register's Value in Mode 6 Example             | 10-41 |

| LCD Specification                                  | 10-42 |

| LCD Register's Value                               | 10-42 |

| Counter/Timer External Interface                   |       |

| Counter/Timer Registers                            |       |

| Control Word Fields                                | 11-4  |

| ReadBack Command Fields                            |       |

| Status Byte Fields                                 | 11-7  |

| Counter/Timer Diagrams' Key                        | 11-9  |

| GATE Effect                                        |       |

| OUT Summary                                        | 11-19 |

| Counter Summary                                    | 11-20 |

| Count Values Limits                                | 11-20 |

| Register Offset                                    |       |

| WDCTLR Fields                                      |       |

| Watchdog Timer Time-Out Periods                    |       |

| External Interface                                 |       |

| PPI Register Map                                   |       |

| Bit[7] Functions                                   |       |

| Bit[0]: Group B, Port C (PC[3:0]) Direction        |       |

| Bit[1]: Group B, Port B Direction                  |       |

| Bit[2]: Group B MODE Select                        | 13-4  |

| Bit[3]: Group A, Port C (PC[7:4]) Direction           | 13-4  |

|-------------------------------------------------------|-------|

| Bit[4]: Group A, Port A Direction                     | 13-5  |

| Bits[6, 5]: Group A Mode Select                       | 13-5  |

| Bit[0]: Set/Reset Function                            | 13-5  |

| Bits[3:1]: Port C Bit Selection                       | 13-5  |

| Interrupt Control                                     |       |

| PPI Operational Modes                                 | 13-6  |

| MODE 0 Port Configurations (Groups A and B in Mode 0) | 13-7  |

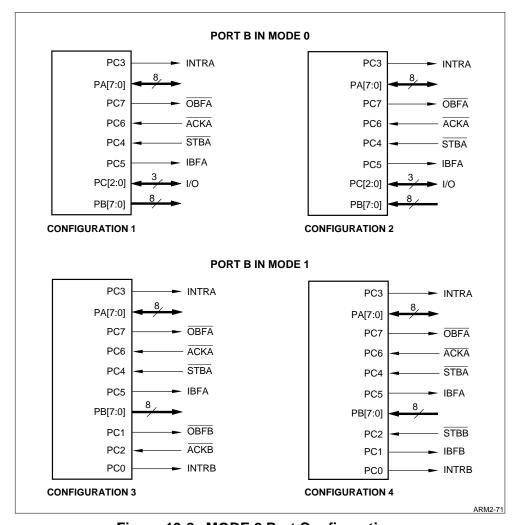

| MODE 1 Port Configurations (Groups A and B in Mode 1  | 13-10 |

| MODE 1 Input Control Signal Definitions               | 13-11 |

| MODE 1 Output Control Signal Definition               | 13-13 |

| MODE 2 Port Configurations                            | 13-15 |

| MODE 2 Bidirectional Control Signal Definition        | 13-16 |

| MODE 0: Groups A and B are both in Mode 0             | 13-18 |

| MODE 1: Groups A and B are both in Mode 1             | 13-18 |

| MODE 2                                                | 13-19 |

| Valid Modes                                           | 13-19 |

| MODE 1 Read Operation Configuration                   | 13-20 |

| MODE 2 Read Operation Configuration                   | 13-21 |

| Interrupt Controller Register Map                     | 14-2  |

| Interrupt Channel Assignment                          | 14-3  |

| ICR0/ICR1 Fields                                      | 14-4  |

| ICLR Fields                                           | 14-5  |

| IRQER Fields                                          | 14-6  |

| FIQER Fields                                          | 14-6  |

| IRQSR Fields                                          | 14-7  |

| FIQSR Fields                                          | 14-7  |

| IPR Fields                                            | 14-8  |

| Exception Vectors Summary                             | 14-9  |

| I/O Configuration Register Map                        | 15-1  |

| IOCR Fields                                           | 15-2  |

| SWRST Fields                                          | 16-2  |

| Register Map                                          | 17-1  |

| IDR Fields                                            | 17-2  |

| Recommended JTAG Pull-up Resistors                    | 18-3  |

| The LH77790B Memory Map                               |       |

| Address Range and Base Address of Registers           |       |

| LH77790B Register Summary                             | 19-4  |

|                                                       |       |

# Chapter 1 Overview

#### Introduction

Portable devices are becoming more and more prevalent in our daily life. They are used as personal information managers, communication devices, digital cameras, handheld games, bar-code scanners, medical equipment, electronic instrumentation, and navigation systems. There are significant design challenges for portable devices. Low cost is a top priority for high volume products. Low power is a must for long battery life. High performance is critical for computationally-intensive applications such as PDAs, GPS, and 2-D scanners. Communication capabilities and effective user interface are integral parts of any portable device. Last, but not least, superior product development support tools are crucial to reducing time-to-market.

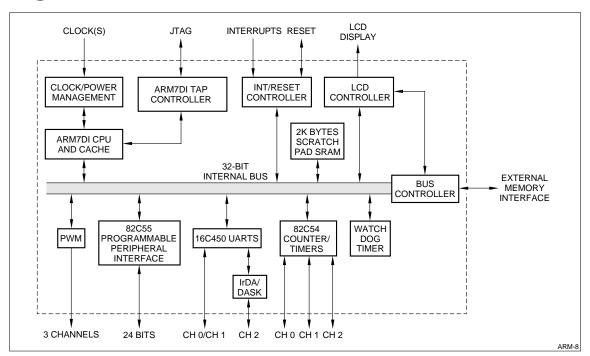

The System On Chip team at SHARP has designed the LH77790B Embedded Microcontroller (a.k.a. 790B) to meet the above challenges in portable design. The LH77790B, powered by an ARM7DI™, is a complete system on chip with a high level of integration to satisfy a wide range of customer requirements and expectations.

The 790B combines a 32-bit ARM7DI RISC engine, a number of essential peripherals (UARTs, Counter/Timers, PIOs, PWMs, etc...), LCD controller, cache, and on-chip SRAM. This high level of integration lowers overall system cost, reduces development cycle time and accelerates product introduction. The 790B's fully static design, power management unit, dual voltage operation (3.3 V/5 V), fast interrupt response time, on-chip cache and SRAM, powerful instruction set, and very low power RISC core provide high performance at low current draw. The on-chip LCD controller, UARTs, IrDA/DASK, and the programmable peripheral interface (PPI) are well suited for wireless, cable, and visual communication requirements. Other features like watchdog timer, programmable memory interface, on-chip SRAM/DRAM controllers and debug support provide a high level of flexibility.

Please check our website at www.sharpsma.com or with your local SHARP sales office for the latest Thermal and Electrical Specifications and/or errata sheets. These documents will contain the latest parameters for the LH77790B.

SHARP 1-1

#### **Features**

- Highly Integrated Single Chip

- 32-Bit ARM7DI RISC Core

- Built-In Debug and ICE Support

- Fast Interrupt Response

- Powerful Instruction Set

- 26-bit External Address Bus

- 512MB Addressable Space

- 16-bit External Data Bus

- 2KB Data/Instruction Cache

- 4 Way Set Associative

- Write Back Policy

- Flexible Modes of Operation

- 2KB Static RAM

- Expandable to 4KB without Cache

- Low Power

- High Performance

- Programmable Clock and Power Management

- Programmable Monochrome LCD Controller

- $-1024 (V) \times 2048 (H)$

- Four Gray Shades

- Frame buffer in Main Memory

- On-Chip Interrupt Controller

- Six External Interrupts

- Seven Internal Interrupts

- ARM7DI Wake-Up

- Three UARTs 16C450-class

- Full Modem Support on UART0

- Partial Modem Support on UART1

- IrDA-1.0/DASK Support on UART2

- IrDA/DASK IR Interface

- IrDA-1.0 (2.4 kbps to 115.2 kbps)

- DASK (2.4 kbps to 57.6 kbps)

- Three Pulse Width Modulator Channels

- PWM0 and PWM1 have 8-Bit Resolution

- PWM2 has 16-Bit Resolution

LH77790B User's Guide Overview

- · Flexible Memory Interface

- Six Multiplexeled Chip Enables/CAS pins

- Two RAS pins

- Fully Programmable

- Six SRAM Banks (64MB each)

- Two DRAM Banks (128MB each)

- Access Privileges (System/User)

- On-Chip DRAM Controller

- Fast Page Mode

- Normal Mode

- CAS before RAS Refresh

- Programmable Peripheral Interface (PPI)

- 24 Programmable I/O Signals

- Three Modes of Operation

- Three 16-Bit Counter/Timer Channels

- Six Modes of Operation

- Binary or BCD Counting

- Hardware Watchdog Timer

- Eight Time-out Intervals

- Protection Mechanism

- Three Time-out Actions

- Little Endian

- JTAG Interface

- Dual Supply Voltage

- 5 V TTL 25 MHz

- 3.3 V LVTTL 16.7 MHz

### **Development Environment**

The 790B Evaluation Board (part number LU7790AH2A) and the ARM Software Development ToolKit (part number LU7V211H1) give users full access to the power and features of the 790B and provide a complete integrated environment for development. Users will be able to develop, benchmark, and profile both hardware and software easily and quickly.

SHARP 1-3

### **Block Diagram**

Figure 1-1. LH77790B Block Diagram

#### Convention

| CONVENTION | DESCRIPTION           | EXAMPLE            |

|------------|-----------------------|--------------------|

| 0x         | Hex Number Prefix     | 0xFFFFA400<br>0x30 |

| 0b         | Binary Number Prefix* | 0b01101<br>01101*  |

| X          | Don't Care Value      | 0b0110X            |

**NOTE:** \*Sometimes a binary number is written without '0b' prefix.

### **Accessing Registers**

All registers that are more than 8-bit wide should be treated as 32-bit registers. Otherwise, the compiler will access them using two STRB/LDRB instructions (Store/Load Byte) resulting in incorrect data being written or read.

# Chapter 2 Pin Descriptions

**Table 2-1. Pin Descriptions**

| PINS                                  | NAME                      | DIRECTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------------------------------|---------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EXTERNAL BUS INTERFACE                |                           |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 36 - 31, 28 - 21,<br>18 - 11, 8 - 5   | A[25:0]                   | 0         | External Address bus. The 790B will provide a 26-bit address to external memories and peripherals.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 60 - 55, 52 - 47,<br>42 - 41, 38 - 37 | D[15:0]                   | I/O       | External 16-Bit data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 72                                    | ŌĒ                        | 0         | Output Enable for external memory and peripherals. $\overline{OE}$ allows external memory and peripherals to drive the data bus and is asserted LOW during a read access and HIGH during a write access.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 71                                    | WE                        | 0         | Write Enable for external memory and peripherals. During a write access, this pin is driven LOW. During a read access, this pin is driven HIGH.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 70 - 65                               | CE[5:0]/<br>CAS[5:0]      | 0         | These pins provide the Chip Enable/Column Address Select signals allowing direct connection to standard external memory/peripheral devices. The pins act as $\overline{CAS}$ when interfacing to DRAMs and as CE otherwise. They are fully programmable by the system designer and can support byte enables.                                                                                                                                                                                               |  |  |  |

| 62 - 61                               | RAS[1:0]                  | 0         | Row Address Select pins for DRAM Bank 0 and Bank 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 74                                    | WAIT                      | I         | External Memory Wait. Allows the use of slow memories. The 790B generates external WAIT cycles (EWC) in response to activating WAIT. WAIT is sampled on the HIGH to LOW transition on XCLK. To add one EWC, WAIT must be active prior to sampling in the last cycle (beginning of the last cycle) of a memory transfer. If WAIT continues to be active (when sampled) in subsequent cycles, more EWC will be added. Once WAIT is deactivated, the 790B will complete the memory transfer.                  |  |  |  |

| 73                                    | BW                        | 0         | Byte Wide Access. $\overline{BW}$ is LOW when the ARM7DI executes a store/load byte instruction. $\overline{BW}$ is HIGH when the ARM7DI Core executes a store/load word instruction or an instruction fetch. $\overline{BW}$ does not depend on the bus size of the external memory/peripheral device. $\overline{BW}$ is valid during an external memory access. It can be used by an external address decoder to generate extra chip/byte enables. $\overline{BW}$ is a don't care during DRAM refresh. |  |  |  |

| 169                                   | BB                        | ı         | Byte Boot selects between x8 or x16 for the boot memory. The 790B samples and captures the state of $\overline{BB}$ on the rising edge of $\overline{RESETI}$ allowing $\overline{BB}$ to change state after Reset. If $\overline{BB}$ is LOW the 790B will boot from a x8 memory. If $\overline{BB}$ is HIGH, the 790B will boot from a x16 memory. This pin is normally tied LOW for x8 boot memory or HIGH for x16 boot memory.                                                                         |  |  |  |

|                                       | COUNTERS/TIMERS INTERFACE |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 123, 121, 117                         | CTGATE[2:0]               | I         | Counter/Timer control gate input signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 124, 122, 118                         | CTOUT[2:0]                | 0         | Counter/Timer output signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                       |                           | INT       | ERRUPT INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 107 - 102                             | INT[5:0]                  | I         | External interrupt input signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

SHARP 2-1

Table 2-1. Pin Descriptions (Cont'd)

| PINS                                                                 | NAME                          | DIRECTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|-------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - 1                                                                  |                               |           | DNTROLLER INTERFACE                                                                                                                                                                                                                                                                                                             |

| 91                                                                   | CP2                           | 0         | Shift/Pixel Clock.                                                                                                                                                                                                                                                                                                              |

| 92                                                                   | CP1                           | 0         | Line Pulse/HSYNC.                                                                                                                                                                                                                                                                                                               |

| 93                                                                   | MCLK                          | 0         | AC Modulation Signal.                                                                                                                                                                                                                                                                                                           |

| 94                                                                   | S                             | 0         | Frame Pulse/VSYNC.                                                                                                                                                                                                                                                                                                              |

| 95                                                                   | LCDCNTL                       | 0         | LCD Control Signal.                                                                                                                                                                                                                                                                                                             |

| 84 - 77                                                              | VD[7:0]                       | 0         | Video Data.                                                                                                                                                                                                                                                                                                                     |

|                                                                      |                               | PROGRAMMA | BLE PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                        |

| 139 - 135, 128 - 126<br>149 - 145, 142 - 140<br>159 - 155, 152 - 150 | PA[7:0]<br>PB[7:0]<br>PC[7:0] | I/O       | Parallel ports A, B, and C signals. Signals have programmable access and can function as Input, Output or Controls (port C only). PB[7:2] and PC[2:0] are multiplexed with UARTs modem signals.                                                                                                                                 |

|                                                                      |                               |           | PWM INTERFACE                                                                                                                                                                                                                                                                                                                   |

| 98 - 96                                                              | PWM[2:0]                      | 0         | Pulse Width Modulator output signals.                                                                                                                                                                                                                                                                                           |

|                                                                      |                               | U         | ARTS INTERFACE                                                                                                                                                                                                                                                                                                                  |

| 114, 112, 108                                                        | RxD[2:0]                      | I         | UART serial data input signals. RxD2 also doubles as the digital input for the IR interface.                                                                                                                                                                                                                                    |

| 115, 113, 111                                                        | TxD[2:0]                      | 0         | UART serial data output signals. TxD2 also doubles as the digital output for the IR interface.                                                                                                                                                                                                                                  |

| 150, 151                                                             | RTS[1:0]                      | 0         | Request To Send for UART0 and UART1. Multiplexed with PC0 and PC1 respectively.                                                                                                                                                                                                                                                 |

| 145, 146                                                             | CTS[1:0]                      | I         | Clear To Send for UART0 and UART1. Multiplexed with PB3 and PB4 respectively.                                                                                                                                                                                                                                                   |

| 142, 147                                                             | RI[1:0]                       | I         | Ring Indicator for UART0 and UART1. Multiplexed with PB2 and PB5 respectively.                                                                                                                                                                                                                                                  |

| 152                                                                  | DTR0                          | 0         | Data Terminal Ready for UART0 only. Multiplexed with PC2.                                                                                                                                                                                                                                                                       |

| 149                                                                  | DSR0                          | I         | Data Set Ready for UART0 only. Multiplexed with PB7.                                                                                                                                                                                                                                                                            |

| 148                                                                  | DCD0                          | I         | Data Carrier Detect for UART0 only. Multiplexed with PB6.                                                                                                                                                                                                                                                                       |

|                                                                      |                               | RESET A   | AND EXTERNAL CLOCKS                                                                                                                                                                                                                                                                                                             |

| 101                                                                  | RESETI**                      | I         | Chip and JTAG TAP Controller Reset Input. RESETI has a built-in glitch detector. RESETO will be driven LOW after a valid reset is detected for as long as RESETI is driven LOW. JTAG reset, TRST, is internally connected to RESETI.                                                                                            |

| 119                                                                  | RESETO                        | 0         | Chip Reset Output. It will be driven LOW during: 1. Chip Reset 2. WDT Timeout Reset 3. Software Controlled Reset                                                                                                                                                                                                                |

| 3                                                                    | XCLK                          | I         | The 790B External Clock Input pin. Duty cycle is 50%.                                                                                                                                                                                                                                                                           |

| 162                                                                  | XCLKDIS                       | 0         | XCLKDIS is an active HIGH output pin that can be used to disable external clock circuitry and will result in reducing current consumption to micro-amperes. XCLKDIS is HIGH in Sleep and Stop modes. Connecting this pin to the external clock circuitry, allows the 790B to go into Stop mode by disabling the external clock. |

| 116                                                                  | UCLK                          |           | UART/DASK Demodulator External clock input signal. Duty cycle is 50%.                                                                                                                                                                                                                                                           |

| 125                                                                  | CTCLK                         | I         | Counter/Timer External clock input signal. Duty cycle is 50%.                                                                                                                                                                                                                                                                   |

LH77790B User's Guide Pin Descriptions

Table 2-1. Pin Descriptions (Cont'd)

| PINS                                                                               | NAME            | DIRECTION | DESCRIPTION                                                                                                                                                    |  |  |  |

|------------------------------------------------------------------------------------|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG INTERFACE**                                                                   |                 |           |                                                                                                                                                                |  |  |  |

| 160                                                                                | TCK             | I         | JTAG Test/EmbeddedICE™ clock input signal. Must be pulled-up for normal operation (56 kΩ is recommended for compatibility with ARM's EmbeddedICE)              |  |  |  |

| 161                                                                                | TMS             | I         | JTAG Test/EmbeddedICE mode select input signal. Must be pulled-up for normal operation (56 k $\Omega$ is recommended for compatibility with ARM's EmbeddedICE) |  |  |  |

| 165                                                                                | TDI             | I         | JTAG Test/EmbeddedICE data input signal. Must be pulled-up for normal operation (56 k $\Omega$ is recommended for compatibility with ARM's EmbeddedICE)        |  |  |  |

| 166                                                                                | TDO             | 0         | JTAG Test/EmbeddedICE data output signal.                                                                                                                      |  |  |  |

|                                                                                    |                 | RES       | SERVED INTERFACE                                                                                                                                               |  |  |  |

| 170                                                                                | ADBE            | I         | Reserved. Must be tied HIGH for normal operation.                                                                                                              |  |  |  |

| 167                                                                                | TEST0           | I         | Reserved. Must be tied LOW for normal operation.                                                                                                               |  |  |  |

| 168                                                                                | TEST1           | 0         | Reserved. No Connect.                                                                                                                                          |  |  |  |

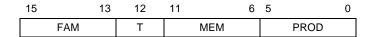

| 171                                                                                | TEST2           | I         | Reserved. Must be tied LOW for normal operation                                                                                                                |  |  |  |