TL/H/9242-1

# LM1141 Dolby B-C Type Noise Reduction Processor

## **General Description**

The LM1141 is a monolithic integrated circuit specifically designed to realise both Dolby B- and Dolby C-type noise reduction systems\*. The circuit has a single input pin for Encode and Decode and includes all active components and switching internally to provide a single channel of a Dolby B- or Dolby C-type system. The low power consumption and compact package design make it ideal for use in automotive and portable Hi-Fi as well as quality cassette or tape sound systems.

\*Available only to licensees of Dolby Laboratories Licensing Corporation. Dolby and the double D symbol are registered trademarks of Dolby Laboratories Licensing Corp.

#### **Features**

- Very low supply current (11.5 mA typ.)

- Wide supply voltage range, 5-16V

- Alternative Dolby levels, 245 mV or 580 mV

- Provision for MPX filter

- Very high signal to noise ratio, 66 dB typ. for encode, C mode CCIR/ARM

- 50 mV encode input sensitivity (30 mV decode)

- D.C.-controlled mode switching

- Minimal switching transients

- 28 pin DIP or QUAD packages available

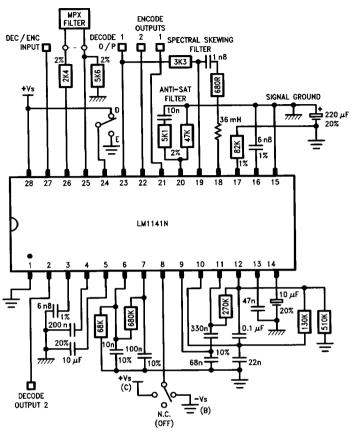

### **Block Diagram**

Order Number LM1141N or LM1141V See NS Package Number N28B or V28A

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage, Vs 17V

Input Voltage, Encode/Decode Vs

Input Voltage, Switching + Vs + 0.5V

$- \mbox{Vs} - 0.3 \mbox{V} \\ \mbox{Soldering Information} \\ \mbox{Dual-In-Line Package} \\ \mbox{}$

Operating Temperature Range

O°C to +70°C

Storage Temperature Range

-65°C to +150°C

Package Dissipation

| M1141N = 2.5W

Electrical Characteristics Vs = 12V, TA = 25°C unless otherwise stated.

0 dB refers to Dolby level which is 245 mV measured at Encode Output 1 with NR OFF. Note: Encode input sensitivity = 50 mV, Decode input sensitivity = 30 mV

| Parameter                         | Conditions                                                                                        | Test Limit<br>Note 2 |              | Design Limit<br>Note 3 |                          |             | Ī              |

|-----------------------------------|---------------------------------------------------------------------------------------------------|----------------------|--------------|------------------------|--------------------------|-------------|----------------|

|                                   |                                                                                                   | Min                  | Max          | Min                    | Тур                      | Max         | Units          |

| Supply Voltage                    | Min Signal Handling = 12 dB<br>at Encode O/P 1                                                    | 5                    | 16           |                        |                          |             | V              |

| Supply Current                    | Encode, NR OFF, No signal                                                                         |                      | 16           |                        | 11.5                     |             | mA             |

| Voltage Gain (Note 4)             | Encode O/P 1, NR OFF<br>Encode O/P 2, NR OFF                                                      | 12.5<br>19.8         | 15.1<br>22.8 |                        | 13.8<br>21.3             |             | dB<br>dB       |

|                                   | Decode O/P 1, NR OFF<br>Decode O/P 2, NR OFF                                                      | 16.9<br>24.2         | 19.5<br>27.2 |                        | 18.2<br>25.7             |             | dB<br>dB       |

| Input Resistance                  | Encode/Decode Input                                                                               | 35                   | 80           |                        | 55                       | <u> </u>    | kΩ             |

| Signal To Noise<br>Ratio (Note 5) | Encode O/P 1 or 2,<br>Rs = 5.6 kΩ C Mode<br>C.C.I.R./A.R.M B Mode                                 |                      |              | 62<br>70               | 66<br>76                 |             | dB<br>dB       |

|                                   | Decode O/P 1 or 2,<br>Rs = $5.6 \text{ k}\Omega$ , NR OFF                                         |                      |              | 78                     | 84                       |             | dB             |

| Signal handling                   | Enc O/P 1, Dec O/P 1, 1 kHz<br>Vs = 5V, NR OFF, 1% T.H.D.                                         | 12                   |              |                        | 13                       |             | dB             |

|                                   | Enc O/P 2, Dec O/P 2, 1 kHz<br>Vs = 9V, NR OFF, 1% T.H.D.                                         | 12                   |              |                        | 13                       |             | dB             |

| Distortion<br>(T.H.D.)            | Encode O/P2, C Mode<br>0 dB, 1 kHz<br>Decode O/P2, C Mode                                         |                      |              |                        | 0.05                     | 0.15        | %              |

|                                   | 0 dB, 1 kHz                                                                                       |                      |              |                        | 0.04                     | 0.15        | %              |

| Encode Characteristics            | B Mode, 5 kHz, 0 dB<br>B Mode, 1 kHz, – 20 dB<br>B Mode, 5 kHz, – 30 dB<br>B Mode, 1 kHz, – 40 dB | 6.7<br>4.7           | 9.7<br>7.7   | -1.2<br>2.7            | 0.3<br>4.2<br>8.2<br>6.2 | 1.8<br>5.7  | dB<br>dB<br>dB |

|                                   | C Mode, 10 kHz, -0 dB<br>C Mode, 1 kHz, -20 dB<br>C Mode, 5 kHz, -30 dB                           |                      |              | 5.5<br>3.9             | -3.5<br>5.9              | -1.5<br>7.9 | dB<br>dB<br>dB |

|                                   | C Mode, 5 kHz, -40 dB                                                                             | 6.4<br>14.2          | 10.4<br>18.2 |                        | 8.4<br>16.2              |             | dB<br>dB       |

| Control Voltage                   | Encode Mode<br>Decode Mode<br>B Mode                                                              | 2.0                  | 0.8          | 0                      |                          | Vs          | V<br>V         |

|                                   | Off Mode C Mode                                                                                   | 2.0<br>4.6           | 0.8<br>3.2   | 0                      | Open                     | Vs          | V<br>V         |

**Note 1:** Above  $T_A = 25^{\circ}C$ , derate with  $\theta_{ja} = 50^{\circ}C/W$  (LM1141N)

75°C/W (LM1141V)

Tj max = 150°C

Note 2: Guaranteed and 100% production tested.

Note 3: Guaranteed but not 100% production tested. These limits are not used to calculate outgoing quality levels.

Note 4: The resistors at the input and output of the MPX Filter are required to match the characteristic impedance of the filter block. The values shown correspond to the most commonly used filter for this application. Values should be checked for each individual application. If no filter is used, a 3.1 dB attenuation pad should be retained for correct operation of the processor.

Note 5: Gaussian noise, monitored over a period of 50 ms with a CCIR filter and an average-responding meter.

## **Pin Function Description**

- PIN 1. Negative supply voltage, -Vs.

- PIN 2. High level decode (playback) output, (580 mV).

- PIN 3. Connection to the variable impedance of sidechain 2. A capacitor is connected between this pin and signal ground to give a variable high pass filter characteristic, controlled by the sidechain.

- PIN 4. A capacitor is connected between this pin and signal ground to provide pre-emphasis at amplifier D in sidechain 2.

- PIN 5. A capacitor is connected between this pin and signal ground which decouples the feedback components of amplifier D of sidechain 2, and reduces system offsets.

- PIN 6/7. Sidechain 2 transient response circuit.

- PIN 8. Selects OFF, B or C mode depending on the d.c. voltage applied.

- PIN 9/10. These pins are connected internally to low saturation switching transistors and externally to the transient response circuit of sidechain 1 in such a way that in C-mode the capacitor values are reduced.

- PIN 11/12 Sidechain 1 transient response circuit.

- PIN 13. A capacitor is connected between this pin and signal ground to provide pre-emphasis at amplifier D in sidechain 1.

- PIN 14. A capacitor is connected between this pin and signal ground which decouples the feedback components of amplifier D of sidechain 1, and reduces the system offsets.

- PIN 15. Signal ground, set internally to approximately half the supply voltage.

- PIN 16. Connection to the variable impedance of sidechain 1. A capacitor is connected between this pin and signal ground to give a variable high pass filter characteristic, controlled by the sidechain.

- PIN 17. A resistor is connected between this pin and

—Vs. This sets up an accurate current required

for correct maximum impedance filter characteristics.

- PIN 18. This pin is connected internally to a low saturation switching transistor and is energised to switch on the Spectral Skewing circuit in Cmode.

- PIN 19. The Spectral Skewing circuit is connected to this pin.

- PIN 20. The Anti-Saturation circuit is connected to this

- PIN 21. Low level encode (record) output (245 mV).

- PIN 22. High level encode (record) output (580 mV).

- PIN 23. Low level decode (playback) output (245 mV).

- PIN 24. Selects encode or decode mode depending on the d.c. voltage applied.

- PIN 25. MPX filter output.

- PIN 26. MPX filter input.

- PIN 27. Signal input (encode and decode).

- PIN 28. Positive supply voltage, + Vs.

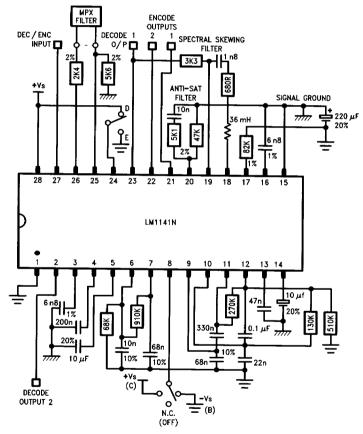

## **Typical Applications**

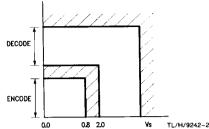

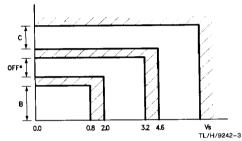

Selection of encode/decode and off/B/C is achieved by applying the required d.c voltage to the appropriate control pin. *Figures 1* and *2* show the relationship between the applied voltage and the mode selected.

FIGURE 1. Pin 24 control voltage (V).

\* Pin 8 open also gives Off mode.

#### FIGURE 2. Pin 8 control voltage (V).

Although audible switching pops have been reduced to a minimum, further improvement may be achieved by including an R-C time constant on the switching pins.

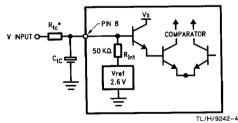

The values chosen for the R-C circuit connected to the OFF-B-C switching pin (8) are important in order that the switching circuitry functions correctly.

The internal configuration at pin 8 includes connection to a darlington input stage comparator and a 2.6V voltage reference via a resistor of value 50 k $\Omega$ , (see *Figure 3*) which allows selection of OFF mode when pin 8 is open-circuited, (See specification).

\* $R_{tc}$  max = 5 k $\Omega$  for 5V operation.

#### FIGURE 3

The capacitor  $C_{tc}$  affects the switching time when selecting OFF-mode (pin 8 open) from C mode. The discharge path is now via the 50 k $\Omega$  resistor to Vref, hence the switching time

# Typical Applications (Continued)

is a function of  $R_{\text{int}}C$ . The Encode/Decode switching pin (24) is unaffected by the connection of a similar R-C network.

#### **Connection of Supply Voltage**

The device may be operated in either single ended or dual supply modes, since the internally generated bias voltage (pin 15) is approximately half the supply voltage.

For single supply applications a large electrolytic capacitor (200  $\mu$ F) should be connected between pin 15 and -Vs.

For dual supply operation this capacitor is not required and pin 15 can be connected to 0y directly.

#### Sidechain Variable High Pass Filters

In encode mode the boost characteristics are controlled by the variable impedances of the sidechains in conjunction with external capacitors and a resistor forming a variable high pass filter.

The capacitors and the resistor (on pin 17 and common to both sidechains) must be accurate and of high stability (a tolerance of 1% is recommended).

# Typical Connection Diagram for 5V to 9V Supply

(All external components 5% unless otherwise stated.)

\*MPX Filter, See note 4 in General Notes.

Device also available in 28 pin quad chip carrier package.

TL/H/9242-5

TL/H/9242-6

# Typical Connection Diagram for 8V to 16V Supply

(All external components 5% unless otherwise stated.)

\*MPX Filter, See note 4 in General Notes.

Device also available in 28 pin quad chip carrier package.