SNOSAHOD - MARCH 2005 - REVISED APRIL 2013

# LM1229 I2C Compatible CMOS TV RGB and Deflection Processor

Check for Samples: LM1229

### **FEATURES**

- Fully Bus Controllable via an I<sup>2</sup>C Compatible Interface

- Contrast Control for Simultaneously Adjusting the RGB Output Peak to Peak Levels

- Gain Controls for Aligning the CRT Color Temperature

- Color Tracking Brightness Control for Maintaining Color Temperature Throughout the Full Range of Adjustment

- Black Level Clamping to Ensure Output Level Stability. The Polarity of the Logic Pulse Input is Register Selectable

- Digital or Analog RGB OSD Inputs, with Adjustable Transparency Available in the Digital Mode and Clamping in the Analog Mode for Black Level Stability

- Choice of Four Levels of OSD Amplitude

- Window Highlight using the OSD Transparency Feature

- ABL Input for Reducing the Video Contrast when the CRT Beam Current Exceeds the Predetermined Threshold et by an External Resistor

- Horizontal and/or Vertical Blanking Directly from Deflection Signals. The Blanking can be Disabled, if Desired

- Matched to TI's Driver and Clamp IC Families

- Black Level Output Adjustable from 0.5V to 1.4V for Compatibility with TI CRT Driver IC's with or without PNP Transistor Buffers

- Three DAC Outputs for Setting CRT Cathode Bias, which can be Set to Full or Half Scale like the LM1267 Series of Preamplifiers

- Spot Killer which Blanks the Video Outputs when V<sub>CC</sub> Falls below the Specified Threshold

- RGB Power Saving Mode with 35% Power Reduction

- Support for Seven Different TV Signal Formats

- RGB Blanking for Scan Loss Protection

- I<sup>2</sup>C Control over Horizontal and Vertical Position and Size, Pincushion, Pin Balance, Trapezoidal, Parallelogram, Top and Bottom Corner Corrections, Vertical S and C Correction, and Dynamic Focus Amplitude

- Programmable Duration 5V Vertical Blanking Output Pulse

- Uses a Low Cost Resonator

- Status Register Indicating Vertical Scan Loss, X-Ray, Horizontal Flyback and Horizontal Lock Status

- Blanks the RGB Outputs Whenever the Loss of Vertical Scan is Detected

- Independent Control over Horizontal and Vertical Sync Input Polarities

#### **APPLICATIONS**

Television Deflection and RGB Video Processing with TI's CRT Drivers

#### **DESCRIPTION**

The LM1229 pre-amp is an integrated CMOS CRT RGB preamp plus horizontal and vertical deflection processing with an I<sup>2</sup>C compatible interface for controlling all the parameters necessary to directly adjust the gain, contrast and brightness and geometry of the CRT display.

In the RGB section, the CRT bias is controlled by the three DAC outputs which are matched to the LM248x integrated bias clamp ICs. The brightness control operates on the video channels rather than the bias channels and is designed to maintain the CRT color temperature through the full range of adjustment. The On Screen Display inputs accept either digital or analog input levels. Black level clamping of the video signal is carried out directly on the AC coupled input signal into the high impedance preamplifier input, thus eliminating the need for additional clamp capacitors. Blanking inputs are provided which can accept both horizontal and vertical flyback inputs for composite blanking of the video. A vertical blanking output pulse is provided which can drive a G1 blanking amplifier such as the one in TI's LM2485 clamp IC. The LM1229 RGB outputs are compatible with TI's high gain drivers.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

### **DESCRIPTION (CONTINUED)**

he Deflection section uses a 12.0 MHz resonator and with it the horizontal processor is capable of locking to seven different television signal formats, 15.734, 28.1, 31.468, 33.7, 37.9, 45.0, and 48.08 kHz by configuring two external tri-state pins. The resonator frequency can be scaled up or down by as much as 5% to accommodate custom scan frequencies, however all scan modes will be scaled up or down by the same percentage. Additional inputs are provided for H and V synchronization, X-Ray protection, V scan protection, and H and V EHT compensation. Deflection output signals are provided for horizontal drive, variable amplitude vertical ramp, vertical ramp reference voltage, variable amplitude dynamic focus, and E-W correction with DC level adjustment for size.

A status register is also provided for the system microcontroller to read and check for failure conditions.

The IC is packaged in an industry standard 64 lead LQFP molded plastic package.

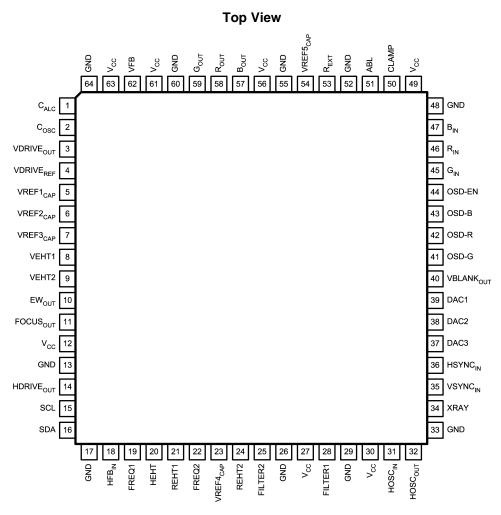

### LM1229 Package and Pinout

Figure 1. 64-Pin Non-Exposed DAP - TQFP Package See Package Number PAG0064A Exposed DAP - HTQFP Package See Package Number PAP0064A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Submit Documentation Feedback

SNOSAHOD -MARCH 2005-REVISED APRIL 2013

# Absolute Maximum Ratings(1)(2)

| 6.0V                                         |

|----------------------------------------------|

| 1.0 mA                                       |

| $V_{CC} - 0.5V \le V_{IN} \le V_{CC} + 0.5V$ |

| 0V ≤ V <sub>IN</sub> ≤ 1.2V                  |

| 1.8W                                         |

| 35 °C/W                                      |

| 41 °C/W                                      |

| 27 °C/W                                      |

| 150°C                                        |

| 3.5 kV                                       |

| 350V                                         |

| −65°C to +150°C                              |

| 265°C                                        |

|                                              |

- (1) All voltages are measured with respect to GND, unless otherwise specified.

- (2) Limits of Absolute Maximum Ratings indicate below which damage to the device will not occur.

- (3) Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

- (4) Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200 pF cap is charged to the specific voltage, then discharged directly into the IC with no external series resistor (resistance of discharge path must be under 50Ω).

### Operating Ratings<sup>(1)</sup>

| Temperature Range              | 0°C to +70°C                    |

|--------------------------------|---------------------------------|

| Supply Voltage V <sub>CC</sub> | 4.75V ≤ V <sub>CC</sub> ≤ 5.25V |

| Video Inputs (peak-peak)       | 0V ≤ V <sub>IN</sub> ≤ 1.0V     |

(1) Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits.

### **Video Signal Electrical Characteristics**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.70 V_{P-P}$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 10 pF$ , Video Outputs = 2.4  $V_{P-P}$ <sup>(1)(2)</sup>

| Symbol                                       | Parameter                               | Conditions                                                                               | Min | Тур   | Max | Units |

|----------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Is                                           | Supply current                          | No output loading <sup>(3)</sup>                                                         |     | 260   | 330 | mA    |

| I <sub>S-PS</sub>                            | Supply current, power save mode         | No output loading <sup>(3)</sup>                                                         |     | 100   | 125 | mA    |

| V <sub>OB TYP</sub>                          | Active video black level output         | No input signal, DC offset = 0x3.                                                        |     | 1.25  |     | V     |

| V <sub>OB MIN</sub>                          | Active video minimum black level output | No input signal, DC offset = 0xF(min)                                                    |     | 0.5   |     | V     |

| V <sub>OB MAX</sub>                          | Active video maximum black level output | No input signal, DC offset = 0x0(max)                                                    |     | 1.45  |     | V     |

| V <sub>OB STEP</sub>                         | Active video black level step size      | No input signal. Varying DC offset.                                                      |     | 65    |     | mV    |

| V <sub>OB MIN BRITE</sub>                    | Active video minimum black level output | No input signal, DC offset = 0x3,<br>gain = 0x7F, brightness.= 0xFF(min)                 |     | 0.8   |     | V     |

| V <sub>OB MAX BRITE</sub>                    | Active video maximum black level output | No input signal, DC offset = 0x3, gain = 0x7F, brightness.= 0x00(max)                    |     | 1.65  |     | V     |

| V <sub>OBB STEP</sub>                        | Active video brightness step size       | No input signal, DC offset = 0x3, varying brightness                                     |     | 6.3   |     | mV    |

| V <sub>O MAX</sub>                           | Maximum video output                    | Video in = 0.70 V <sub>P-P</sub> , contrast = 0x7F,<br>brightness = 0x0, DC offset = 0x3 |     | 4.75  |     | V     |

| LE                                           | Linearity error                         | Staircase input signal (4)                                                               |     | 5     |     | %     |

| t <sub>R</sub> <sup>(5)</sup>                | Video rise time                         | 10% to 90%, AC input signal (6)                                                          |     | 8     |     | ns    |

| OS <sub>R</sub>                              | Rising edge overshoot                   | AC input signal (6)                                                                      |     | 2     |     | %     |

| t <sub>F</sub> <sup>(5)</sup>                | Video fall time                         | 90% to 10%, AC input signal (6)                                                          |     | 8     |     | ns    |

| OS <sub>F</sub>                              | Falling edge overshoot                  | AC input signal (6)                                                                      |     | 2     |     | %     |

| BW                                           | Channel bandwidth (-3 dB)               | AC input signal (6)                                                                      |     | 70    |     | MHz   |

| SEP <sub>10 kHz</sub>                        | Video amplifier 10 kHz isolation        | See <sup>(7)</sup>                                                                       |     | 70    |     | dB    |

| SEP <sub>10 MHz</sub>                        | Video amplifier 10 MHz isolation        | See <sup>(7)</sup>                                                                       |     | 50    |     | dB    |

| A <sub>V MAX</sub>                           | Maximum voltage gain                    | Video in = 0.70 V <sub>P-P</sub> , Maximum contrast and gain, V <sub>ABL</sub> = 5.0V    |     | 4.35  |     | V/V   |

| A <sub>V 50% CONT</sub>                      | Contrast attenuation @ 50%              | Maximum gain, V <sub>ABL</sub> = 5.0V                                                    |     | -5.15 |     | dB    |

| A <sub>V MIN</sub> /<br>A <sub>V MAX</sub>   | Maximum contrast attenuation.           | Maximum gain, V <sub>ABL</sub> = 5.0V                                                    |     | -20.5 |     | dB    |

| A <sub>V 50%</sub> GAIN                      | Gain attenuation @ 50%                  | Maximum contrast, V <sub>ABL</sub> = 5.0V                                                |     | -4.15 |     | dB    |

| A <sub>V MIN GAIN</sub> / A <sub>V MAX</sub> | Maximum gain attenuation                | Maximum contrast, V <sub>ABL</sub> = 5.0V                                                |     | -12   |     | dB    |

| A <sub>V MATCH</sub>                         | Maximum gain match between channels     | Maximum contrast, V <sub>ABL</sub> = 5.0V                                                |     | ±0.6  |     | dB    |

| A <sub>V TRACK</sub>                         | Gain tracking channel to channel        | AC input signal <sup>(8)</sup>                                                           |     | ±0.6  |     | dB    |

| V <sub>ABL HIGH</sub>                        | ABL control range upper limit           | AC input signal <sup>(9)</sup>                                                           |     | 4.5   |     | V     |

| V <sub>ABL LOW</sub>                         | ABL control range lower limit           | AC input signal (9)                                                                      |     | 2.5   |     | V     |

- (1) Datasheet min/max specification limits are specified by design, test, or statistical analysis. The ensured specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

- (2) Typical specifications are specified at +25°C and represent the most likely parametric norm.

- (3) The supply current specified is the quiescent current for V<sub>CC</sub> = 5V and with R<sub>L</sub> = ∞. Load resistors are not required and are not used in the test circuit, therefore all the supply current is used by the pre-amp.

- (4) Linearity Error is the maximum variation in step height of a 16 step staircase input signal waveform with a 0.7 V<sub>P-P</sub> level at the input. All 16 steps equal, with each at least 100 ns in duration.

- (5)  $dt/dV_{CC} = 200*(t_{5.5V}-t_{4.5V})/((t_{5.5V}+t_{4.5V}))$  %/V, where:  $t_{5.5V}$  is the rise or fall time at  $V_{CC} = 5.5V$ , and  $t_{4.5V}$  is the rise or fall time at  $V_{CC} = 4.5V$ .

- (6) Input from signal generator:  $t_r$ ,  $t_f < 1$  ns.

- (7) Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at f<sub>IN</sub> = 10 MHz for V<sub>SEP</sub> 10 MHz.

- (8) AA<sub>V</sub> track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three gain stages. It is the difference in gain change between any two amplifiers with the contrast set to A<sub>V 50%</sub> and measured relative to the A<sub>V MAX</sub> condition. For example, at A<sub>V MAX</sub> the three amplifiers' gains might be 12.1 dB, 11.9 dB, and 11.8 dB and change to 2.2 dB, 1.9 dB and 1.7 dB respectively for contrast set to A<sub>V 50%</sub>. This yields a typical gain change of 10.0 dB with a tracking change of ±0.2 dB.

- (9) The ABL input provides smooth decrease in gain over the operational range of 0 dB to −5 dB: ΔA<sub>ABL</sub> = A<sub>V MAX</sub> − A<sub>V</sub> (V<sub>ABL</sub> = V<sub>ABL MIN GAIN</sub>). Beyond −5 dB the gain characteristics, linearity and pulse response may depart from normal values.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

SNOSAHOD -MARCH 2005-REVISED APRIL 2013

### **Video Signal Electrical Characteristics (continued)**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.70~V_{P-P}$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 10~pF$ , Video Outputs =  $2.4~V_{P-P}^{(1)(2)}$

| Symbol                                 | Parameter                                     | Conditions                                                             | Min | Тур  | Max | Units |

|----------------------------------------|-----------------------------------------------|------------------------------------------------------------------------|-----|------|-----|-------|

| A <sub>V 2.5</sub> /A <sub>V MAX</sub> | ABL Gain Reduction at V <sub>ABL</sub> = 2.5V | AC input signal (9)                                                    |     | -5.8 |     | dB    |

| I <sub>ABL ACTIVE</sub>                | ABL input bias current during ABL.            | AC input signal. V <sub>ABL</sub> = 2.5V <sup>(9)</sup>                |     |      | 10  | μΑ    |

| I <sub>ABL MAX</sub>                   | ABL input current sink capability             | AC input signal (9)                                                    |     | 1.0  |     | mA    |

| A <sub>V ABL TRACK</sub>               | ABL channel to channel gain tracking error.   | Input signal = 0.7 V <sub>P-P</sub> , ABL voltage set to 4.5V and 3.0V |     | 0    | 7.5 | %     |

| R <sub>IP</sub>                        | Minimum input resistance (pins 45, 46, 47)    |                                                                        |     | 20   |     | МΩ    |

#### **OSD Electrical Characteristics**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V^{(1)(2)}$

| Symbol                    | Parameter                                                                                                                            | Conditions                                               | Min | Тур  | Max | Units |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|------|-----|-------|

| DIGITAL MODE              |                                                                                                                                      |                                                          |     | *    |     |       |

| $V_{LOW}$                 | Maximum low input voltage, (OSD and Enable)                                                                                          | Enable: video inputs selected OSD: OSD black displayed   |     |      | 1.0 | V     |

| V <sub>HIGH</sub>         | Minimum high input voltage, (OSD and Enable)                                                                                         | Enable: OSD inputs selected OSD: OSD colors displayed    | 3.0 |      |     | V     |

| V <sub>OSD-11</sub>       | OSD output amplitude                                                                                                                 | OSD Enable = 1, OSD Contrast = 11                        |     | 2.65 |     | V     |

| V <sub>OSD-10</sub>       | OSD output amplitude                                                                                                                 | OSD Enable = 1, OSD Contrast = 10                        |     | 2.35 |     | V     |

| V <sub>OSD-01</sub>       | OSD output amplitude                                                                                                                 | OSD Enable = 1, OSD Contrast = 01                        |     | 2.15 |     | V     |

| V <sub>OSD-00</sub>       | OSD output amplitude                                                                                                                 | OSD Enable = 1, OSD Contrast = 00                        |     | 1.75 |     | V     |

| V <sub>OSD-AUX</sub>      | OSD output amplitude (AUX)                                                                                                           | OSD Enable = 1, OSD[5] = 1                               |     | 3.0  |     | V     |

| ΔV <sub>OSD BLACK</sub>   | Difference between OSD and video black levels  Difference between OSD and video black levels  Same channel, contrast and gain = 0x60 |                                                          | -85 |      | 100 | mV    |

| ΔV <sub>OSD WHITE</sub>   | Output Match between channels                                                                                                        | OSD Contrast = 11, maximum difference between R, G and B |     | 3    |     | %     |

| V <sub>OSD TRACK</sub>    | Output Variation between channels                                                                                                    | OSD contrast varied from max to min                      |     | 3    |     | %     |

| HT <sub>MAX</sub>         | OSD background video maximum level                                                                                                   | OSD[3] = 1, OSD TRANS = 0x7F <sup>(3)</sup>              |     | 100  |     | %     |

| HT <sub>MIN</sub>         | OSD background video minimum level                                                                                                   | $OSD[3] = 1$ , $OSD\ TRANS = 0x00^{(3)}$                 |     | 10   |     | %     |

| ANALOG MODE               |                                                                                                                                      |                                                          |     |      |     |       |

| A <sub>V</sub> ANALOG OSD | Analog gain from pins 41, 42, 43 to the video outputs, with input level 0.7 V <sub>PP</sub>                                          | OSD Enable = 1, Gains at maximum                         |     | 3.75 |     | V/V   |

| <b>BOTH MODES</b>         | <del></del>                                                                                                                          |                                                          |     | ,    |     | •     |

| I <sub>LOW</sub>          | Low input current (OSD and Enable)                                                                                                   | V <sub>IN</sub> = 0V                                     |     | -3.0 |     | μA    |

| I <sub>HIGH</sub>         | High input current (OSD and Enable)                                                                                                  | V <sub>IN</sub> = 5V                                     |     | .001 |     | μA    |

| SEP <sub>10 kHz</sub>     | Crosstalk from video @ 10 kHz                                                                                                        | See <sup>(4)</sup>                                       |     | -70  |     | dB    |

| SEP <sub>10 MHz</sub>     | Crosstalk from video @ 10 MHz                                                                                                        | See <sup>(4)</sup>                                       |     | -50  |     | dB    |

<sup>(1)</sup> Datasheet min/max specification limits are specified by design, test, or statistical analysis. The ensured specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

<sup>(2)</sup> Typical specifications are specified at +25°C and represent the most likely parametric norm.

<sup>(3)</sup> In the transparency mode, the OSD background consists of video with contrast level determined by the Transparency Register. The OSD foreground is unaffected.

<sup>(4)</sup> Video input = 0.7 V<sub>P-P</sub> and the OSD Enable is active with the OSD inputs at black. For each video input, in turn, set the specified video input at the designated frequency and measure the video feedthrough at the video outputs.

### **DAC Output Electrical Characteristics**

Unless otherwise noted:  $T_A = 25$ °C,  $V_{CC} = +5.0$ V,  $V_{IN} = 0.7$ V,  $V_{ABL} = V_{CC}$ ,  $C_L = 10$  pF, Video Outputs = 2.4  $V_{P-P}$ <sup>(1)(2)</sup>. DAC parameters apply to all 3 DACs.

| Symbol                      | Parameter                                         | Conditions                                                               | Min  | Тур | Max  | Units |

|-----------------------------|---------------------------------------------------|--------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>DAC MIN</sub>        | Minimum DAC output voltage                        | Register Value = 0x00                                                    |      | 0.5 |      | V     |

| V <sub>DAC MAX MODE 0</sub> | Maximum DAC output voltage (full scale)           | Register Value = 0xFF,<br>GLOBAL[5] = 0                                  |      | 4.2 |      | V     |

| V <sub>DAC MAX MODE 1</sub> | Maximum DAC output voltage (half scale)           | Register Value = 0xFF,<br>GLOBAL[5] = 1                                  |      | 2.1 |      | V     |

| $\Delta V_{DAC\ TEMP}$      | DAC output voltage variation with temperature     | 0°C < T < 70°C ambient                                                   |      | 0.5 |      | mV/°C |

| $\Delta V_{DAC\ VCC}$       | DAC output voltage variation with V <sub>CC</sub> | 4.75V ≤ V <sub>CC</sub> ≤ 5.25V,<br>DAC register set to mid-range (0x7F) |      | 50  |      | mV    |

| Linearity                   | Linearity of DAC over its range                   |                                                                          |      | 5   |      | %     |

| Monotonicity                | Monotonicity of the DAC excluding dead zones      |                                                                          | -0.5 |     | +0.5 | LSB   |

| I <sub>MAX</sub>            | Maximum DAC output load current                   |                                                                          |      |     | 1.0  | mA    |

<sup>(1)</sup> Datasheet min/max specification limits are specified by design, test, or statistical analysis. The ensured specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

### **Deflection Signal Characteristics**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.7V$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 10 \text{ pF}^{(1)(2)}$

| Symbol                      | Parameter                                                      | Conditions                                                    | Min | Тур  | Max | Units           |

|-----------------------------|----------------------------------------------------------------|---------------------------------------------------------------|-----|------|-----|-----------------|

| f <sub>XTL</sub>            | Ceramic resonator input frequency                              |                                                               |     | 12   |     | MHz             |

| $V_{HFB}$                   | Switching threshold for detecting horizontal flyback on pin 18 |                                                               |     | 2.4  |     | V               |

| t <sub>FW</sub>             | Flyback Width                                                  |                                                               | 1   |      |     | μs              |

| $V_{VFB-DC}$                | DC bias point of VFB input                                     |                                                               |     | 1.25 |     | V               |

| V <sub>VFB-SW</sub>         | Switching threshold for detection                              |                                                               |     | 1.75 |     | V               |

| $V_{X-RAY}$                 | X-Ray Threshold Voltage                                        | Above V <sub>X-RAY</sub> the HDRIVE output is disabled (high) |     | 2.5  | 3.2 | V               |

| V <sub>CCforXRAYRESET</sub> | X-Ray Reset                                                    | V <sub>CC</sub> required to reset X-Ray                       |     | 4    |     | V               |

| $\Delta f_{FR}$             | Free-run frequency tolerance                                   | (ceramic resonator tolerance)                                 |     |      | ±1  | %               |

| f <sub>CR</sub>             | PLL capture range                                              |                                                               |     | ±6   |     | %               |

| t <sub>HDPHASE</sub>        | Horizontal phase control range                                 | All scan frequencies                                          |     | ±25  |     | %T <sub>H</sub> |

| t <sub>PARCOR</sub>         | Maximum parallelogram correction                               | Measured at 31 kHz                                            |     | ±1   |     | μs              |

| t <sub>BOWCOR</sub>         | Maximum pin balance (bow) correction                           | Measured at 31 kHz                                            |     | ±0.5 |     | μs              |

| H <sub>EHT</sub> -          | HEHT phase shift left (R <sub>EHT</sub> = 20k)                 | HEHT[3:0] = 0011b and $V_{20} = 1.5V$                         |     | -2.7 |     | %T <sub>H</sub> |

| H <sub>EHT+</sub>           | HEHT phase shift right (R <sub>EHT</sub> = 20k)                | HEHT[3:0] = 0111b and $V_{20} = 3.5V$                         |     | 2.8  |     | %T <sub>H</sub> |

| $V_{HDOL}$                  | HDRIVE Max low level output                                    | I <sub>OL</sub> = 10 mA                                       |     | 0.7  |     | V               |

| I <sub>HDO</sub>            | HDRIVE Max sink current                                        |                                                               |     |      | 10  | mA              |

| V <sub>HDOH</sub>           | HDRIVE Max high level output voltage                           |                                                               |     | 5    |     | V               |

| δ                           | HDRIVE Duty cycle                                              | During normal use                                             |     | 50   |     | %               |

| t <sub>ON</sub>             | Delay to 50% duty cycle                                        |                                                               |     | 60   |     | lines           |

| t <sub>JITTER</sub>         | Jitter <sup>(3)</sup>                                          | Measured at 31 kHz scan frequency                             |     | 1.8  |     | ns              |

| f <sub>VMIN</sub>           | Minimum vertical lock frequency                                |                                                               |     |      | 50  | Hz              |

| f <sub>VMAX</sub>           | Maximum vertical lock frequency                                |                                                               | 120 |      |     | Hz              |

<sup>(1)</sup> Datasheet min/max specification limits are specified by design, test, or statistical analysis. The ensured specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

Submit Documentation Feedback

<sup>(2)</sup> Typical specifications are specified at +25°C and represent the most likely parametric norm.

<sup>(2)</sup> Typical specifications are specified at +25°C and represent the most likely parametric norm.

<sup>(3)</sup> Jitter is measured at the 31 kHz scan rate by measuring the time difference between the leading edge of HSYNC and the leading edge of the HDRIVE output pulse.

### SNOSAH0D -MARCH 2005-REVISED APRIL 2013

# **Deflection Signal Characteristics (continued)**

Unless otherwise noted: T<sub>A</sub> = 25°C, V<sub>CC</sub> = +5.0V, V<sub>IN</sub> = 0.7V, V<sub>ABL</sub> = V<sub>CC</sub>, C<sub>L</sub> = 10 pF<sup>(1)(2)</sup>

| Symbol                            | Parameter                                        | Conditions                                                                                                       | Min | Тур    | Max  | Units |

|-----------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|--------|------|-------|

| f <sub>VFR</sub>                  | Vertical free run frequency                      |                                                                                                                  |     | 30     |      | Hz    |

| V <sub>MAXRAMPOUT</sub>           | Maximum ramp amplitude                           | VSIZE[7:0] = 0xFF                                                                                                | 1.7 | 2.2    |      | V     |

| V <sub>VMINRAMPOUT</sub>          | Minimum ramp amplitude                           | VSIZE[7:0] = 0x00                                                                                                |     | 1.4    | 1.9  | V     |

| V <sub>RAMPDCOUT</sub>            | Vertical ramp DC reference voltage               |                                                                                                                  |     | 2.5    |      | V     |

| $\Delta V_{RAMP}/\Delta V_{EHT1}$ | Ramp amplitude reduction with V <sub>EHT1</sub>  | VEHT[3:0] varied from 0x0 to 0xF                                                                                 | 0   |        | -4.4 | %/V   |

| R <sub>IN-VEHT1</sub>             | Pin 8 input resistance                           |                                                                                                                  | 1   |        |      | МΩ    |

| $\Delta V_{EW}/\Delta V_{EHT2}$   | Change in EW output level with V <sub>EHT2</sub> | VEHT[7:4] varied from 0x0 to 0xF                                                                                 | 0   |        | 348  | mV/V  |

| R <sub>IN-VEHT2</sub>             | Pin 9 input resistance                           |                                                                                                                  |     | 50     |      | kΩ    |

| k <sub>S</sub>                    | S correction range                               |                                                                                                                  | 0   |        | 10   | %     |

| k <sub>C</sub>                    | C correction range                               |                                                                                                                  | -11 |        | 11   | %     |

| $V_{DF}$                          | Dynamic Focus Amplitude                          | DYN_FOCUS[6:0] = 0x7F                                                                                            |     | 1.1    |      | V     |

| V <sub>EW</sub>                   | Maximum E-W amplitude peak-peak                  | PIN[6:0] = 0x7F                                                                                                  |     | 1.2    |      | V     |

| I <sub>EW</sub>                   | E-W output current                               |                                                                                                                  | -3  |        | 3    | mA    |

| V <sub>EWDCMIN</sub>              | EW output DC at middle of parabola               | HSIZE[6:0] = 0x00                                                                                                |     | 1.4    |      | V     |

| V <sub>EWDCMAX</sub>              | EW output DC at middle of parabola               | HSIZE[6:0] = 0x7F                                                                                                |     | 2.5    |      | V     |

| V <sub>EWTRAP</sub>               | Trapezoid correction parabola tilt               | Beginning and end of parabola shift oppositely and equally. PIN[6:0] = 0x00, T_CORNER[6:0], B_CORNER[6:0] = 0x3F |     | ±0.375 |      | V     |

| V <sub>EWCORNER</sub>             | Corner correction shift at end points            | Top & bottom adjusted independently. PIN [6:0] = 0x00, TRAP[6:0] = 0x3F                                          |     | ±0.375 |      | V     |

| V <sub>EWPIN</sub>                | Pin correction amplitude                         | TRAP[6:0], T_CORNER[6:0],<br>B_CORNER[6:0] = 0x3F                                                                | 0   |        | 1.8  | V     |

### **System Interface Signal Characteristics**

Unless otherwise noted:  $T_A = 25$ °C,  $V_{CC} = +5.0$ V,  $V_{IN} = 0.7$ V,  $V_{ABL} = V_{CC}$ ,  $C_L = 10$  pF, Video Outputs = 2.4  $V_{P-P}$ <sup>(1)(2)</sup>

| Symbol                                               | Parameter                                              | Conditions                                                                                                                    | Min  | Тур  | Max                   | Units |

|------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------|-------|

| V <sub>SPOT</sub>                                    | Spot Killer Voltage                                    | V <sub>CC</sub> Adjusted to Activate <sup>(3)</sup>                                                                           |      | 4.0  |                       | V     |

| $V_{REF}$                                            | V <sub>REF</sub> output voltage (pin 2)                |                                                                                                                               |      | 1.2  |                       | V     |

| V <sub>IL</sub>                                      | Logic low input voltage (SCL, SDA, HSYNC, VSYNC)       |                                                                                                                               | -0.5 |      | 1.5                   | V     |

| $V_{IH}$                                             | Logic high input voltage (SCL, SDA, HSYNC, VSYNC)      |                                                                                                                               | 3.0  |      | V <sub>CC</sub> + 0.5 | V     |

| IL                                                   | Logic low input current (SCL, SDA, HSYNC, VSYNC)       | SDA or SCL, Input Voltage = 0V                                                                                                |      | ±10  |                       | μA    |

| I <sub>H</sub>                                       | Logic high input current (SCL, SDA, HSYNC, VSYNC)      | SDA or SCL, Input Voltage = 5.0V                                                                                              |      | ±10  |                       | μA    |

| V <sub>OL</sub>                                      | Logic low output voltage (SCL, SDA)                    | I <sub>O</sub> = 3 mA                                                                                                         |      | 0.5  |                       | V     |

| I <sub>FB</sub> THRESHOLD                            | I <sub>IN</sub> blank detection threshold (pin 24)     |                                                                                                                               |      | -20  |                       | μA    |

| I <sub>FB IN MAX</sub>                               | Flyback input                                          | Absolute maximum current during flyback                                                                                       |      |      | 5                     | mA    |

| I <sub>FB IN MAX</sub>                               | Peak flyback input current                             | Design value - AC coupled                                                                                                     |      | 1.0  |                       | mA    |

| I <sub>FB OUT MAX</sub>                              | Flyback input current                                  | Absolute maximum during scan                                                                                                  | -500 |      |                       | μA    |

| t <sub>H-BLANK</sub> ON                              | Blanking time delay - on                               | + Zero crossing of I <sub>FB</sub> to 50% of output blanking start. I <sub>FB</sub> = +1.5 mA                                 |      | 50   |                       | ns    |

| t <sub>H-BLANK</sub> OFF                             | Blanking time delay - off                              | - Zero crossing of I <sub>FB</sub> to 50% of output blanking end. I <sub>FB</sub> = −100 μA                                   |      | 50   |                       | ns    |

| V <sub>BLANK MAX</sub>                               | Maximum video blanking level                           | CONTRAST[6:0], RGAIN[6:0],<br>GGAIN[6:0], BGAIN[6:0] = 0x7F,<br>BRIGHTNESS[7:0] = 0x00,<br>OFFSET[3:0] = 0xC, AC input signal | 0    |      | 0.25                  | V     |

| t <sub>PW CLAMP</sub>                                | Minimum clamp pulse width                              | See <sup>(4)</sup>                                                                                                            | 200  |      |                       | ns    |

| V <sub>CLAMP MAX</sub>                               | Maximum low level clamp voltage                        | To ensure low state                                                                                                           |      |      | 1.0                   | V     |

| V <sub>CLAMP MIN</sub>                               | Minimum high level clamp voltage                       | To ensure high state                                                                                                          | 3.0  |      |                       | V     |

| I <sub>CLAMP LOW</sub>                               | Clamp gate low input current                           | V <sub>23</sub> = 0V                                                                                                          |      | -0.4 |                       | μA    |

| I <sub>CLAMP HIGH</sub>                              | Clamp gate high input current                          | V <sub>23</sub> = 5.0V                                                                                                        |      | 0.4  |                       | μA    |

| t <sub>CLAMP-VIDEO</sub>                             | Minimum wait from end of clamp pulse to start of video | Referenced to RGB video inputs                                                                                                | 50   |      |                       | ns    |

| V <sub>HEHT-LOW</sub>                                | Low limit of pin 20 HEHT input                         |                                                                                                                               |      | 1.4  |                       | V     |

| V <sub>HEHT-HIGH</sub>                               | High limit of pin 20 HEHT input                        |                                                                                                                               |      | 3.4  |                       | V     |

| V <sub>VEHT1-LOW</sub> ,<br>V <sub>VEHT2-LOW</sub>   | Low limit of pins 8 and 9 VEHT inputs                  |                                                                                                                               |      | 1    |                       | V     |

| V <sub>VEHT1-HIGH</sub> ,<br>V <sub>VEHT2-HIGH</sub> | High limit of pins 8 and 9 VEHT inputs                 |                                                                                                                               |      | 4    |                       | V     |

<sup>(1)</sup> Datasheet min/max specification limits are specified by design, test, or statistical analysis. The ensured specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

<sup>(2)</sup> Typical specifications are specified at +25°C and represent the most likely parametric norm.

<sup>(3)</sup> Once the spot killer has been activated, the LM1229 remains in the off state until V<sub>CC</sub> is cycled (reduced below 0.5V and then restored to 5V).

<sup>(4)</sup> A minimum pulse width of 200 ns is the specified minimum for a horizontal line of 15 kHz. This limit is ensured by design. If a lower line rate is used then a longer clamp pulse may be required.

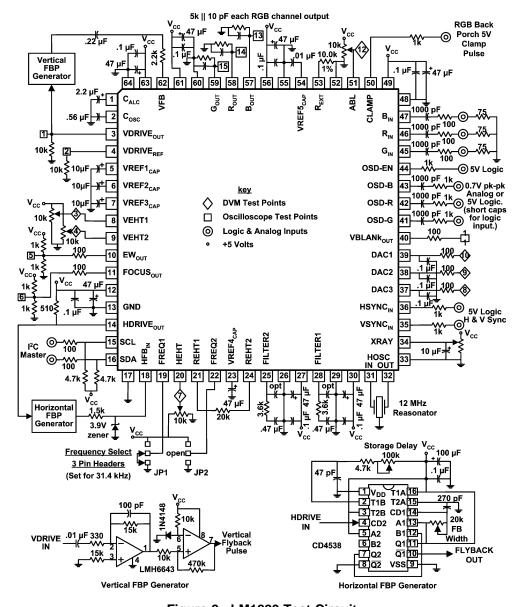

#### LM1229 Test Circuit

The LM1229 RGB test circuit is shown in Figure 2. The video generator should be a clean 75 $\Omega$  source to prevent unwanted reflections from the terminations. The output waveforms should be measured with a 10X, low capacitance probe on an oscilloscope with at least 400 MHz bandwidth. The jumpers JP1 and JP2 determine the free running frequency according to Table 1. The OSD inputs are shown as analog 0.7V peak to peak. If higher level signals are available, suitable attenuation and termination should be used to achieve the proper input level. To prevent overdriving the input pins, the 1000 pF capacitors should be removed (shorted) to test the digital OSD mode. Caution—Do not apply TTL OSD input signals to the LM1229 while it is in the analog OSD mode.

Figure 2. LM1229 Test Circuit

Copyright © 2005-2013, Texas Instruments Incorporated

### **APPLICATION INFORMATION**

### **PIN CONNECTIONS**

| Pin<br>No.              | Pin Name                                       | Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2                     | C <sub>ALC</sub><br>C <sub>OSC</sub>           | C <sub>ALC</sub> 1<br>2.2 μF 2<br>C <sub>OSC</sub> 2<br>.56 μF 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C <sub>ALC</sub> is the feedback loop filter which maintains constant vertical ramp amplitude according to the value set in the vertical height register.  C <sub>OSC</sub> is the capacitor which determines the slope of the vertical ramp.                                                                                                                                               |

| 3 4                     | VDRIVE <sub>OUT</sub><br>VDRIVE <sub>REF</sub> | Vert. Yoke = Vertical Amp VDRIVE OUT YORIVE Amp VDRIVE | These two outputs provide the inputs to a vertical output amplifier which drives the vertical yoke winding. Since the VDRIVE <sub>OUT</sub> amplitude is from 1.5V to 2.5V peak to peak, the gain of the output amplifier must be set with external resistors to match the vertical yoke being used. The VDRIVE <sub>OUT</sub> slope is positive (increasing voltage with time).            |

| 5<br>6<br>7<br>23<br>54 | V <sub>REF</sub> Caps                          | Pin Value<br>5,6,7: 10 µF 5,6,7,<br>23: 47 µF 23,54<br>54: .01 µF VREF<br>Bypass Caps * ESD Protection to pin 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Provides filtering for the internal voltages which set the internal bias currents in conjunction with $R_{EXT}.$ For proper filtering, pins 5, 6 and 7 should be 10 $\mu\text{F},$ pin 23 should be 54 $\mu\text{F}$ and pin 54 should be .01 $\mu\text{F}.$ These capacitors should be placed as close to their pins as possible.                                                          |

| 8                       | VEHT1                                          | ABL 330k VEHT1  120k VEHT1  100k 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | This input pin is used to control the height of the vertical ramp based on changes in the high voltage. A 1V negative change at pin 8 causes a maximum of 5% reduction in the ramp amplitude when the VEHT[3:0] is set to 0xF. If this pin is not used, bit 3 of the SYNCPOL register should be set to 1. The values shown give a 350 mV change at pin 8 from a 2.5V change at the ABL pin. |

| 9                       | VEHT2                                          | ABL 240k VEHT2 2.4V pin 51  .1 µF 220k 220k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This input pin is used to control the level of the E-W parabola based on changes in the high voltage. A 1V negative change at pin 9 causes a maximum of 300 mV increase in the ramp DC level when the VEHT[7:4] is set to 0xF. If this pin is unused, bit 4 of the SYNCPOL register should be set to 1. The values shown give a 350 mV change at pin 9 from a 2.5V change at the ABL pin.   |

| 10                      | EW <sub>OUT</sub>                              | 4.7k  4.7k  4.7k  1k  EW <sub>OUT</sub> 10  4.7k  O.1 µF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EW <sub>OUT</sub> is the output used for control of width, pincushion, trapezoid and top and bottom corners. Its lowest voltage is in the middle of vertical scan. The amplitudes of these functions are register controlled.                                                                                                                                                               |

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

### SNOSAH0D -MARCH 2005-REVISED APRIL 2013

| Pin<br>No. | Pin Name              | Schematic                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|-----------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | FOCUS <sub>OUT</sub>  | FOCUS <sub>OUT</sub> 11                                                                                        | FOCUS <sub>OUT</sub> is used for dynamic focus adjustment. The peak to peak amplitude is register controlled and if it is used for both horizontal and vertical dynamic focus, their amplitudes will be controlled proportionately.                                                                                                                                                                                      |

|            | V <sub>CC</sub> & GND | V <sub>CC</sub> 0<br>12, 27, 30, 49, 56, 61, 63<br>47 µF .1 µF<br>GND = 13, 17, 26, 29, 33, 48, 52, 55, 60, 64 | Power supply and ground pin for all the LM1229. Note the recommended charge storage and high frequency capacitors which should be as close to pins wherever possible.                                                                                                                                                                                                                                                    |

| 14         | HDRIVE <sub>OUT</sub> | V <sub>CC</sub> 0 + 180 510 510 4.7 μF HDRIVE <sub>OUT</sub> 4.7 μF ESD Protection Protection                  | This is the horizontal drive output. When this output is low, the horizontal output transistor is on and a positive edge at pin 14 starts the flyback pulse. The duty cycle slowly increases to 50% when power is applied. The output sink current should not exceed 10 mA.                                                                                                                                              |

| 15         | SCL                   | 4.7k Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vc                                                                    | The I²C compatible clock line. A pull-up resistor of about 4.7 k $\Omega$ should be connected between this pin and V <sub>CC</sub> . A resistor of at least 100 $\Omega$ should be connected in series with the clock line for additional ESD protection.                                                                                                                                                                |

| 16         | SDA                   | 4.7k Data In Data In Data Out                                                                                  | The $I^2C$ compatible data line. A pull-up resistor of about 4.7 k $\Omega$ should be connected between this pin and $V_{CC}$ . A resistor of at least $100\Omega$ should be connected in series with the data line for additional ESD protection.                                                                                                                                                                       |

| 18         | Horizontal<br>Flyback | Horizontal Flyback Pulse R <sub>H</sub> 3.9V zener * ESD Protection                                            | The input is a threshold detector at approximately 2.4V. $R_H$ should be large enough to limit the combined peak current during flyback to a few milliamperes in the zener diode in accordance with the zener power rating. It may be desirable to add a resistor from $V_{CC}$ or GND to pin 18 to offset the switching point up or down by a small amount. Be sure to start with small offsets and work up from there. |

Copyright © 2005–2013, Texas Instruments Incorporated

Submit Documentation Feedback

| Pin<br>No. | Pin Name | Schematic           | Description                                            |

|------------|----------|---------------------|--------------------------------------------------------|

| 19         | FREQ1    |                     | These two pins select the frequency of the horizontal  |

| 22         | FREQ2    | r v <sub>cc</sub> , | PLL. They are tri-state and may be hard wired for a    |

|            |          | │                   | single frequency design or driven by a microcontroller |

for a multiple frequency design. The  $100\Omega$  resistor is To Microcontroller used for ESD and arcing protection when the or Hard Wire connections comes from a long distance away and are recommended even if the pins are hard wired. The input logic states and their corresponding scan frequencies are given in Table 1. \* ESD Protection **HEHT** 20 This pin provides horizontal phase compensation, if needed, for beam current loading. The polarity and magnitude are selectable from the I<sup>2</sup>C bus. See HEHT Table 4, which shows the compensation for R<sub>EHT</sub> = 20k. If this correction is not needed then it can be R<sub>H3</sub> disabled by setting HEHT[3] to 1 and pin 20 can be left REHT1 The R<sub>EHT</sub> resistor determines the gain of the horizontal 21 24 REHT2 phase compensation, HEHT. A smaller resistor increases the compensation and a larger resistor decreases it. If this feature is not used, pins 21 and 24 may be left open. REHT 20k \* ESD Protection FILTER2 25 These are the currently recommended filter values for PLL 2. These components should be kept as close to pins 25 and 26 as possible, and high frequency signals should be routed away from this filter to avoid optional affecting the loop. FILTER1 These are the currently recommended filter values for 28 PLL 1. These components should be kept as close to pins 28 and 29 as possible, and high frequency signals should be routed away from this filter to avoid optional affecting the loop. HOSC2 The oscillator can be a standard 12 MHz ceramic or HOSC1 crystal oscillator. Two suitable manufacturer's part numbers are Murata CST12.0MT and Panasonic PX1200MC-ND. 12 MHz Xtal out 34 **XRAY** This pin provides X-ray sense and shutdown. The input is a rectified horizontal flyback pulse. R<sub>B</sub> is adjusted to cause shutdown at the desired amplitude ESD Protection of the flyback pulse. This provides X-ray protection by turning off the horizontal drive. After the shutdown, the LM1229 will be reset when V<sub>CC</sub> drops below 4V or when the HDRIVE output is disabled and reenabled with bit 5 of the HEHT register. This shutdown function can be disabled by setting bit 6 of the HEHT register to a 1.

| Pin<br>No.     | Pin Name                                           | Schematic                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35<br>36       | HSYNC<br>VSYNC                                     | Sync 1N4148 35 36 1N4148 1N4148 1N4148 1N4148 1N4148 1N4148 1N4148 1N4148               | These are the horizontal and vertical sync inputs to the LM1229. The horizontal sync is required by the horizontal PLL and the horizontal blanking function. The vertical sync is required by the vertical blanking function which includes the programmable vertical blanking output pulse and the RGB vertical blanking. These are both 5V logic levels with thresholds as given in the specifications section. Care must be taken to prevent sync overshoots from reaching the LM1229.                             |

| 37<br>38<br>39 | DAC 3 Output<br>DAC 2 Output<br>DAC 1 Output       | DAC Outputs 37 100 100 100 100 100 100 100 100 100 10                                   | These are the DAC outputs for the RGB cathode cutoff adjustments. The DAC output levels are set through the I <sup>2</sup> C compatible bus. These can be set for 4.2V or 2.1V full scale to match the various TI bias ICs.  TI's CRT arcing tests and experience shows that the best output termination for the DAC outputs is a 0.1 µF capacitor to ground at the IC terminals and a series 1k resistor close to the load.                                                                                          |

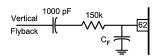

| 40             | VBLANK <sub>OUT</sub>                              | VBLANK <sub>OUT</sub> 1k  * ESD Protection                                              | This is a positive going logic pulse which can be used for vertical blanking on G1. It can be an input to the LM2485 where it is amplified to either 20V or 40V negative going peak to peak, depending on an option pin. The pulse starts when an input is received on the Vertical Flyback Input on pin 62 and lasts for the number of scan lines loaded in the VBLANK register, 0x51[7:0].                                                                                                                          |

| 41<br>42<br>43 | Green OSD<br>Red OSD<br>Blue OSD<br>(Digital Mode) | OSD 100 41 42 43 * ESD Protection                                                       | These inputs can be used for either analog or digital inputs. In the digital mode these inputs accept either TTL or CMOS input levels. Each color is either fully on (logic high) or fully off (logic low). Unused pins should be connected to ground with a 47k resistor. Texas Instruments does not recommend mixing analog and digital inputs in the same application.                                                                                                                                             |

| 41<br>42<br>43 | Green OSD<br>Red OSD<br>Blue OSD<br>(Analog Mode)  | V <sub>CC</sub> DC Restoration  V <sub>IN</sub> 100  C <sub>IN</sub> 43  ESD Protection | In the analog OSD mode, the inputs should be AC coupled through a 1000 pF capacitor, and the gain is about 3.5, so that a peak to peak input of 0.7V results in a 2.45V peak to peak signal at the RGB outputs when the OSD contrast is maximum. Signal input amplitudes larger than 0.7V are not recommended. The external ESD diodes are recommended if the input OSD video is generated some distance away from the LM1229. The 75 $\Omega$ termination may not be needed if the signal amplitude is already 0.7V. |

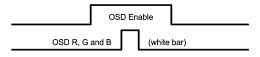

| 44             | OSD Enable                                         | OSD 100 Enable  * ESD Protection                                                        | This input accepts either TTL or CMOS input levels. When this input is a "0", only video is displayed. When it is a "1", the OSD from pins 1, 2 and 3 is displayed. If bit 3 of the OSD register (0x0B) is a "1" then the background of the OSD (when the Enable is a "1" and the OSD inputs are "0") will be video attenuated by the OSD_TRANS register (0x0A). If this input is unused, connect it to ground through a 47k resistor.                                                                                |

| Pin<br>No.     | Pin Name                                        | Schematic                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |