# LM22675 1A SIMPLE SWITCHER®, Step-Down Voltage Regulator with Precision Enable

#### **General Description**

www

The LM22675 series of regulators are monolithic integrated circuits which provide all of the active functions for a stepdown (buck) switching regulator capable of driving up to 1A loads with excellent line and load regulation characteristics. High efficiency (>90%) is obtained through the use of a low ON-resistance N-channel MOSFET. The series consists of a fixed 5V output and an adjustable version.

The SIMPLE SWITCHER® concept provides for an easy to use complete design using a minimum number of external components and National's WEBENCH® design tool. National's WEBENCH® tool includes features such as external component calculation, electrical simulation, thermal simulation, and Build-It boards for easy design-in. The switching clock frequency is provided by an internal fixed frequency oscillator which operates at 500 kHz. The LM22675 series also has built in thermal shutdown, current limiting and an enable control input that can power down the regulator to a low 25  $\mu$ A quiescent current standby condition.

#### **Features**

-

- Wide input voltage range: 4.5V to 42V

- Internally compensated voltage mode control

- Stable with low ESR ceramic capacitors

- 200 mΩ N-channel MOSFET

- Output voltage options: -ADJ (outputs as low as 1.285V) -5.0 (output fixed to 5V)

- ±1.5% feedback reference accuracy

- Switching frequency of 500 kHz

- -40°C to 125°C operating junction temperature range

- Precision enable pin

- Integrated boot diode

- Integrated soft-start

- Fully WEBENCH<sup>®</sup> enabled

- Step-down and inverting buck-boost applications

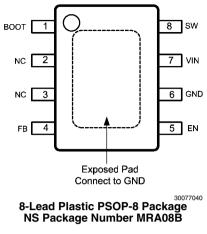

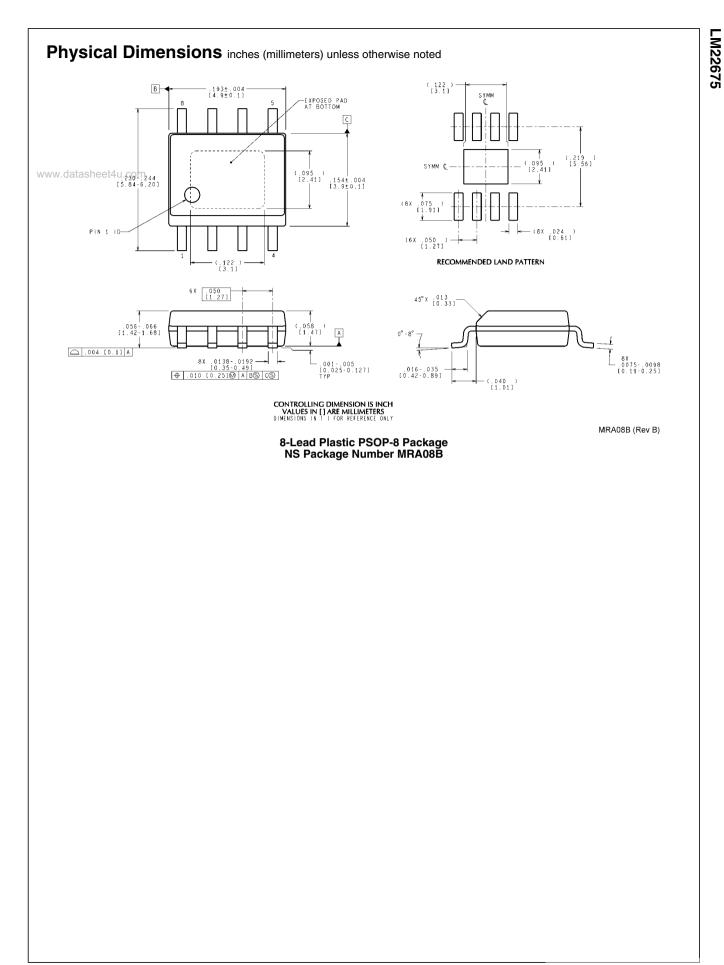

#### Package

PSOP-8 (Exposed Pad)

#### **Applications**

- Industrial Control

- Telecom and Datacom Systems

- Embedded Systems

- Automotive Telematics and Body Electronics

- Conversions from Standard 24V, 12V and 5V Input Rails

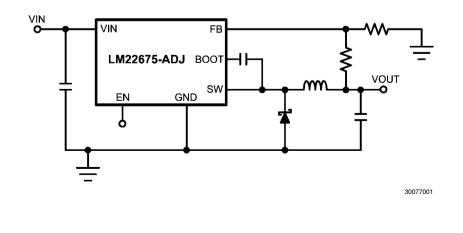

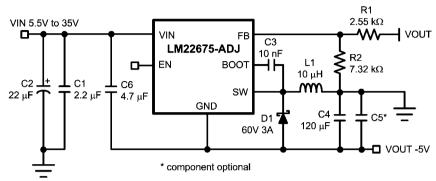

### **Simplified Application Schematic**

LM22675

www.datasheet4u.com

## **Connection Diagram**

## **Ordering Information**

| Output Voltage | Order Number   | Package Type       | NSC Package Drawing    | Supplied As                 |

|----------------|----------------|--------------------|------------------------|-----------------------------|

| ADJ            | LM22675MR-ADJ  | PSOP-8 Exposed Pad |                        | 95 Units in Rails           |

| ADJ            | LM22675MRE-ADJ |                    |                        | 250 Units in Tape and Reel  |

| ADJ            | LM22675MRX-ADJ |                    | P-8 Exposed Pad MRA08B | 2500 Units in Tape and Reel |

| 5.0            | LM22675MR-5.0  |                    |                        | 95 Units in Rails           |

| 5.0            | LM22675MRE-5.0 |                    |                        | 250 Units in Tape and Reel  |

| 5.0            | LM22675MRX-5.0 |                    |                        | 2500 Units in Tape and Reel |

## **Pin Descriptions**

| Pins | Name | Description          | Application Information                                                                     |  |

|------|------|----------------------|---------------------------------------------------------------------------------------------|--|

| 1    | BOOT | Bootstrap input      | Provides the gate voltage for the high side NFET.                                           |  |

| 2, 3 | NC   | Not Connected        | Pins are not electrically connected inside the chip. Pins do function as thermal conductor. |  |

| 4    | FB   | Feedback pin         | Inverting input to the internal voltage error amplifier.                                    |  |

| 5    | EN   | Precision enable pin | When pulled low regulator turns off.                                                        |  |

| 6    | GND  | System ground        | Provide good capacitive decoupling between VIN and this pin                                 |  |

| 7    | VIN  | Source input voltage | Input to the regulator. Operates from 4.5V to 42V.                                          |  |

| 8    | SW   | Switch pin           | Attaches to the switch node                                                                 |  |

| ~ |

|---|

|   |

| N |

| N |

| 6 |

| ~ |

| G |

219°C

240°C

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Distributors for availability and                           |                                              | Wave (4 sec.)                                                        | 260°C                          |

|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|--------------------------------|

| VIN to GND<br>EN Pin Voltage<br>SW to GND (Note 2)          | 43V<br>-0.5V to 6V<br>-5V to V <sub>IN</sub> | ESD Rating (Note 3)<br>Human Body Model<br>Storage Temperature Range | ±2 kV<br>-65°C to +150°C       |

| BOOT Pin Voltage                                            | V <sub>SW</sub> + 7V<br>-0.5V to 7V          | Operating Ratings (N                                                 | ote 1)                         |

| FB Pin Voltage<br>Power Dissipation<br>Junction Temperature | Internally Limited<br>150°C                  | Supply Voltage (V <sub>IN</sub> )<br>Junction Temperature Range      | 4.5V to 42V<br>-40°C to +125°C |

Soldering Information Vapor Phase (75 sec.)

Infrared (10 sec.)

**Electrical Characteristics** Limits in standard type are for  $T_J = 25^{\circ}C$  only; limits in **boldface type** apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_A = T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise specified:  $V_{IN} = 12V$ .

| Symbol              | Parameter                     | Conditions                                                      | Min<br>(Note 5)     | Typ<br>(Note 4) | Max<br>(Note 5)     | Units |

|---------------------|-------------------------------|-----------------------------------------------------------------|---------------------|-----------------|---------------------|-------|

| M22675-5.0          | )                             | 1                                                               |                     | , ,             |                     |       |

| V <sub>FB</sub>     | Feedback Voltage              | V <sub>IN</sub> = 8V to 42V                                     | 4.925/ <b>4.9</b>   | 5.0             | 5.075/ <b>5.1</b>   | V     |

| M22675-AD           | Ĵ                             | •                                                               |                     |                 |                     |       |

| $V_{FB}$            | Feedback Voltage              | V <sub>IN</sub> = 4.7V to 42V                                   | 1.266/ <b>1.259</b> | 1.285           | 1.304/ <b>1.311</b> | V     |

| All Output V        | oltage Versions               | •                                                               |                     |                 |                     |       |

| Ι <sub>Q</sub>      | Quiescent Current             | V <sub>FB</sub> = 5V                                            |                     | 3.4             | 6                   | mA    |

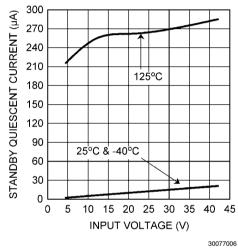

| I <sub>STDBY</sub>  | Standby Quiescent Current     | EN Pin = 0V                                                     |                     | 25              | 40                  | μA    |

| I <sub>CL</sub>     | Current Limit                 |                                                                 | 1.3/ <b>1.2</b>     | 1.5             | 1.7/ <b>1.8</b>     | Α     |

| Ι                   | Output Leakage Current        | $V_{IN} = 42V$ , EN Pin = 0V, $V_{SW} = 0V$                     |                     | 0.2             | 2                   | μA    |

|                     |                               | $V_{SW} = -1V$                                                  |                     | 0.1             | 3                   | μA    |

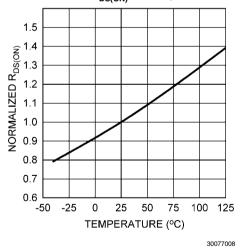

| R <sub>DS(ON)</sub> | Switch On-Resistance          |                                                                 |                     | 0.2             | 0.24/ <b>0.32</b>   | Ω     |

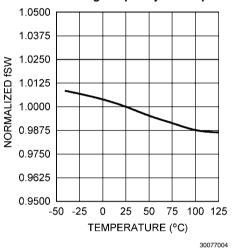

| f <sub>O</sub>      | Oscillator Frequency          |                                                                 | 400                 | 500             | 600                 | kHz   |

| TOFFMIN             | Minimum Off-time              |                                                                 |                     | 300             |                     | ns    |

| T <sub>ONMIN</sub>  | Minimum On-time               |                                                                 |                     | 100             |                     | ns    |

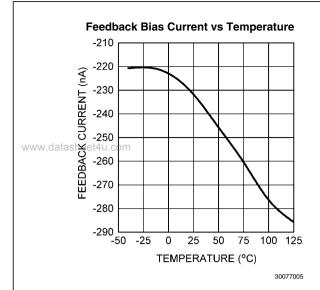

| I <sub>BIAS</sub>   | Feedback Bias Current         | V <sub>FB</sub> = 1.3V (ADJ Version Only)                       |                     | 230             |                     | nA    |

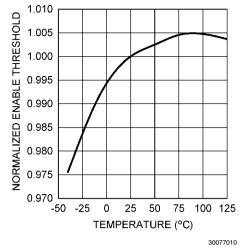

| V <sub>EN</sub>     | Enable Threshold Voltage      |                                                                 | 1.3                 | 1.6             | 1.9                 | V     |

| I <sub>EN</sub>     | Enable Input Current          | EN Input = 0V                                                   |                     | 6               |                     | μA    |

| T <sub>SD</sub>     | Thermal Shutdown<br>Threshold |                                                                 |                     | 150             |                     | °C    |

| $\theta_{JA}$       | Thermal Resistance            | MR package, Junction to ambient temperature resistance (Note 6) |                     | 60              |                     | °C/W  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the recommended Operating Ratings is not implied. The recommended Operating Ratings indicate conditions at which the device is functional and should not be operated beyond such conditions.

Note 2: The absolute maximum specification of the 'SW to GND' applies to DC voltage. An extended negative voltage limit of -10V applies to a pulse of up to 50 ns.

Note 3: ESD was applied using the human body model, a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin.

Note 4: Typical values represent most likely parametric norms at the conditions specified and are not guaranteed.

Note 5: Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

WWW.datash Note 6 The value of 01a for the PSOP-8 exposed pad (MR) package of 60°C/W is valid if package is mounted to 1 square inch of copper. The 01a value can range from 42 to 115°C/W depending on the amount of PCB copper dedicated to heat transfer.

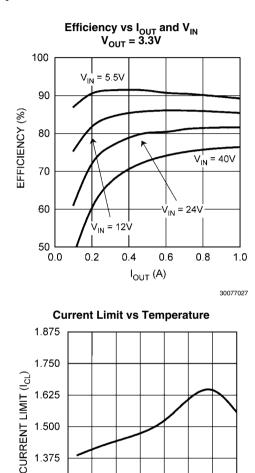

Typical Performance Characteristics Unless otherwise specified the following conditions apply: Vin =

12V, T<sub>.1</sub> = 25°C.

#### Normalized R<sub>DS(ON)</sub> vs Temperature

1.500

1.375

1.250

1.125

-50 -25 0 25 50 75 100 125

30077003

TEMPERATURE (°C)

Standby Quiescent Current vs Input Voltage

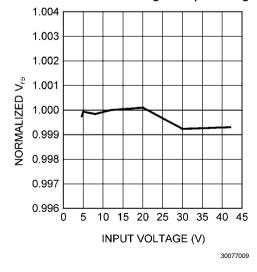

Normalized Feedback Voltage vs Input Voltage

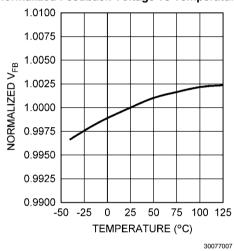

Normalized Feedback Voltage vs Temperature

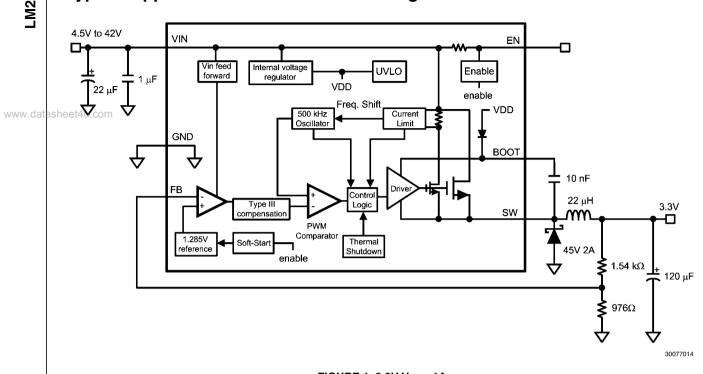

## **Typical Application Circuit and Block Diagram**

FIGURE 1. 3.3V V<sub>OUT</sub>, 1A

### **Detailed Operating Description**

The LM22675 switching regulator features all of the functions necessary to implement an efficient high voltage buck regulator using a minimum of external components. This easy to use regulator integrates a 42V N-Channel switch with an output current capability of 1A. The regulator control method is based on voltage mode control with input voltage feed forward. The loop compensation is integrated into the LM22675 so that no external components need to be se-

lected or utilized. Voltage mode control offers short minimum on-times allowing short duty-cycles necessary in high input voltage applications. The operating frequency is fixed at 500kHz to allow for small external components while avoiding excessive switching losses. The output voltage can be set as low as 1.285V with the -ADJ device. Fault protection features include current limiting, thermal shutdown and remote shutdown capability. The device is available in the PSOP-8 package featuring an exposed pad to aid thermal dissipation.

The functional block diagram with typical application of the LM22675 are shown in *Figure 1*.

The internal compensation of the -ADJ option of the LM22675 is optimized for output voltages up to 5V. If an output voltage of 5V or higher is needed, the -5.0 fixed output voltage option with an additional external resistive feedback voltage divider may also be used.

## **Precision Enable**

The precision enable pin (EN) can be used to shut down the power supply. Connecting this pin to ground or to a voltage less than typical 1.6V will completely turn off the regulator. The current drain from the input supply when off is typically 25  $\mu$ A with 12V input voltage. The power consumed during this off state is mostly defined by an internal 2 M $\Omega$  resistor to VIN. The enable pin has an internal pull-up current source of approximately 6  $\mu$ A. When driving the enable pin, the high voltage level for the on condition should not exceed the 6V absolute maximum limit. When enable control is not required, the EN pin should be left floating. The precision feature enables simple sequencing of multiple power supplies with a resistor divider from another power supply.

# Maximum Duty-Cycle / Dropout Voltage

The typical maximum duty-cycle is 85% at 500 kHz switching frequency. This corresponds to a typical minimum off-time of 300 ns. This forced off-time is important to provide enough time for the Cboot capacitor to charge during each cycle. The lowest input voltage required to maintain operation is:

$$V_{IN} = \frac{V_{OUT} + V_D}{1 - (T_{OFFMIN} \times F)} - V_D + V_Q$$

Where  $V_D$  is the forward voltage drop across the re-circulating Schottky diode and  $V_Q$  is the voltage drop across the internal power N-FET of the LM22675. The  $R_{DS(ON)}$  of the FET is specified in the electrical characteristics section of this datasheet to calculate  $V_Q$  according to the FET current. F is the switching frequency.

## Minimum Duty-Cycle

Besides a minimum off-time, there is also a minimum on-time which will take effect when the output voltage is adjusted very low and the input voltage is very high. Should the operation require a shorter minimum on-time than the typical 100 ns, individual switching pulses will be skipped.

$$D = \frac{V_{OUT}}{V_{IN}}$$

where D is the duty-cycle.

## **Current Limit**

When the power switch turns on, the slight capacitance loading of the Schottky diode, D1, causes a leading-edge current spike with an extended ringing period. This spike can cause the current limit comparator to trip prematurely. A leading edge blanking time ( $T_{BLK}$ ) of 110 ns (typical) is used to avoid sampling the spike.

When the switch current reaches the current limit threshold, the switch is immediately turned off and the internal switching frequency is reduced. This extends the off time of the switch to prevent a steady state high current condition. As the switch current falls below the current limit threshold, the switch current will attempt to turn on. If a load fault continues, the switch will again exceed the threshold and turn off. This will result in a low duty-cycle pulsing of the power switch to minimize the overall fault condition power dissipation.

The switching frequency will reduce (fold back) if the overload condition causes the output voltage to be 72.4% (typical) of the adjusted output voltage.

The current limit will only protect the inductor from a runaway condition if the LM22675 is operating in its safe operating area. A runaway condition of the inductor is potentially catastrophic to the application. For every design, the safe operating area needs to be calculated. Factors in determining the safe operating area are the switching frequency, input voltage, output voltage, minimum on-time and feedback voltage during an over current condition.

As a first pass check, if the following equation holds true, a given design is considered in a safe operating area and the current limit will protect the circuit:

If the equation above does not hold true, the following secondary equation will need to hold true to be in safe operating area:

$$(V_{IN} - V_{OUT}) \ge T_{BLK} < (V_{OUT} + V_D) \ge \left(\frac{1}{F}\right) - T_{BLK}$$

If both equations do not hold true, a particular design will not have an effective current limit function which might damage the circuit during startup, over current conditions, or steady state over current and short circuit condition. Oftentimes a reduction of the maximum input voltage will bring a design into the safe operating area.

#### Soft-Start

The soft-start feature allows the regulator to gradually reach the initial steady state operating point, thus reducing start-up stresses and surges. The soft-start is fixed to 500 µs (typical) start-up time and cannot be modified.

### **Boot Pin**

The LM22675 integrates an N-Channel FET switch and associated floating high voltage level shift / gate driver. This gate driver circuit works in conjunction with an internal diode and an external bootstrap capacitor. A 0.01  $\mu$ F ceramic capacitor connected with short traces between the BOOT pin and the SW pin is recommended to effectively drive the internal FET switch. During the off-time of the switch, the SW voltage is approximately -0.5V and the external bootstrap capacitor is charged from the internal supply through the internal bootstrap diode. When operating with a high PWM duty-cycle, the buck switch will be forced off each cycle to ensure that the bootstrap capacitor is recharged. See the maximum duty-cy-

Thermal Protection

cle section for more details.

Internal Thermal Shutdown circuitry protects the LM22675 in the event the maximum junction temperature is exceeded. When activated, typically at 150°C, the regulator is forced into a low power reset state. There is a typical hysteresis of 15 degrees.

## **Internal Compensation**

The LM22675 has internal compensation designed for a stable loop with a wide range of external power stage components.

Insuring stability of a design with a specific power stage (inductor and output capacitor) can be tricky. The LM22675 stability can be verified over varying loads and input and output voltages using WEBENCH® Designer online circuit simulation tool at www.national.com. A quick start spreadsheet can also be downloaded from the online product folder.

The internal compensation of the -ADJ option of the LM22675 is optimized for output voltages below 5V. If an output voltage of 5V or higher is needed, the -5.0 option with an additional external resistor divider may also be used.

The typical location of the internal compensation poles and zeros as well as the DC gain is given in *Table 1*. The LM22675 has internal type III compensation allowing for the use of most output capacitors including ceramics.

This information can be used to calculate the transfer function from the FB pin to the internal compensation node (input to the PWM comparator in the block diagram).

| Corners | Frequency |  |  |  |

|---------|-----------|--|--|--|

| Pole 1  | 150 kHz   |  |  |  |

| Pole 2  | 250 kHz   |  |  |  |

| Pole 3  | 100 Hz    |  |  |  |

| Zero 1  | 1.5 kHz   |  |  |  |

| Zero 2  | 15 kHz    |  |  |  |

| DC gain | 37.5 dB   |  |  |  |

TABLE 1.

For the power stage transfer function the standard voltage mode formulas for the double pole and the ESR zero apply:

$$f_{DP} = \frac{1}{2\pi \sqrt{L \times C_{OUT}}}$$

$$f_{ESR} = \frac{1}{2\pi \times C_{OUT} \times ESR}$$

The peak ramp level of the oscillator signal feeding into the PWM comparator is  $V_{\rm IN}/10$  which equals a gain of 20dB of this modulator stage of the IC. The -5.0 fixed output voltage option has twice the gain of the compensation transfer function compared to the -ADJ option which is 43.5dB instead of 37.5dB.

Generally, calculation as well as simulation can only aid in selecting good power stage components. A good design practice is to test for stability with load transient tests or loop measurement tests. Application note AN-1889 shows how to easily perform a loop transfer function measurement with only an oscilloscope and a function generator.

## **Application Information**

#### EXTERNAL COMPONENTS

The following design procedures can be used to design a nonsynchronous buck converter with the LM22675.

#### Inductor

The inductor value is determined based on the load current, ripple current, and the minimum and maximum input voltage. To keep the application in continuous current conduction mode (CCM), the maximum ripple current,  $I_{RIPPLE}$ , should be less than twice the minimum load current.

The general rule of keeping the inductor current peak-to-peak ripple around 30% of the nominal output current is a good compromise between excessive output voltage ripple and excessive component size and cost. Using this value of ripple current, the value of inductor, L, is calculated using the following formula:

$$L = \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{I_{RIPPLE} \times F \times V_{IN(MAX)}}$$

where F is the switching frequency which is 500 kHz (typical). This procedure provides a guide to select the value of the inductor L. The nearest standard value will then be used in the circuit.

Increasing the inductance will generally slow down the transient response but reduce the output voltage ripple amplitude. Reducing the inductance will generally improve the transient response but increase the output voltage ripple.

The inductor must be rated for the peak current,  $I_{PK_+}$ , to prevent saturation. During normal loading conditions, the peak current occurs at maximum load current plus maximum ripple. Under an overload condition as well as during load transients, the peak current is limited to 1.5A typical (1.8A maximum). This requires that the inductor be selected such that it can run at the maximum current limit and not only the steady state current.

Depending on inductor manufacturer, the saturation rating is defined as the current necessary for the inductance to reduce by 30% at 20°C. In typical designs the inductor will run at higher temperatures. If the inductor is not rated for enough current, it might saturate and due to the propagation delay of the current limit circuitry, the power supply may get damaged.

#### Input Capacitor

Good quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the switch current during on-time. When the switch turns on, the current into the VIN pin steps to the peak value, then drops to zero at turnoff. The average current into VIN during switch on-time is the load current. The input capacitance should be selected for

www.datas

RMS current,  $I_{RMS}$ , and minimum ripple voltage. A good approximation for the required ripple current rating necessary is  $I_{RMS} > I_{OUT} / 2$ .

Quality ceramic capacitors with a low ESR should be selected for the input filter. To allow for capacitor tolerances and voltage effects, multiple capacitors may be used in parallel. If step input voltage transients are expected near the maximum rating of the LM22675, a careful evaluation of ringing and possible voltage spikes at the VIN pin should be completed. An wadditional damping network or input voltage clamp may be required in these cases.

Usually putting a higher ESR electrolytic input capacitor in parallel to the low ESR bypass capacitor will help to reduce excessive voltages during a line transient and will also move the resonance frequency of the input filter away from the regulator bandwidth.

#### **Output Capacitor**

The output capacitor can limit the output ripple voltage and provide a source of charge for transient loading conditions. Multiple capacitors can be placed in parallel. Very low ESR capacitors such as ceramic capacitors reduce the output ripple voltage and noise spikes, while larger higher ESR capacitors in parallel provide large bulk capacitance for transient loading conditions. An approximation for the output voltage ripple is:

$$\Delta V_{OUT} = \Delta I_{L} \times \left( \text{ESR} + \left( \frac{1}{8 \times F \times C_{OUT}} \right) \right)$$

where  $\Delta I_1$  is the inductor ripple current.

#### **Cboot Capacitor**

The bootstrap capacitor between the BOOT pin and the SW pin supplies the gate current to turn on the N-channel MOS-FET. The recommended value of this capacitor is 10 nF and should be a good quality, low ESR ceramic capacitor.

It is possible to put a small resistor in series with the Cboot capacitor to slow down the turn-on transition time of the internal N-channel MOSFET. Resistors in the range of  $10\Omega$  to  $50\Omega$  can slow down the transition time. This can reduce EMI of a switched mode power supply circuit. Using such a series resistor is not recommended for every design since it will increase the switching losses of the application and makes thermal considerations more challenging.

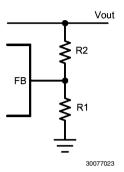

#### **Resistor Divider**

For the -5.0 option no resistor divider is required for 5V output voltage. The output voltage should be directly connected to the FB pin. Output voltages above 5V can use the -5.0 option with a resistor divider as an alternative to the -ADJ option. This may offer improved loop bandwidth in some applications. See the Internal Compensation section for more details.

For the -ADJ option no resistor divider is required for 1.285V output voltage. The output voltage should be directly connected to the FB pin. Other output voltages can use the -ADJ option with a resistor divider.

The resistor values can be determined by the following equations:

-ADJ option:

$$R1 = \frac{R2}{\frac{V_{OUT}}{V_{FB}} - 1}$$

-5.0 option:

R1 =

$$\frac{R2 \times V_{FB}}{(R2 \times 500 \ \mu A) + V_{OUT} - V_{FB}}$$

. .

Where  $V_{FB}$  = 1.285V typical for the -ADJ option and 5V for the -5.0 option

**FIGURE 2. Resistive Feedback Divider**

A maximum value of 10 k $\Omega$  is recommended for the sum of R1 and R2 to keep high output voltage accuracy for the –ADJ option. A maximum of 2 k $\Omega$  is recommended for the -5.0 output voltage option. For the 5V fixed output voltage option, the total internal divider resistance is typically 9.93 k $\Omega$ .

At loads less than 5 mA, the boot capacitor will not hold enough charge to power the internal high side driver. The output voltage may droop until the boot capacitor is recharged. Selecting a total feedback resistance to be below 3 k $\Omega$  will provide some minimal load and can keep the output voltage from collapsing in such low load conditions.

#### Catch Diode

A Schottky type re-circulating diode is required for all LM22675 applications. Ultra-fast diodes which are not Schottky diodes are not recommended and may result in damage to the IC due to reverse recovery current transients. The near ideal reverse recovery characteristics and low forward voltage drop of Schottky diodes are particularly important diode characteristics for high input voltage and low output voltage applications common to the LM22675. The reverse recovery characteristic determines how long the current surge lasts each cycle when the N-channel MOSFET is turned on. The reverse recovery characteristics of Schottky diodes minimizes the peak instantaneous power in the switch occurring during turn-on for each cycle. The resulting switching losses are significantly reduced when using a Schottky diode. The reverse breakdown rating should be selected for the maximum V<sub>IN</sub>, plus some safety margin. A rule of thumb is to select a diode with the reverse voltage rating of 1.3 times the maximum input voltage.

The forward voltage drop has a significant impact on the conversion efficiency, especially for applications with a low output voltage. 'Rated' current for diodes varies widely from various manufacturers. The worst case is to assume a short circuit load condition. In this case the diode will carry the output current almost continuously. For the LM22675 this current can be as high as 1.5A (typical). Assuming a worst case 1V drop across the diode, the maximum diode power dissipation can be as high as 1.5W.

www.datas

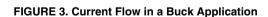

#### **Circuit Board Layout**

Board layout is critical for switching power supplies. First, the ground plane area must be sufficient for thermal dissipation purposes. Second, appropriate guidelines must be followed to reduce the effects of switching noise. Switch mode converters are very fast switching devices. In such devices, the rapid increase of input current combined with the parasitic trace inductance generates unwanted L di/dt noise spikes. The magnitude of this noise tends to increase as the output

current increases. This parasitic spike noise may turn into electromagnetic interference (EMI) and can also cause problems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise.

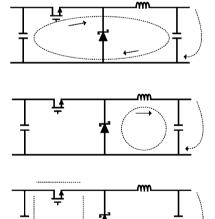

The most important layout rule is to keep the AC current loops as small as possible. *Figure 3* shows the current flow of a buck converter. The top schematic shows a dotted line which represents the current flow during the FET switch on-state. The middle schematic shows the current flow during the FET switch off-state.

The bottom schematic shows the currents referred to as AC currents. These AC currents are the most critical since current is changing in very short time periods. The dotted lines of the bottom schematic are the traces to keep as short as possible. This will also yield a small loop area reducing the loop inductance. To avoid functional problems due to layout, review the PCB layout example. Best results are achieved if the placement of the LM22675, the bypass capacitor, the Schottky diode and the inductor are placed as shown in the example. It is also recommended to use 2oz copper boards or thicker to help thermal dissipation and to reduce the parasitic inductances of board traces.

30077024

## **Thermal Considerations**

The two highest power dissipating components are the recirculating diode and the LM22675 regulator IC. The easiest method to determine the power dissipation within the LM22675 is to measure the total conversion losses (Pin – Pout) then subtract the power losses in the Schottky diode and output inductor. An approximation for the Schottky diode loss is:

$$P = (1 - D) \times I_{OUT} \times V_D$$

An approximation for the output inductor power is:

$$\mathsf{P} = \mathsf{I}_{\mathsf{OUT}}^2 \mathsf{x} \mathsf{R} \mathsf{x} \mathsf{1.1},$$

where R is the DC resistance of the inductor and the 1.1 factor is an approximation for the AC losses. The regulator has an exposed thermal pad to aid power dissipation. Adding several vias under the device to the ground plane will greatly reduce the regulator junction temperature. Selecting a diode with an exposed pad will aid the power dissipation of the diode. The most significant variables that affect the power dissipated by the LM22675 are the output current, input voltage and operating frequency. The power dissipated while operating near the maximum output current and maximum input voltage can be appreciable. The junction-to-ambient thermal resistance of the LM22675 will vary with the application. The most significant variables are the area of copper in the PC board, the number of vias under the IC exposed pad and the amount of forced air cooling provided. The integrity of the solder connection from the IC exposed pad to the PC board is critical. Excessive voids will greatly diminish the thermal dissipation capacity. The junction-to-ambient thermal resistance of the LM22675 PSOP-8 package is specified in the electrical characteristics table under the applicable conditions.

30077041

LM22675

# Schematic for Buck/Boost (Inverting) Application

See AN-1888 for more information on the inverting (buckboost) application generating a negative output voltage from a positive input voltage.

www.datasheet4u.com

30077026

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com