LM5155, LM51551

SNVSB75B - DECEMBER 2018 - REVISED JANUARY 2020

# LM5155x 2.2-MHz Wide Input Nonsynchronous Boost, SEPIC, Flyback Controller

#### **Features**

- Functional safety capable

- Documentation available to aid functional safety system design

- Wide Input Operating Range for Battery **Applications**

- 3.5-V to 45-V Operating Range

- 2.97-V to 16-V When BIAS = VCC

- Minimum Boost Supply Voltage 1.5 V When BIAS ≥ 3.5 V

- Input Transient Protection up to 50 V

- Minimized Battery Drain

- Low Shutdown Current ( $I_O \le 2.6 \mu A$ )

- Low Operating Current (I<sub>O</sub> ≤ 480 µA)

- Small Solution Size and Low Cost

- Maximum Switching Frequency of 2.2 MHz

- 12-Pin WSON Package (3 mm x 2 mm)

- Integrated Error Amplifier Allows Primary-Side Regulation Without Optocoupler (Flyback)

- Minimized Undershoot During Cranking (Startstop Application)

- Higher Efficiency With Low-Power Dissipation

- 100-mV ±7% Low Current Limit Threshold

- Strong 1.5-A Peak Standard MOSFET Driver

- Supports External VCC Supply

- Avoid AM Band Interference and Crosstalk

- Optional Clock Synchronization

- Dynamically Programmable Switching Frequency from 100 kHz to 2.2 MHz

- Integrated Protection Features

- Constant Peak Current Limiting Over Input Voltage

- Optional Hiccup Mode Short-Circuit Protection (see the *Device Comparison Table*)

- Programmable Line UVLO

- **OVP Protection**

- Thermal Shutdown

- Accurate ±1% Accuracy Feedback Reference

- Programmable Extra Slope Compensation

- Adjustable Soft Start

- **PGOOD Indicator**

- Create a Custom Design Using the LM5155x With the WEBENCH® Power Designer

# 2 Applications

- Multiple-Output Flyback Without Optocoupler

- **LED Bias Supply**

- Wide Input Boost, SEPIC, Flyback Power Module

- Portable Speaker Application

- Battery-Powered Boost, SEPIC, Flyback

# 3 Description

The LM5155x ( LM5155 and LM51551 ) device is a wide input range, non-synchronous boost controller that uses peak current mode control. The device can be used in boost, SEPIC, and flyback topologies.

The LM5155x device can start up from a 1-cell battery with a minimum of 2.97 V if the BIAS pin is connected to the VCC pin. It can operate with the input supply voltage as low as 1.5 V if the BIAS pin is greater than 3.5 V.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LM5155x     | WSON (12) | 3.00 mm × 2.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

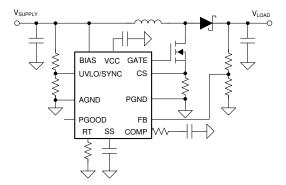

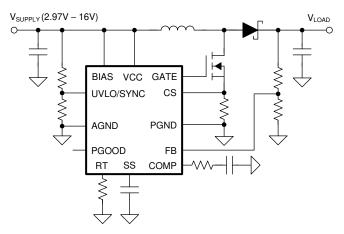

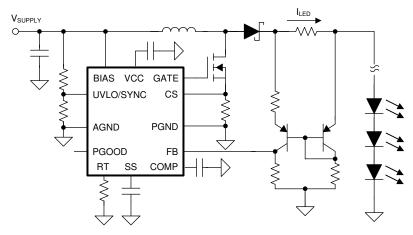

#### **Typical Boost Application**

# **Table of Contents**

| 1 | Features 1                              | 10 | Application and Implementation                      | 25    |

|---|-----------------------------------------|----|-----------------------------------------------------|-------|

| 2 | Applications 1                          |    | 10.1 Application Information                        | 25    |

| 3 | Description 1                           |    | 10.2 Typical Application                            | 25    |

| 4 | Revision History2                       |    | 10.3 System Examples                                | 29    |

| 5 | Description (continued)                 | 11 | Power Supply Recommendations                        | 35    |

| 6 | Device Comparison Table                 | 12 | Layout                                              | 36    |

| 7 | Pin Configuration and Functions 4       |    | 12.1 Layout Guidelines                              | 36    |

| 8 | Specifications                          |    | 12.2 Layout Examples                                | 37    |

| O | 8.1 Absolute Maximum Ratings            | 13 | Device and Documentation Support                    | 39    |

|   | 8.2 ESD Ratings                         |    | 13.1 Device Support                                 | 39    |

|   | 8.3 Recommended Operating Conditions    |    | 13.2 Documentation Support                          | 39    |

|   | 8.4 Thermal Information                 |    | 13.3 Related Links                                  | 39    |

|   | 8.5 Electrical Characteristics 6        |    | 13.4 Receiving Notification of Documentation Update | es 40 |

|   |                                         |    | 13.5 Community Resources                            | 40    |

| ^ | 21 21 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |    | 13.6 Trademarks                                     |       |

| 9 | Detailed Description                    |    | 13.7 Electrostatic Discharge Caution                | 40    |

|   | 9.1 Overview                            |    | 13.8 Glossary                                       |       |

|   | 9.2 Functional Block Diagram 11         | 14 | -                                                   |       |

|   | 9.3 Feature Description                 | 17 | Information                                         | 40    |

|   | 9.4 Device Functional Modes             |    | IIIOIIII audii                                      | 40    |

|   |                                         |    |                                                     |       |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (January 2020) to Revision B   |      |  |  |

|--------------------------------------------------------|------|--|--|

| Added Added Functional Safety Capable to Features list | 1    |  |  |

| Changes from Original (December 2018) to Revision A    | Page |  |  |

| Added device LM51551 to data sheet                     | 1    |  |  |

# 5 Description (continued)

The internal VCC regulator also supports BIAS pin operation up to 45 V (50-V absolute maximum). The switching frequency is dynamically programmable with an external resistor from 100 kHz to 2.2 MHz. Switching at 2.2 MHz minimizes AM band interference and allows for a small solution size and fast transient response.

The device features a 1.5-A standard MOSFET driver and a low 100-mV current limit threshold. The device also supports the use of an external VCC supply to improve efficiency. Low operating current and pulse-skipping operation improve efficiency at light loads.

The device has built-in protection features such as cycle-by-cycle current limit, overvoltage protection, line UVLO, and thermal shutdown. Hiccup mode overload protection is available in the LM51551 device option. Additional features include low shutdown I<sub>Q</sub>, programmable soft start, programmable slope compensation, precision reference, power-good indicator, and external clock synchronization.

# 6 Device Comparison Table

| DEVICE OPTION | HICCUP MODE PROTECTION | INTERNAL REFERENCE |

|---------------|------------------------|--------------------|

| LM5155        | Disabled               | 1 V                |

| LM51551       | Enabled                | 1 V                |

Product Folder Links: LM5155 LM51551

# 7 Pin Configuration and Functions

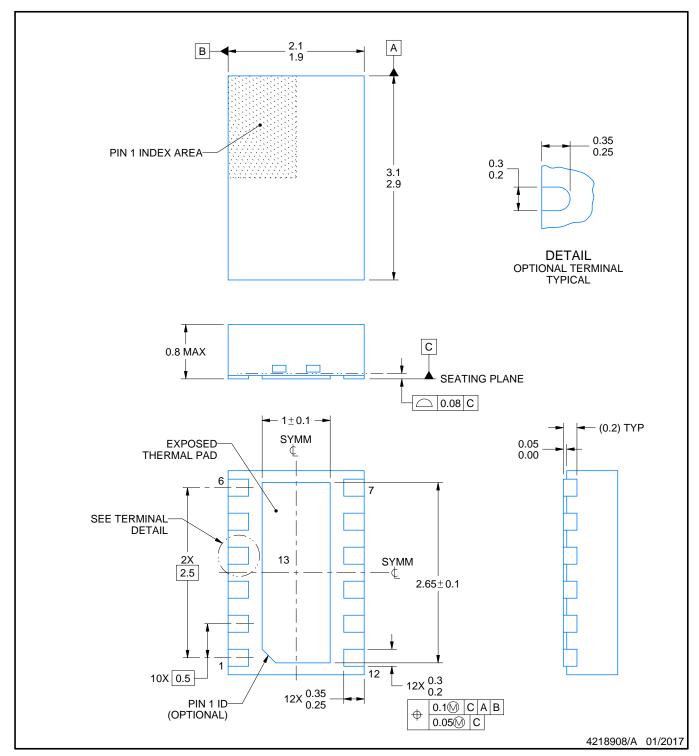

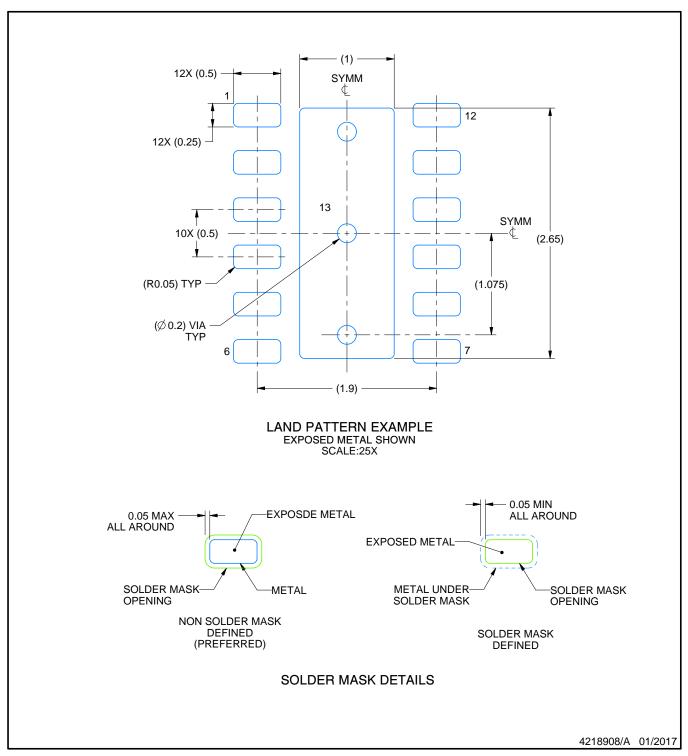

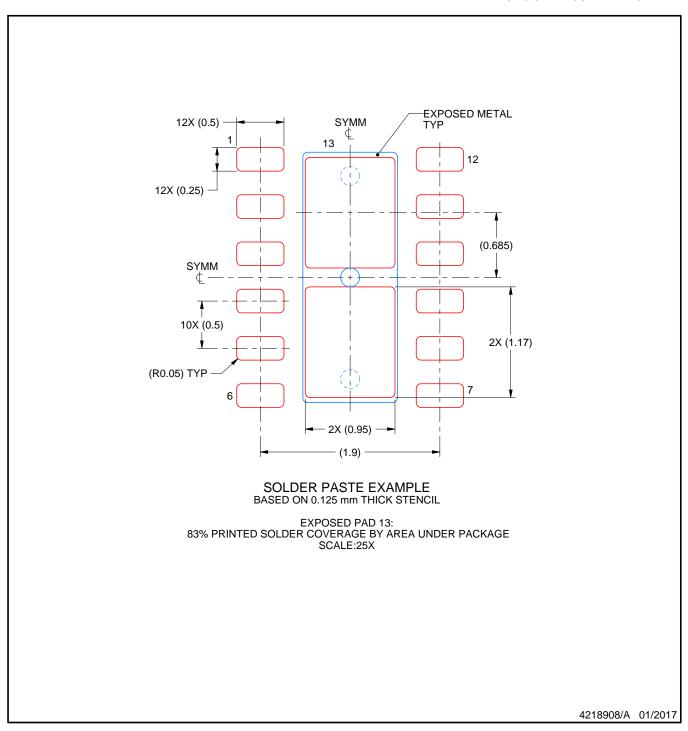

#### DSS Package 12-Pin WSON Top View

#### **Pin Functions**

|     | PIN TYPE <sup>(1)</sup> |      | DECORPTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----|-------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME                    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1   | BIAS                    | Р    | Supply voltage input to the VCC regulator. Connect a bypass capacitor from this pin to PGND                                                                                                                                                                                                                                                                                                                             |  |

| 2   | VCC                     | Р    | Output of the internal VCC regulator and supply voltage input of the MOSFET driver. Connect a ceramic bypass capacitor from this pin to PGND.                                                                                                                                                                                                                                                                           |  |

| 3   | GATE                    | 0    | N-channel MOSFET gate drive output. Connect directly to the gate of the N-channel MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                          |  |

| 4   | PGND                    | G    | Power ground pin. Connect directly to the ground connection of the sense resistor through a low inductance wide and short path.                                                                                                                                                                                                                                                                                         |  |

| 5   | CS                      | 1    | Current sense input pin. Connect to the positive side of the current sense resistor through a short path.                                                                                                                                                                                                                                                                                                               |  |

| 6   | COMP                    | 0    | Output of the internal transconductance error amplifier. Connect the loop compensation components between this pin and PGND.                                                                                                                                                                                                                                                                                            |  |

| 7   | AGND                    | G    | Analog ground pin. Connect to the analog ground plane through a wide and short path.                                                                                                                                                                                                                                                                                                                                    |  |

| 8   | FB                      | I    | Inverting input of the error amplifier. Connect a voltage divider from the output to this pin to set output voltage in boost/SEPIC topologies. Connect the low-side feedback resistor to AGND.                                                                                                                                                                                                                          |  |

| 9   | SS                      | I    | Soft-start time programming pin. An external capacitor and an internal current source set the ramp rate of the internal error amplifier reference during soft start. Connect the ground connection of the capacitor to AGND.                                                                                                                                                                                            |  |

| 10  | RT                      | 1    | Switching frequency setting pin. The switching frequency is programmed by a single resistor between RT and AGND.                                                                                                                                                                                                                                                                                                        |  |

| 11  | PGOOD                   | 0    | Power-good indicator. An open-drain output which goes low if FB is below the under voltage threshold. Connect a pullup resistor to the system voltage rail.                                                                                                                                                                                                                                                             |  |

| 12  | UVLO/EN/SY<br>NC        | I    | Undervoltage lockout programming pin. The converter start-up and shutdown levels can be programmed by connecting this pin to the supply voltage through a resistor divider. The internal clock can be synchronized to an external clock by applying a negative pulse signal into the UVLO/EN/SYNC pin. This pin must not be left floating. Connect to BIAS pin if not used. Connect the low-side UVLO resistor to AGND. |  |

|     | EP                      | _    | Exposed pad of the package. The exposed pad must be connected to AGND and the large ground copper plane to decrease thermal resistance.                                                                                                                                                                                                                                                                                 |  |

(1) G = Ground, I = Input, O = Output, P = Power

# 8 Specifications

## 8.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range<sup>(1)</sup>

|              |                                          | MIN  | MAX                    | UNIT |

|--------------|------------------------------------------|------|------------------------|------|

|              | BIAS to AGND                             | -0.3 | 50                     |      |

|              | UVLO to AGND                             | -0.3 | V <sub>BIAS</sub> +0.3 |      |

|              | SS to AGND <sup>(2)</sup>                | -0.3 | 3.8                    |      |

|              | RT to AGND <sup>(2)</sup>                | -0.3 | 3.8                    |      |

| Input        | FB to AGND                               | -0.3 | 3.8                    | V    |

|              | CS to AGND(DC)                           | -0.3 | 0.3                    |      |

|              | CS to AGND(100ns transient)              | -1   |                        |      |

|              | CS to AGND(20ns transient)               | -2   |                        |      |

|              | PGND to AGND                             | -0.3 | 0.3                    |      |

|              | VCC to AGND                              | -0.3 | 18 <sup>(3)</sup>      |      |

|              | GATE to AGND (100ns transient)           | -1   |                        |      |

| Output       | GATE to AGND (50ns transient)            | -2   |                        | V    |

|              | PGOOD to AGND <sup>(4)</sup>             | -0.3 | 18                     |      |

|              | COMP to AGND <sup>(5)</sup>              | -0.3 |                        |      |

| Junction ten | nperature, T <sub>J</sub> <sup>(6)</sup> | -40  | 150                    | °C   |

| Storage tem  | perature, T <sub>stg</sub>               | -55  | 150                    | -0   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) This pin is not specified to have an external voltage applied.

- (3) 18 V or V<sub>BIAS</sub> + 0.3 V whichever is lower

- (4) The maximum current sink is limited to 1 mA when V<sub>PGOOD</sub>>V<sub>BIAS</sub>.

- (5) This pin has an internal max voltage clamp which can handle up to 1.6 mA.

- (6) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# 8.2 ESD Ratings

|                    |               |                                                                               | VALUE | UNIT |

|--------------------|---------------|-------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Copyright © 2018–2020, Texas Instruments Incorporated

# 8.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 125°C (unless otherwise specified) (1)

|                   |                                 | MIN  | NOM MAX | UNIT |

|-------------------|---------------------------------|------|---------|------|

| $V_{BIAS}$        | Bias input <sup>(2)</sup>       | 2.97 | 45      | V    |

| $V_{VCC}$         | VCC voltage <sup>(3)</sup>      | 2.97 | 16      | V    |

| $V_{\text{UVLO}}$ | UVLO input                      | 0    | 45      | V    |

| $V_{FB}$          | FB input                        | 0    | 3.7     | V    |

| f <sub>SW</sub>   | Typical switching frequency     | 100  | 2200    | kHz  |

| f <sub>SYNC</sub> | Synchronization pulse frequency | 100  | 2200    | kHz  |

| TJ                | Operating junction temperature  | -40  | 125     | °C   |

<sup>(1)</sup> Operating Ratings are conditions under the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics

#### 8.4 Thermal Information

|                      |                                                              | LM5155x   |      |

|----------------------|--------------------------------------------------------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                                | DSS(WSON) | UNIT |

|                      |                                                              | 12 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance (LM5155EVM-BST)       | 40.8      | °C/W |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                       | 63.7      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                    | 61.0      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                         | 32.1      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter (LM5155EVM-BST)   | 1.5       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter                   | 2.3       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter (LM5155EVM-BST) | 22.5      | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter                 | 31.9      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance                 | 11.2      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 8.5 Electrical Characteristics

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over  $T_J$  = -40°C to 125°C. Unless otherwise stated,  $V_{BIAS}$  = 12V,  $R_T$  = 9.09k $\Omega$

|                               | PARAMETER                  | TEST CONDITIONS                                                                    | MIN  | TYP   | MAX  | UNIT |

|-------------------------------|----------------------------|------------------------------------------------------------------------------------|------|-------|------|------|

| SUPPLY CURRE                  | NT                         |                                                                                    |      |       |      |      |

| I <sub>SHUTDOWN(BIAS)</sub>   | BIAS shutdown current      | V <sub>BIAS</sub> = 12 V, V <sub>UVLO</sub> = 0 V                                  |      | 2.6   | 5    | uA   |

| I <sub>OPERATING(BIAS)</sub>  | BIAS operating current     | $V_{BIAS}$ = 12 V, $V_{UVLO}$ = 2 V, $V_{FB}$ = $V_{REF}$ , $R_T$ = 220 k $\Omega$ |      | 480   | 540  | uA   |

| VCC REGULATO                  | R                          |                                                                                    |      |       |      |      |

| V <sub>VCC-REG</sub>          | VCC regulation             | V <sub>BIAS</sub> = 8 V, No load                                                   | 6.5  | 6.85  | 7    | V    |

|                               | VCC regulation             | $V_{BIAS} = 8 \text{ V}, I_{VCC} = 35 \text{ mA}$                                  | 6.5  |       |      | V    |

| V <sub>VCC-UVLO(RISING)</sub> | VCC UVLO threshold         | VCC rising                                                                         | 2.75 | 2.85  | 2.95 | V    |

|                               | VCC UVLO hysteresis        | VCC falling                                                                        |      | 0.063 |      | V    |

| I <sub>VCC-CL</sub>           | VCC sourcing current limit | V <sub>BIAS</sub> = 10 V, V <sub>VCC</sub> = 0 V                                   | 35   | 105   |      | mA   |

| ENABLE                        |                            |                                                                                    |      |       |      |      |

| V <sub>EN(RISING)</sub>       | Enable threshold           | EN rising                                                                          | 0.4  | 0.52  | 0.7  | V    |

| V <sub>EN(FALLING)</sub>      | Enable threshold           | EN falling                                                                         | 0.33 | 0.49  | 0.63 | V    |

| V <sub>EN(HYS)</sub>          | Enable hysteresis          | EN falling                                                                         |      | 0.03  |      | V    |

Product Folder Links: LM5155 LM51551

<sup>(2)</sup> BIAS pin operating range is from 2.97 V to 16 V when VCC is directly connected to BIAS. BIAS pin operating range is from 3.5 V to 45 V when VCC is supplied from the internal VCC regulator.

<sup>(3)</sup> This pin voltage should be less than  $V_{BIAS}$  + 0.3 V.

# **Electrical Characteristics (continued)**

Typical values correspond to  $T_J = 25$ °C. Minimum and maximum limits apply over  $T_J = -40$ °C to 125°C. Unless otherwise stated,  $V_{BIAS} = 12V$ ,  $R_T = 9.09k\Omega$

|                            | PARAMETER                                | TEST CONDITIONS                            | MIN      | TYP  | MAX   | UNIT   |

|----------------------------|------------------------------------------|--------------------------------------------|----------|------|-------|--------|

| UVLO/SYNC                  |                                          |                                            |          |      |       |        |

| V <sub>UVLO(RISING)</sub>  | UVLO / SYNC threshold                    | UVLO rising                                | 1.425    | 1.5  | 1.575 | V      |

| V <sub>UVLO(FALLING)</sub> | UVLO / SYNC threshold                    | UVLO falling                               | 1.370    | 1.45 | 1.520 | V      |

| V <sub>UVLO(HYS)</sub>     | UVLO / SYNC threshold hysteresis         | UVLO falling                               |          | 0.05 |       | V      |

| I <sub>UVLO</sub>          | UVLO hysteresis current                  | V <sub>UVLO</sub> = 1.6 V                  | 4        | 5    | 6     | uA     |

| SS                         | ,                                        |                                            | ·        |      | ·     |        |

| I <sub>SS</sub>            | Soft-start current                       |                                            | 9        | 10   | 11    | uA     |

|                            | SS pull-down switch R <sub>DSON</sub>    |                                            |          | 55   |       | Ω      |

| PULSE WIDTH                | MODULATION                               |                                            |          |      |       |        |

| fsw1                       | Switching frequency                      | $R_T = 220 \text{ k}\Omega$                | 85       | 100  | 115   | kHz    |

| fsw2                       | Switching frequency                      | $R_T = 9.09 \text{ k}\Omega$               | 1980     | 2200 | 2420  | kHz    |

| t <sub>ON(MIN)</sub>       | Minimum on-time                          | $R_T = 9.09 \text{ k}\Omega$               |          | 50   |       | ns     |

| D <sub>MAX1</sub>          | Maximum duty cycle limit                 | $R_T = 9.09 \text{ k}\Omega$               | 80%      | 85%  | 90%   |        |

| D <sub>MAX2</sub>          | Maximum duty cycle limit                 | $R_T = 220 \text{ k}\Omega$                | 90%      | 93%  | 96%   |        |

| CURRENT SEN                | SE                                       |                                            |          |      |       |        |

| I <sub>SLOPE</sub>         | Peak slope compensation current          | $R_T = 220 \text{ k}\Omega$                | 22.5     | 30   | 37.5  | uA     |

| V <sub>CLTH</sub>          | Current Limit threshold (CS-PGND)        |                                            | 93       | 100  | 107   | mV     |

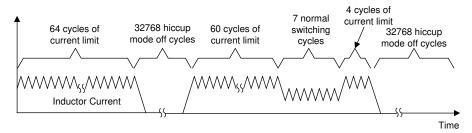

| HICCUP MODE                | PROTECTION (LM51551)                     |                                            |          |      |       |        |

|                            | Hiccup enable cycles                     |                                            |          | 64   |       | Cycles |

|                            | Hiccup timer reset cycles                |                                            |          | 8    |       | Cycles |

| ERROR AMPLIF               | FIER                                     |                                            | •        |      |       |        |

| $V_{REF}$                  | FB reference                             | LM5155, LM51551                            | 0.99     | 1    | 1.01  | V      |

| Gm                         | Transconductance                         |                                            |          | 2    |       | mA/V   |

|                            | COMP sourcing current                    | V <sub>COMP</sub> = 1.2 V                  | 180      |      |       | uA     |

|                            | COMP clamp voltage                       | COMP rising (V <sub>UVLO</sub> = 2.0V)     | 2.5      | 2.8  |       | V      |

|                            | COMP clamp voltage                       | COMP falling                               |          | 1    | 1.1   | V      |

| OVP                        | -                                        |                                            | •        |      |       |        |

| V <sub>OVTH</sub>          | Over-voltage threshold                   | FB rising (referece to V <sub>REF</sub> )  | 107%     | 110% | 113%  |        |

|                            | Over-voltage threshold                   | FB falling (referece to V <sub>REF</sub> ) |          | 105% |       |        |

| PGOOD                      | ,                                        |                                            |          |      | '     |        |

|                            | PGOOD pull-down switch R <sub>DSON</sub> | 1 mA sinking                               |          | 90   |       | Ω      |

| V <sub>UVTH</sub>          | Undervoltage threshold                   | FB falling (referece to V <sub>REF</sub> ) | 87%      | 90%  | 93%   |        |

|                            | Undervoltage threshold                   | FB rising (referece to V <sub>REF</sub> )  |          | 95%  |       |        |

| MOSFET DRIVE               | •                                        | 150                                        | <u> </u> |      |       |        |

|                            | High-state voltage drop                  | 100 mA sinking                             |          | 0.25 |       | V      |

|                            | Low-state voltage drop                   | 100 mA sourcing                            |          | 0.15 |       | V      |

| THERMAL SHU                | • •                                      |                                            | +        |      |       |        |

| T <sub>TSD</sub>           | Thermal shutdown threshold               | Temperature rising                         |          | 175  |       | °C     |

| .02                        | Thermal shutdown hysteresis              | <u> </u>                                   |          | 15   |       | °C     |

Copyright © 2018–2020, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

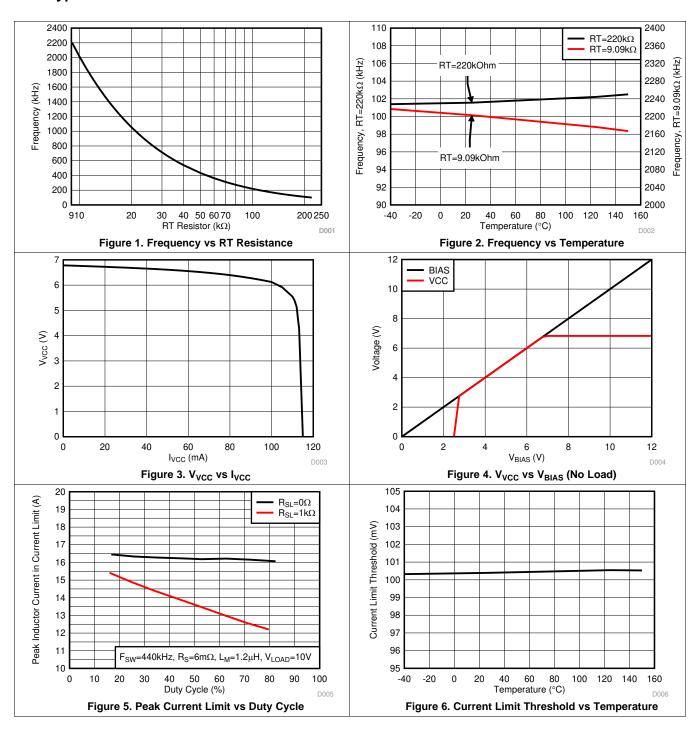

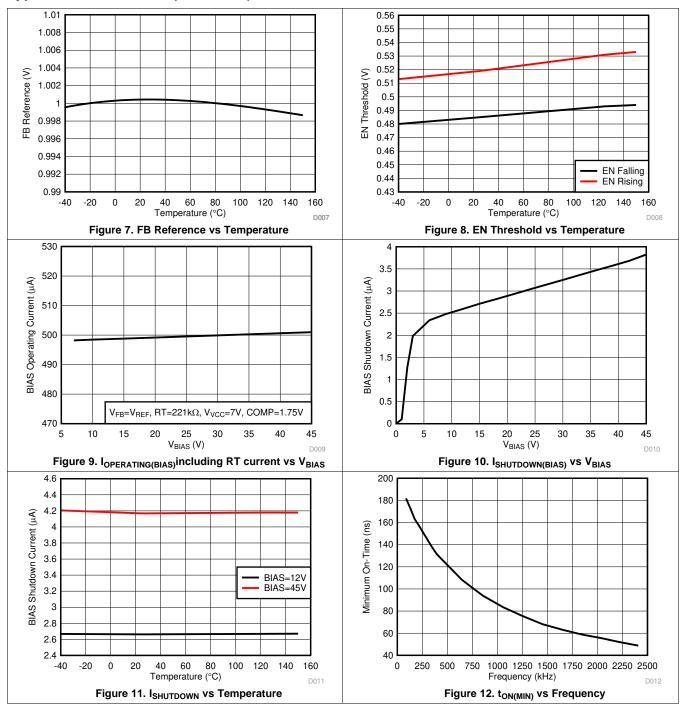

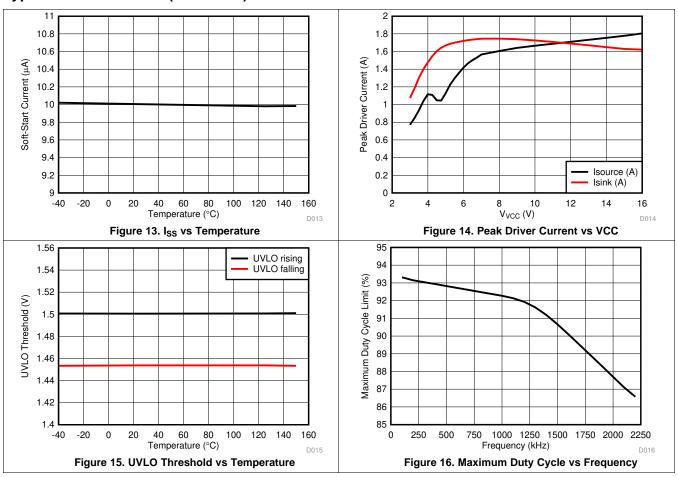

# 8.6 Typical Characteristics

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# **Detailed Description**

#### Overview

The LM5155x device is a wide input range, non-synchronous boost controller that uses peak-current-mode control. The device can be used in boost, SEPIC, and flyback topologies.

The LM5155x device can start up from a 1-cell battery with a minimum of 2.97 V if the BIAS pin is connected to the VCC pin. It can operate with the input supply voltage as low as 1.5 V if the BIAS pin is greater than 3.5 V. The internal VCC regulator also supports BIAS pin operation up to 45 V (50-V absolute maximum). The switching frequency is dynamically programmable with an external resistor from 100 kHz to 2.2 MHz. Switching at 2.2 MHz minimizes AM band interference and allows for a small solution size and fast transient response.

The device features a 1.5-A standard MOSFET driver and a low 100-mV current limit threshold. The device also supports the use of an external VCC supply to improve efficiency. Low operating current and pulse skipping operation improve efficiency at light loads.

The device has built-in protection features such as cycle-by-cycle current limit, overvoltage protection, line UVLO and thermal shutdown. Hiccup mode overload protection is available in the LM51551 device option. Additional features include low shutdown Io, programmable soft start, programmable slope compensation, precision reference, power good indicator, and external clock synchronization.

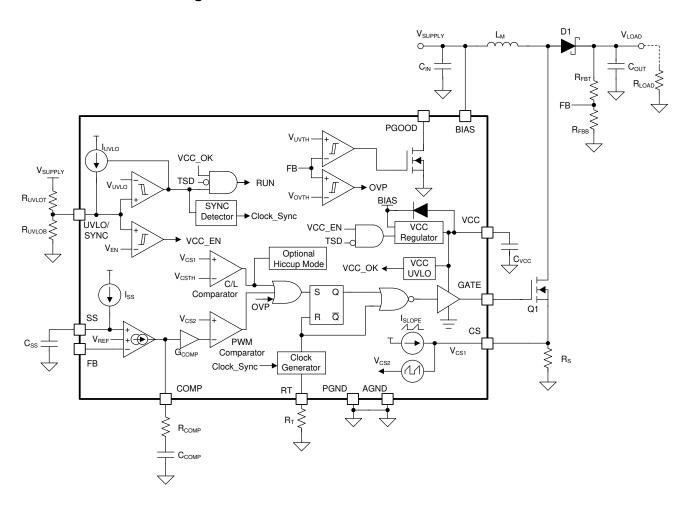

## 9.2 Functional Block Diagram

Copyright © 2018-2020, Texas Instruments Incorporated

#### 9.3 Feature Description

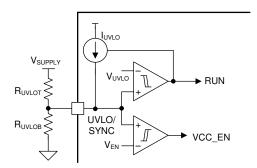

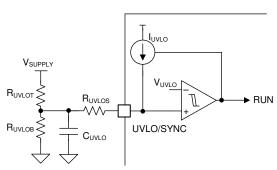

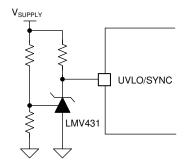

#### 9.3.1 Line Undervoltage Lockout (UVLO/SYNC pin)

The device has a dual-level UVLO circuit. During power-on, if the BIAS pin voltage is greater than 2.7 V, and the UVLO pin voltage is in between the enable threshold ( $V_{EN}$ ) and the UVLO threshold ( $V_{UVLO}$ ) for more than 1.5 µs (see *Clock Synchronization (UVLO/SYNC Pin)* for more details), the device starts up and an internal configuration starts. The device typically requires a 65-µs internal start-up delay before entering standby mode. In the standby mode, VCC regulator and RT regulator are operational, SS pin is grounded, and no switching at the GATE output.

Figure 17. Line UVLO and Enable

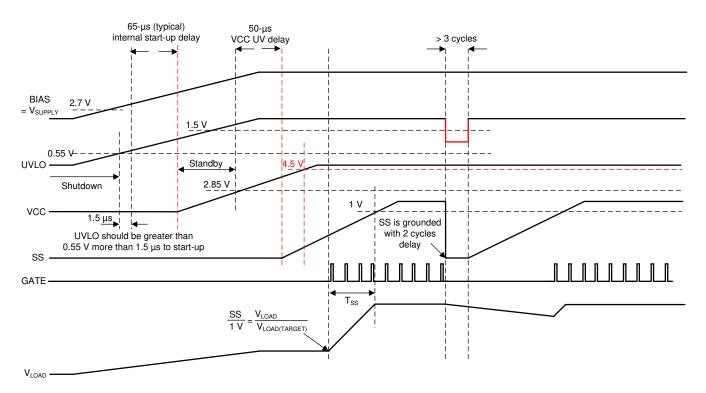

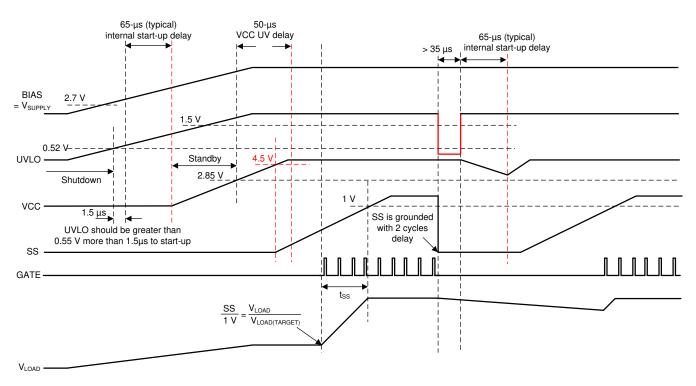

When the UVLO pin voltage is above the UVLO threshold, the device enters run mode. In the run mode, a soft-start sequence starts if the VCC voltage is greater than 4.5 V, or 50  $\mu$ s after the VCC voltage exceeds the 2.85-V VCC UV threshold ( $V_{VCC-UVLO}$ ), whichever comes first. UVLO hysteresis is accomplished with an internal 50-mV voltage hysteresis and an additional 5- $\mu$ A current source that is switched on or off. When the UVLO pin voltage exceeds the UVLO threshold, the current source is enabled to quickly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the UVLO threshold, the current source is disabled causing the voltage at the UVLO pin to fall quickly. When the UVLO pin voltage is less than the enable threshold ( $V_{EN}$ ), the device enters shutdown mode after a 35- $\mu$ s (typical) delay with all functions disabled.

Figure 18. Boost Start-Up Waveforms

Case 1: Start-Up by 2.85-V VCC UVLO, UVLO Toggle After Start-Up

Figure 19. Boost Start-Up Waveforms

Case2: Start-Up When VCC > 4.5 V, EN Toggle After Start-Up

Copyright © 2018–2020, Texas Instruments Incorporated

The external UVLO resistor divider must be designed so that the voltage at the UVLO pin is greater than 1.5 V (typical) when the input voltage is in the desired operating range. The values of  $R_{UVLOT}$  and  $R_{UVLOB}$  can be calculated as shown in Equation 1 and Equation 2.

$$R_{UVLOT} = \frac{V_{SUPPLY(ON)} \times \frac{V_{UVLO(FALLING)}}{V_{UVLO(RISING)}} - V_{SUPPLY(OFF)}}{I_{UVLO}}$$

#### where

• V<sub>SUPPLY(ON)</sub> is the desired start-up voltage of the converter.

$$R_{UVLOB} = \frac{V_{UVLO(RISING)} \times R_{UVLOT}}{V_{SUPPLY(ON)} - V_{UVLO(RISING)}}$$

(2)

UVLO capacitor ( $C_{UVLO}$ ) is required in case the input voltage drops below the  $V_{SUPPLY(OFF)}$  momentarily during the start-up or during a severe load transient at the low input voltage. If the required UVLO capacitor is large, an additional series UVLO resistor ( $R_{UVLOS}$ ) can be used to quickly raise the voltage at the UVLO pin when the 5- $\mu$ A hysteresis current turns on.

Figure 20. Line UVLO using Three UVLO Resistors

Do not leave the UVLO pin floating. Connect to the BIAS pin if not used.

#### 9.3.2 High Voltage VCC Regulator (BIAS, VCC Pin)

The device has an internal wide input VCC regulator which is sourced from the BIAS pin. The wide input VCC regulator allows the BIAS pin to be connected directly to supply voltages from 3.5 V to 45 V.

The VCC regulator turns on when the device is in the standby or run mode. When the BIAS pin voltage is below the VCC regulation target, the VCC output tracks the BIAS with a small dropout voltage. When the BIAS pin voltage is greater than the VCC regulation target, the VCC regulator provides 6.85-V supply for the N-channel MOSFET driver.

The VCC regulator sources current into the capacitor connected to the VCC pin with a minimum of 35-mA capability. The recommended VCC capacitor value is from 1  $\mu$ F to 4.7  $\mu$ F.

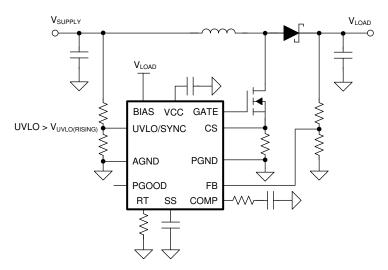

The device supports a wide input range from 3.5 V to 45 V in normal configuration. By connecting the BIAS pin directly to the VCC pin, the device supports inputs from 2.97 V to 16 V. This configuration is recommended when the device starts up from a 1-cell battery.

Figure 21. 2.97-V Start-Up (BIAS = VCC)

The minimum supply voltage after start-up can be further decreased by supplying the BIAS pin from the boost converter output or from an external power supply as shown in Figure 22.

Figure 22. Decrease the Minimum Operating Voltage After Start-Up

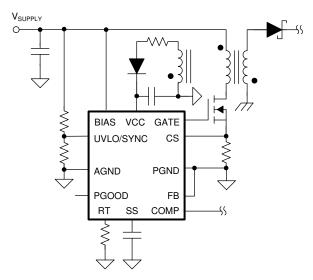

In flyback topology, the internal power dissipation of the device can be decreased by supplying the VCC using an additional transformer winding. In this configuration, the external VCC supply voltage must be greater than the VCC regulation target (V<sub>VCC-REG</sub>), and the BIAS pin voltage must be greater the VCC voltage because the VCC regulator includes a diode between VCC and BIAS.

Copyright © 2018-2020, Texas Instruments Incorporated

Figure 23. External VCC Supply (BIAS ≥ VCC)

If the voltage of the external VCC bias supply is greater than the BIAS pin voltage, use an external blocking diode from the input power supply to the BIAS pin to prevent the external bias supply from passing current to the boost input supply through VCC.

#### 9.3.3 Soft Start (SS pin)

The soft-start feature helps the converter gradually reach the steady state operating point, thus reducing start-up stresses and surges. The device regulates the FB pin to the SS pin voltage or the internal reference, whichever is lower.

At start-up, the internal 10- $\mu$ A soft-start current source ( $I_{SS}$ ) turns on 50  $\mu$ s after the VCC voltage exceeds the 2.85-VCC UV threshold, or if the VCC voltage is greater than 4.5 V, whichever comes first. The soft-start current gradually increases the voltage on an external soft-start capacitor connected to the SS pin. This results in a gradual rise of the output voltage. The SS pin is pulled down to ground by an internal switch when the VCC is less than VCC UVLO threshold, the UVLO is less than the UVLO threshold, during hiccup mode off-time or thermal shutdown.

In boost topology, soft-start time ( $t_{SS}$ ) varies with the input supply voltage. The soft-start time in boost topology is calculated as shown in Equation 3.

$$t_{SS} = \frac{C_{SS}}{I_{SS}} \times \left(1 - \frac{V_{SUPPLY}}{V_{LOAD}}\right)$$

(3)

In SEPIC topology, the soft-start time (t<sub>SS</sub>) is calculated as follows.

$$t_{SS} = \frac{C_{SS}}{I_{SS}} \tag{4}$$

TI recommends choosing the soft-start time long enough so that the converter can start up without going into an overcurrent state. See the *Hiccup Mode Overload Protection (LM51551 Only)* section for more detailed information.

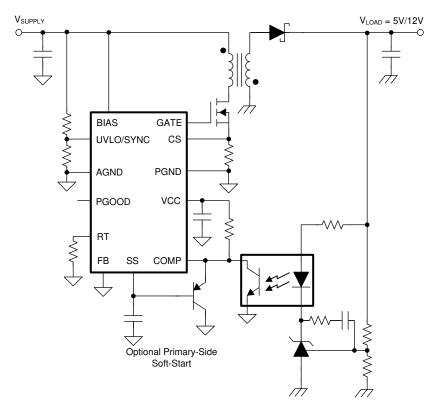

Figure 24 shows an implementation of primary side soft-start in flyback topology.

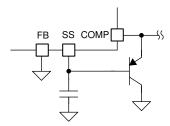

Figure 24. Primary-Side Soft-Start in Flyback

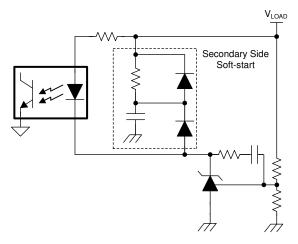

Figure 25 shows an implementation of secondary side soft-start in flyback topology.

Figure 25. Secondary-Side Soft-Start in Flyback

#### 9.3.4 Switching Frequency (RT Pin)

The switching frequency of the device can be set by a single RT resistor connected between the RT and the AGND pins. The resistor value to set the RT switching frequency ( $f_{RT}$ ) is calculated as shown in Equation 5.

$$R_{T} = \frac{2.21 \times 10^{10}}{f_{RT(TYPICAL)}} - 955 \tag{5}$$

The RT pin is regulated to 0.5 V by the internal RT regulator when the device is enabled.

#### 9.3.5 Clock Synchronization (UVLO/SYNC Pin)

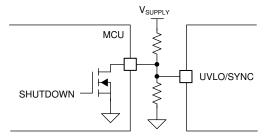

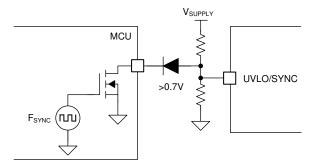

The switching frequency of the device can be synchronized to an external clock by pulling down the UVLO/SYNC pin. The internal clock of the device is synchronized at the falling edge, but ignores the falling edge input during the forced off-time which is determined by the maximum duty cycle limit. The external synchronization clock must pull down the UVLO/SYNC pin voltage below 1.45 V (typical). The duty cycle of the pulldown pulse is not limited, but the minimum pulldown pulse width must be greater than 150 ns, and the minimum pullup pulse width must be greater than 250 ns. Figure 26 shows an implementation of the remote shutdown function. The UVLO pin can be pulled down by a discrete MOSFET or an open-drain output of an MCU. In this configuration, the device stops switching immediately after the UVLO pin is grounded, and the device shuts down 35 µs (typical) after the UVLO pin is grounded.

Figure 26. UVLO and Shutdown

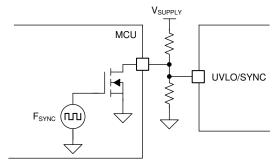

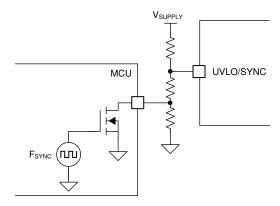

Figure 27 shows an implementation of shutdown and clock synchronization functions together. In this configuration, the device stops switching immediately when the UVLO pin is grounded, and the device shuts down if the  $f_{SYNC}$  stays in high logic state for longer than 35  $\mu s$  (typical) (UVLO is in low logic state for more than 35  $\mu s$  (typical)). The device runs at the  $f_{SYNC}$  if clock pulses are provided after the device is enabled.

Figure 27. UVLO, Shutdown and Clock Synchronization

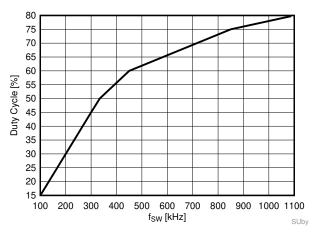

Figure 29 and Figure 30 show implementations of standby and clock synchronization functions together. In this configuration, The device stops switching immediately if  $f_{SYNC}$  stays in high logic state and enters standby mode if  $f_{SYNC}$  stays in high logic state for longer than 2 switching cycles. The device runs at the  $f_{SYNC}$  if clock pulses are provided. Because the device can be enabled when the UVLO pin voltage is greater than the enable threshold for more than 1.5  $\mu$ s, the configurations in Figure 29 and Figure 30 are recommended if the external clock synchronization pulses are provided from the start before the device is enabled. This 1.5- $\mu$ s requirement can be relaxed when the duty cycle of the synchronization pulse is greater than 50%. Figure 28 shows the required minimum duty cycle to start up by synchronization pulses. When the switching frequency is greater than 1.1MHz, the UVLO pin voltage should be greater than the enable threshold for more than 1.5  $\mu$ s before applying the external synchronization pulse.

Figure 28. Required Duty Cycle to Start Up by SYNC

Figure 29. UVLO, Standby and Clock Synchronization (a)

Figure 30. UVLO, Standby and Clock Synchronization (b)

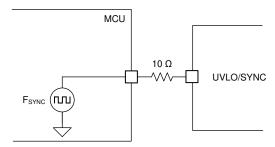

If the UVLO function is not required, the shutdown and clock synchronization functions can be implemented together by using one push-pull output of the MCU. In this configuration, the device shuts down if  $f_{SYNC}$  stays in low logic state for longer than 35  $\mu$ s (typical). The device is enabled if  $f_{SYNC}$  stays in high logic state for longer than 1.5  $\mu$ s. The device runs at the  $f_{SYNC}$  if clock pulses are provided after the device is enabled. Also, in this configuration, it is recommended to apply the external clock pulses after the BIAS is supplied. By limiting the current flowing into the UVLO pin below 1 mA using a current limiting resistor, the external clock pulses can be supplied before the BIAS is supplied (see Figure 31).

Figure 31. Shutdown and Clock Synchronization

Figure 32 shows an implementation of inverted enable using external circuit.

Figure 32. Inverted UVLO (TBD)

The external clock frequency (f<sub>SYNC</sub>) must be within +25% and -30% of f<sub>RT(TYPICAL)</sub>. Because the maximum duty cycle limit and the peak current limit with slope resistor(R<sub>SL</sub>) are affected by the clock synchronization, take extra care when using the clock synchronization function. See the *Current Sense and Slope Compensation (CS Pin)*, *Current Limit and Minimum On-time (CS Pin)*, and *Maximum Duty Cycle Limit and Minimum Input Supply Voltage* sections for more information.

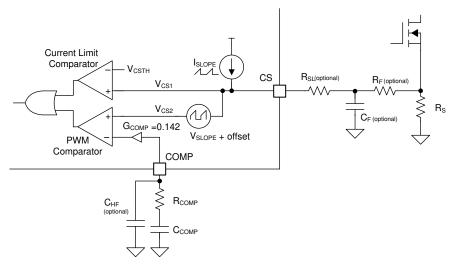

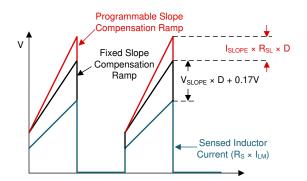

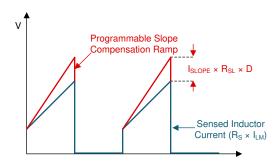

## 9.3.6 Current Sense and Slope Compensation (CS Pin)

The device has a low-side current sense and provides both fixed and optional programmable slope compensation ramps, which help to prevent sub-harmonic oscillation at high duty cycle. Both fixed and programmable slope compensation ramps are added to the sensed inductor current input for the PWM operation. But, only the programmable slope compensation ramp is added to the sensed inductor current input (see Figure 33). For an accurate peak current limit operation over the input supply voltage, TI recommends using only the fixed slope compensation (see Figure 5).

The device can generate the programmable slope compensation ramp using an external slope resistor ( $R_{SL}$ ) and a sawtooth current source with a slope of 30  $\mu$ A ×  $f_{RT}$ . This current flows out of the CS pin.

Figure 33. Current Sensing and Slope Compensation

Figure 34. Slope Compensation Ramp (a) at PWM Comparator Input

Figure 35. Slope Compensation Ramp (b) at Current Limit Comparator Input

Use Equation 6 to calculate the value of the peak slope current ( $I_{SLOPE}$ ) and use Equation 7 to calculate the value of the peak slope voltage ( $V_{SLOPE}$ ).

$$I_{SLOPE} = 30\mu A \times \frac{f_{RT}}{f_{SYNC}}$$

$$V_{SLOPE} = 40mV \times \frac{f_{RT}}{f_{SYNC}}$$

(6)

where

$$f_{SYNC} = f_{RT}$$

if clock synchronization is not used. (7)

According to peak current mode control theory, the slope of the compensation ramp must be greater than half of the sensed inductor current falling slope to prevent sub-harmonic oscillation at high duty cycle. Therefore, the minimum amount of slope compensation in boost topology should satisfy the following inequality:

$$0.5 \times \frac{\left(V_{LOAD} + V_{F}\right) - V_{SUPPLY}}{L_{M}} \times R_{S} \times Margin < 40 mV \times f_{SW}$$

where

The recommended for margin to cover non-ideal factors is 1.2. If required,  $R_{SL}$  can be added to further increase the slope of the compensation ramp. Typically 82% of the sensed inductor current falling slope is known as an optimal amount of the slope compensation. The  $R_{SL}$  value to achieve 82% of the sensed inductor current falling slope is calculated as shown in Equation 9.

$$0.82 \times \frac{\left(V_{LOAD} + V_{F}\right) - V_{SUPPLY}}{L_{M}} \times R_{S} = \left(30uA \times R_{SL} + 40mV\right) \times f_{SW}$$

$$(9)$$

If clock synchronization is not used, the  $f_{SW}$  frequency equals the  $f_{RT}$  frequency. If clock synchronization is used, the  $f_{SW}$  frequency equals the  $f_{SYNC}$  frequency. The maximum value for the  $R_{SL}$  resistance is 2 k $\Omega$ .

# 9.3.7 Current Limit and Minimum On-time (CS Pin)

The device provides cycle-by-cycle peak current limit protection that turns off the MOSFET when the sum of the inductor current and the programmable slope compensation ramp reaches the current limit threshold ( $V_{CLTH}$ ). Peak inductor current limit ( $I_{PEAK-CL}$ ) in steady state is calculated as shown in Equation 10.

$$I_{PEAK-CL} = \frac{V_{CLTH} - 30\mu A \times R_{SL} \times \frac{f_{RT}}{f_{SYNC}} \times D}{R_{S}}$$

(10)

Copyright © 2018–2020, Texas Instruments Incorporated

The practical duty cycle is greater than the estimated due to voltage drops across the MOSFET and sense resistor. The estimated duty cycle is calculated as shown in Equation 11.

$$D = 1 - \frac{V_{SUPPLY}}{V_{LOAD} + V_F}$$

(11)

Boost converters have a natural pass-through path from the supply to the load through the high-side power diode (D1). Because of this path and the minimum on-time limitation of the device, boost converters cannot provide current limit protection when the output voltage is close to or less than the input supply voltage. The minimum on-time is shown in Figure 12 and is calculated as Equation 12.

$$t_{ON(MIN)} \approx \frac{800 \times 10^{-15}}{\frac{1}{8 \times R_T} + 4 \times 10^{-6}}$$

(12)

If required, a small external RC filter ( $R_F$ ,  $C_F$ ) at the CS pin can be added to overcome the large leading edge spike of the current sense signal. Select an  $R_F$  value which is in the range of 10  $\Omega$  to 200  $\Omega$  and a  $C_F$  value which is in the rage of 100 pF to 2 nF. Because of the effect of this RC filter, the peak current limit is not valid when the on-time is less than 2  $\times$   $R_F$   $\times$   $C_F$ . To fully discharge the  $C_F$  during the off-time, the RC time constant should satisfy the following inequality.

$$3 \times R_F \times C_F < \frac{1 - D}{f_{SW}} \tag{13}$$

#### 9.3.8 Feedback and Error Amplifier (FB, COMP Pin)

The feedback resistor divider is connected to an internal transconductance error amplifier which features high output resistance ( $R_O = 10 \ M\Omega$ ) and wide bandwidth (BW = 7 MHz). The internal transconductance error amplifier sources current which is proportional to the difference between the FB pin and the SS pin voltage or the internal reference, whichever is lower. The internal transconductance error amplifier provides symmetrical sourcing and sinking capability during normal operation and reduces its sinking capability when the FB is greater than OVP threshold.

To set the output regulation target, select the feedback resistor values as shown in Equation 14.

$$V_{LOAD} = V_{REF} \times \left(\frac{R_{FBT}}{R_{FBB}} + 1\right)$$

(14)

The output of the error amplifier is connected to the COMP pin, allowing the use of a Type 2 loop compensation network.  $R_{COMP}$ ,  $C_{COMP}$  and optional  $C_{HF}$  loop compensation components configure the error amplifier gain and phase characteristics to achieve a stable loop response. The absolute maximum voltage rating of the FB pin is 3.8 V. If necessary, especially during automotive load dump transient, the feedback resistor divider input can be clamped with an external zener diode.

The COMP pin features internal clamps. The maximum COMP clamp limits the maximum COMP pin voltage below its absolute maximum rating even in shutdown. The minimum COMP clamp limits the minimum COMP pin voltage in order to start switching as soon as possible during no load to heavy load transition. The minimum COMP clamp is disabled when FB is connected to ground in flyback topology.

#### 9.3.9 Power-Good Indicator (PGOOD pin)

The device has a power-good indicator (PGOOD) to simplify sequencing and supervision. The PGOOD switches to a high impedance open-drain state when the FB pin voltage is greater than the feedback under voltage threshold ( $V_{UVTH}$ ), the VCC is greater than the VCC UVLO threshold and the UVLO/EN is greater than the EN threshold. A 25- $\mu$ s deglitch filter prevents any false pulldown of the PGOOD due to transients. The recommended minimum pullup resistor value is 10 k $\Omega$ .

Due to the internal diode path from the PGOOD pin to the BIAS pin, the PGOOD pin voltage cannot be greater than  $V_{\text{BIAS}}$ + 0.3 V.

#### 9.3.10 Hiccup Mode Overload Protection (LM51551 Only)

To further protect the converter during prolonged current limit conditions, the LM51551 device option provides a hiccup mode overload protection. The internal hiccup mode fault timer of the LM51551 counts the PWM clock cycles when the cycle-by-cycle current limiting occurs. When the hiccup mode fault timer detects 64 cycles of current limiting, an internal hiccup mode off timer forces the device to stop switching and pulls down SS. Then, the device will restart after 32,768 cycles of hiccup mode off-time. The 64 cycle hiccup mode fault timer is reset if 8 consecutive switching cycles occur without exceeding the current limit threshold. The soft-start time must be long enough not to trigger the hiccup mode protection during soft-start time because the hiccup mode fault timer is enabled during the soft-start.

Figure 36. Hiccup Mode Overload Protection

To avoid an unexpected hiccup mode operation during a harsh load transient condition, it is recommended to have more margin when programming the peak-current limit.

# 9.3.11 Maximum Duty Cycle Limit and Minimum Input Supply Voltage

When designing boost converters, the maximum duty cycle should be reviewed at the minimum supply voltage. The minimum input supply voltage that can achieve the target output voltage is limited by the maximum duty cycle limit, and it can be estimated as follows.

$$V_{SUPPLY(MIN)} \approx \left(V_{LOAD} + V_{F}\right) \times \left(1 - D_{MAX}\right) + I_{SUPPLY(MAX)} \times R_{DCR} + I_{SUPPLY(MAX)} \times \left(R_{DS(ON)} + R_{S}\right) \times D_{MAX}$$

where

- I<sub>SUPPLY(MAX)</sub> is the maximum input current.

- R<sub>DCR</sub> is the DC resistance of the inductor.

- $R_{DS(ON)}$  is the on-resistance of the MOSFET. (15)

$$D_{MAX1} = 1 - 0.1 \times \frac{f_{SYNC}}{f_{RT}}$$

(16)

$$D_{MAX2} = 1 - 100 \text{ns} \times f_{SW} \tag{17}$$

The minimum input supply voltage can be further decreased by supplying  $f_{SYNC}$  which is less than  $f_{RT}$ .  $D_{MAX}$  is  $D_{MAX1}$  or  $D_{MAX2}$ , whichever is lower.

#### 9.3.12 MOSFET Driver (GATE Pin)

The device provides an N-channel MOSFET driver that can source or sink a peak current of 1.5 A. The peak sourcing current is larger when supplying an external VCC that is higher than 6.75 V VCC regulation target. During start-up especially when the input voltage range is below the VCC regulation target , the VCC voltage must be sufficient to completely enhance the MOSFET. If the MOSFET drive voltage is lower than the MOSFET gate plateau voltage during start-up, the boost converter may not start up properly and it may stick at the maximum duty cycle in a high power dissipation state. This condition can be avoided by selecting a lower threshold N-channel MOSFET switch and setting the  $V_{\text{SUPPLY(ON)}}$  greater than 6 to 7 V. Because the internal VCC regulator has a limited sourcing capability, the MOSFET gate charge should satisfy the following inequality.

$$Q_{G@VCC} \times f_{SW} < 35mA$$

(18)

An internal 1-M $\Omega$  resistor is connected between GATE and PGND to prevent a false turnon during shutdown. In boost topology, switch node dV/dT must be limited during the 65-µs internal start-up delay to avoid a false turnon, which is caused by the coupling through C<sub>DG</sub> parasitic capacitance of the MOSFET.

## 9.3.13 Overvoltage Protection (OVP)

The device has OVP for the output voltage. OVP is sensed at the FB pin. If the voltage at the FB pin rises above the overvoltage threshold (V<sub>OVTH</sub>), OVP is triggered and switching stops. During OVP, the internal error amplifier is operational, but the maximum source and sink capability is decreased to 40 µA.

#### 9.3.14 Thermal Shutdown (TSD)

An internal thermal shutdown turns off the VCC regulator, disables switching and pulls down the SS when the junction temperature exceeds the thermal shutdown threshold (T<sub>TSD</sub>). After the temperature is decreased by 15°C, the VCC regulator is enabled again and the device performs a soft start.

#### 9.4 Device Functional Modes

#### 9.4.1 Shutdown Mode

If the UVLO pin voltage is below the enable threshold for longer than 35 µs (typical), the device goes to the shutdown mode with all functions disabled. In shutdown mode, the device decreases the BIAS pin current consumption to below 2.6 µA (typical)

# 9.4.2 Standby Mode

If the UVLO pin voltage is greater than the enable threshold and below the UVLO threshold for longer than 1.5 us, the device is in standby mode with the VCC regulator operational, RT regulator operational, SS pin grounded, and no switching at the GATE output. The PGOOD is activated when the VCC voltage is greater than the VCC UV threshold.

#### 9.4.3 Run Mode

If the UVLO pin voltage is above the UVLO threshold and the VCC voltage is sufficient, the device enters RUN mode. In this mode, soft start starts 50 µs after the VCC voltage exceeds the 2.85 VCC UV threshold, or if the VCC voltage is greater than 4.5 V, whichever comes first.

Submit Documentation Feedback

Copyright © 2018-2020, Texas Instruments Incorporated

# 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Application Information

TI provides three application notes which explaining how to design boost, SEPIC and Flyback converters using the device. These comprehensive application notes include component selections and loop response optimization.

See the *How to Design a Boost Converter Using LM5155-Q1* application note for information on loop response and component selections for the boost converter.

# 10.2 Typical Application

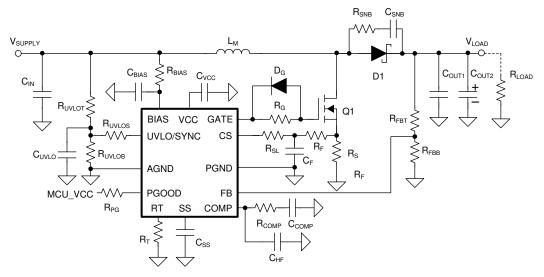

Figure 37 shows all optional components to design a boost converter.

Figure 37. Typical Boost Converter Circuit With Optional Components

# 10.2.1 Design Requirements

Table 1 shows the intended input, output, and performance parameters for this application example.

Table 1. Design Example Parameters

| DESIGN PARAMETER                                         | VALUE           |

|----------------------------------------------------------|-----------------|

| Minimum input supply voltage (V <sub>SUPPLY(MIN)</sub> ) | 6 V             |

| Target output voltage (V <sub>LOAD</sub> )               | 24 V            |

| Maximum load current (I <sub>LOAD</sub> )                | 2 A (≈ 48 Watt) |

| Typical switching frequency (f <sub>SW</sub> )           | 440 kHz         |

#### 10.2.2 Detailed Design Procedure

Use the Quick Start Calculator to expedite the process of designing of a regulator for a given application based on the LM5155 device. Download the LM5155 Boost Controller Quick Start Calculator.

## 10.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM5155x device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , and output current  $(I_{OUT})$  requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 10.2.2.2 Recommended Components

Table 2 shows a recommended list of materials for this typical application.

Table 2. List of Materials (1)

| REFERENCE<br>DESIGNATOR  | QTY. | SPECIFICATION                                                                            | MANUFACTURER  | PART NUMBER          |

|--------------------------|------|------------------------------------------------------------------------------------------|---------------|----------------------|

| R <sub>T</sub>           | 1    | RES, 49.9 k, 1%, 0.1 W, AEC-Q200 Grade 0, 0603                                           | Vishay-Dale   | CRCW060349K9FKEA     |

| R <sub>FBT</sub>         | 1    | RES, 47.0 k, 1%, 0.1 W, AEC-Q200 Grade 0, 0603                                           | Vishay-Dale   | CRCW060347K0FKEA     |

| R <sub>FBB</sub>         | 1    | RES, 2.0 k, 5%, 0.1 W, AEC-Q200 Grade 0, 0603                                            | Vishay-Dale   | CRCW06032K00JNEA     |

| L <sub>M</sub>           | 1    | Inductor, Shielded, Composite, 6.8 uH, 18.5 A, 0.01 ohm, SMD                             | Coilcraft     | XAL1010-682MEB       |

| R <sub>S</sub>           | 1    | RES, 0.008, 1%, 3 W, AEC-Q200 Grade 0, 2512 WIDE                                         | Susumu        | KRL6432E-M-R008-F-T1 |

| R <sub>SL</sub>          | 1    | RES, 0, 5%, 0.1 W, 0603                                                                  | Yageo America | RC0603JR-070RL       |

| C <sub>OUT1</sub>        | 3    | CAP, CERM, 4.7 uF, 50 V, +/- 10%, X7R, 1210                                              | TDK           | C3225X7R1H475K250AB  |

| C <sub>OUT2</sub> (Bulk) | 2    | CAP, Aluminum Polymer, 100 uF, 50 V, +/- 20%, 0.025 ohm, AEC-Q200 Grade 2, D10xL10mm SMD | Chemi-Con     | HHXB500ARA101MJA0G   |

| C <sub>IN1</sub>         | 6    | CAP, CERM, 10 uF, 50 V, +/- 10%, X7R, 1210                                               | MuRata        | GRM32ER71H106KA12L   |

| C <sub>IN2</sub> (Bulk)  | 1    | CAP, Polymer Hybrid, 100 uF, 50 V, +/- 20%, 28 ohm, 10x10 SMD                            | Panasonic     | EEHZC1H101P          |

| Q1                       | 1    | MOSFET, N-CH, 40 V, 50 A, AEC-Q101, SON-8                                                | Infineon      | IPC50N04S5L5R5ATMA1  |

| D1                       | 1    | Schottky, 60 V, 10 A, AEC-Q101, CFP15                                                    | Nexperia      | PMEG060V100EPDZ      |

| R <sub>COMP</sub>        | 1    | RES, 11.3 k, 1%, 0.1 W, AEC-Q200 Grade 0, 0603                                           | Vishay-Dale   | CRCW060311K3FKEA     |

| C <sub>COMP</sub>        | 1    | CAP, CERM, 0.022 uF, 100 V, +/- 10%, X7R, AEC-Q200<br>Grade 1, 0603                      | TDK           | CGA3E2X7R2A223K080AA |

| C <sub>HF</sub>          | 1    | CAP, CERM, 220 pF, 20 V, +/- 5%, C0G/NP0, AEC-<br>Q200 Grade 1, 0603                     | TDK           | CGA3E2C0G1H221J080AA |

| R <sub>UVLOT</sub>       | 1    | RES, 21.0 k, 1%, 0.1 W, AEC-Q200 Grade 0, 0603                                           | Vishay-Dale   | CRCW060321K0FKEA     |

| R <sub>UVLOB</sub>       | 1    | RES, 7.32 k, 1%, 0.1 W, AEC-Q200 Grade 0, 0603                                           | Vishay-Dale   | CRCW06037K32FKEA     |

| R <sub>UVLOS</sub>       | 0    | N/A                                                                                      | N/A           | N/A                  |

| C <sub>SS</sub>          | 1    | CAP, CERM, 0.22 uF, 50 V, +/- 10%, X7R, AEC-Q200<br>Grade 1, 0603                        | TDK           | CGA3E3X7R1H224K080AB |

| $D_G$                    | 0    | N/A                                                                                      | N/A           | N/A                  |

(1) See Third-party Products Disclaimer

# Table 2. List of Materials<sup>()</sup> (continued)

| REFERENCE DESIGNATOR | QTY. | SPECIFICATION                                                  | MANUFACTURER                  | PART NUMBER        |

|----------------------|------|----------------------------------------------------------------|-------------------------------|--------------------|

| $R_{G}$              | 1    | RES, 0, 5%, 0.1 W, 0603                                        | Yageo America                 | RC0603JR-070RL     |

| $C_F$                | 1    | CAP, CERM, 100 pF, 50 V,+/- 1%, C0G/NP0, 0603                  | Kemet                         | C0603C101F5GACTU   |

| $R_{F}$              | 1    | RES, 100, 1%, 0.1 W, 0603                                      | Yageo America                 | RC0603FR-07100RL   |

| R <sub>SNB</sub>     | 0    | N/A                                                            | N/A                           | N/A                |

| C <sub>SNB</sub>     | 0    | N/A                                                            | N/A                           | N/A                |

| R <sub>BIAS</sub>    | 1    | RES, 0, 5%, 0.1 W, AEC-Q200 Grade 0, 0603                      | Panasonic                     | ERJ-3GEY0R00V      |

| C <sub>BIAS</sub>    | 1    | CAP, CERM, 0.01 uF, 50 V, +/- 10%, X7R, 0603                   | Samsung Electro-<br>Mechanics | CL10B103KB8NCNC    |

| C <sub>VCC</sub>     | 1    | CAP, CERM, 1 uF, 16 V, +/- 20%, X7R, AEC-Q200<br>Grade 1, 0603 | MuRata                        | GCM188R71C105MA64D |

| R <sub>PG</sub>      | 1    | RES, 24.9 k, 1%, 0.1 W, 0603                                   | Yageo America                 | RC0603FR-0724K9L   |

#### 10.2.2.3 Inductor Selection (L<sub>M</sub>)

When selecting the inductor, consider three key parameters: inductor current ripple ratio (RR), falling slope of the inductor current, and RHP zero frequency (f<sub>RHP</sub>).

Inductor current ripple ratio is selected to have a balance between core loss and copper loss. The falling slope of the inductor current must be low enough to prevent sub-harmonic oscillation at high duty cycle (additional  $R_{SL}$  resistor is required if not). Higher  $f_{RHP}$  (= lower inductance) allows a higher crossover frequency and is always preferred when using a small value output capacitor.

The inductance value can be selected to set the inductor current ripple between 30% and 70% of the average inductor current as a good compromise between RR, F<sub>RHP</sub> and inductor falling slope.

# 10.2.2.4 Output Capacitor (C<sub>OUT</sub>)

There are a few ways to select the proper value of output capacitor (C<sub>OUT</sub>). The output capacitor value can be selected based on output voltage ripple, output overshoot or undershoot due to load transient.

The ripple current rating of the output capacitors must be enough to handle the output ripple current. By using multiple output capacitors, the ripple current can be split. In practice, ceramic capacitors are placed closer to the diode and the MOSFET than the bulk aluminum capacitors in order to absorb the majority of the ripple current.

#### 10.2.2.5 Input Capacitor

The input capacitors decrease the input voltage ripple. The required input capacitor value is a function of the impedance of the source power supply. More input capacitors are required if the impedance of the source power supply is not low enough.

#### 10.2.2.6 MOSFET Selection

The MOSFET gate driver of the device is sourced from the VCC. The maximum gate charge is limited by the 35-mA VCC sourcing current limit.

A leadless package is preferred for high switching-frequency designs. The MOSFET gate capacitance should be small enough so that the gate voltage is fully discharged during the off-time.

#### 10.2.2.7 Diode Selection

A Schottky is the preferred type for D1 diode due to its low forward voltage drop and small reverse recovery charge. Low reverse leakage current is important parameter when selecting the Schottky diode. The diode must be rated to handle the maximum output voltage plus any switching node ringing. Also, it must be able to handle the average output current.

Product Folder Links: LM5155 LM51551

#### 10.2.2.8 Efficiency Estimation

The total loss of the boost converter ( $P_{TOTAL}$ ) can be expressed as the sum of the losses in the device ( $P_{IC}$ ), MOSFET power losses ( $P_{Q}$ ), diode power losses ( $P_{D}$ ), inductor power losses ( $P_{L}$ ), and the loss in the sense resistor ( $P_{RS}$ ).

$$P_{TOTAL} = P_{IC} + P_{Q} + P_{D} + P_{L} + P_{RS}$$

(19)

P<sub>IC</sub> can be separated into gate driving loss (P<sub>G</sub>) and the losses caused by quiescent current (P<sub>IQ</sub>).

$$P_{IC} = P_G + P_{IQ} \tag{20}$$

Each power loss is approximately calculated as follows:

$$P_{G} = Q_{G(@VCC)} \times V_{BIAS} \times f_{SW}$$

(21)

$$P_{IQ} = V_{BIAS} \times I_{BIAS} \tag{22}$$

$I_{VIN}$  and  $I_{VOUT}$  values in each mode can be found in the supply current section of the *Electrical Characteristics* table

$P_Q$  can be separated into switching loss ( $P_{Q(SW)}$ ) and conduction loss ( $P_{Q(COND)}$ ).

$$P_{Q} = P_{Q(SW)} + P_{Q(COND)}$$

(23)

Each power loss is approximately calculated as follows:

$$P_{Q(SW)} = 0.5 \times (V_{LOAD} + V_F) \times I_{SUPPLY} \times (t_R + t_F) \times f_{SW}$$

(24)

$t_R$  and  $t_F$  are the rise and fall times of the low-side N-channel MOSFET device.  $I_{SUPPLY}$  is the input supply current of the boost converter.

$$P_{Q(COND)} = D \times I_{SUPPLY}^{2} \times R_{DS(ON)}$$

(25)

$R_{DS(ON)}$  is the on-resistance of the MOSFET and is specified in the MOSFET data sheet. Consider the  $R_{DS(ON)}$  increase due to self-heating.

P<sub>D</sub> can be separated into diode conduction loss (P<sub>VF</sub>) and reverse recovery loss (P<sub>RR</sub>).

$$P_{D} = P_{VF} + P_{RR} \tag{26}$$

Each power loss is approximately calculated as follows:

$$P_{VF} = (1 - D) \times V_F \times I_{SUPPLY}$$

(27)

$$P_{RR} = V_{LOAD} \times Q_{RR} \times f_{SW}$$

(28)

Q<sub>RR</sub> is the reverse recovery charge of the diode and is specified in the diode datasheet. Reverse recovery characteristics of the diode strongly affect efficiency, especially when the output voltage is high.

$P_L$  is the sum of DCR loss ( $P_{DCR}$ ) and AC core loss ( $P_{AC}$ ). DCR is the DC resistance of inductor which is mentioned in the inductor data sheet.

$$P_{L} = P_{DCR} + P_{AC} \tag{29}$$

Each power loss is approximately calculated as follows:

$$P_{DCR} = I_{SUPPLY}^2 \times R_{DCR}$$

(30)

$$P_{AC} = K \times \Delta I^{\beta} \times f_{SW}^{\alpha}$$

(31)

Submit Documentation Feedback

Copyright © 2018–2020, Texas Instruments Incorporated

$$\Delta I = \frac{V_{SUPPLY} \times D \times \frac{1}{f_{SW}}}{L_{M}}$$

(32)

$\Delta I$  is the peak-to-peak inductor current ripple. K,  $\alpha$ , and  $\beta$  are core dependent factors which can be provided by the inductor manufacturer.

P<sub>RS</sub> is calculated as follows:

$$P_{RS} = D \times I_{SUPPLY}^2 \times R_S \tag{33}$$

Efficiency of the power converter can be estimated as follows:

$$Efficiency = \frac{V_{LOAD} \times I_{LOAD}}{P_{TOTAL} + V_{LOAD} \times I_{LOAD}}$$

(34)

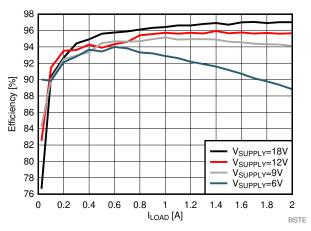

# 10.2.3 Application Curve

Figure 38. Efficiency

# 10.3 System Examples

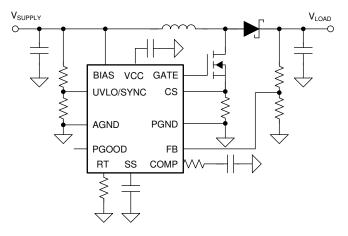

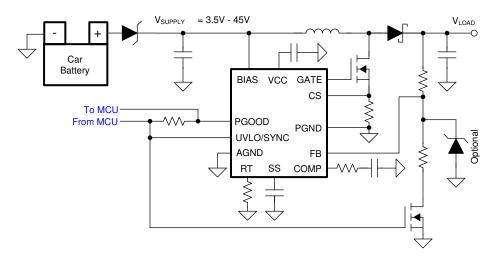

Figure 39. Typical Boost Application

Copyright © 2018–2020, Texas Instruments Incorporated

Figure 40. Typical Start-Stop Application

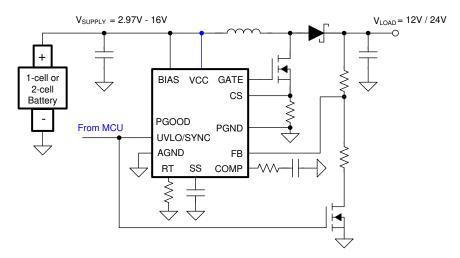

Figure 41. Emergency-call / Boost On-Demand / Portable Speaker

Figure 42. Typical SEPIC Application

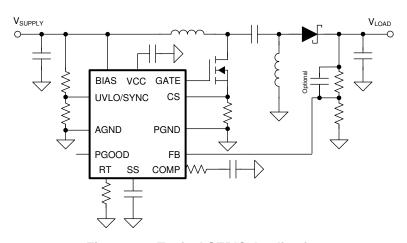

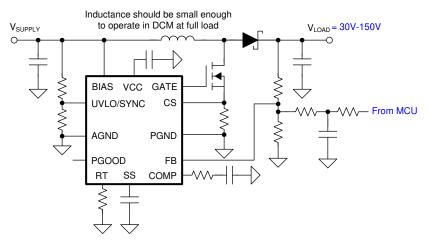

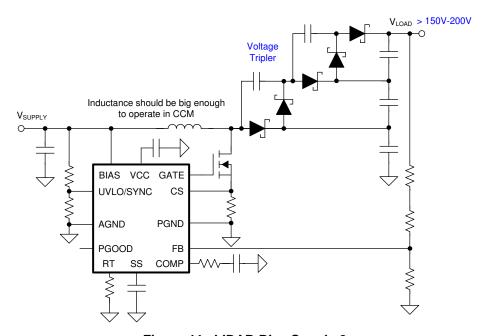

Figure 43. LIDAR Bias Supply 1

Figure 44. LIDAR Bias Supply 2

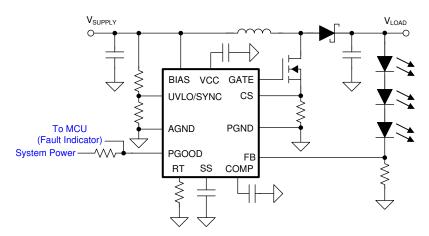

Figure 45. Low-Cost LED Driver

Figure 46. Secondary-Side Regulated Isolated Flyback

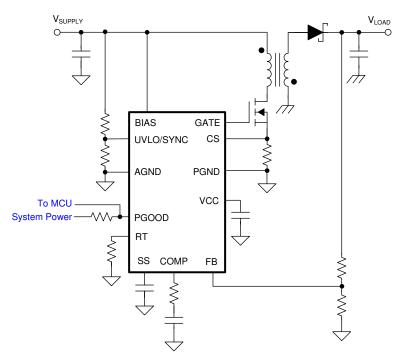

Figure 47. Primary-Side Regulated Multiple-Output Isolated Flyback

Figure 48. Typical Non-Isolated Flyback

Figure 49. LED Driver with High-Side Current Sensing

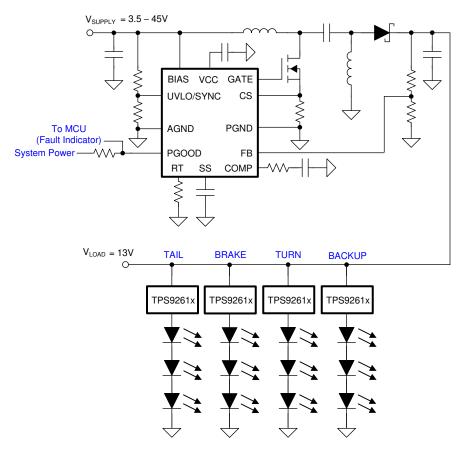

Figure 50. Dual-Stage Automotive Rear-Lights LED Driver

# 11 Power Supply Recommendations

The device is designed to operate from a power supply or a battery whose voltage range is from 1.5 V to 45 V. The input power supply must be able to supply the maximum boost supply voltage and handle the maximum input current at 1.5 V. The impedance of the power supply and battery including cables must be low enough that an input current transient does not cause an excessive drop. Additional input ceramic capacitors may be required at the supply input of the converter.

# 12 Layout

# 12.1 Layout Guidelines

The performance of switching converters heavily depends on the quality of the PCB layout. The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimize generation of unwanted EMI.

- Put the Q1, D1, and R<sub>S</sub> components on the board first.

- Use a small size ceramic capacitor for C<sub>OUT</sub>.

- Make the switching loop (C<sub>OUT</sub> to D1 to Q1 to R<sub>S</sub> to C<sub>OUT</sub>) as small as possible.

- Leave a copper area near the D1 diode for thermal dissipation.

- Put the device near the R<sub>S</sub> resistor.

- Put the C<sub>VCC</sub> capacitor as near the device as possible between the VCC and PGND pins.

- Use a wide and short trace to connect the PGND pin directly to the center of the sense resistor.

- Connect the CS pin to the center of the sense resistor. If necessary, use vias.

- Connect a filter capacitor between CS pin and power ground trace.

- Connect the COMP pin to the compensation components (R<sub>COMP</sub> and C<sub>COMP</sub>).

- Connect the C<sub>COMP</sub> capacitor to the power ground trace.

- Connect the AGND pin directly to the analog ground plane. Connect the AGND pin to the R<sub>UVLOB</sub>, R<sub>T</sub>, C<sub>SS</sub>, and R<sub>FBB</sub> components.

- Connect the exposed pad to the AGND and PGND pins under the device.

- Connect the GATE pin to the gate of the Q1 FET. If necessary, use vias.

- Make the switching signal loop (GATE to Q1 to R<sub>S</sub> to PGND to GATE) as small as possible.

- Add several vias under the exposed pad to help conduct heat away from the device. Connect the vias to a large ground plane on the bottom layer.

Submit Documentation Feedback

Copyright © 2018–2020, Texas Instruments Incorporated

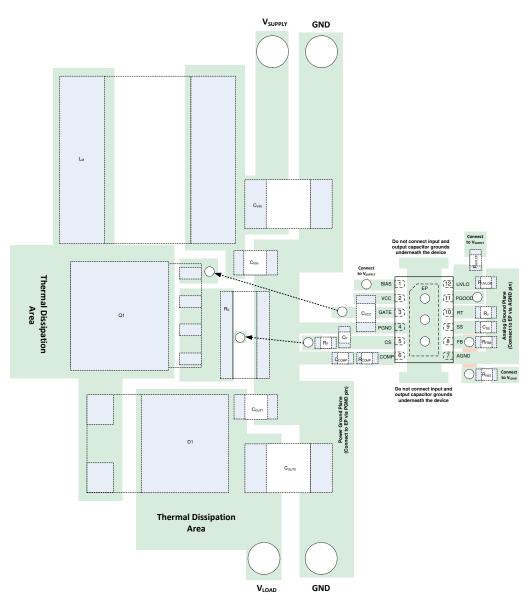

# 12.2 Layout Examples

Figure 51. PCB Layout Example 1

Product Folder Links: LM5155 LM51551

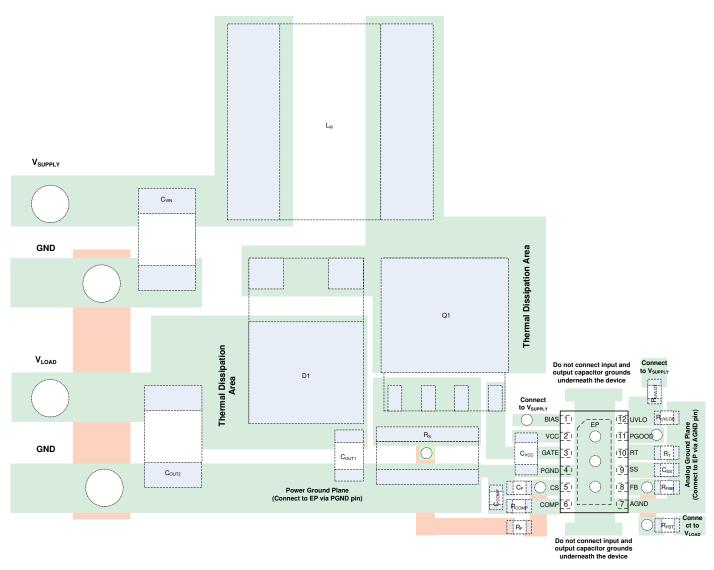

# **Layout Examples (continued)**

Figure 52. PCB Layout Example 2

Product Folder Links: LM5155 LM51551

# 13 Device and Documentation Support

### 13.1 Device Support

### 13.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 13.1.2 Development Support

For development support see the following:

LM5155 Boost Controller Quick Start Calculator

### 13.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM5155x device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , and output current  $(I_{OUT})$  requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 13.2 Documentation Support

#### 13.2.1 Related Documentation

For related documentation see the following:

Copyright © 2018-2020, Texas Instruments Incorporated

- Texas Instruments, LM5155EVM-BST User's Guide

- Texas Instruments, How to Design a Boost Converter Using LM5155-Q1

- Texas Instruments, LM5155EVM-FLY User's Guide

- Texas Instruments, How to Design an Isolated Flyback Converter Using LM5155-Q1

### 13.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

**Table 3. Related Links**

| PARTS   | PRODUCT FOLDER | ORDER NOW  | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|---------|----------------|------------|---------------------|---------------------|---------------------|

| LM5155  | Click here     | Click here | Click here          | Click here          | Click here          |

| LM51551 | Click here     | Click here | Click here          | Click here          | Click here          |

Draduat Folder Links, IME455 IME4

### 13.4 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on Alert me to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 13.5 Community Resources

TI E2ETM support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 13.6 Trademarks

E2E is a trademark of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

## **Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 13.8 Glossary

SLYZ022 — TI Glossary.

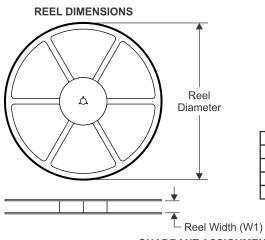

This glossary lists and explains terms, acronyms, and definitions.