# LM9076Q 150mA Ultra-Low Quiescent Current LDO Regulator with Delayed Reset Output

Check for Samples: LM9076Q

### **FEATURES**

- AEC-Q100 Grade1 Qualified (-40°C to +125°C)

- Available with 5.0V or 3.3V Output Voltage

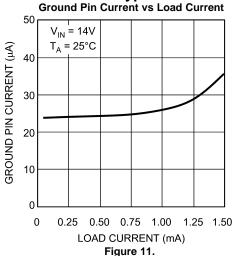

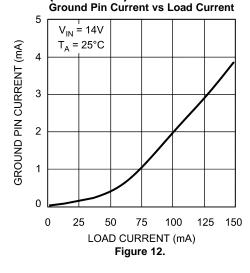

- Ultra Low Ground Pin Current, 25 μA Typical for 100 μA Load

- V<sub>OUT</sub> Initial Accuracy of ±1.5%

- V<sub>OUT</sub> Accurate to ±3% Over Load and Temperature Conditions

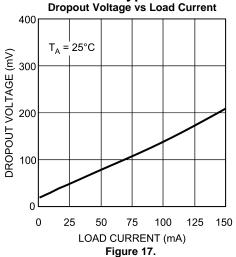

- Low Dropout Voltage, 200 mV Typical with 150 mA Load

- Low Off State Ground Pin Current for LM9076QBMA

- Delayed RESET Output Pin for Low V<sub>OUT</sub> Detection

- +70V/-50V Voltage Transients

- Operational V<sub>IN</sub> up to +40V

#### DESCRIPTION

The LM9076Q is a ±3%, 150 mA logic controlled voltage regulator. The regulator features an active low delayed reset output flag which can be used to reset a microprocessor system at turn-ON and in the event that the regulator output voltage falls below a minimum value. An external capacitor programs a delay time interval before the reset output pin can return high.

Designed for automotive and industrial applications, the LM9076Q contains a variety of protection features such as thermal shutdown, input transient protection and a wide operating temperature range. The LM9076Q uses an PNP pass transistor which allows low drop-out voltage operation.

₩.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

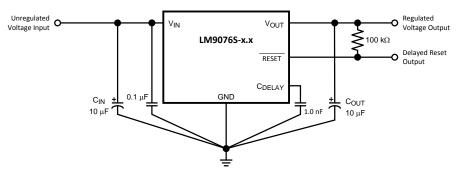

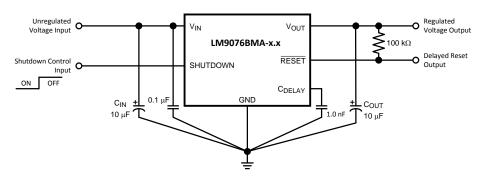

## **Typical Applications**

Figure 1. LM9076QS-x.x In 5 lead SFM package

Figure 2. LM9076QBMA-x.x in 8 lead SOIC package

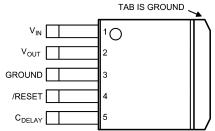

## **Connection Diagram**

Figure 4. Top View See SOIC Package Number D0008A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Submit Documentation Feedback

## Absolute Maximum Ratings (1)(2)

| V <sub>IN</sub> (DC)                                 | -15V to +55V                    |

|------------------------------------------------------|---------------------------------|

| V <sub>IN</sub> (+Transient) t< 10ms, Duty Cycle <1% | +70V                            |

| V <sub>IN</sub> (-Transient) t< 1ms, Duty Cycle <1%  | -50V                            |

| SHUTDOWN Pin                                         | -15V to +52V                    |

| RESET Pin                                            | -0.3V to 20V                    |

| C <sub>DELAY</sub> Pin                               | -0.3V to V <sub>OUT</sub> +0.3V |

| Storage Temperature                                  | -65°C to +150°C                 |

| Junction Temperature (T <sub>J</sub> )               | +175C                           |

| ESD, HBM, per AEC - Q100 - 002                       | +/-2 kV                         |

| ESD, MM, per AEC - Q100 - 003                        | +/-250V                         |

Absolute Maximum Ratings indicate the limits beyond which the device may cease to function, and/or damage to the device may occur.

## Operating Ratings (1)

| V <sub>IN</sub> Pin                        | 5.35V to 40V                    |         |

|--------------------------------------------|---------------------------------|---------|

| V <sub>SHUTDOWN</sub> Pin                  | 0V to 40V                       |         |

| Junction Temperature                       | -40°C < T <sub>J</sub> < +125°C |         |

| Thermal Resistance KTT0005B <sup>(2)</sup> | θја                             | 75°C/W  |

|                                            | θјс                             | 2.9°C/W |

| Thermal Resistance D0008A (2)              | θja                             | 156°C/W |

|                                            | θјс                             | 59°C/W  |

Absolute Maximum Ratings indicate the limits beyond which the device may cease to function, and/or damage to the device may occur.

Copyright © 2011-2013, Texas Instruments Incorporated

#### Electrical Characteristics for LM9076Q-3.3

The following specifications apply for  $V_{\text{IN}}$  = 14V;  $I_{\text{LOAD}}$  = 10 mA;  $T_{\text{J}}$  = +25C;  $C_{\text{OUT}}$  = 10  $\mu\text{F}$ ,  $0.5\Omega$  < ESR < 4.0 $\Omega$ ; unless otherwise specified. **Bold values indicate -40°C**  $\leq$   $T_{\text{J}}$   $\leq$  +125°C. (1) (2) Minimum and Maximum limits are specified through test, design or statistical correlation.

| Symbol                  | Parameter                              | Conditions                                                                                | Min   | Тур  | Max   | Units |

|-------------------------|----------------------------------------|-------------------------------------------------------------------------------------------|-------|------|-------|-------|

| LM9076Q-3.3 REGULATOR C | CHARACTERISTICS                        |                                                                                           |       |      |       | •     |

|                         |                                        |                                                                                           | 3.251 | 3.30 | 3.349 | V     |

|                         | Output Voltage                         | $-20$ °C $\leq$ T <sub>J</sub> $\leq$ 85°C<br>1 mA $\leq$ I <sub>LOAD</sub> $\leq$ 150 mA | 3.234 | 3.30 | 3.366 | V     |

|                         | Output voltage                         | $1\text{mA} \le I_{\text{LOAD}} \le 150 \text{ mA}$                                       | 3.201 | 3.30 | 3.399 | V     |

| $V_{OUT}$               |                                        | $V_{IN} = 60V$ ,<br>$R_{LOAD} = 1 \text{ k}\Omega$ , $t \le 40\text{ms}$                  | 2.970 | 3.30 | 3.630 | V     |

|                         | Output Voltage Off<br>LM9076Q BMA only | $V_{SHUTDOWN} \ge 2V$ , $R_{LOAD} = 1 \text{ k}\Omega$                                    | -     | 0    | 250   | mV    |

|                         | Reverse Battery                        | $V_{IN} = -15V,$ $R_{LOAD} = 1 \text{ k}\Omega$                                           | -300  | 0    | _     | mV    |

|                         | Line Degulation                        | $9.0V \le V_{IN} \le 16V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                 | -     | 4    | 25    | mV    |

| $\Delta V_{OUT}$        | Line Regulation                        | $16V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                  | _     | 17   | 35    | mV    |

|                         | Load Regulation                        | 1 mA ≤ I <sub>LOAD</sub> ≤ 150 mA                                                         |       | 42   | 60    | mV    |

The regulated output voltage specification is not ensured for the entire range of V<sub>IN</sub> and output loads. Device operational range is limited by the maximum junction temperature (T  $_{\rm J}$ ). The junction temperature is influenced by the ambient temperature (T  $_{\rm A}$ ), package selection, input voltage (VIN), and the output load current. When operating with maximum load currents the input voltage and/or ambient temperature will be limited. When operating with maximum input voltage the load current and/or the ambient temperature will be limited. Pulse testing used maintain constant junction temperature (T<sub>J</sub>).

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

Worst case (FREE AIR) per EIA/JESD51-3.

## Electrical Characteristics for LM9076Q-3.3 (continued)

The following specifications apply for  $V_{IN}$  = 14V;  $I_{LOAD}$  = 10 mA;  $T_J$  = +25C;  $C_{OUT}$  = 10  $\mu$ F, 0.5 $\Omega$  < ESR < 4.0 $\Omega$ ; unless otherwise specified. **Bold values indicate** -40°C  $\leq T_J \leq$  +125°C. (1) (2) Minimum and Maximum limits are specified through test, design or statistical correlation.

| Symbol                              | Parameter                                      | Conditions                                                                                                                         | Min                     | Тур                     | Max       | Units                    |

|-------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----------|--------------------------|

|                                     |                                                | I <sub>LOAD</sub> = 10 mA                                                                                                          | _                       | 30                      | 50        | mV                       |

| $V_{DO}$                            | Dropout Voltage                                | $I_{LOAD} = 50 \text{ mA}$                                                                                                         | _                       | 80                      | -         | mV                       |

|                                     |                                                | $I_{LOAD} = 150 \text{ mA}$                                                                                                        | _                       | 150                     | 250       | mV                       |

|                                     |                                                | 9V ≤ V <sub>IN</sub> ≤ 16V,<br>I <sub>LOAD</sub> = 100 uA                                                                          | _                       | 25                      | 45        | μA                       |

|                                     | Ground Pin Current                             | $9V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                                                            | _                       | 125                     | 160       | μА                       |

| I <sub>GND</sub>                    | Ground Pin Current                             | $9V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 50 \text{ mA}$                                                                            | _                       | 0.6                     | -         | mA                       |

|                                     |                                                | $9V \le V_{IN} \le 16V$ ,<br>$I_{LOAD} = 150 \text{ mA}$                                                                           | _                       | 3.6                     | 4.5       | mA                       |

| I <sub>SC</sub>                     | V <sub>OUT</sub> Short Circuit<br>Current      | $V_{IN} = 14V,$<br>$R_{LOAD} = 1\Omega$                                                                                            | 200                     | 400                     | 750       | mA                       |

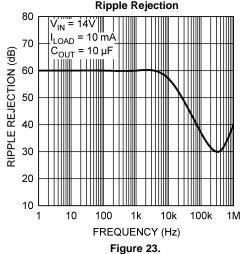

| PSRR                                | Ripple Rejection                               | $V_{IN} = (14V_{DC}) + (1V_{RMS})$<br>@ 120Hz)<br>$I_{LOAD} = 50 \text{ mA}$                                                       | 50                      | 60                      | -         | dB                       |

| RESET PIN CHARACTERIST              | TICS                                           |                                                                                                                                    |                         |                         |           |                          |

| $V_{OR}$                            | Minimum V <sub>IN</sub> for valid RESET Status |                                                                                                                                    | (3)_                    | 1.3                     | 2.0       | V                        |

| $V_{THR}$                           | V <sub>OUT</sub> Threshold for RESET Low       | (3)                                                                                                                                | 0.83                    | 0.89                    | 0.94      | X V <sub>OUT</sub> (Nom) |

| V <sub>OH</sub>                     | RESET pin high voltage                         | External pull-up resistor to $V_{OUT} = 100 \text{ k}\Omega$                                                                       | V <sub>OUT</sub> X 0.90 | V <sub>OUT</sub> X 0.99 | $V_{OUT}$ | V                        |

| $V_{OL}$                            | RESET pin low voltage                          | C <sub>DELAY</sub> < 4.0V,<br>I <sub>SINK</sub> = 250 μA                                                                           | _                       | 0.2                     | 0.3       | V                        |

| C <sub>DELAY</sub> PIN CHARACTERIST | TICS                                           |                                                                                                                                    |                         |                         |           |                          |

| I <sub>DELAY</sub>                  | C <sub>DELAY</sub> Charging<br>Current         | $V_{IN} = 14V,$<br>$V_{DELAY} = 0V$                                                                                                | -0.70                   | -0.42                   | -0.25     | uA                       |

| V <sub>OL</sub>                     | C <sub>DELAY</sub> pin low voltage             | V <sub>OUT</sub> < 4.0V,<br>I <sub>SINK</sub> = I <sub>DELAY</sub>                                                                 | _                       | 0.100                   | -         | V                        |

| tDELAY                              | Reset Delay Time                               | $V_{IN}$ = 14V, $C_{DELAY}$ = 0.001 uF<br>$V_{OUT}$ rising from 0V, $\Delta t$<br>$from \ V_{OUT}$ > $V_{OR}$ to<br>RESET pin HIGH | 4.7                     | 7.8                     | 13.2      | ms                       |

<sup>(3)</sup> Not Production tested, Specified by Design. Minimum, Typical, and/or Maximum values are provided for informational purposes only.

## Electrical Characteristics for LM9076Q-5.0

The following specifications apply for  $V_{IN}$ = 14V;  $V_{SHUTDOWN}$  = Open;  $I_{LOAD}$  = 10 mA;  $T_J$  = +25°C;  $C_{OUT}$  = 10  $\mu$ F, 0.5 $\Omega$  < ESR < 4.0 $\Omega$ ; unless otherwise specified. **Bold Values indicate** -40°C  $\leq T_J \leq$  125°C. (1), (2) Minimum and Maximum limits are specified through test design or statistical correlation.

| Symbol                           | Parameter                                                | Conditions                                                                                | Min                     | Тур                     | Max              | Units                   |

|----------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|-------------------------|------------------|-------------------------|

| _M9076Q-5.0 REGULAT              | OR CHARACTERISTICS                                       | 1                                                                                         |                         | 1                       |                  | <b>U</b> I              |

|                                  |                                                          |                                                                                           | 4.925                   | 5.00                    | 5.075            | V                       |

|                                  | Outrast Walks as                                         | $-20$ °C $\leq$ T <sub>J</sub> $\leq$ 85°C<br>1 mA $\leq$ I <sub>LOAD</sub> $\leq$ 150 mA | 4.900                   | 5.00                    | 5.100            | V                       |

|                                  | Output Voltage                                           | 1 mA ≤ I <sub>LOAD</sub> ≤ 150 mA                                                         | 4.850                   | 5.00                    | 5.150            | V                       |

| $V_{OUT}$                        |                                                          | $V_{IN} = 60V$ ,<br>$R_{LOAD} = 1 \text{ k}\Omega$ , $t \le 40\text{ms}$                  | 4.500                   | 5.00                    | 5.500            | V                       |

|                                  | Output Voltage Off<br>LM9076Q BMA only                   | $V_{SHUTDOWN} \ge 2V$ , $R_{LOAD} = 1 \text{ k}\Omega$                                    | _                       | 0                       | 250              | mV                      |

|                                  | Reverse Battery                                          | $V_{IN} = -15V$ ,<br>$R_{LOAD} = 1 \text{ k}\Omega$                                       | -300                    | 0                       | -                | mV                      |

|                                  | Line Regulation                                          | $9.0V \le V_{IN} \le 16V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                 | _                       | 4                       | 25               | mV                      |

| $\Delta V_{OUT}$                 | Line Regulation                                          | $16V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                  | _                       | 17                      | 35               | mV                      |

|                                  | Load Regulation                                          | 1 mA ≤ I <sub>LOAD</sub> ≤ 150 mA                                                         | _                       | 42                      | 60               | mV                      |

|                                  |                                                          | I <sub>LOAD</sub> = 10 mA                                                                 | _                       | 30                      | 50               | mV                      |

| $V_{DO}$                         | Dropout Voltage                                          | $I_{LOAD} = 50 \text{ mA}$                                                                | _                       | 80                      | _                | mV                      |

|                                  |                                                          | $I_{LOAD} = 150 \text{ mA}$                                                               | _                       | 150                     | 250              | mV                      |

|                                  |                                                          | $9V \le V_{IN} \le 16V$ ,<br>$I_{LOAD} = 100 \text{ uA}$                                  | _                       | 25                      | 45               | μA                      |

|                                  | Ground Pin Current                                       | $9V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 10 \text{ mA}$                                   | _                       | 125                     | 160              | μA                      |

| $I_{GND}$                        | Glound Fill Culterit                                     | $9V \le V_{IN} \le 40V$ ,<br>$I_{LOAD} = 50 \text{ mA}$                                   | _                       | 0.6                     | -                | mA                      |

|                                  |                                                          | 9V ≤ V <sub>IN</sub> ≤ 16V,<br>I <sub>LOAD</sub> = 150 mA                                 | _                       | 3.6                     | 4.5              | mA                      |

|                                  | Ground Pin Current in<br>Shutdown Mode                   | $9V \le V_{IN} \le 40V$ ,<br>$V_{SHUTDOWN} = 2V$                                          | _                       | 15                      | 25               | μА                      |

| I <sub>SC</sub>                  | V <sub>OUT</sub> Short Circuit<br>Current                | $V_{IN} = 14V,$<br>$R_{LOAD} = 1\Omega$                                                   | 200                     | 400                     | 750              | mA                      |

| PSRR                             | Ripple Rejection                                         | $V_{IN} = (14V_{DC}) + (1V_{RMS})$<br>@ 120Hz)<br>$I_{LOAD} = 50 \text{ mA}$              | 50                      | 60                      | -                | dB                      |

| RESET PIN CHARACTER              | RISTICS                                                  |                                                                                           |                         |                         |                  | 1                       |

| $V_{OR}$                         | Min <u>imum V<sub>IN</sub> for valid</u><br>RESET Status |                                                                                           | (3)                     | 1.3                     | 2.0              | V                       |

| $V_{THR}$                        | V <sub>OUT</sub> Threshold for RESET Low                 | (3)                                                                                       | 0.83                    | 0.89                    | 0.94             | X V <sub>OU</sub> (Nom) |

| $V_{OH}$                         | RESET pin high voltage                                   | External pull-up resistor to $V_{OUT} = 100 \text{ k}\Omega$                              | V <sub>OUT</sub> X 0.90 | V <sub>OUT</sub> X 0.99 | V <sub>OUT</sub> | V                       |

| $V_{OL}$                         | RESET pin low voltage                                    | C <sub>DELAY</sub> < 4.0V,<br>I <sub>SINK</sub> = 250 μA                                  | _                       | 0.2                     | 0.3              | V                       |

| C <sub>DELAY</sub> PIN CHARACTER | RISTICS                                                  |                                                                                           |                         | ,                       |                  |                         |

| I <sub>DELAY</sub>               | C <sub>DELAY</sub> Charging<br>Current                   | V <sub>IN</sub> = 14V,<br>V <sub>DELAY</sub> = 0V                                         | -0.70                   | -0.42                   | -0.25            | uA                      |

<sup>(1)</sup> Pulse testing used maintain constant junction temperature (T<sub>J</sub>).

(2) The regulated output voltage specification is not ensured for the entire range of V<sub>IN</sub> and output loads. Device operational range is limited by the maximum junction temperature (T  $_{\rm J}$ ). The junction temperature is influenced by the ambient temperature (T  $_{\rm A}$ ), package selection, input voltage (V $_{\rm IN}$ ), and the output load current. When operating with maximum load currents the input voltage and/or ambient temperature will be limited. When operating with maximum input voltage the load current and/or the ambient temperature will be limited. Not Production tested, Specified by Design. Minimum, Typical, and/or Maximum values are provided for informational purposes only.

## Electrical Characteristics for LM9076Q-5.0 (continued)

The following specifications apply for  $V_{IN}$ = 14V;  $V_{SHUTDOWN}$  = Open;  $I_{LOAD}$  = 10 mA;  $T_J$  = +25°C;  $C_{OUT}$  = 10  $\mu$ F, 0.5 $\Omega$  < ESR < 4.0 $\Omega$ ; unless otherwise specified. **Bold Values indicate** -40°C  $\leq T_J \leq$  125°C. (1), (2) Minimum and Maximum limits are specified through test, design, or statistical correlation.

| Symbol              | Parameter                              | Conditions                                                                                                                                                                                                                                                   | Min | Тур   | Max  | Units    |

|---------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|----------|

| V <sub>OL</sub>     | C <sub>DELAY</sub> pin low voltage     | $S_{DELAY}$ pin low voltage $V_{OUT} < 4.0V$ , $I_{SINK} = I_{DELAY}$                                                                                                                                                                                        |     | 0.100 | _    | ٧        |

| tDELAY              | Reset Delay Time                       | $\begin{aligned} &V_{\text{IN}} = 14\text{V, } C_{\text{DELAY}} = \\ &0.001 \text{ uF} \\ &V_{\text{OUT}} \text{ rising from 0V, } \Delta t \\ &\underline{\text{from } V_{\text{OUT}}} > V_{\text{OR}} \text{ to} \\ &RESET \text{ pin HIGH} \end{aligned}$ | 7.1 | 11.9  | 20.0 | ms       |

| SHUTDOWN CONTROL L  | OGIC — LM9076QBMA-5.0                  | Only                                                                                                                                                                                                                                                         |     |       | •    | ,        |

| $V_{IL(SD)}$        | SHUTDOWN Pin Low<br>Threshold Voltage  | V <sub>SHUTDOWN</sub> pin falling<br>from 5.0V until V <sub>OUT</sub><br>>4.5V (V <sub>OUT</sub> = On)                                                                                                                                                       | 1   | 1.5   | _    | <b>\</b> |

| V <sub>IH(SD)</sub> | SHUTDOWN Pin High<br>Threshold Voltage | V <sub>SHUTDOWN</sub> pin rising<br>from 0V until V <sub>OUT</sub> <<br>0.5V (V <sub>OUT</sub> = Off)                                                                                                                                                        | -   | 1.5   | 2    | <b>\</b> |

|                     |                                        | V <sub>SHUTDOWN</sub> = 40V                                                                                                                                                                                                                                  | -   | 35    | _    | μA       |

| I <sub>IH(SD)</sub> | SHUTDOWN Pin High<br>Bias Current      | V <sub>SHUTDOWN</sub> = 5V                                                                                                                                                                                                                                   | =   | 15    | 35   | μA       |

|                     | Bias ourion                            | V <sub>SHUTDOWN</sub> = 2V                                                                                                                                                                                                                                   | =   | 6     | 10   | μA       |

| I <sub>IL(SD)</sub> | SHUTDOWN Pin Low<br>Bias Current       | V <sub>SHUTDOWN</sub> = 0V                                                                                                                                                                                                                                   | _   | 0     | _    | μA       |

Product Folder Links: LM9076Q

Submit Documentation Feedback

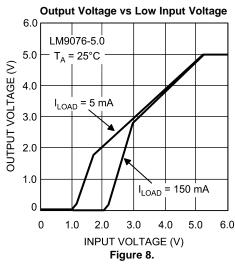

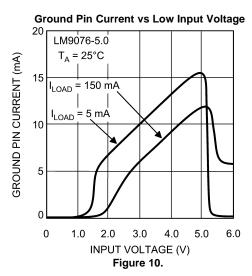

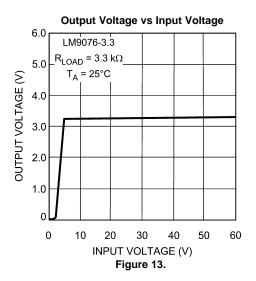

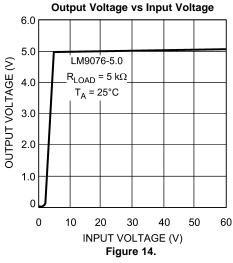

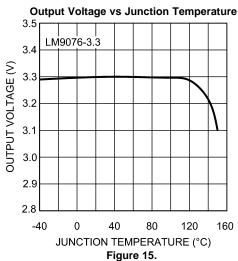

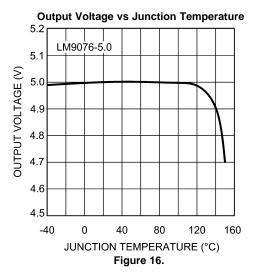

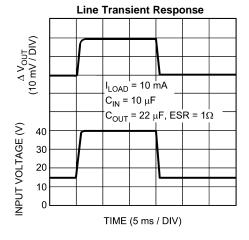

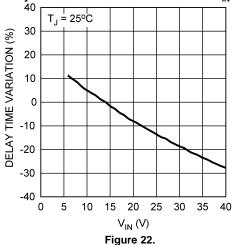

## **Typical Performance Characteristics**

## **Typical Performance Characteristics (continued)**

Submit Documentation Feedback

# Typical Performance Characteristics (continued) Dropout Voltage vs Load Current Load Trans

Figure 18.

Delayed Reset Time vs Vin Normalized to V<sub>IN</sub> = 14V T<sub>J</sub> = 25°C 30

Figure 21.

Submit Documentation Feedback

# Typical Performance Characteristics (continued) Ripple Rejection

#### APPLICATION INFORMATION

#### **REGULATOR BASICS**

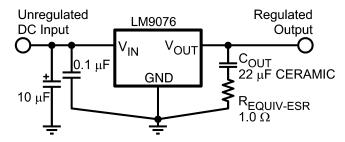

The LM9076Q regulator is suitable for Automotive and Industrial applications where continuous connection to a battery supply is required (refer to the Typical Application circuit).

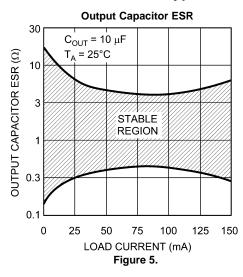

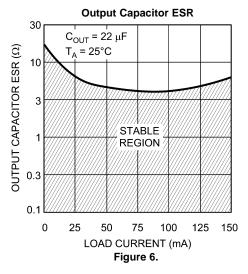

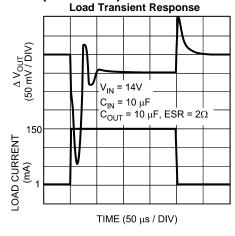

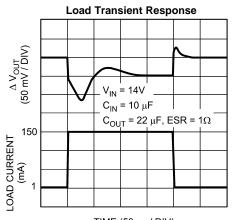

The pass element of the regulator is a PNP device which requires an output bypass capacitor for stability. The minimum bypass capacitance for the output is 10  $\mu$ F (refer to ESR limitations). A 22  $\mu$ F, or larger, output bypass capacitor is recommended for typical applications

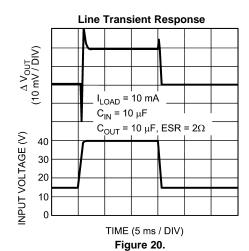

#### INPUT CAPACITOR

The LM9076Q requires a low source impedance to maintain regulator stability because critical portions of the internal bias circuitry are connected to directly to  $V_{IN}$ . In general, a 10  $\mu F$  electrolytic capacitor, located within two inches of the LM9076Q, is adequate for a majority of applications. Additionally, and at a minimum, a 0.1  $\mu F$  ceramic capacitor should be located between the LM9076Q  $V_{IN}$  and Ground pin, and as close as is physically possible to the LM9076Q itself .

#### **OUTPUT CAPACITOR**

An output bypass capacitor is required for stability. This capacitance must be placed between the LM9076Q  $V_{OUT}$  pin and Ground pin, as close as is physically possible, using traces that are not part of the load current path.

The output capacitor must meet the requirements for minimum capacitance and also maintain the appropriate ESR value across the entire operating ambient temperature range. There is no limit to the maximum output capacitance as long as ESR is maintained.

The minimum bypass capacitance for the output is 10  $\mu$ F (refer to ESR limitations). A 22  $\mu$ F, or larger, output bypass capacitor is recommended for typical applications.

Solid tantalums capacitors are recommended as they generally maintain capacitance and ESR ratings over a wide temperature range. Ceramic capacitor types XR7 and XR5 may be used if a series resistor is added to simulate the minimum ESR requirement. See Figure 24.

Aluminum electrolytic capacitors are not recommended as they are subject to wide changes in capacitance and ESR across temperature.

Figure 24. Using Low ESR Capacitors

### **DELAY CAPACITOR**

The capacitor on the Delay pin must be a low leakage type since the charge current is minimal (420 nA typical) and the pin must fully charge to  $V_{OUT}$ . Ceramic, Mylar, and polystyrene capacitor types are generally recommended, although changes in capacitance values across temperature changes will have some effect on the delay timing.

Any leakage of the  $I_{DELAY}$  current, be it through the delay capacitor or any other path, will extend the delay time, possibly to the point that the Reset pin output does not go high.

#### SHUTDOWN PIN - LM9076QBMA ONLY

The basic On/Off control of the regulator is accomplished with the SHUTDOWN pin. By pulling the SHUTDOWN pin high the regulator output is switched Off. When the regulator is switched Off the load on the battery will be primarily due to the SHUTDOWN pin current.

When the SHUTDOWN pin is low, or left open, the regulator is switched On. When an unregulated supply, such as V BATTERY , is used to pull the SHUTDOWN pin high a series resistor in the range of  $10 \text{K}\Omega$  to  $50 \text{K}\Omega$  is recommended to provide reverse voltage transient protection of the SHUTDOWN pin. Adding a small capacitor (0.001uF typical) from the SHUTDOWN pin to Ground will add noise immunity to prevent accidental turn on due to noise on the supply line.

#### **RESET FLAG**

The  $\overline{\text{RESET}}$  pin is an open collector output which requires an external pull-up resistor to develop the reset signal. The external pull-up resistor should be in the range of 10 k $\Omega$  to 200 k $\Omega$ .

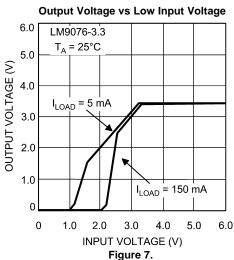

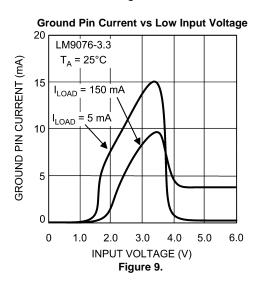

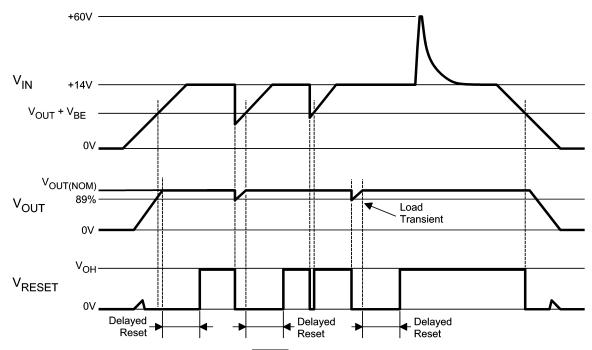

At  $V_{IN}$  values of less than typically 2V the  $\overline{RESET}$  pin voltage will be high. For  $V_{IN}$  values between typically 2V and approximately  $V_{OUT} + V_{BE}$  the  $\overline{RESET}$  pin voltage will be low. For  $V_{IN}$  values greater than approximately  $V_{OUT} + V_{BE}$  the  $\overline{RESET}$  pin voltage will be dependent on the status of the  $V_{OUT}$  pin voltage and the Delayed Reset circuitry. The value of  $V_{BE}$  is typically 600 mV at 25°C and will decrease approximately 2 mV for every 1°C increase in the junction temperature. During normal operation the  $\overline{RESET}$  pin voltage will be high .

Any load condition that causes the V<sub>OUT</sub> pin voltage to drop below typically 89% of normal will activate the Delayed Reset circuit and the RESET pin will go low for the duration of the delay time.

Any line condition that causes  $V_{IN}$  pin voltage to drop below typically  $V_{OUT} + V_{BE}$  will cause the  $\overline{RESET}$  pin to go low without activating the Delayed Reset circuitry.

Excessive thermal dissipation will raise the junction temperature and could activate the Thermal Shutdown circuitry which, in turn, will cause the RESET pin to go low.

For the LM9076QBMA devices, pulling the SHUTDOWN pin high will turn off the output which, in turn, will cause the  $\overline{RESET}$  pin to go low once the  $V_{OUT}$  voltage has decayed to a value that is less than typically 89% of normal. See Figure 25.

#### **RESET DELAY TIME**

When the regulator output is switched On, or after recovery from brief  $V_{OUT}$  fault condition, the  $\overline{RESET}$  flag can be can be programmed to remain low for an additional delay time. This will give time for any system reference voltages, clock signals, etc., to stabilize before the micro-controller resumes normal operation.

This delay time is controlled by the capacitor value on the  $C_{DELAY}$  pin. During normal operation the  $C_{DELAY}$  capacitor is charged to near  $V_{OUT}$ . When a  $V_{OUT}$  fault causes the RESET pin to go low, the  $C_{DELAY}$  capacitor is quickly discharged to ground. When the  $V_{OUT}$  fault is removed, and  $V_{OUT}$  returns to the normal operating value, the  $C_{DELAY}$  capacitor begins charging at a typical constant 0.420 uA rate. When the voltage on the  $C_{DELAY}$  capacitor reaches the same potential as the  $V_{OUT}$  pin the RESET pin will be allowed to return high.

The typical RESET delay time can be calculated with the following formula:

$$t_{DELAY} = V_{OUT} X (C_{DELAY} / I_{DELAY})$$

(1)

For the LM9076Q-3.3 with a  $C_{DELAY}$  value of 0.001 uF and a  $I_{DELAY}$  value of 0.420 uA the typical  $\overline{RESET}$  delay time is:

$$t_{DELAY} = 3.3 \text{V} \times (0.001 \text{ uF} / 0.420 \text{ uA}) = 7.8 \text{ ms}$$

(2)

For the LM9076Q-5.0 with a  $C_{DELAY}$  value of 0.001 uF and a  $I_{DELAY}$  value of 0.420 uA the typical  $\overline{RESET}$  delay time is:

$$t_{DELAY} = 5.0V \text{ X } (0.001 \text{uF} / 0.420 \text{uA}) = 11.9 \text{ ms}$$

(3)

#### THERMAL PROTECTION

Device operational range is limited by the maximum junction temperature  $(T_J)$ . The junction temperature is influenced by the ambient temperature  $(T_A)$ , package selection, input voltage  $(V_{IN})$ , and the output load current. When operating with maximum load currents the input voltage and/or ambient temperature will be limited. When operating with maximum input voltage the load current and/or the ambient temperature will be limited.

Even though the LM9076Q is equipped with circuitry to protect itself from excessive thermal dissipation, it is not recommended that the LM9076Q be operated at, or near, the maximum recommended die junction temperature (T<sub>J</sub>) as this may impair long term device reliability.

The thermal protection circuity monitors the temperature at the die level. When the die temperature exceeds typically 160°C the voltage regulator output will be switched off.

Figure 25. Typical Reset Pin Operational Waveforms

## SNVS713B -APRIL 2011-REVISED MARCH 2013

## **REVISION HISTORY**

| Cł | nanges from Revision A (March 2013) to Revision B  | Pa | ge |

|----|----------------------------------------------------|----|----|

| •  | Changed layout of National Data Sheet to TI format |    | 13 |

13-Sep-2014

#### **PACKAGING INFORMATION**

| Orderable Device     | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|----------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|-------------------------|---------|

| LM9076QBMA-3.3/NOPB  | ACTIVE | SOIC         | D                  | 8    | 95             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 9076B<br>QMA3.3         | Samples |

| LM9076QBMA-5.0/NOPB  | ACTIVE | SOIC         | D                  | 8    | 95             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 9076B<br>QMA5.0         | Samples |

| LM9076QBMAX-3.3/NOPB | ACTIVE | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 9076B<br>QMA3.3         | Samples |

| LM9076QBMAX-5.0/NOPB | ACTIVE | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 9076B<br>QMA5.0         | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

## **PACKAGE OPTION ADDENDUM**

13-Sep-2014

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 21-Mar-2013

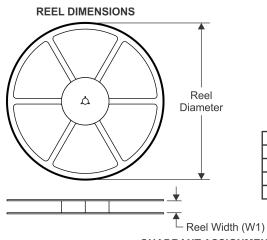

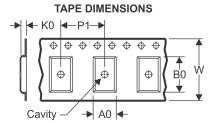

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

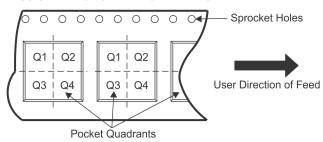

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device                   | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM9076QBMAX-3.3/NOP<br>B | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM9076QBMAX-5.0/NOP<br>B | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Mar-2013

#### \*All dimensions are nominal

| Device               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM9076QBMAX-3.3/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LM9076QBMAX-5.0/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

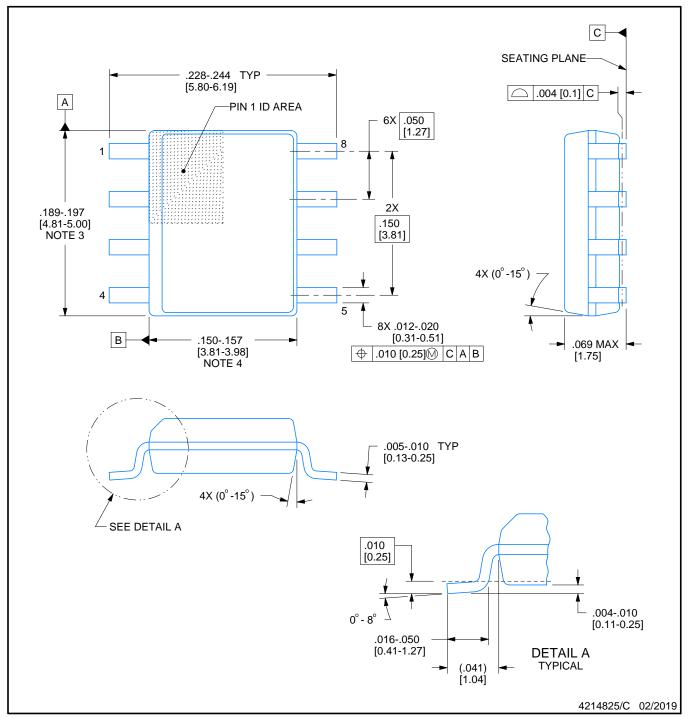

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

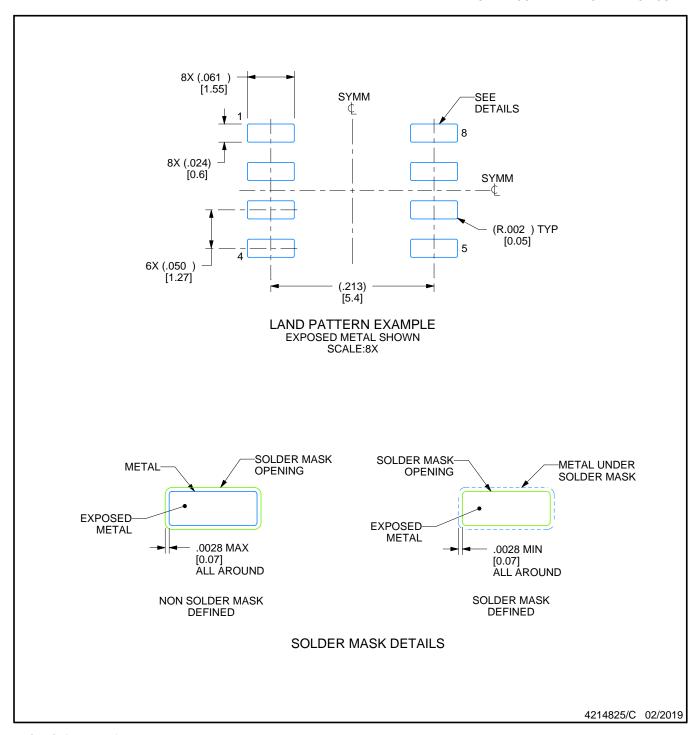

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

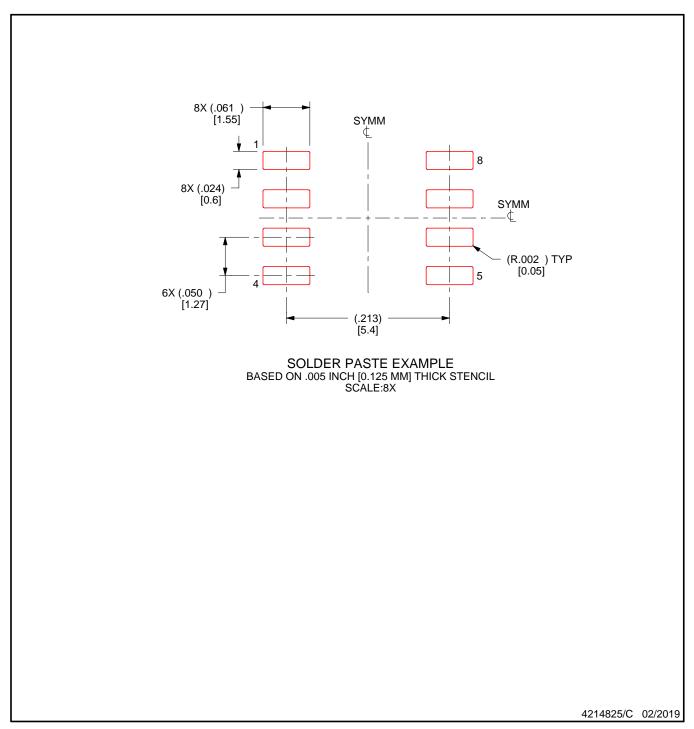

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated