# LM95010 Digital Temperature Sensor with SensorPath™ Bus

Check for Samples: LM95010

## **FEATURES**

- SensorPath Bus

- 4 Hardware Programmable Addresses

- Temperature Sensing

- 0.25 °C Resolution

- 127.75 °C Maximum Temperature Reading

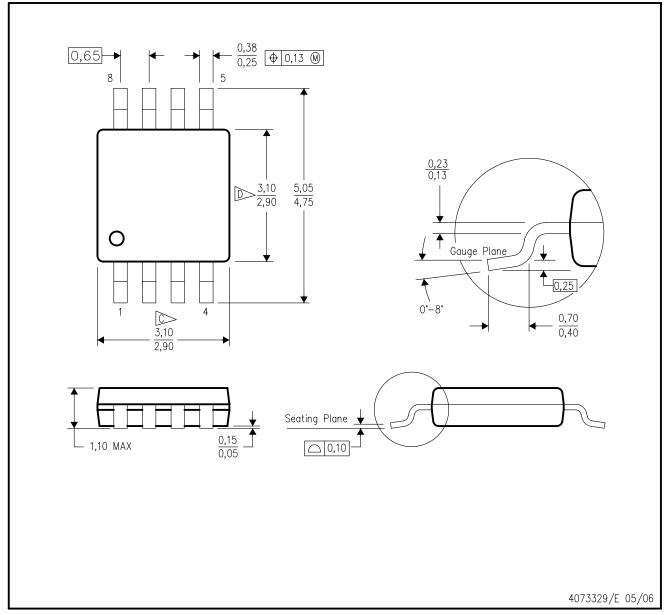

- 8-Lead VSSOP Package

## **APPLICATIONS**

- Microprocessor Based Equipment

- (Motherboards, Base-stations, Routers, ATMs, Point of Sale, ...)

- Power Supplies

## **KEY SPECIFICATIONS**

- Temperature Sensor Accuracy ±2°C (max)

- Temperature Range -20 to +125°C

- Power Supply Voltage +3.0 to +3.6 V

- Power Supply Current 0.5 mA (typ)

- Conversion Time 14 to 1456 ms

#### DESCRIPTION

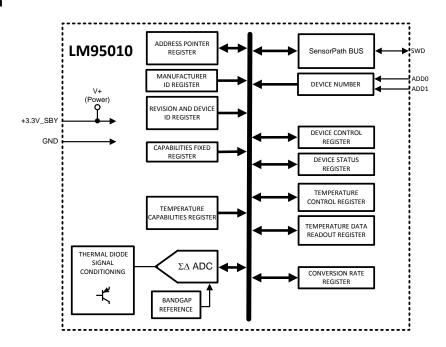

The LM95010 is a digital output temperature sensor that has single-wire interface compatible with the SensorPath interface. It uses a  $\Delta V_{be}$  analog temperature sensing technique that generates a differential voltage that is proportional to temperature. This voltage is digitized using a Sigma-Delta analogto-digital converter. The LM95010 is part of a hardware monitor system, comprised of two parts: the PC System Health Controller (Master), such as a Super I/O, and up to seven slaves of which four can be LM95010s. Using SensorPath, the LM95010 will be controlled by the master and report to the master its own die temperature. SensorPath data is pulse width encoded, thereby allowing the LM95010 to be easily connected to many general purpose microcontrollers.

## **Block Diagram**

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SensorPath is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

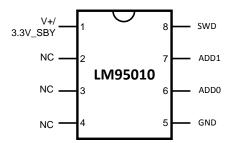

## **Connection Diagram**

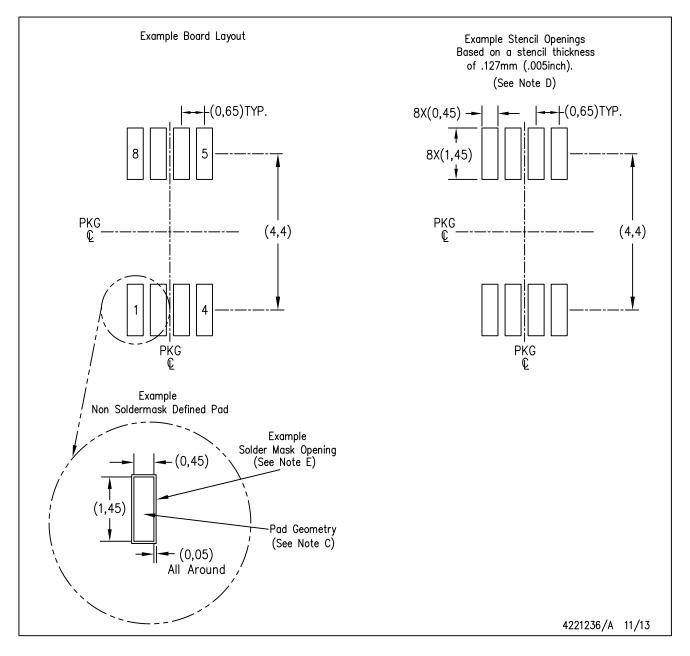

Figure 1. 8-Lead VSSOP See DGK Package

#### **PIN DESCRIPTION**

| Pin<br>Number | Pin Name      | Туре             | Description                                                           | Typical Connection                                                                                                                                                                                  |

|---------------|---------------|------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | V+/3.3V<br>SB | Power            | Positive power supply pin +3.3V pin.                                  | Should be powered by +3.3V Standby power. This pin should be bypassed with a 0.1 $\mu$ F capacitor. A bulk capacitance of approximately 10 $\mu$ F needs to be in the near vicinity of the LM95010. |

| 2-4           | NC            |                  |                                                                       | Must be grounded.                                                                                                                                                                                   |

| 5             | GND           | Power            | Ground                                                                | System ground                                                                                                                                                                                       |

| 6             | ADD0          | Input            | Address select input that assigns the serial bus device number        | $10k\Omega$ resistor to V+ or GND; must never be left floating                                                                                                                                      |

| 7             | ADD1          | Input            | Address select input that assigns the serial bus device number        | $10k\Omega$ resistor to V+ or GND; must never be left floating                                                                                                                                      |

| 8             | SWD           | Input/<br>Output | Single-wire Data, SensorPath serial interface line; Open-drain output | Super I/O with 1.25kΩ pull-up to 3.3V                                                                                                                                                               |

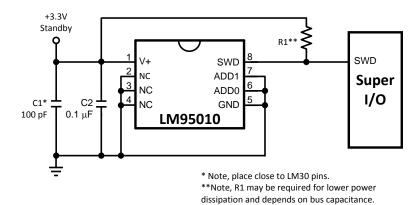

## **Typical Application**

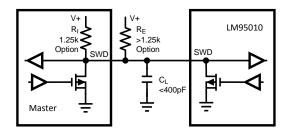

Figure 2. LM95010 connection to SensorPath master such as a Super I/O.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Product Folder Links: *LM95010*

Copyright © 2003-2013, Texas Instruments Incorporated

## Absolute Maximum Ratings (1)(2)

| Supply Voltage (V <sup>+</sup> )       |                          | -0.5 V to 6.0 V        |

|----------------------------------------|--------------------------|------------------------|

| Voltage on Pin 2                       |                          | -0.3 V to (V+ + 0.3 V) |

| Voltage on all other Pins              |                          | -0.5 V to 6.0 V        |

| Input Current per Pin <sup>(3)</sup>   |                          | 5 mA                   |

| Package Input Current (3)              |                          | 30 mA                  |

| Package Power Dissipation              |                          | (4)                    |

| Output Sink Current                    |                          | 10 mA                  |

| Storage Temperature                    |                          | −65 °C to +150 °C      |

| ESD Susceptibility (5)                 | Human Body Model         | 2000 V                 |

|                                        | Machine Model            | 200 V                  |

| Soldering Information, Lead Temperatur | re                       |                        |

| VSSOP Package <sup>(6)</sup>           | Vapor Phase (60 seconds) | 215 °C                 |

|                                        | Infrared (15 seconds)    | 220 °C                 |

- (1) All voltages are measured with respect to GND, unless otherwise noted.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

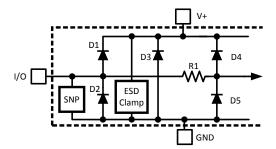

- (3) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < GND or V<sub>IN</sub> > V+), the current at that pin should be limited to 5 mA. Parasitic components and/or ESD protection circuitry are shown below for the LM95010's pins. The nominal breakdown voltage of D3 is 6.5 V. SNP stands for snap-back device. Devices that are connected to a particular pin are marked with a "√" in Table 1.

- (4) Thermal resistance junction-to-ambient when attached to a printed circuit board with 2 oz. foil is 210 °C/W.

- (5) Human body model, 100 pF discharged through a 1.5 kΩ resistor. Machine model, 200 pF discharged directly into each pin. See Figure 3 for the ESD Protection Input Structure.

- (6) See the URL "http://www.ti.com/packaging/" for other recommendations and methods of soldering surface mount devices.

## Operating Ratings (1)(2)

| Temperature Range for Electrical Characteristics | $T_{MIN} \le T_A \le T_{MAX}$     |

|--------------------------------------------------|-----------------------------------|

| LM95010CIMM                                      | -20 °C ≤ T <sub>A</sub> ≤ +125 °C |

| Operating Temperature Range                      | -20 °C ≤ T <sub>A</sub> ≤ +125 °C |

| Supply Voltage Range (V+)                        | +3.0 V to +3.6 V                  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) All voltages are measured with respect to GND, unless otherwise noted.

#### **DC Electrical Characteristics**

The following specifications apply for V+ = 3.0  $V_{DC}$  to 3.6  $V_{DC}$ , unless otherwise specified in the conditions. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = +25 °C.

| Symbol             | Parameter                                          | Conditions                                                                | Typical <sup>(1)</sup> | Limits (2) | Units<br>(Limit)   |

|--------------------|----------------------------------------------------|---------------------------------------------------------------------------|------------------------|------------|--------------------|

| V+                 | Power Supply Voltage                               |                                                                           | 3.3                    | 3.0<br>3.6 | V (min)<br>V (max) |

| I+ <sub>AVG</sub>  | Average Power Supply Current                       | SensorPath Bus Inactive (3)                                               | 500                    | 750        | μA (max)           |

| I+ <sub>Peak</sub> | Peak Power Supply Current                          | SensorPath Bus Inactive (3)                                               | 1.6                    |            | mA                 |

|                    | Power-On Reset Threshold Voltage                   |                                                                           |                        | 1.6        | V (min)            |

|                    |                                                    |                                                                           |                        | 2.8        | V (max)            |

| EMPERATU           | RE-TO-DIGITAL CONVERTER CHARACTERI                 | ISTICS                                                                    |                        |            |                    |

|                    | Temperature Error                                  | $T_A = -20  ^{\circ}\text{C} \text{ and } +125  ^{\circ}\text{C}  ^{(4)}$ | ±1                     | ±3         | °C (max)           |

|                    |                                                    | +25 °C ≤ T <sub>A</sub> ≤ +60 °C <sup>(4)</sup>                           |                        | ±2         | °C (max)           |

|                    | Temperature Resolution                             |                                                                           | 10                     |            | Bits               |

|                    |                                                    |                                                                           | 0.25                   |            | °C                 |

| WD and ADI         | D DIGITAL INPUT CHARACTERISTICS                    |                                                                           |                        | <u> </u>   |                    |

| V <sub>IH</sub>    | SWD Logical High Input Voltage                     |                                                                           |                        | 2.1        | V (min)            |

|                    |                                                    |                                                                           |                        | V+ + 0.5   | V (max)            |

| V <sub>IL</sub>    | SWD Logical Low Input Voltage                      |                                                                           |                        | 0.8        | V (max)            |

|                    |                                                    | T <sub>A</sub> = 0 °C to +85 °C                                           |                        | -0.5       | V (min)            |

|                    |                                                    |                                                                           |                        | -0.3       | V (min)            |

| V <sub>IH</sub>    | ADD Logical High Input Voltage                     |                                                                           |                        | 90% x V+   | V (min)            |

| $V_{IL}$           | ADD Logical Low Input Voltage                      |                                                                           |                        | 10% x V+   | V (max)            |

| V <sub>HYST</sub>  | SWD Input Hysteresis                               |                                                                           | 300                    |            | mV                 |

| ΙL                 | SWD and ADD Input Leakage Current                  | GND ≤V <sub>IN</sub> ≤ V+                                                 | ±0.005                 | ±10        | μA (max)           |

|                    | SWD Input Leakage Current with V+ Open or Grounded | GND ≤V <sub>IN</sub> ≤ 3.6 V, and V+ Open or GND                          | ±0.005                 |            | μΑ                 |

| C <sub>IN</sub>    | Digital Input Capacitance                          |                                                                           | 10                     |            | pF                 |

| WD DIGITAL         | OUTPUT CHARACTERISTICS                             | •                                                                         |                        |            |                    |

| V <sub>OL</sub>    | Open-drain Output Logic "Low" Voltage              | I <sub>OL</sub> = 4 mA                                                    |                        | 0.4        | V (max)            |

|                    |                                                    | I <sub>OL</sub> = 50 μA                                                   |                        | 0.2        | V (max)            |

| I <sub>OH</sub>    | Open-drain Output Off Current                      |                                                                           | ±0.005                 | ±10        | μA (max)           |

| C <sub>OUT</sub>   | Digital Output Capacitance                         |                                                                           | 10                     |            | pF                 |

<sup>(1) &</sup>quot;Typicals" are at T<sub>A</sub> = 25 °C and represent most likely parametric norm. They are to be used as general reference values not for critical design calculations.

<sup>(2)</sup> Limits are specified to TI's AOQL (Average Outgoing Quality Level).

<sup>(3)</sup> The supply current will not increase substantially with SensorPath transactions.

<sup>(4)</sup> Temperature accuracy does not include the effects of self-heating. The rise in temperature due to self-heating is the product of the internal power dissipation of the LM95010 and the thermal resistance. See Note 4 in Absolute Maximum Ratings table for thermal resistance to be used in the self-heating calculation.

## **AC Electrical Characteristics**

The following specification apply for  $V_+ = +3.0 V_{DC}$  to  $+3.6 V_{DC}$ , unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub>** = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>; all other limits T<sub>A</sub> = T<sub>J</sub> = 25 °C. The SensorPath Characteristics conform to the SensorPath specification. Please refer to that specification for further details.

| Symbol               | Parameter                                                                                             | Conditions                                           | Typical <sup>(1)</sup> | Limits <sup>(2)</sup> | Units<br>(Limits) |

|----------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------|-----------------------|-------------------|

| t <sub>CONV</sub>    | Total Monitoring Cycle                                                                                | Default                                              | 182                    | 163.8                 | ms (min           |

|                      | Time (3)                                                                                              |                                                      |                        | 200.2                 | ms (max           |

| sorPath Bus Cl       | HARACTERISTICS                                                                                        | •                                                    |                        |                       | •                 |

| t <sub>f</sub>       | SWD fall time (4)                                                                                     | $R_{pull-up}$ = 1.25 k $\Omega$ ±30%, $C_L$ = 400 pF |                        | 300                   | ns (max           |

| t <sub>r</sub>       | SWD rise time (5)                                                                                     | $R_{pull-up}$ = 1.25 k $\Omega$ ±30%, $C_L$ = 400 pF |                        | 1000                  | ns (max           |

| t <sub>INACT</sub>   | Minimum inactive time<br>(bus at high level) ensured<br>by the LM95010 before an<br>Attention Request |                                                      |                        | 11                    | μs (min           |

| t <sub>MtrO</sub>    | Master drive for Data Bit 0                                                                           |                                                      |                        | 11.8                  | µs (min           |

|                      | write and for Data Bit 0-1 read                                                                       |                                                      |                        | 17.0                  | µs (max           |

| t <sub>Mtr1</sub>    | Master drive for Data Bit 1                                                                           |                                                      |                        | 35.4                  | μs (min           |

|                      | write                                                                                                 |                                                      |                        | 48.9                  | μs (max           |

| t <sub>SFEdet</sub>  | Time allowed for LM95010 activity detection                                                           |                                                      |                        | 9.6                   | µs (max           |

| t <sub>SLout1</sub>  | LM95010 drive for Data                                                                                |                                                      |                        | 28.3                  | μs (min           |

|                      | Bit 1 read by master                                                                                  |                                                      |                        | 38.3                  | μs (max           |

| t <sub>MtrS</sub>    | Master drive for Start Bit                                                                            |                                                      |                        | 80                    | μs (min           |

|                      |                                                                                                       |                                                      |                        | 109                   | µs (max           |

| t <sub>SLoutA</sub>  | LM95010 drive for                                                                                     |                                                      |                        | 165                   | μs (min           |

|                      | Attention Request                                                                                     |                                                      |                        | 228                   | µs (max           |

| t <sub>RST</sub>     | Master or LM95010 drive for Reset                                                                     |                                                      |                        | 354                   | μs (min           |

| t <sub>RST_MAX</sub> | Maximum drive of SWD by<br>an LM95010, after the<br>power supply is raised<br>above 3V                |                                                      |                        | 500                   | ms (ma            |

<sup>&</sup>quot;Typicals" are at T<sub>A</sub> = 25 °C and represent most likely parametric norm. They are to be used as general reference values not for critical (1) design calculations.

## Table 1.

| Pin Name   | PIN# | D1 | D2 | D3 | D4 | D5 | R1 | SNP | ESD<br>CLAMP |

|------------|------|----|----|----|----|----|----|-----|--------------|

| V+/3.3V SB | 1    |    |    | ✓  |    |    |    |     | ✓            |

| NC         | 2    | ✓  | ✓  | ✓  | ✓  | ✓  | ✓  |     | ✓            |

| NC         | 3    |    |    |    |    |    |    |     |              |

| NC         | 4    |    | ✓  | ✓  |    | ✓  | ✓  | ✓   |              |

| ADD0       | 6    |    | ✓  | ✓  |    | ✓  | ✓  | ✓   |              |

| ADD1       | 7    |    | ✓  | ✓  |    |    |    | ✓   |              |

| SWD        | 8    |    | ✓  | ✓  |    | 1  | ✓  | ✓   |              |

Limits are specified to TI's AOQL (Average Outgoing Quality Level).

This specification is provided only to indicate how often temperature data is updated once enabled.

The output fall time is measured from  $V_{IL\ max}$  to  $V_{IL\ min}$ . The output rise time is ensured by design. The output rise time is measured from  $V_{IL\ max}$  to  $V_{IH\ min}$ . The output rise time is ensured by design.

Devices that are connected to a particular pin are marked with a " $\checkmark$ " in the table above.

Figure 3. ESD Protection Input Structure

See SensorPath BIT SIGNALING for further details.

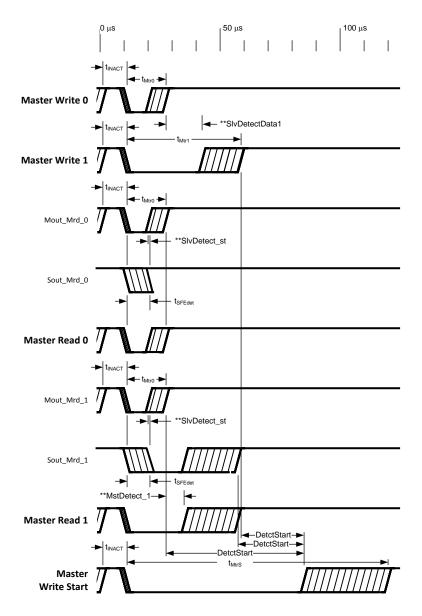

Figure 4. Timing for Data Bits 0, 1 and Start Bit

See SensorPath BIT SIGNALING for further details.

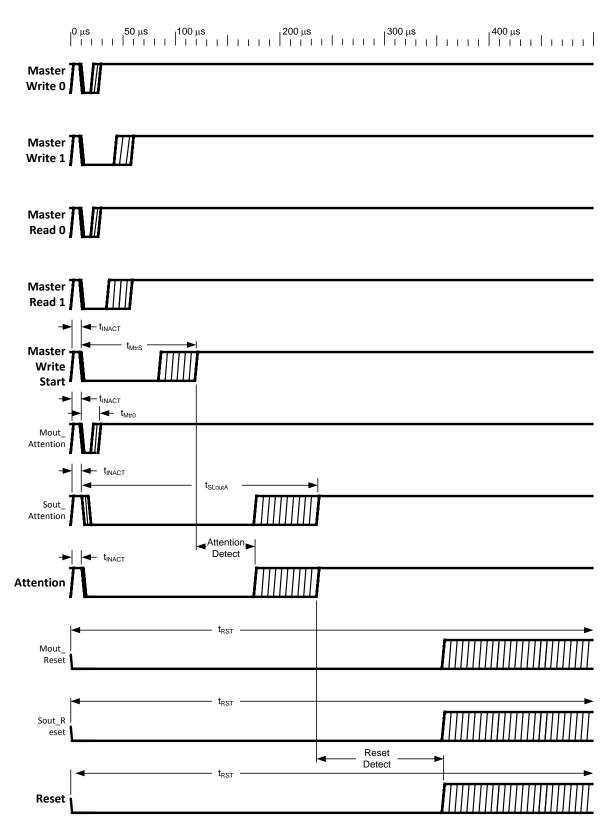

Figure 5. Timing for Attention Request and Reset

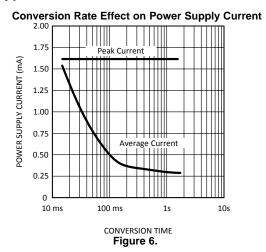

## Typical Performance Characteristics

#### **FUNCTIONAL DESCRIPTION**

The LM95010 is based on a  $\Delta V_{be}$  temperature sensing method. A differential voltage, representing temperature, is digitized using a Sigma-Delta analog to digital converter. The digital temperature data can be retrieved over a simple single-wire interface called SensorPath. SensorPath is optimized for hardware monitoring. TI offers a royalty-free license in connection with its intellectual property rights in the SensorPath bus.

The LM95010 has 2 address pins that allow up to 4 LM95010s to be connected to one SensorPath bus. The physical interface of SensorPath's SWD signal is identical to the familiar industry standard SMBus SMBDAT signal. The digital information is encoded in the pulse width of the signal being transmitted. Every bit can be synchronized by the master simplifying the implementation of the master when implemented with a microcontroller. For microcontroller's with greater functionality an asynchronous attention signal can be transmitted by the LM95010 to interrupt the microcontroller and notify it that temperature data has been updated in the readout register.

To optimize the LM95010's power consumption to the system requirements, the LM95010 has a shutdown mode as well as it supports multiple conversion rates.

## SensorPath BUS SWD

SWD is the Single Wire Data line used for communication. SensorPath uses 3.3V single-ended signaling, with a pull-up resistor and open-drain low-side drive (see Figure 7). For timing purposes SensorPath is designed for capacitive loads (C<sub>L</sub>) of up to 400pF. Note that in many cases a 3.3V standby rail of the PC will be used as a power supply for both the sensor and the master. Logic high and low voltage levels for SWD are TTL compatible. The master may provide an internal pull-up resistor. In this case the external resistor is not needed. The minimum value of the pull-up resistor must take into account the maximum allowable output load current of 4mA.

Figure 7. SensorPath SWD simplified schematic

#### SensorPath BIT SIGNALING

Signals are transmitted over SensorPath using pulse-width encoding. There are five types of "bit signals":

#### www.ti.com

- Data Bit 0

- Data Bit 1

- Start Bit

- Attention Request

- Reset

All the "bit signals" involve driving the bus to a low level. The duration of the low level differentiates between the different "bit-signals". Each "bit signal" has a fixed pulse width. SensorPath supports a Bus Reset Operation and Clock Training sequence that allows the slave device to synchronize its internal clock rate to the master. Since the LM95010 meets the ±15% timing requirements of SensorPath, the LM95010 does not require the Clock Training sequence and does support this feature. This section defines the "bit signal" behavior in all the modes. Please refer to the timing diagrams in Electrical Characteristics (Figure 4 and Figure 5) while going through this section. Note that the timing diagrams for the different types of "bit signals" are shown together to better highlight the timing relationships between them. However, the different types of "bit signals" appear on SWD at different points in time. These timing diagrams show the signals as driven by the master and the LM95010 slave as well as the signal as seen when probing SWD. Signals labels that begin with the label Mout\_ depict a drive by the master. Signals labels that begin with the label SIv\_ depict the drive by the LM95010. All other signals show what would be seen when probing SWD for a particular function (e.g. "Master Wr 0" is the Master transmitting a Data Bit with the value of 0).

#### **Bus Inactive**

The bus is inactive when the SWD signal is high for a period of at least t<sub>INACT</sub>. The bus is inactive between each "bit signal".

#### Data Bit 0 and 1

All Data Bit signal transfers are started by the master. A Data Bit 0 is indicated by a "short" pulse; a Data Bit 1 is indicated by a longer pulse. The direction of the bit is relative to the master, as follows:

- Data Write a Data Bit transferred from the master to the LM95010.

- Data Read a Data Bit transferred from the LM95010 to the master.

A master must monitor the bus as inactive before starting a Data Bit (read or Write).

A master initiates a data write by driving the bus active (low level) for the period that matches the data value ( $t_{Mtr0}$  or  $t_{Mtr1}$  for a write of "0" or "1", respectively). The LM95010 will detect that the SWD becomes active within a period of  $t_{SFEdet}$ , and will start measuring the duration of that the SWD is active in order to detect the data value.

A master initiates a data read by driving the bus for a period of  $t_{Mtr0}$ . The LM95010 will detect that the SWD have become active within a period of  $t_{SFEdet}$ . For a data read of "0", the LM95010 will not drive the SWD. For a data read of "1" the LM95010 will start within  $t_{SFEdet}$  to drive the SWD low for a period of  $t_{SLout1}$ . Both master and LM95010 must monitor the time at which the bus becomes inactive to identify a data read of "0" or "1".

During each Data Bit, both the master and all the LM95010s must monitor the bus (the master for Attention Request and Reset; at the LM95010s for Start Bit, Attention Request and Reset) by measuring the time SWD is active (low). If a Start Bit, Attention Requests or Reset "bit signal" is detected, the current "bit signal" is not treated as a Data Bit.

Note that the bit rate of the protocol varies depending on the data transferred. Thus, the LM95010 has a value of "0" in reserved or unused register bits for bus bandwidth efficiency.

## Start Bit

A master must monitor the bus as inactive before beginning a Start Bit.

The master uses a Start Bit to indicate the beginning of a transfer. LM95010s will monitor for Start Bits all the time, to allow synchronization of transactions with the master. If a Start Bit occurs in the middle of a transaction, the LM95010 being addressed will abort the current transaction. In this case the transaction is not "completed" by the LM95010 (see SensorPath BUS TRANSACTIONS).

During each Start Bit, both the master and all the LM95010s must monitor the bus for Attention Request and Reset, by measuring the time SWD is active (low). If an Attention Request or Reset condition is detected, the current "bit signal" is not treated as a Start Bit. The master may attempt to send the Start Bit at a later time.

#### **Attention Request**

The LM95010 may initiate an Attention Request when the SensorPath bus is inactive.

Note that a Data Bit, or Start Bit, from the master may start simultaneously with an Attention Request from the LM95010. In addition, two LM95010s may start an Attention Request simultaneously. Due to its length, the Attention Request has priority over any other "bit signal", except Reset. Conflict with Data Bits and Start Bits are detected by all the devices, to allow the bits to be ignored and re-issued by their originator.

The LM95010 will either check to see that the bus is inactive before starting an Attention Request, or start the Attention Request with the  $t_{SFEdet}$  time interval after SWD becomes active. The LM95010 will drive the signal low for  $t_{SLoutA}$  time. After this, both the master and the LM95010 must monitor the bus for a Reset Condition. If a Reset condition is detected, the current "bit signal" is not treated as an Attention Request.

After Reset, an Attention Request can not be sent before the master has sent 14 Data Bits on the bus. See Attention Request Transaction for further details on Attention Request generation.

#### **Bus Reset**

The LM95010 issues a Reset at power up. The master must also generate a Bus Reset at power-up for at least the minimum reset time, it must not rely on the LM95010. SensorPath puts no limitation on the maximum reset time of the master. Following a Bus Reset, the LM95010 may generate an Attention Request only after the master has sent 14 Data Bits on the bus. See Attention Request Transaction for further details on Attention Request generation.

## SensorPath BUS TRANSACTIONS

SensorPath is designed to work with a single master and up to seven slave devices. Each slave has a unique address. The LM95010's supports up to 4 device addresses that are selected by the state of the address pins ADD0 and ADD1. The Register Set of the LM95010 is defined in Register Set.

#### **Bus Reset Operation**

A Bus Reset Operation is global on the bus and affects only the communication interface of all the devices connected to it. The Bus Reset operation does not affect either the contents of the device registers, or device operation, to the extent defined in LM95010 Register Set, see Register Set.

The Bus Reset operation is performed by generating a Reset signal on the bus. The master must apply Reset after power-up, and before it starts operation. The Reset signal end will be monitored by all the LM95010s on the bus.

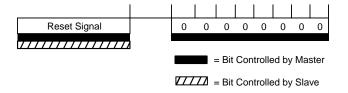

After the Reset Signal SensorPath BIT SIGNALING requires that the master send a sequence of 8 Data Bits with a value of "0", without a preceding Start Bit. This is required to enable slaves that "train" their clocks to the bit timing. The LM95010 does not require nor does it support clock training.

Figure 8. Bus Reset Transaction

#### **Read Transaction**

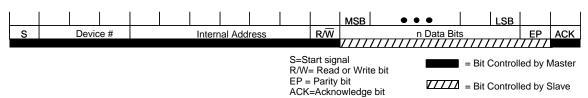

During a read transaction, the master reads data from a register at a specified address within a slave. A read transaction begins with a Start Bit and ends with an ACK bit, as shown in Figure 9.

- **Device Number** This is the address of the LM95010 device accessed. Address "000" is a broadcast address and can be responded to by all the slave devices. The LM95010 ignores the broadcast address during a read transaction

- Internal Address The address of a register within the LM95010 that is read.

- Read/Write (R/W) A "1" indicates a read transaction.

- **Data Bits** During a read transaction the data bits are driven by the LM95010. Data is transferred serially with the most significant bit first. This allows throughput optimization based on the information that needs to be read.

- The LM95010 supports 8-bit or 16-bit data fields, as described in Register Set.

- Even Parity (EP) This bit is based on all preceding bits (device number, internal address, read/write and data bits) and the parity bit itself. The parity -number of 1's of all the preceding bits and the parity bit must be even i.e., the result must be 0. During a read transaction, the EP bit is sent by the LM95010 to the master to allow the master to check the received data before using it.

- Acknowledge (ACK) During a read transaction the ACK bit is sent by the master indicating that the EP bit

was received and was found to be correct, when compared to the data preceding it, and that no conflict was

detected on the bus (excluding Attention Request Attention Request Transaction). A read transfer is

considered "complete" only when the ACK bit is received. A transaction that was not positively acknowledged

is not considered "complete" by the LM95010 and following are performed:

- The BER bit in the LM95010 Device Status register is set

- The LM95010 generates an Attention Request before, or together with the Start Bit of the next transaction A transaction that was not positively acknowledged is also not considered "complete" by the master (i.e. internal operations related to the transaction are not performed). The transaction may be repeated by the master, after detecting the source of the Attention Request (the LM95010 that has a set BER bit in the Device Status register). Note that the SensorPath protocol neither forces, nor automates re-execution of the transaction by the master. The values of the ACK bit are:

- 1: Data was received correctly

- 0: An error was detected (no-acknowledge).

Figure 9. Read Transaction, master reads data from LM95010

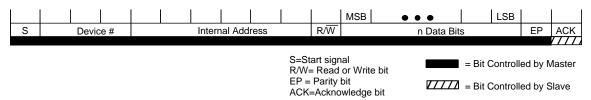

#### Write Transaction

In a write transaction, the master writes data to a register at a specified address in the LM95010. A write transaction begins with a Start Bit and ends with an ACK Data Bit, as show in Figure 10.

- Device Number This is the address of the slave device accessed. Address "000" is a broadcast address and

is responded to by all the slave devices. The LM95010 responds to broadcast messages to the Device

Control Register.

- Internal Address This is the register address in the LM95010 that will be written.

- Read/Write (R/W) A "0" data bit directs a write transaction.

- Data Bits This is the data written to the LM95010 register, are driven by the master. Data is transferred

serially with the most significant bit first. The number of data bits may vary from one address to another,

based on the size of the register in the LM95010. This allows throughput optimization based on the

information that needs to be written.

- The LM95010 supports 8-bit or 16-bit data fields, as described in Register Set.

- Even Parity (EP) This data bit is based on all preceding bits (Device Number, Internal Address, Read/Write and Data bits) and the Even Parity bit itself. The parity (number of 1's) of all the preceding bits and the parity

Copyright © 2003–2013, Texas Instruments Incorporated

bit must be even - i.e. the result must be 0. During a write transaction, the EP bit is sent by the master to the LM95010 to allow the LM95010 to check the received data before using it.

- Acknowledge (ACK) During the write transaction the ACK bit is sent by the LM95010 indicating to the master that the EP was received and was found correct, and that no conflict was detected on the bus (excluding Attention Request see Attention Request Transaction). A write transfer is considered "completed" only when the ACK bit is generated. A transaction that was not positively acknowledged is not considered complete by the LM95010 (i.e. internal operation related to the transaction are not performed) and the following are performed:

- The BER bit in the LM95010 Device Status register is set;

- The LM95010 generates an Attention Request before, or together with the Start Bit of the next transaction A transaction that was not positively acknowledged is also not considered "complete" by the master (i.e. internal operations related to the transaction are not performed). The transaction may be repeated by the master, after detecting the source of the Attention Request (the LM95010 that has a set BER bit in the Device Status register). Note that the SensorPath protocol neither forces, nor automates re-execution of the transaction by the master. The values of the ACK bit are:

- 1: Data was received correctly;

- 0: An error was detected (no-acknowledge).

Figure 10. Write Transaction, master write data to LM95010

## **Read and Write Transaction Exceptions**

This section describes master and LM95010 handling of special bus conditions, encountered during either Read or Write transactions.

If an LM95010 receives a Start Bit in the middle of a transaction, it aborts the current transaction (the LM95010 does not "complete" the current transaction) and begins a new transaction. Although not recommend for SensorPath normal operation, this situation is legitimate, therefore it is not flagged as an error by the LM95010 and Attention Request is not generated in response to it. The master generating the Start Bit, is responsible for handling the not "complete" transaction at a "higher level".

If LM95010 receives more than the expected number of data bits (defined by the size of the accessed register), it ignores the unnecessary bits. In this case, if both master and LM95010 identify correct EP and ACK bits they "complete" the transaction. However, in most cases, the additional data bits differ from the correct EP and ACK bits. In this case, both the master and the LM95010 do not "complete" the transaction. In addition, the LM95010 performs the following:

- the BER bit in the LM95010 Device Status register is set

- the LM95010 generates an Attention Request

If the LM95010 receives less than the expected number of data bits (defined by the size of the accessed register), it waits indefinitely for the missing bits to be sent by the master. If then the master sends the missing bits, together with the correct EP/ACK bits, both master and LM95010 "complete" the transaction. However, if the master starts a new transaction generating a Start Bit, the LM95010 aborts the current transaction (the LM95010 does not "complete" the current transaction) and begins the new transaction. The master is not notified by the LM95010 of the incomplete transaction.

#### **Attention Request Transaction**

Attention Request is generated by the LM95010 when it needs the attention of the master. The master and all LM95010s must monitor the Attention Request to allow bit re-sending in case of simultaneous start with a Data Bit or Start Bit transfer. Refer to Attention Request of the data sheet.

The LM95010 will generate an Attention Request using the following rules:

- 1. A Function event that sets the Status Flag has occurred and Attention Request is enabled and

- 2. The "physical" condition for an Attention Request is met (i.e., the bus is inactive), and

- 3. At the first time 2 is met after 1 occurred, there has not been an Attention request on the bus since a read of the Device Status register, **or** since a Bus Reset.

#### OR

- 1. A bus error event occurred, and

- 2. the "physical" condition for an Attention Request is met (i.e., the bus is inactive), and

- 3. At the first time 2. is met after 1 occurred, there has not been a Bus Reset.

All devices (master or slave) must monitor the bus for an Attention Request signal. The following notes clarify the intended system operation that uses the Attention Request Indication.

- Masters are expected to use the attention request as a trigger to read results from the LM95010. This is done

in a sequence that covers all LM95010s. This sequence is referred to as "master sensor read sequence".

- After an Attention Request is sent by an LM95010 until after the next read from the Device Status register the LM95010 does not send Attention Requests for a function event since it is ensured that the master will read the Status register as part of the master sensor read sequence. Note that the LM95010 will send an attention for BER, regardless of the Status register read, to help the master with any error recovery operations and prevent deadlocks.

- A master must record the Attention Request event. It must then scan all slave devices in the system by reading their Device Status register and must handle any pending event in them before it may assume that there are no more events to handle.

#### NOTE

There is no indication of which slave has sent the request. The requirement that multiple requests are not sent allows the master to know within one scan of register reads that there are no more pending events.

#### **Fixed Number Setting**

The LM95010 device number is defined by strapping of the ADD0 and ADD1 pins. The LM95010 will wake (after Device Reset) with the Device Number field of the Device Number register set to the address as designated in DEVICE NUMBER (Addr 00o). It is the responsibility of the system designer to avoid having two devices with the same Device Number on the bus.

Devices should be detected by the master by a read operation of the Device Number register. The read returns "000" if there is no device at that address on the bus (the EP bit must be ignored).

## **Register Set**

## **REGISTER SET SUMMARY**

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4    | Bit 3 | Bit 2 | Bit 1   | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|---------|----------|-------|-------|---------|--------------|

| 000        | Device           | R       | *                  |                  |           |           | Not Av    | ailable   |           |       |       |       | R     | eserve  | ed       |       | Se    | e Table | e 2          |

| 000        | Number           |         |                    |                  |           |           |           |           |           |       |       | 0     | 0     | 0       | 0        | 0     |       |         |              |

| 000<br>001 | Manufacture r ID | R       | 100B<br>h          | 0                | 0         | 0         | 1         | 0         | 0         | 0     | 0     | 0     | 0     | 0       | 0        | 1     | 0     | 1       | 1            |

| 000        | Device ID        | R       | 21h                |                  |           | RevID     |           |           |           |       |       |       | D     | evice I | D        | •     |       | •       |              |

| 010        |                  |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 0     | 0     | 0     | 1       | 0        | 0     | 0     | 0       | 1            |

| 000        | Capabilities     | R       | 1h                 |                  |           | •         |           |           | Rese      | erved |       |       |       | •       |          |       | Func  | tion 1  | ,            |

| 011        | Fixed            |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 0     | 0     | 0     | 0       | 0        | 0     | 0     | 0       | 1            |

| 000<br>100 | Device<br>Status | R       | 0h                 |                  |           |           | Not Av    | ailable   | !         |       |       | BER   | 0     | 0       | ERF<br>1 | 0     | 0     | 0       | SF1          |

| Reg<br>Add                 | Register<br>Name            | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8           | Bit 7        | Bit 6      | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1              | Bit 0<br>LSb  |

|----------------------------|-----------------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-----------------|--------------|------------|-------|--------|-------|-------|--------------------|---------------|

| 000                        | Device                      | R/      | 0h                 |                  |           |           |           | R         | eserve    | ed    | •               |              | •          |       | EnF    | Res   | Low   | Shut               | Res           |

| 101                        | Control                     | W       |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 0               | 0            | 0          | 0     | 1      | 0     | Pwr   | dow<br>n           | et            |

| 001<br>000                 | Temperature<br>Capabilities | R       | 014A<br>h          |                  |           | R         | eserve    | ed        |           |       | Int<br>Sen<br>s | Rout<br>Size | Sign       |       | 10Bits |       |       | 0.25°C<br>esolutio |               |

|                            |                             |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 1               | 0            | 1          | 0     | 0      | 1     | 0     | 1                  | 0             |

| 001                        | Temperature                 | R       |                    | MSb              | 64°       | 32°       | 16°       | 8°C       | 4°C       | 2°C   | 1°C             | 0.5          | LSb        |       |        | Rese  | erved |                    |               |

| 001                        | Data<br>Readout             |         |                    | Sign             | С         | С         | С         |           |           |       |                 | °C           | 0.25<br>°C | 0     | 0      | 0     | 0     | 0                  | 0             |

| 001                        | Temperature                 |         | 0h                 |                  |           |           |           |           |           | Rese  | erved           |              |            |       |        |       |       | EN0                | ATE           |

| 010                        | Control                     | W       |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 0               | 0            | 0          | 0     | 0      | 0     | 0     |                    |               |

| 001<br>011 -<br>011<br>111 | Reserved                    | R       |                    |                  |           |           |           |           |           |       | Unde            | fined        |            |       |        |       |       |                    |               |

| 100<br>000                 | Conversion<br>Rate          | R/W     | 2h                 |                  |           |           | Not Av    | ailable/  |           |       |                 | 0            | 0          | 0     | 0      | 0     | 0     |                    | ersion<br>ate |

| 100<br>001 -<br>111<br>111 | Undefined<br>Registers      | R       |                    |                  |           |           |           |           |           |       | Unde            | fined        |            |       |        |       |       |                    |               |

<sup>\*</sup> Depends on state of ADD pins see Table 2.

## **Device Reset Operation**

A Device Reset operation is performed in the following conditions:

- At device power-up.

- When the Reset bit in the Device Control register is set to 1 (see DEVICE CONTROL (Addr 050)).

The Device Reset operation performs the following:

- Aborts any device operation in progress and restarts device operation.

- Sets all device registers to their "Reset" (default) value.

## **DEVICE NUMBER (Addr 000)**

This register is used to specify a unique address for each device on the bus.

| Reg Add | Register Name | R/<br>W | P<br>O<br>R<br>Val | Bit 7 | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|---------|---------------|---------|--------------------|-------|-------|----------|-------|-------|-------|-------|--------------|

| 000 000 | Device Number | R       | 4h-1h              |       |       | Reserved |       |       | AS2   | AS1   | AS0          |

|         |               |         |                    | 0     | 0     | 0        | 0     | 0     |       |       |              |

The value of AS2:AS0 is determined by the setting of the ADD0 and ADD1 input pins:

**Table 2. Device Number Assignment**

| [ADD1:ADD0] | [AS2:AS0] |

|-------------|-----------|

| 00          | 001       |

| 01          | 010       |

| 10          | 011       |

| 11          | 100       |

The value of AS2:AS0 will directly change and follow the value determined by ADD1:ADD0. Since this is a read only register the value of the address cannot be changed by software.

### **MANUFACTURER ID (Addr 010)**

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 000<br>001 | Manufacture r ID | R       | 100B<br>h          | 0                | 0         | 0         | 1         | 0         | 0         | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 1            |

The manufacturer ID matches that assigned by the PCI SIG. This register may be used to identify the manufacturer of the device in order to perform manufacturer specific operations.

## **DEVICE ID (Addr 020)**

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|---------|-------|-------|-------|-------|--------------|

| 000        | Device ID        | R       | 21h                | ,                |           | RevID     |           |           |           |       |       |       | С     | Devicel | D     |       |       |       | ,            |

| 010        |                  |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 0     | 0     | 0     | 1       | 0     | 0     | 0     | 0     | 1            |

The device ID is defined by the manufacturer of the device and is unique for each device produced by a manufacturer. Bits 15-11 identify the revision number of die and will be incremented upon revision of the device.

| Bit   | Туре | Description                                                                  |  |  |  |  |  |  |

|-------|------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| 10-0  | RO   | eviceID (Device ID Value) A fixed value that identifies the device.          |  |  |  |  |  |  |

| 15-11 | RO   | RevID (Revision ID Value) A fixed value that identifies the device revision. |  |  |  |  |  |  |

## **CAPABILITIES FIXED (Addr 03o)**

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9           | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 000        |                  |         |                    |                  |           |           |           |           |           | FuncDescriptor1 |       |       |       |       |       |       |       |       |              |

| 011        | Fixed            |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0               | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1            |

The value of this register defines the capabilities of the LM95010. The LM95010 supports only one function, that of Temperature Measurement type. Please refer to SensorPath BIT SIGNALING for further details on other FuncDescriptor values.

## **DEVICE STATUS (Addr 040)**

This register is set to the reset value by a Device Reset.

| Reg Add | Register Name | R/<br>W | P<br>O<br>R<br>Val | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|---------|---------------|---------|--------------------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 000 100 | Device Status | R       | 0h                 | BER   | 0     | 0     | ERF1  | 0     | 0     | 0     | SF1          |

| Bit | Туре | Description                                                                                                                                                                                                                                                                                                             |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | RO   | <b>SF1 (Status Function 1).</b> This bit is set by a Function Event within Function 1. Event details are function dependent and are described within the function. SF1 is cleared by Device Reset or by handling the event within the function (seeTEMPERATURE MEASUREMENT FUNCTION (TYPE - 0001) for further details). |

|     |      | 0: Status flag for Function 1 is inactive (no event).                                                                                                                                                                                                                                                                   |

|     |      | 1: Status flag for Function 1 is active indicating that a Function Event has occurred.                                                                                                                                                                                                                                  |

| Bit | Туре | Description                                                                                                                                                                                                                                                           |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-1 | RO   | Not supported. Will always read "0".                                                                                                                                                                                                                                  |

| 4   | RO   | <b>ERF1 (Error Function 1)</b> This bit is set in response to an error indication within Function 1. ERF1 is cleared by Device Reset or by handling the error condition within the function (see TEMPERATURE MEASUREMENT FUNCTION (TYPE - 0001) for further details). |

|     |      | 0: No error occurred in Function 1.                                                                                                                                                                                                                                   |

|     |      | 1: Error occurred in Function 1.                                                                                                                                                                                                                                      |

| 6-5 | RO   | Not supported. Will always read "0".                                                                                                                                                                                                                                  |

| 7   | RO   | <b>BER (Bus Error).</b> This bit is set when the device either generates, or receives an error indication in the ACK bit of the transaction (i.e., no-acknowledge). BER is cleared by Device Reset or by reading the Device Status register.                          |

|     |      | 0: No transaction error occurred.                                                                                                                                                                                                                                     |

|     |      | 1: An ACK bit error (no-acknowledge) occurred during the last transaction.                                                                                                                                                                                            |

## **DEVICE CONTROL (Addr 050)**

This register responds to a broadcast write command (DeviceNumber 000). Write using broadcast address is ignored by bits 15-2. This register is set to the reset value by a Device Reset.

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|------|-------|-------|-------|-------|-------|-------|-------|----------|--------------|

| 000        | Device           | R/      | 0h                 |                  |           |           |           | R         | eserve    | ed   |       |       |       |       | EnF   | Res   | Low   | Shut     | Re           |

| 101        | Control          | W       |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0    | 0     | 0     | 0     | 0     | 1     |       | Pwr   | dow<br>n | set          |

| Bit  | Туре | Description                                                                                                                                                                                                                                                                |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | R/W  | Reset (Device Reset). When set to "1" this bit initiates a Device Reset operation ( See Device Reset Operation). This bit self-clears after the Device Reset operation is completed.                                                                                       |

|      |      | 0: Normal device operation. (default)                                                                                                                                                                                                                                      |

|      |      | 1: Device Reset                                                                                                                                                                                                                                                            |

|      |      | The LM95010 does not require a Device Reset command after power.                                                                                                                                                                                                           |

| 1    | R/W  | <b>Shutdown (Shutdown Mode).</b> When set to "1" this bit stops the operation of all functions and places the device in the lowest power consumption mode.                                                                                                                 |

|      |      | 0: Device in Active Mode. (default)                                                                                                                                                                                                                                        |

|      |      | 1: Device in Shutdown Mode.                                                                                                                                                                                                                                                |

| 2    | R/W  | <b>LowPwr (Low-Power Mode).</b> When set to "1" this bit slows the operation of all functions and places the device in a low power consumption mode. In Low-Power Mode, the conversion rate of the LM95010 is effected see CONVERSION RATE (Addr 40o) for further details. |

|      |      | 0: Device in Active Mode. (default)                                                                                                                                                                                                                                        |

|      |      | 1: Device in Low-Power Mode.                                                                                                                                                                                                                                               |

| 3    | RO   | Not supported. Will always read "0".                                                                                                                                                                                                                                       |

| 4    | R/W  | <b>EnF1 (Enable Function 1).</b> When bit is set to "1" this bit Function 1 is enabled for operation. A function may require setup before this bit is set. The function registers can be accessed even when the function is disabled.                                      |

|      |      | 0: Function 1 is disabled. (default)                                                                                                                                                                                                                                       |

|      |      | 1: Function is enabled.                                                                                                                                                                                                                                                    |

| 15-5 | RO   | Not supported. Will always read "0".                                                                                                                                                                                                                                       |

Product Folder Links: *LM95010*

Copyright © 2003–2013, Texas Instruments Incorporated

#### **TEMPERATURE MEASUREMENT FUNCTION (TYPE - 0001)**

This section defines the register structure and operation of a Temperature Measurement function as it applies to the LM95010. The FuncDescriptor value of this function is '0001'.

#### Operation

The Temperature Measurement function as implemented in the LM95010 supports one temperature zone, the LM95010's internal temperature (LM95010's junction temperature). Since the LM95010 only supports one temperature measurement the Sensor Scan function as defined in SensorPath BIT SIGNALING only applies to one temperature sensor. A temperature scan is enabled by the SensorEnable bit (EN0). The minimum scan rate is recommended to be 4Hz (i.e. the measurement data is updated at least once in 250 ms), see CONVERSION RATE (Addr 400) for further details. In Low-Power Mode, the scan rate is four time lower than the scan rate in Active Mode. The scan rate effects the bus bandwidth required to read the results. The sampling rate of the temperature measurements can also be controlled via the Conversion Rate register, see CONVERSION RATE (Addr 400) for further details.

**Data Readout** When a new result is stored in the Readout register a Function Event is generated. Reading the Readout register clears the Status Function 1 flag (SF1). The result is available in the Readout register waiting for the master to read it during the master sensor read sequence. If a new result is ready before the previous result has been read, the new result overwrites the previous result and the Error Function 1 flag (ERF1) is set (indicating an overrun event). Reading the Readout register clears also the Error Function 1 flag (ERF1). The Readout register contains the temperature data, and the sensor number. Since the LM95010 only supports one temperature zone the sensor number field will always report zero. Other fields in the Readout register as defined by the SensorPath BIT SIGNALING are not supported.

**Readout Resolution** The resolution of the readout is defined in the Temperature Capabilities register. The resolution of the LM95010 is fixed and cannot be modified by software.

**Function Event** The Temperature Measurement function generates a Function Event whenever a temperature conversion cycle is completed and new data is stored in the Readout Register. When the new data is stored into the Readout register the SF1 bit in the device Status register is set to "1" and remains set, until it is cleared by reading the Readout register. An Attention Request is generated on the bus, only if it is enabled by the Attention Enable bit (ATE) in the Temperature Control register.

**Setup Before Enabling** No setup is required for the Temperature Measurement function before the function is enabled.

## Temperature Capabilities (Addr 10o)

| Reg<br>Add | Register<br>Name            | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7        | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2                | Bit 1 | Bit 0<br>LSb |

|------------|-----------------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|--------------|-------|--------|-------|-------|----------------------|-------|--------------|

| 001<br>000 | Temperature<br>Capabilities | R       | 014A<br>h          |                  | Reserved  |           |           |           |           |       |       | Rout<br>Size | Sign  | 10Bits |       |       | 0.25°C<br>Resolution |       |              |

|            |                             |         |                    | 0                | 0         | 0         | 0         | 0         | 0         | 0     | 1     | 0            | 1     | 0      | 0     | 1     | 0                    | 1     | 0            |

This register defines the format of the temperature data in the readout register. The LM95010 only supports one format as defined by the values of this register.

| Bit | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0 | R    | <b>Resolution.</b> This field defines the value of 1 LSb of the Temperature Readout field in the Readout Register. The SensorPath specification defines many different weights for the temperature LSb. The LM95010 supports a resolution of 0.25 °C and thus a value of 010 for this field. For a full definition of this field please refer to the SensorPath specification.                                                                                                              |

| 5-3 | R    | <b>Number of Bits.</b> This field defines the total number of significant bits of the Temperature Readout field in the Readout register. The total number of osignificant bits includes the number of bits representing the interger part of the temperature data and the fractional part of it, as defined by the Resolution field. The LM95010 supports 10 bits and thus a value of 001 for this field. For a full definition of this field please refer to the SensorPath specification. |

#### SNIS133D - SEPTEMBER 2003-REVISED MARCH 2013

| Bit  | Туре | Description                                                                                                                 |

|------|------|-----------------------------------------------------------------------------------------------------------------------------|

| 6    | R    | Sign (Signed Data). Defines the type of data in the Temperature Readout field of the Readout register.                      |

|      |      | 0: Unsigned, positive fixed point value.                                                                                    |

|      |      | 1: Signed, 2's complement fixed point value. (value for the LM95010)                                                        |

| 7    | R    | RoutSize (Readout Register size). Defines the total size of the Readout register.                                           |

|      |      | 0: 16 bits. (LM95010 default)                                                                                               |

|      |      | 1: 24 bits.                                                                                                                 |

| 8    | R/W  | IntSens (Internal Sensor Support). Indicates if the device supports internal temperature measurements, as the LM95010 does. |

|      |      | 0: No internal temperature measurement                                                                                      |

|      |      | 1: Internal temperature sensor implemented. (value for the LM95010)                                                         |

| 15-9 | RO   | Reserved. Will always read "0".                                                                                             |

## Temperature Data Readout (Addr 11o)

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|------------|-------|-------|-------|-------|-------|--------------|

| 001        | Temperature      | R       |                    | MSb              | 64°       | 32°       | 16°       | 8°C       | 4°C       | 2°C   | 1°C   | 0.5   | LSb        |       |       | Rese  | erved |       |              |

| 001        | Data<br>Readout  |         |                    | Sign             | С         | С         | С         |           |           |       |       | °C    | 0.25<br>°C | 0     | 0     | 0     | 0     | 0     | 0            |

The LM95010's temperature data format is two's complement and has 10-bits of resolution with the LSb having a weight of 0.25 °C. The LM95010 can resolve temperature between +127.75 °C and -128 °C, inclusive. It can measure temperatures between +127.75 °C and -20 °C with an accuracy of  $\pm 3.0$  °C.

**Table 3. Temperature Data Format**

| Decimal    | Binary       | Hex   |

|------------|--------------|-------|

| +127.75 °C | 01 1111 1111 | 1FFh  |

| +100.00 °C | 01 1001 0000 | 190h  |

| +1.00 °C   | 00 0000 0100 | 004h  |

| +0.25 °C   | 00 0000 0001 | 001h  |

| 0 °C       | 00 0000 0000 | 000h  |

| -0.25 °C   | 11 1111 1111 | 3FFh  |

| -1.00 °C   | 11 1111 1100 | 3FCh  |

| -20.00 °C  | 11 1011 0000 | 3 B0h |

| -39.75 °C  | 11 0110 0001 | 361h  |

| -40.00 °C  | 11 0110 0000 | 360h  |

| -128.00 °C | 10 0000 0000 | 200h  |

## Temperature Control (Addr 120)

This register is set to the reset value by a Device Reset.

| Reg<br>Add | Register<br>Name | R/<br>W | P<br>O<br>R<br>Val | Bit<br>15<br>MSb | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSb |

|------------|------------------|---------|--------------------|------------------|-----------|-----------|-----------|-----------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 001        | Temperature      |         |                    |                  |           |           |           |           | R         | eserve | b     |       |       |       |       |       |       | EN0   | ATE          |

| 010        | Control          | W       | 0h                 | 0                | 0         | 0         | 0         | 0         | 0         | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |              |

| Bit  | Туре | Description                                                                                                                                                                                                                                |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | R    | ATE (Attention Enable). When set, this bit enables an Attention Request signal to generated by the LM95010, if the EN0 bit is set.  0: Attention Request disabled (from enabled Temperature Sensor- default)  1: Attention Request enabled |

| 1    | R    | EN0 (Enable Sensor). When this bit is set, the Temperature Sensor is enabled for temperature measurements.  0: Temperature Sensor disabled (default)  1: Temperature Sensor enabled                                                        |

| 15-2 | R    | Reserved. Will allways read "0".                                                                                                                                                                                                           |

### **CONVERSION RATE (Addr 40o)**

| F | Reg Add | Register Name   | R/<br>W | P<br>O<br>R<br>Val | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0<br>LSb |

|---|---------|-----------------|---------|--------------------|-------|-------|-------|-------|-------|-------|---------|--------------|

|   | 100 000 | Conversion Rate | R/<br>W | 2h                 | 0     | 0     | 0     | 0     | 0     | 0     | Convers | ion Rate     |