SNAS474H - APRIL 2009 - REVISED MARCH 2015

LM98725

## LM98725 3 Channel, 16-Bit, 81 MSPS Analog Front End with LVDS/CMOS Output, Integrated CCD/CIS Sensor Timing Generator and Spread Spectrum Clock Generation

#### **Features**

- LVDS/CMOS Outputs

- LVDS/CMOS/Crystal Clock Source with PLL Multiplication

- Integrated Flexible Spread Spectrum Clock Generation

- CDS or S/H Processing for CCD or CIS Sensors

- Independent Gain/Offset Correction for Each Channel

- Automatic per-Channel Gain and Offset Calibration

- Programmable Input Clamp Voltage

- Flexible CCD/CIS Sensor Timing Generator

## **Applications**

- Multi-Function Peripherals

- High-speed Currency/Check Scanners

- Flatbed or Handheld Color Scanners

- **High-speed Document Scanners**

## **Key Specifications:**

- Maximum Input Level

- 1.2 or 2.4 Volt Modes

- (Both with + or Polarity Option)

- ADC Resolution: 16-Bit

- ADC Sampling Rate: 81 MSPS

- INL: +17/- 28 LSB (typ)

- Channel Sampling Rate: 30/30/27 MSPS

- PGA Gain Steps: 256 Steps PGA Gain Range: 0.62 to 8.3x - Analog DAC Resolution: ±9 Bits

- Analog DAC Range: ±307 mV or ±614 mV

- Digital DAC Resolution: ±6 Bits

- Digital DAC Range: -2048 LSB to + 2016 LSB

- SNR: –74dB (@0 dB PGA Gain) Power Dissipation: 755 mW (LVDS)

- Operating Temp: 0 to 70°C

- Supply Voltage: 3.3 V Nominal (3.0-V to 3.6-V Range)

## 3 Description

The LM98725 is a fully integrated, high performance 16-Bit, 81 MSPS signal processing solution for digital color copiers, scanners, and other image processing applications. The LM98725 achieves high-speed signal throughput with an innovative architecture utilizing Correlated Double Sampling (CDS), typically employed with CCD arrays, or Sample and Hold (S/H) inputs (for higher speed CCD or CMOS image sensors). The signal paths utilize 8 bit Programmable Gain Amplifiers (PGA), a ±9-Bit offset correction DAC, and independently controlled Digital Black Level correction loops for each input. independently programmed PGA and offset DAC allow unique values of gain and offset for each of the three analog inputs. The signals are then routed to a 81 MHz high performance analog-to-digital converter (ADC). The fully differential processing channel shows exceptional noise immunity with a very low noise floor of -74 dB. The 16-bit ADC has excellent performance making the transparent in the image reproduction chain.

A very flexible integrated Spread Spectrum Clock Generation (SSCG) modulator is included to assist with EM compliance and reduce system costs.

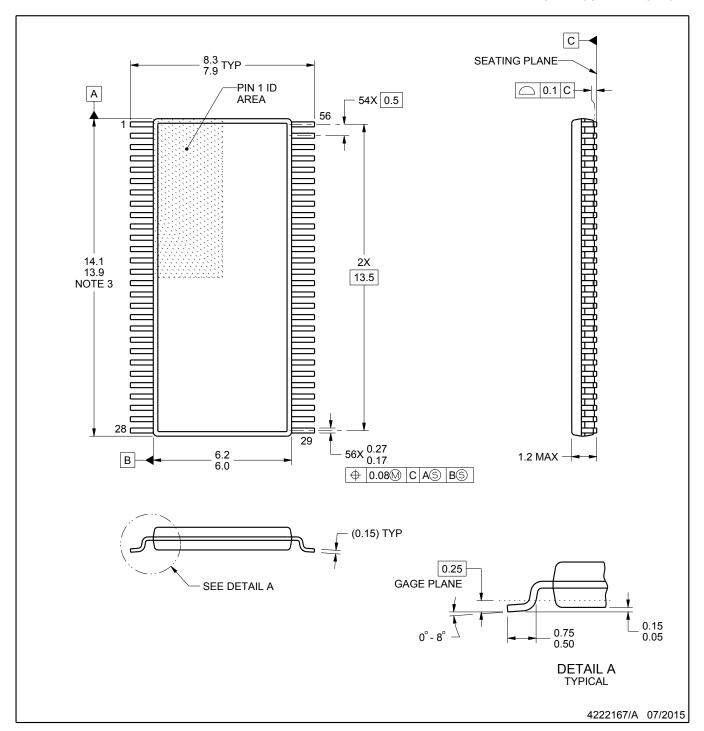

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LM98725     | TSSOP (56) | 14.0 mm × 6.10 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

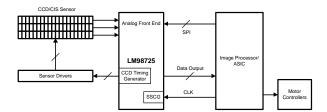

#### System Block Diagram

| Table of Co | ntents |

|-------------|--------|

|-------------|--------|

| 1 | Features 1                           |    | 7.1 Overview                                  | 14  |

|---|--------------------------------------|----|-----------------------------------------------|-----|

| 2 | Applications 1                       |    | 7.2 Functional Block Diagrams                 | 15  |

| 3 | Description 1                        |    | 7.3 Feature Description                       | 16  |

| 4 | Revision History                     |    | 7.4 Device Functional Modes                   | 24  |

|   | Pin Configuration and Functions      |    | 7.5 Register Maps                             | 88  |

| 6 | Specifications6                      | 8  | Layout                                        | 136 |

| U | 6.1 Absolute Maximum Ratings         |    | 8.1 Layout Example                            | 136 |

|   | 6.2 Handling Ratings                 | 9  | <b>Device and Documentation Support</b>       | 137 |

|   | 6.3 Recommended Operating Conditions |    | 9.1 Trademarks                                | 137 |

|   | 6.4 Electrical Characteristics       |    | 9.2 Device Support                            | 137 |

|   | 6.5 AC Timing Specifications         |    | 9.3 Electrostatic Discharge Caution           | 137 |

|   | 6.6 Serial Interface Timing Details  |    | 9.4 Glossary                                  | 137 |

| 7 | Detailed Description                 | 10 | Mechanical, Packaging, and Ordera Information |     |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision G (October 2014) to Revision H                                                                                                                                                     | Page         |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| •  | Changed "29" to "33" for Pin number 32 in Pin Functions                                                                                                                                                 | 4            |

| •  | Deleted "Boldface limits apply" statement in <i>Electrical Characteristics</i> and <i>AC Timing Specifications</i>                                                                                      | <del>7</del> |

| •  | Changed "internal" to "external" and "external" to "internal" for "SH_R Capture Clock Select (Page 0, Register 0x0 Bit 5)" heading in <i>Clock Sources - Additional Settings and Flexibility</i>        |              |

| •  | Changed 25 MHz to 27 MHz and 75 MHz to 81 MHz for Table 3                                                                                                                                               | 24           |

| •  | Changed "Page 2" to "Page 0" in CCD Timing Generator Master/Slave Modes                                                                                                                                 | 63           |

| •  | Changed "Page 2" to "Page 0" in Master Timing Generator Mode                                                                                                                                            | 63           |

| •  | Changed "1100 0000" to " 1100 0010" in Table 18                                                                                                                                                         | 101          |

| •  | Added, updated, or renamed the following sections: Device Information Table, Pin Configuration and Functions; Layout; Device and Documentation Support, Mechanical, Packaging, and Ordering Information | 1            |

| •  | hanges from Revision F (January 2014) to Revision G  Added, updated, or renamed the following sections: Device Information Table, <i>Pin Configuration and Functions</i> ;                              | Page         |

| •  | Added "Note" in Serial Interface                                                                                                                                                                        |              |

| _  |                                                                                                                                                                                                         |              |

| CI | hanges from Revision E (April 2013) to Revision F                                                                                                                                                       | Page         |

| •  | Added content from System Overview section to end of document.                                                                                                                                          | 16           |

| CI | hanges from Revision D (April 2009) to Revision E                                                                                                                                                       | Page         |

| •  | Changed layout of National Data Sheet to TI format                                                                                                                                                      | 13           |

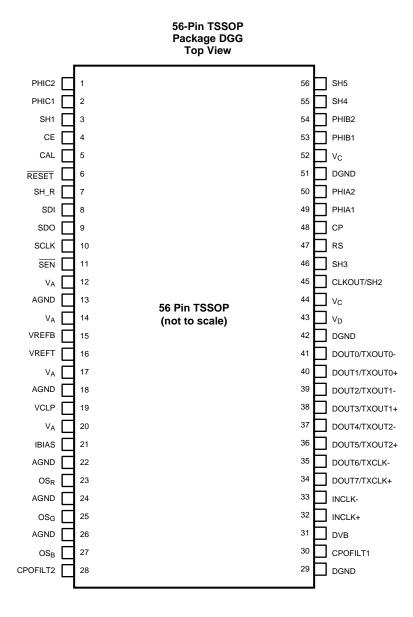

## 5 Pin Configuration and Functions

Copyright © 2009–2015, Texas Instruments Incorporated

Submit Documentation Feedback

## **Pin Functions**

|     | Pin Functions PIN |     |     |     |                                                                                                                                                                                                                                |  |  |

|-----|-------------------|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME              | 1/0 | TYP | RES | DESCRIPTION                                                                                                                                                                                                                    |  |  |

| 1   | PHIC2             | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                                                                                  |  |  |

| 2   | PHIC1             | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                                                                                  |  |  |

| 3   | SH1               | 0   | D   |     | Configurable low speed sensor timing output.                                                                                                                                                                                   |  |  |

| 4   | CE                | 1   | D   |     | Chip Serial Interface Address Setting Input                                                                                                                                                                                    |  |  |

|     |                   |     |     |     | CE Level Address                                                                                                                                                                                                               |  |  |

|     |                   |     |     |     | VD 01                                                                                                                                                                                                                          |  |  |

|     |                   |     |     |     | Float 10                                                                                                                                                                                                                       |  |  |

|     |                   |     |     |     | DGND 00                                                                                                                                                                                                                        |  |  |

| 5   | CAL               | - 1 | D   | PD  | Initiate calibration sequence. Leave unconnected or tie to DGND if unused.                                                                                                                                                     |  |  |

| 6   | RESET             | ı   | D   | PU  | Active-low master reset. NC when function not being used.                                                                                                                                                                      |  |  |

| 7   | SH_R              | ı   | D   | PD  | External request for an SH pulse.                                                                                                                                                                                              |  |  |

| 8   | SDI               | 1   | D   | PD  | Serial Interface Data Input. Can be tied to SDO for compatibility with LM98714 designs.                                                                                                                                        |  |  |

| 9   | SDO               | 0   | D   |     | Serial Interface Data Output. Can be tied to SDI for compatibility with LM98714 designs.                                                                                                                                       |  |  |

| 10  | SCLK              | 1   | D   | PD  | Serial Interface shift register clock.                                                                                                                                                                                         |  |  |

| 11  | SEN               | 1   | D   | PU  | Active-low chip enable for the Serial Interface.                                                                                                                                                                               |  |  |

| 12  | V <sub>A</sub>    |     | Р   |     | Analog power supply. Bypass voltage source with 4.7µF and pin with 0.1µF to AGND.                                                                                                                                              |  |  |

| 13  | AGND              |     | Р   |     | Analog ground return.                                                                                                                                                                                                          |  |  |

| 14  | V <sub>A</sub>    |     | Р   |     | Analog power supply. Bypass voltage source with 4.7µF and pin with 0.1µF to AGND.                                                                                                                                              |  |  |

| 15  | VREFB             | 0   | Α   |     | Bottom of ADC reference. Bypass with a 0.1µF capacitor to ground.                                                                                                                                                              |  |  |

| 16  | VREFT             | 0   | Α   |     | Top of ADC reference. Bypass with a 0.1µF capacitor to ground.  Analog power supply. Bypass voltage source with 4.7µF and pip with 0.1µF to AGND.                                                                              |  |  |

| 17  | V <sub>A</sub>    |     | Р   |     | Analog power supply. Bypass voltage source with 4.7μF and pin with 0.1μF to AGND.                                                                                                                                              |  |  |

| 18  | AGND              |     | Р   |     | Analog ground return.                                                                                                                                                                                                          |  |  |

| 19  | VCLP              | Ю   | Α   |     | Input Clamp Voltage. Normally bypassed with a 0.1µF, and a 4.7µF capacitor to AGND. An external reference voltage may be applied to this pin.                                                                                  |  |  |

| 20  | V <sub>A</sub>    |     | Р   |     | Analog power supply. Bypass voltage source with 4.7µF and pin with 0.1µF to AGND.                                                                                                                                              |  |  |

| 21  | IBIAS             | 0   | Α   |     | Bias setting pin. Connect a 9.0 kΩ 1% resistor to AGND.                                                                                                                                                                        |  |  |

| 22  | AGND              |     | Р   |     | Analog ground return.                                                                                                                                                                                                          |  |  |

| 23  | OS <sub>R</sub>   | ı   | Α   |     | Analog input signal. Typically sensor Red output AC-coupled thru a capacitor.                                                                                                                                                  |  |  |

| 24  | AGND              |     | Р   |     | Analog ground return.                                                                                                                                                                                                          |  |  |

| 25  | OS <sub>G</sub>   | I   | Α _ |     | Analog input signal. Typically sensor Green output AC-coupled thru a capacitor.                                                                                                                                                |  |  |

| 26  | AGND              |     | P   |     | Analog ground return.                                                                                                                                                                                                          |  |  |

| 27  | OS <sub>B</sub>   | 1   | A   |     | Analog input signal. Typically sensor Blue output AC-coupled thru a capacitor.                                                                                                                                                 |  |  |

| 28  | CPOFILT2          |     | Α   |     | Charge Pump Filter Capacitor. Bypass this supply pin with a 0.1µF capacitor to CPOFILT1.                                                                                                                                       |  |  |

| 29  | DGND              |     | Р   |     | Digital ground return.                                                                                                                                                                                                         |  |  |

| 30  | CPOFILT1          |     | A   |     | Charge Pump Filter Capacitor.  Bypass this supply pin with a 0.1µF capacitor to CPOFILT2.                                                                                                                                      |  |  |

| 31  | DVB               | 0   | D   |     | Digital Core Voltage bypass. Not an input. Bypass with 0.1µF capacitor to DGND.                                                                                                                                                |  |  |

| 32  | INCLK+            | I   | D   |     |                                                                                                                                                                                                                                |  |  |

| 33  | INCLK-            | I   | D   |     | Clock Input. When XTALEN=0 Inverting input for LVDS clocks, connect to DGND for CMOS clock. When XTALEN=1 Connection to terminal 1 of crystal. A 18 pF capacitor should be connected from terminal 1 of the crystal to ground. |  |  |

Submit Documentation Feedback

Copyright © 2009–2015, Texas Instruments Incorporated

## Pin Functions (continued)

|     | PIN            |     |     |     | DESCRIPTION                                                                                                                                                                |  |  |

|-----|----------------|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME           | I/O | TYP | RES | DESCRIPTION                                                                                                                                                                |  |  |

| 34  | DOUT7/         | 0   | D   |     | Bit 7 of the digital video output bus in CMOS Mode, LVDS Frame Clock+ in LVDS Mode.                                                                                        |  |  |

|     | TXCLK+         |     |     |     |                                                                                                                                                                            |  |  |

| 35  | DOUT6/         | 0   | D   |     | Bit 6 of the digital video output bus in CMOS Mode, LVDS Frame Clock- in LVDS Mode.                                                                                        |  |  |

|     | TXCLK-         |     |     |     |                                                                                                                                                                            |  |  |

| 36  | DOUT5/         | 0   | D   |     | Bit 5 of the digital video output bus in CMOS Mode, LVDS Data Out2+ in LVDS Mode.                                                                                          |  |  |

|     | TXOUT2+        |     |     |     |                                                                                                                                                                            |  |  |

| 37  | DOUT4/         | 0   | D   |     | Bit 4 of the digital video output bus in CMOS Mode, LVDS Data Out2- in LVDS Mode.                                                                                          |  |  |

|     | TXOUT2-        |     |     |     |                                                                                                                                                                            |  |  |

| 38  | DOUT3/         | 0   | D   |     | Bit 3 of the digital video output bus in CMOS Mode, LVDS Data Out1+ in LVDS Mode.                                                                                          |  |  |

|     | TXOUT1+        |     |     |     |                                                                                                                                                                            |  |  |

| 39  | DOUT2/         | 0   | D   |     | Bit 2 of the digital video output bus in CMOS Mode, LVDS Data Out1- in LVDS Mode.                                                                                          |  |  |

|     | TXOUT1-        |     |     |     |                                                                                                                                                                            |  |  |

| 40  | DOUT1/         | 0   | D   |     | Bit 1 of the digital video output bus in CMOS Mode, LVDS Data Out0+ in LVDS Mode.                                                                                          |  |  |

|     | TXOUT0+        |     |     |     |                                                                                                                                                                            |  |  |

| 41  | DOUT0/         | 0   | D   |     | Bit 0 of the digital video output bus in CMOS Mode, LVDS Data Out0- in LVDS Mode.                                                                                          |  |  |

|     | TXOUT0-        |     |     |     |                                                                                                                                                                            |  |  |

| 42  | DGND           | 0   | р   |     | Digital ground return.                                                                                                                                                     |  |  |

| 43  | $V_D$          |     | Р   |     | Power supply for the digital circuits. Bypass this supply pin with 0.1µF capacitor. A single 4.7µF capacitor should be used between the supply and the VD, VR and VC pins. |  |  |

| 44  | V <sub>C</sub> |     | Р   |     | Power supply for the sensor control outputs. Bypass this supply pin with 0.1µF capacitor.                                                                                  |  |  |

| 45  | CLKOUT/SH2     | 0   | D   |     | Output clock for registering output data when using CMOS outputs, or a configurable low speed sensor timing output.                                                        |  |  |

| 46  | SH3            | 0   | D   |     | Configurable low speed sensor timing output.                                                                                                                               |  |  |

| 47  | RS             | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 48  | СР             | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 49  | PHIA1          | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 50  | PHIA2          | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 51  | DGND           |     | Р   |     | Digital ground return.                                                                                                                                                     |  |  |

| 52  | V <sub>C</sub> |     | Р   |     | Power supply for the sensor control outputs. Bypass this supply pin with 0.1µF capacitor.                                                                                  |  |  |

| 53  | PHIB1          | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 54  | PHIB2          | 0   | D   |     | Configurable high speed sensor timing output.                                                                                                                              |  |  |

| 55  | SH4            | 0   | D   | -   | Configurable low speed sensor timing output.                                                                                                                               |  |  |

| 56  | SH5            | 0   | D   |     | Configurable low speed sensor timing output.                                                                                                                               |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings (1)(2)(3)

|                                                                      | MIN  | MAX | UNIT |

|----------------------------------------------------------------------|------|-----|------|

| Any Positive Supply Voltage (VA, VR, VD, VC)                         |      | 4.2 | V    |

| Voltage on Any Input or Output Pin (except DVB) (Not to exceed 4.2V) | -0.3 | 4.2 | V    |

| DVB Output Voltage                                                   |      | 2.0 | V    |

| Input Current at any pin <sup>(4)</sup>                              |      | ±25 | mA   |

| Package Input Current <sup>(4)</sup>                                 |      | ±50 | mA   |

| Package Dissipation at T <sub>A</sub> = 25°C <sup>(5)</sup>          |      | 1.9 | W    |

| Soldering Temperature, Infrared, 10 seconds (6)                      |      | 235 | °C   |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

- All voltages are measured with respect to A<sub>GND</sub> = D<sub>GND</sub> = 0V, unless otherwise specified.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sub>A</sub> or V<sub>D</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

- (5) The absolute maximum junction temperature (T<sub>JMAX</sub>) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>JMAX</sub>, the junction to ambient thermal resistance (R<sub>θJA</sub>), and the ambient temperature (TA), and can be calculated using the formula PDMAX = (T<sub>JMAX</sub> TA)/R<sub>θJA</sub>. The values for maximum power dissipation listed will be reached only when the LM98725 is operated in a severe faulty condition.

- (6) See AN450, "Surface Mounting Methods and Their Effect on Product Reliability", or the section entitled "Surface Mount" found in any post 1986 Texas Instruments Semiconductor Linear Data Book, for other methods of soldering surface mount devices.

## 6.2 Handling Ratings

|                    | 0                           |                                                                               |     |      |      |

|--------------------|-----------------------------|-------------------------------------------------------------------------------|-----|------|------|

|                    |                             |                                                                               | MIN | MAX  | UNIT |

| T <sub>stg</sub>   | Storage temperature rang    | storage temperature range                                                     |     | +150 | °C   |

| V                  | Electrostatic discharge (1) | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (2)              |     | 2500 | V    |

| V <sub>(ESD)</sub> |                             | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (3) |     | 250  | V    |

- (1) Human body model is 100 pF capacitor discharged through a 1.5-kΩ resistor. Machine model is 220-pF discharged through 0Ω.

- (2) JEDEC document JEP155 states that 2500-V HBM allows safe manufacturing with a standard ESD control process.

- (3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions (1)(2)

|                             | MIN   | MAX                  | UNIT |

|-----------------------------|-------|----------------------|------|

| Operating Temperature Range | 0 ≤ . | T <sub>A</sub> ≤ +70 | ô    |

| All Supply Voltage          | +3.0  | +3.6                 | V    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

- (2) All voltages are measured with respect to AGND = DGND = 0V, unless otherwise specified.

### 6.4 Electrical Characteristics

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 27 MHz unless otherwise specified. all other limits  $T_A$  = 25°C. (1)

|                    | PARAMETER                     | TEST CONDITIONS                                          | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|--------------------|-------------------------------|----------------------------------------------------------|--------------------|--------------------|--------------------|------|

| CMOS D             | IGITAL INPUT DC SPECIFICATION | ONS (RESETb, SH_R, SCLK, SENb)                           |                    |                    |                    |      |

| V <sub>IH</sub>    | Logical "1" Input Voltage     |                                                          | 2.0                |                    |                    | V    |

| V <sub>IL</sub>    | Logical "0" Input Voltage     |                                                          |                    |                    | 0.8                | V    |

| V <sub>IHYST</sub> | Logic Input Hysteresis        |                                                          |                    | 0.6                |                    | V    |

|                    |                               | V <sub>IH</sub> = VD:                                    |                    |                    |                    |      |

|                    |                               | RESET, SEN                                               |                    | 100                |                    | nA   |

| I <sub>IH</sub>    | Logical "1" Input Current     | SH_R, SCLK, SDI, CAL                                     |                    | 65                 |                    | •    |

|                    |                               | CE                                                       |                    | 30                 |                    | μA   |

|                    |                               | V <sub>IL</sub> = DGND:                                  | <b>"</b>           |                    | · ·                |      |

|                    |                               | RESET, SEN                                               |                    | -65                |                    | μA   |

| I <sub>IL</sub>    | Logical "0" Input Current     | SH_R, SCLK, SDI, CAL                                     |                    | -100               |                    | nA   |

|                    |                               | CE                                                       |                    | -30                |                    | μA   |

| CMOS D             | DIGITAL OUTPUT DC SPECIFICA   | TIONS (SH1 to SH5, RS, CP, PHIA, PHIB, PHIC)             |                    |                    |                    |      |

| V <sub>OH</sub>    | Logical "1" Output Voltage    | I <sub>OUT</sub> = -0.5 mA                               | 3.0                |                    |                    | V    |

| V <sub>OL</sub>    | Logical "0" Output Voltage    | I <sub>OUT</sub> = 1.6 mA                                |                    |                    | 0.21               | V    |

| I <sub>OS</sub>    | Output Short Circuit Current  | V <sub>OUT</sub> = DGND                                  |                    | 18                 |                    |      |

| 00                 | ·                             | V <sub>OUT</sub> = VD                                    |                    | -25                |                    | mA   |

| I <sub>OZ</sub>    | CMOS Output TRI-STATE         | V <sub>OUT</sub> = DGND                                  |                    | 20                 |                    |      |

| 02                 | Current                       | V <sub>OUT</sub> = VD                                    |                    | -25                |                    | nA   |

| CMOS D             | DIGITAL OUTPUT DC SPECIFICA   | TIONS (CMOS DATA OUTPUTS)                                |                    |                    |                    |      |

| V <sub>OH</sub>    | Logical "1" Output Voltage    | I <sub>OUT</sub> = -0.5 mA                               |                    | 2.3                |                    | V    |

| V <sub>OL</sub>    | Logical "0" Output Voltage    | I <sub>OUT</sub> = 1.6 mA                                |                    | 0.12               |                    | V    |

| I <sub>OS</sub>    | Output Short Circuit Current  | V <sub>OUT</sub> = DGND                                  |                    | 12                 |                    |      |

|                    |                               | V <sub>OUT</sub> = VD                                    |                    | -14                |                    | mA   |

| l <sub>OZ</sub>    | CMOS Output TRI-STATE         | V <sub>OUT</sub> = DGND                                  |                    | 20                 |                    |      |

|                    | Current                       | $V_{OUT} = VD$                                           |                    | -25                |                    | nA   |

| LVDS/CI            | MOS CLOCK RECEIVER DC SPE     | CIFICATIONS (INCLK+ and INCLK-PINS)                      | <b>"</b>           |                    | · ·                |      |

| V <sub>IHL</sub>   | Differential LVDS Clock       |                                                          |                    |                    | 222                |      |

|                    | High Threshold Voltage        | $R_1 = 100 \Omega$                                       |                    |                    | 200                | mV   |

| V <sub>ILL</sub>   | Differential LVDS Clock       | V <sub>CM</sub> (LVDS Input Common Mode Voltage)= 1.25 V | 000                |                    |                    |      |

|                    | Low Threshold Voltage         |                                                          | -200               |                    |                    | mV   |

| $V_{IHC}$          | CMOS Clock                    |                                                          |                    |                    |                    |      |

|                    | High Threshold Voltage        |                                                          | 2.0                |                    |                    | V    |

| V <sub>ILC</sub>   | CMOS Clock                    | INCLK- = DGND                                            |                    |                    |                    | ,,   |

| -                  | Low Threshold Voltage         |                                                          |                    |                    | 8.0                | V    |

| I <sub>IHL</sub>   | CMOS Clock                    |                                                          |                    |                    | 225                |      |

|                    | Input High Current            |                                                          |                    | 230                | 260                | μΑ   |

| I <sub>ILC</sub>   | CMOS Clock                    |                                                          | 105                | 400                |                    |      |

|                    | Input Low Current             |                                                          | -135               | -120               |                    | μΑ   |

<sup>(1)</sup> The analog inputs are protected as shown in Figure 2. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per Note 4 under the Absolute Maximum Ratings Table. However, input errors will be generated If the input goes above VA and below AGND.

<sup>(2)</sup> Test limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level).

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

## **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 27 MHz unless otherwise specified. all other limits  $T_A$  = 25°C. (1)

|                     | PARAMETER                                                                   | TEST CONDITIONS                                                                                 | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT   |

|---------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------|

| LVDS OL             | JTPUT DC SPECIFICATIONS                                                     |                                                                                                 |                    |                    |                    |        |

| V <sub>OD</sub>     | Differential Output Voltage                                                 | $R_L = 100 \Omega$                                                                              | 280                | 390                | 490                | mV     |

| Vos                 | LVDS Output Offset Voltage                                                  |                                                                                                 | 1.08               | 1.20               | 1.33               | V      |

| I <sub>OS</sub>     | Output Short Circuit Current                                                | $V_{OUT} = 0 \text{ V}, R_L = 100 \Omega$                                                       |                    | 8.5                |                    | mA     |

| POWER               | SUPPLY SPECIFICATIONS                                                       |                                                                                                 |                    |                    |                    |        |

|                     |                                                                             | LVDS Output Data Format                                                                         |                    | 152                | 180                | mA     |

| IA                  | VA Analog Supply Current                                                    | LVDS Output Data Format (Powerdown)                                                             |                    | 3.6                | 6                  | mA     |

|                     |                                                                             | CMOS Output Data Format<br>(40 MHz)                                                             |                    | 136                | 168                | mA     |

|                     |                                                                             | LVDS Output Data Format                                                                         |                    | 76                 | 94                 | mA     |

| ID                  | VD Digital Output Driver<br>Supply Current                                  | LVDS Output Data Format (Powerdown)                                                             |                    | 8.5                | 17                 | mA     |

|                     | опрлу опполи                                                                | CMOS Output Data Format<br>(ATE Loading of CMOS Outputs > 50 pF) (40 MHz)                       |                    | 46                 | 68                 | mA     |

| IC                  | VC CCD Timing Generator<br>Output Driver Supply Current                     | Typical sensor outputs: SH1-SH5, PHIA, PHIB, PHIC, RS, CP (ATE Loading of CMOS Outputs > 50 pF) |                    | 1                  | 4                  | mA     |

|                     |                                                                             | LVDS Output Data Format                                                                         |                    | 755                | 885                | mW     |

| PWR                 | Average Power Dissipation                                                   | LVDS Output Data Format (Powerdown)                                                             |                    | 40                 | 70                 | mW     |

|                     |                                                                             | CMOS Output Data Format<br>(ATE Loading of CMOS Outputs > 50 pF) (40 MHz)                       |                    | -                  | 740                | mW     |

| INPUT S             | AMPLING CIRCUIT SPECIFICAT                                                  | IONS                                                                                            | *                  |                    |                    |        |

| \/                  | logest Voltage Level                                                        | CDS Gain=1x, PGA Gain=1x                                                                        |                    | 2.3                |                    | \/m == |

| $V_{IN}$            | Input Voltage Level                                                         | CDS Gain=2x, PGA Gain= 1x                                                                       |                    | 1.22               |                    | Vp-p   |

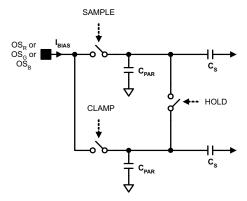

|                     |                                                                             | Source Followers Off CDS/SH Gain = 1x OS <sub>X</sub> = VA (OS <sub>X</sub> = AGND)             | (-200)             | 32<br>(-165)       | 50                 | μA     |

| I <sub>IN_SH</sub>  | Sample and Hold Mode<br>Input Leakage Current<br>(Vclamp = Default = 2.6 V) | Source Followers Off<br>CDS/SH Gain = 2x<br>OS <sub>X</sub> = VA (OS <sub>X</sub> = AGND)       | (-290)             | 55<br>(–240)       | 70                 | μΑ     |

|                     |                                                                             | Source Followers On<br>CDS/SH Gain = 2x<br>OS <sub>X</sub> = VA (OS <sub>X</sub> = AGND)        | (-250)             | 20<br>(–50)        | 250                | nA     |

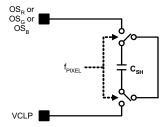

|                     | Sample/Hold Mode                                                            | CDS Gain = 1x                                                                                   |                    | 2.5                |                    | pF     |

| C <sub>SH</sub>     | Equivalent Input Capacitance (see Figure 12)                                | CDS Gain = 2x                                                                                   |                    | 4                  |                    | pF     |

| I <sub>IN_CDS</sub> | CDS Mode<br>Input Leakage Current                                           | Source Followers Off $OS_X = VA (OS_X = AGND)$                                                  | (-250)             | 10<br>(–50)        | 250                | nA     |

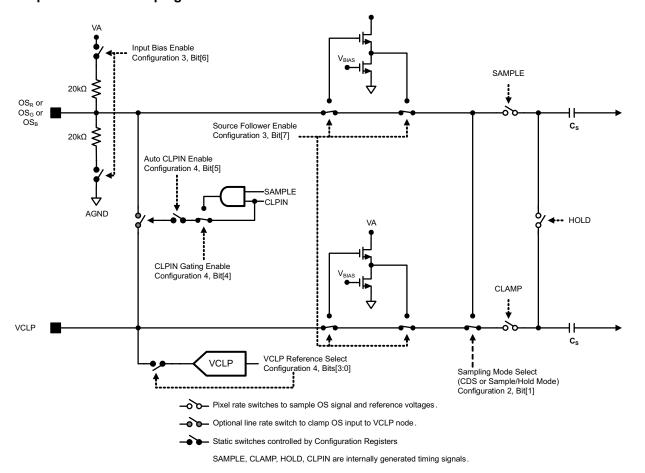

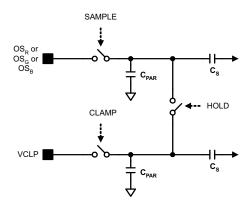

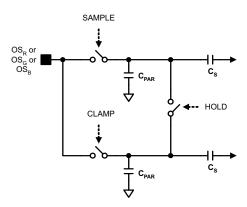

| R <sub>CLPIN</sub>  | CLPIN Switch Resistance<br>(OS <sub>X</sub> to VCLP Node in<br>Figure 9)    |                                                                                                 |                    | 16                 | 55                 | Ω      |

## **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 27 MHz unless otherwise specified. all other limits  $T_A$  = 25°C.<sup>(1)</sup>

|                 | PARAMETER                             | TEST CONDITIONS                                                              | MIN <sup>(2)</sup> | TYP <sup>(3)</sup>          | MAX <sup>(2)</sup> | UNIT  |

|-----------------|---------------------------------------|------------------------------------------------------------------------------|--------------------|-----------------------------|--------------------|-------|

| VCLP RI         | EFERENCE CIRCUIT SPECIFIC             | ATIONS                                                                       |                    |                             |                    |       |

|                 | VCLP Voltage 000                      | VCLP Voltage Setting = 000                                                   |                    | 0.85VA                      |                    | V     |

|                 | VCLP Voltage 001                      | VCLP Voltage Setting = 001                                                   |                    | 0.9VA                       |                    | V     |

|                 | VCLP Voltage 010                      | VCLP Voltage Setting = 010                                                   |                    | 0.95VA                      |                    | V     |

| \               | VCLP Voltage 011                      | VCLP Voltage Setting = 011                                                   |                    | 0.6VA                       |                    | V     |

| $V_{VCLP}$      | VCLP Voltage 100                      | VCLP Voltage Setting = 100                                                   |                    | 0.55VA                      |                    | V     |

|                 | VCLP Voltage 101                      | VCLP Voltage Setting = 101                                                   |                    | 0.4VA                       |                    | V     |

|                 | VCLP Voltage 110                      | VCLP Voltage Setting = 110                                                   |                    | 0.35VA                      |                    | V     |

|                 | VCLP Voltage 111                      | VCLP Voltage Setting = 111                                                   |                    | 0.15VA                      |                    | V     |

| I <sub>SC</sub> | VCLP DAC Short Circuit Output Current |                                                                              |                    | 30                          |                    | mA    |

| BLACK           | LEVEL OFFSET DAC SPECIFIC             | CATIONS                                                                      | <u>'</u>           |                             |                    |       |

|                 | Resolution                            |                                                                              |                    | 10                          |                    | Bits  |

|                 | Monotonicity                          |                                                                              |                    | nsured by                   |                    |       |

|                 |                                       | CDS Gain = 1x                                                                |                    |                             |                    |       |

|                 |                                       | Minimum DAC Code = 0x000                                                     |                    | -614                        |                    | mV    |

|                 | Offset Adjustment Range               | Maximum DAC Code = 0x3FF                                                     |                    | 614                         |                    |       |

|                 | Referred to AFE Input                 | CDS Gain = 2x                                                                |                    |                             |                    |       |

|                 |                                       | Minimum DAC Code = 0x000                                                     |                    | -307                        |                    | mV    |

|                 |                                       | Maximum DAC Code = 0x3FF                                                     |                    | 307                         |                    |       |

|                 | Offset Adjustment Range               | Minimum DAC Code = 0x000                                                     | -17500             |                             | -16130             | LCD   |

|                 | Referred to AFE Output                | Maximum DAC Code = 0x3FF                                                     | +16130             |                             | +17500             | LSB   |

|                 | DAO I OD Otara O'                     | CDS Gain = 1x                                                                |                    | 1.2                         |                    | mV    |

|                 | DAC LSB Step Size                     | Referred to AFE Output                                                       |                    | (32)                        |                    | (LSB) |

| DNL             | Differential Non-Linearity            |                                                                              | -0.84              | +0.74/<br>-0.37             | +2.4               | LSB   |

| INL             | Integral Non-Linearity                |                                                                              | -2.5               | +0.72/<br>-0.56             | +2.5               | LSB   |

| PGA SP          | ECIFICATIONS                          | •                                                                            | ·                  |                             |                    | •     |

|                 | Gain Resolution                       |                                                                              |                    | 8                           |                    | Bits  |

|                 | Monotonicity                          |                                                                              |                    | Ensured by characterization |                    |       |

|                 | Maximum Cain                          | CDS Gain = 1x                                                                | 7.7                | 8.3                         | 8.8                | V/V   |

|                 | Maximum Gain                          | CDS Gain = 1x                                                                | 17.7               | 18.4                        | 18.9               | dB    |

|                 | Minimum Coin                          | CDS Gain = 1x                                                                | 0.58               | 0.62                        | 0.67               | V/V   |

|                 | Minimum Gain                          | CDS Gain = 1x                                                                | -4.7               | -4.2                        | -3.5               | dB    |

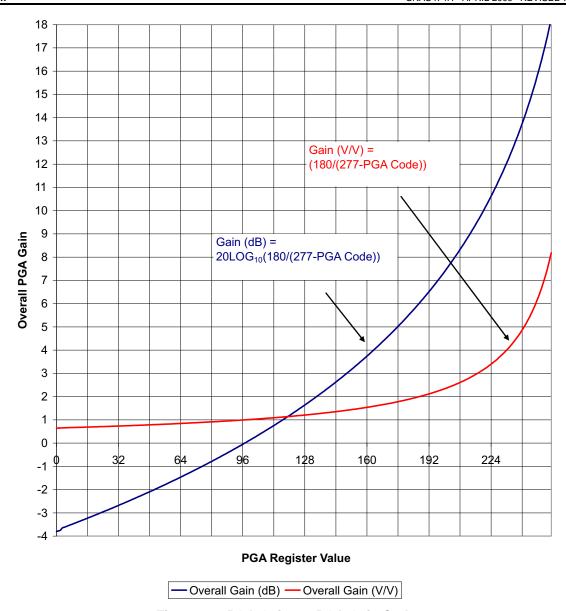

|                 | PGA Function                          | Gain (V/V) = (180/(277-PGA Code))<br>Gain (dB) = 20LOG10(180/(277-PGA Code)) |                    |                             |                    |       |

|                 | Channel Matchine                      | Minimum PGA Gain                                                             |                    | 3%                          |                    |       |

|                 | Channel Matching                      | Maximum PGA Gain                                                             |                    | 12.7%                       |                    |       |

## **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 27 MHz unless otherwise specified. all other limits  $T_A$  = 25°C. (1)

|                                          | PARAMETER                                         | TEST CONDITIONS                 | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT       |

|------------------------------------------|---------------------------------------------------|---------------------------------|--------------------|--------------------|--------------------|------------|

| ADC SPE                                  | ECIFICATIONS                                      |                                 |                    |                    |                    |            |

| V <sub>REFT</sub>                        | Top of Reference                                  |                                 |                    | 2.07               |                    | V          |

| $V_{REFB}$                               | Bottom of Reference                               |                                 |                    | 0.89               |                    | V          |

| V <sub>REFT</sub> -<br>V <sub>REFB</sub> | Differential Reference Voltage                    |                                 | 1.06               | 1.18               | 1.30               | V          |

|                                          | Over range Output Code                            |                                 |                    | 65535              |                    |            |

|                                          | Under range Output Code                           |                                 |                    | 0                  |                    |            |

| DIGITAL                                  | OFFSET "DAC" SPECIFICATION                        | NS                              | •                  |                    |                    |            |

|                                          | Resolution                                        |                                 |                    | 7                  |                    | Bits       |

|                                          | Digital Offset DAC LSB Step<br>Size               | Referred to AFE Output          |                    | 32                 |                    | LSB        |

|                                          |                                                   | Min DAC Code =7'b0000000        |                    | -2048              |                    |            |

|                                          | Offset Adjustment Range<br>Referred to AFE Output | Mid DAC Code =7'b1000000        |                    | 0                  |                    | LSB        |

|                                          | Referred to Ar E Output                           | Max DAC Code = 7'b1111111       | +2016              |                    |                    |            |

| FULL CH                                  | IANNEL PERFORMANCE SPECI                          | FICATIONS                       |                    |                    |                    |            |

| DNL                                      | Differential Non-Linearity                        | See (4)                         | -0.999             | +0.8/<br>-0.7      | 2.5                | LSB        |

| INL                                      | Integral Non-Linearity                            | See (4)                         | -75                | +18/<br>-25        | 75                 | LSB        |

|                                          |                                                   |                                 |                    | -76                |                    | dB         |

| SNR Tota                                 | Tatal Output Naisa                                | Minimum PGA Gain (4)            |                    | 10                 | 26                 | LSB<br>RMS |

|                                          | Total Output Noise                                |                                 |                    | -56                |                    | dB         |

|                                          |                                                   | Maximum PGA Gain <sup>(4)</sup> |                    | 96                 |                    | LSB<br>RMS |

|                                          | Channel to Channel Constalle                      | Mode 3                          |                    | 26                 |                    | 1.05       |

|                                          | Channel to Channel Crosstalk                      | Mode 2                          |                    | 17                 |                    | LSB        |

<sup>(4)</sup> This parameter ensured by design and characterization.

Submit Documentation Feedback

Copyright © 2009–2015, Texas Instruments Incorporated

10

## 6.5 AC Timing Specifications

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 27 MHz unless otherwise specified. All other limits  $T_A$  = 25°C. (1)

|                   | PARAMETER                     | TEST CONDITIONS                   | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT      |  |

|-------------------|-------------------------------|-----------------------------------|--------------------|--------------------|--------------------|-----------|--|

| INPUT (           | CLOCK TIMING SPECIFICATIONS   |                                   |                    |                    |                    |           |  |

|                   |                               |                                   | 0.66               |                    | 27<br>(Mode 3)     |           |  |

|                   |                               | INCLK = PIXCLK (Pixel Rate Clock) | 1                  |                    | 30<br>(Mode 2)     | MHz       |  |

| f                 | Input Clock Frequency         |                                   | 1                  |                    | 30<br>(Mode 1)     |           |  |

| finclk            | input Glock Frequency         |                                   | 2                  |                    | 81<br>(Mode 3)     | MHz       |  |

|                   |                               | INCLK = ADCCLK (ADC Rate Clock)   | 2                  |                    | 60<br>(Mode 2)     |           |  |

|                   |                               |                                   | 2                  |                    | 30<br>(Mode 1)     |           |  |

| T <sub>dc</sub>   | Input Clock Duty Cycle        |                                   | 40/60%             | 50/50%             | 60/40%             |           |  |

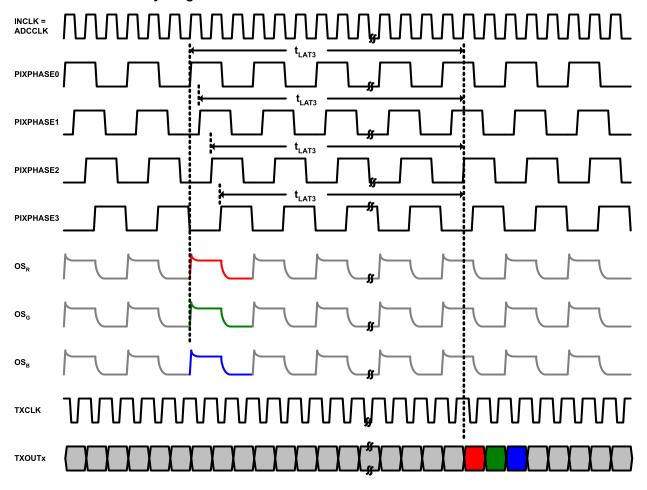

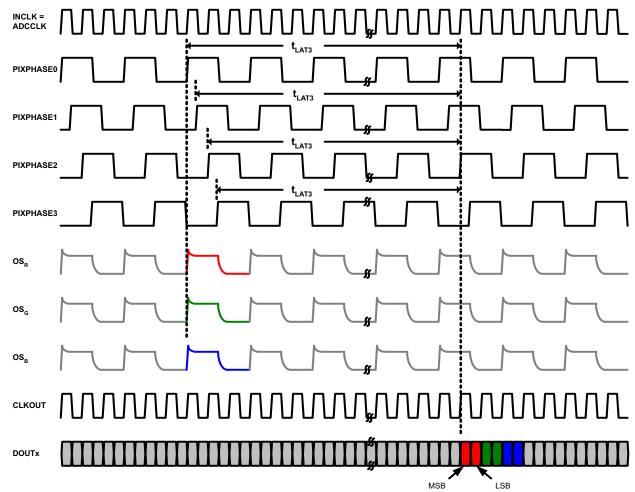

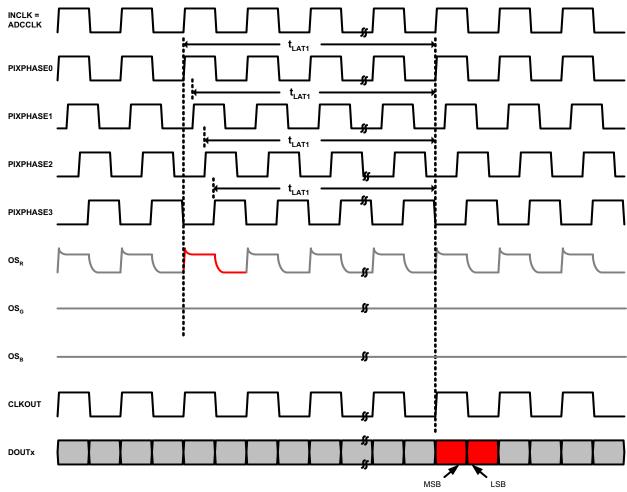

| FULL C            | HANNEL LATENCY SPECIFICATIONS |                                   |                    |                    |                    |           |  |

|                   | 3 Channel Mode Pipeline Delay | PIXPHASE0                         | 24                 |                    |                    |           |  |

|                   | Figure 54 (LVDS)              | PIXPHASE1                         |                    | 23.5               |                    | -         |  |

| t <sub>LAT3</sub> | Figure 59 (CMOS)              | PIXPHASE2                         |                    | 23                 |                    | $T_{ADC}$ |  |

|                   |                               | PIXPHASE3                         |                    | 22.5               |                    |           |  |

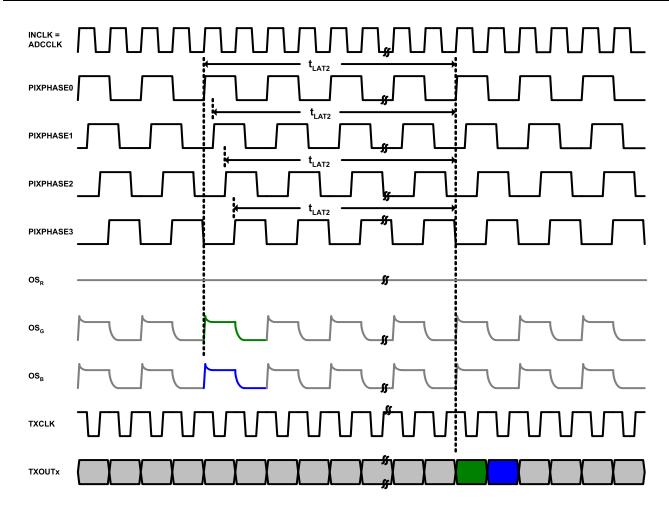

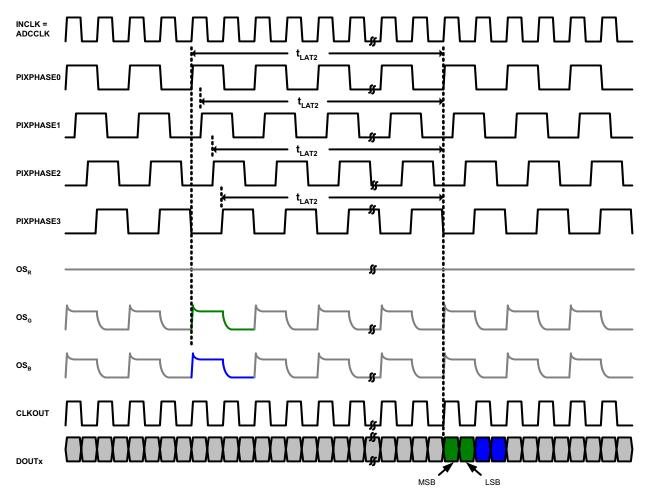

|                   | 2 Channel Mode Pipeline Delay | PIXPHASE0                         |                    | 21                 |                    |           |  |

|                   | Figure 55 (LVDS)              | PIXPHASE1                         |                    | 20.5               |                    | _         |  |

| t <sub>LAT2</sub> | Figure 60 (CMOS)              | PIXPHASE2                         |                    | 20                 |                    | $T_{ADC}$ |  |

| _                 |                               | PIXPHASE3                         |                    |                    |                    |           |  |

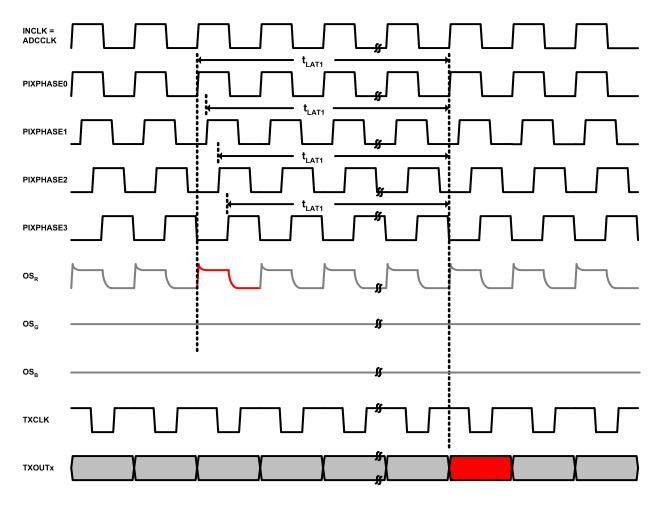

|                   | 1 Channel Mode Pipeline Delay | PIXPHASE0                         |                    | 19                 |                    |           |  |

|                   | Figure 56 (LVDS)              | PIXPHASE1                         |                    | 18.5               |                    | _         |  |

| t <sub>LAT1</sub> | Figure 61 (CMOS)              | PIXPHASE2                         | 18<br>17.5         |                    |                    | $T_{ADC}$ |  |

|                   |                               | PIXPHASE3                         |                    |                    |                    |           |  |

<sup>(1)</sup> The analog inputs are protected as shown in Figure 2. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per Note 4 under the Absolute Maximum Ratings Table. However, input errors will be generated If the input goes above VA and below AGND.

<sup>(2)</sup> Test limits are specified to AOQL (Average Outgoing Quality Level).

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

## **AC Timing Specifications (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L = 10 \text{ pF}$ , and  $f_{INCLK} = 27 \text{ MHz}$  unless otherwise specified. All other limits  $T_A = 25^{\circ}C.^{(1)}$

|                    | PARAMETER                                         | TEST CONDITIONS                                                                                 | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT               |

|--------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

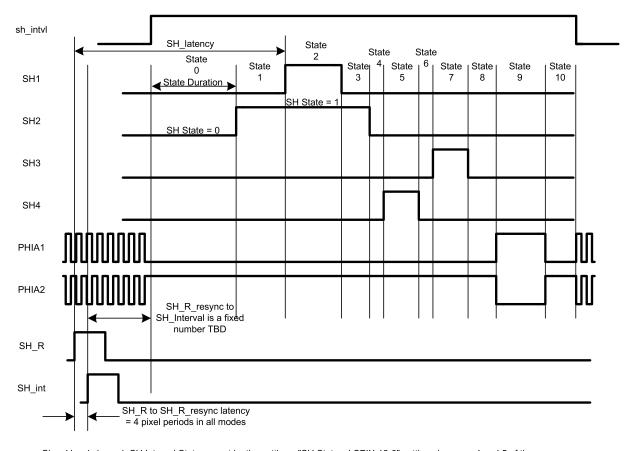

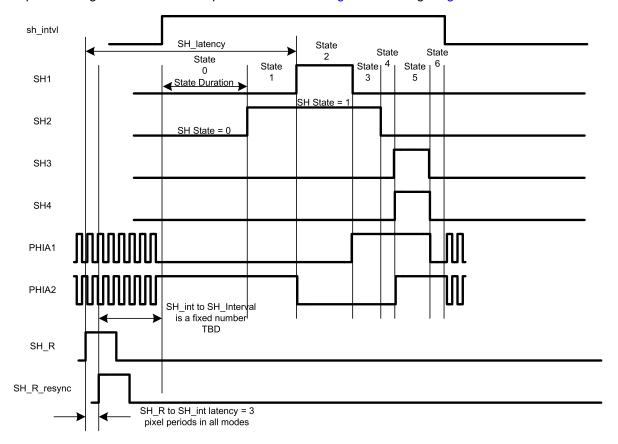

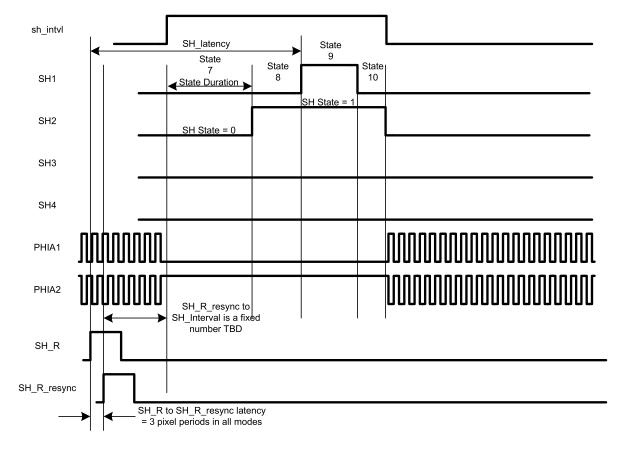

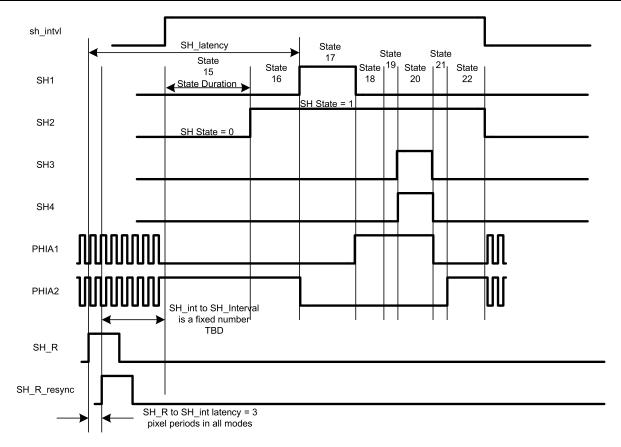

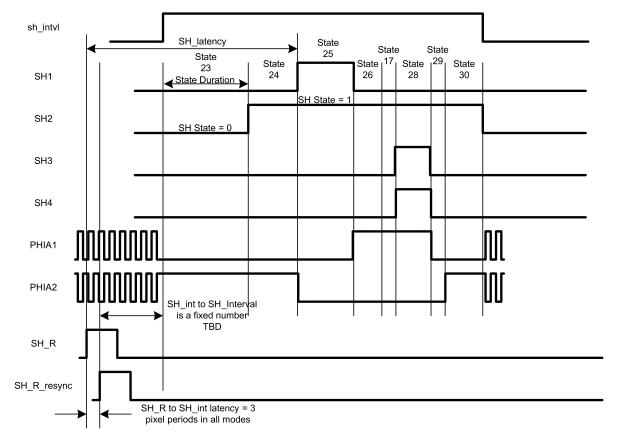

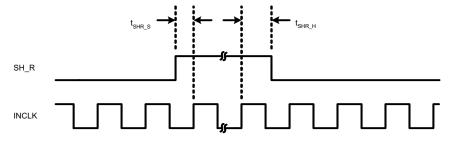

| SH_R TI            | IMING SPECIFICATIONS (Figure 44)                  |                                                                                                 |                    |                    | '                  |                    |

| t <sub>SHR_S</sub> | SH_R Setup Time                                   |                                                                                                 |                    | 2                  |                    | ns                 |

| t <sub>SHR_H</sub> | SH_R Hold Time                                    |                                                                                                 |                    | 2                  |                    | ns                 |

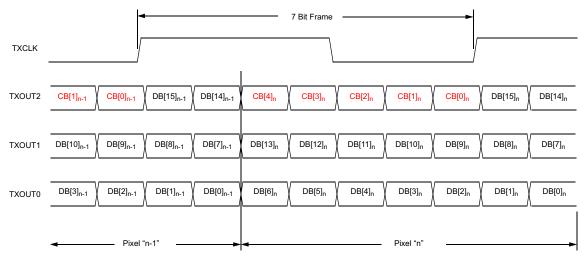

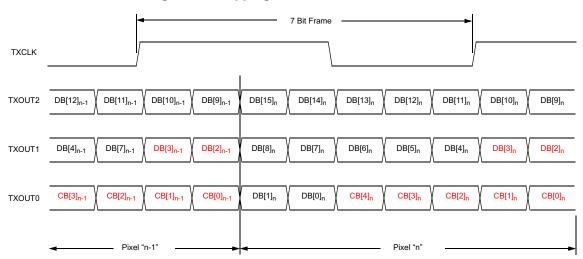

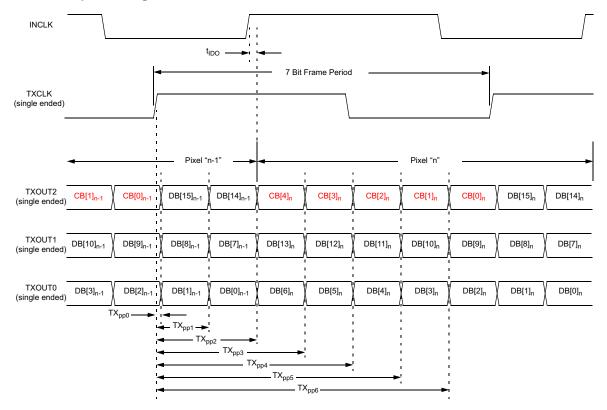

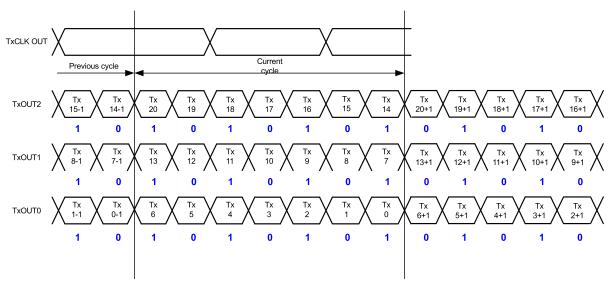

| LVDS O             | UTPUT TIMING SPECIFICATIONS (Figure               | 53)                                                                                             |                    |                    |                    |                    |

| $TX_{pp0}$         | TXCLK to Pulse Position 0                         |                                                                                                 | -0.26              | 0                  | 0.26               | ns                 |

| TX <sub>pp1</sub>  | TXCLK to Pulse Position 1                         |                                                                                                 | 1.50               | 1.76               | 2.02               | ns                 |

| TX <sub>pp2</sub>  | TXCLK to Pulse Position 2                         |                                                                                                 | 3.26               | 3.53               | 3.79               | ns                 |

| $TX_{pp3}$         | TXCLK to Pulse Position 3                         |                                                                                                 | 5.03               | 5.29               | 5.55               | ns                 |

| TX <sub>pp4</sub>  | TXCLK to Pulse Position 4                         |                                                                                                 | 6.80               | 7.06               | 7.32               | ns                 |

| TX <sub>pp5</sub>  | TXCLK to Pulse Position 5                         |                                                                                                 | 8.56               | 8.82               | 9.08               | ns                 |

| TX <sub>pp6</sub>  | TXCLK to Pulse Position 6                         |                                                                                                 | 10.32              | 10.58              | 10.84              | ns                 |

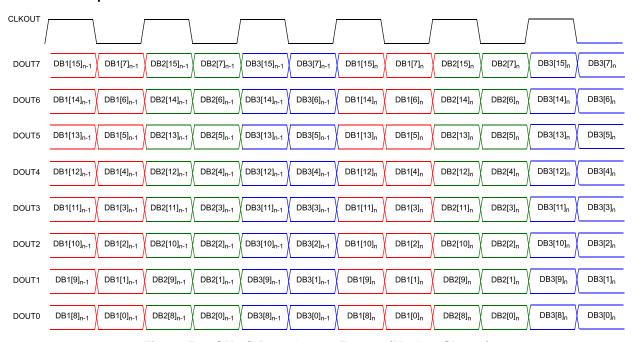

| CMOS C             | DUTPUT TIMING SPECIFICATIONS                      |                                                                                                 | •                  |                    | ·                  |                    |

| t <sub>CRDO</sub>  | CLKOUT Rising Edge to CMOS Output Data Transition | f <sub>INCLK</sub> = 40 MHz, INCLK = ADCCLK (ADC Rate Clock)                                    | 2                  | 4.5                | 9                  | ns                 |

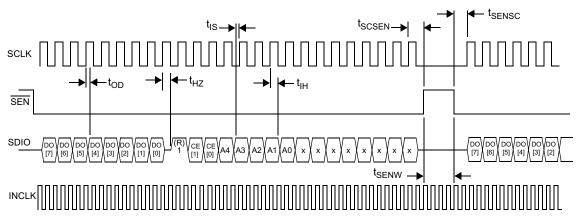

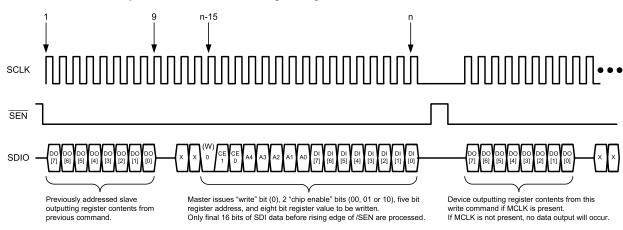

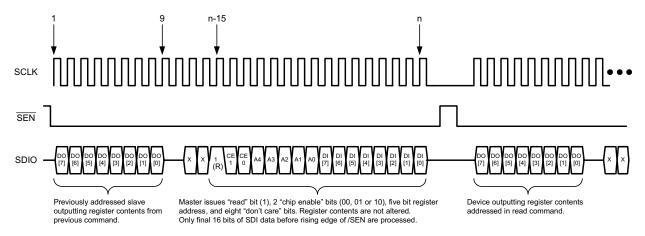

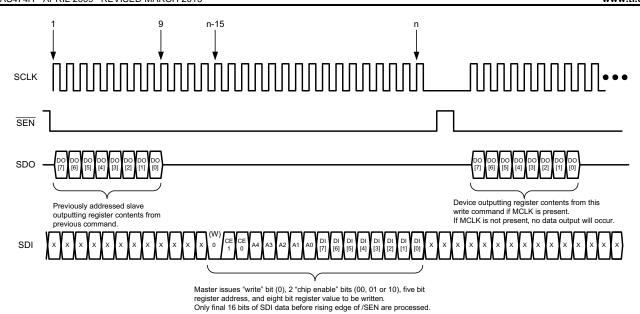

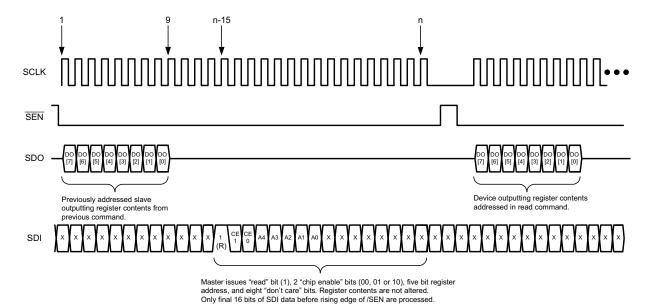

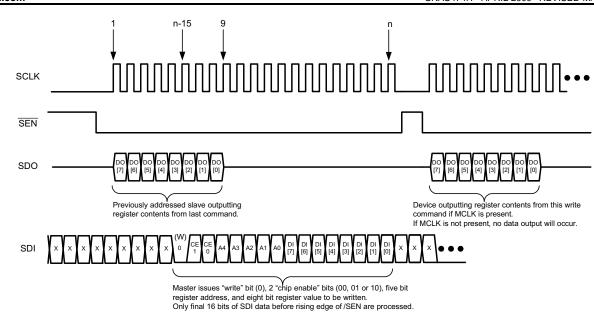

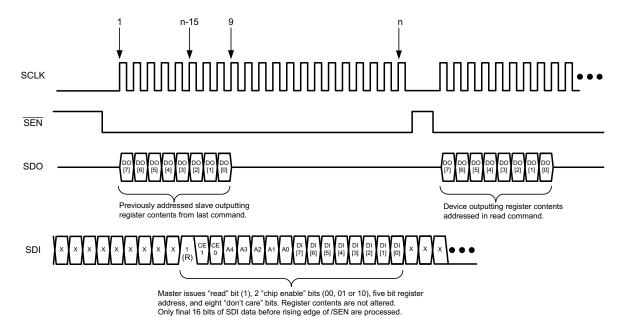

| SERIAL             | INTERFACE TIMING SPECIFICATIONS                   |                                                                                                 |                    |                    |                    |                    |

| 4                  | Input Clock Frequency                             | f <sub>SCLK</sub> <= f <sub>INCLK</sub> ,<br>INCLK = PIXCLK<br>(Pixel Rate Clock)<br>Mode 3/2/1 |                    |                    | 27/30/30           | MHz                |

| f <sub>SCLK</sub>  | input Glock i requesity                           | f <sub>SCLK</sub> <= f <sub>INCLK</sub> ,<br>INCLK = ADCCLK<br>(ADC Rate Clock)<br>Mode 3/2/1   |                    |                    | 81/60/30           | MHz                |

|                    | SCLK Duty Cycle                                   |                                                                                                 |                    | 50/50              |                    | ns                 |

| $t_{\text{IH}}$    | Input Hold Time                                   |                                                                                                 | 1.5                |                    |                    | ns                 |

| $t_{IS}$           | Input Setup Time                                  |                                                                                                 | 2.5                |                    |                    | ns                 |

| t <sub>SENSC</sub> | SCLK Start Time after SEN Low                     |                                                                                                 | 1.5                |                    |                    | ns                 |

| t <sub>SCSEN</sub> | SEN High after last SCLK Rising Edge              |                                                                                                 | 2.5                |                    |                    | ns                 |

| <b>t</b>           | SEN Pulse Width                                   | INCLK present (4)(5)                                                                            | 6                  |                    |                    | T <sub>INCLK</sub> |

| t <sub>SENW</sub>  | SEN FUISE WIUIT                                   | INCLK stopped <sup>(4)(5)</sup>                                                                 | 50                 |                    |                    | ns                 |

| t <sub>OD</sub>    | Output Delay Time                                 |                                                                                                 |                    | 11                 | 14                 | ns                 |

| $t_{HZ}$           | Data Output to High Z                             |                                                                                                 |                    |                    | 0.5                | $T_{SCLK}$         |

If the input INCLK is divided down to a lower internal clock rate via the PLL, the parameter  $t_{SENW}$  will be increased by the same factor. When the Spread Spectrum Clock Generation feature is enabled,  $t_{SENW}$  should be increased by 1.

Product Folder Links: LM98725

Submit Documentation Feedback

## 6.6 Serial Interface Timing Details

Figure 1. Serial Interface Specification Diagram

Copyright © 2009–2015, Texas Instruments Incorporated

Submit Documentation Feedback

## 7 Detailed Description

#### 7.1 Overview

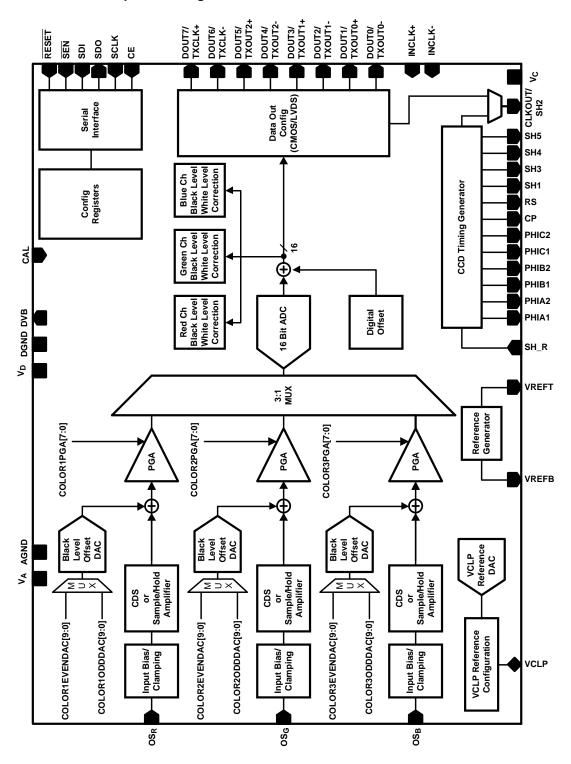

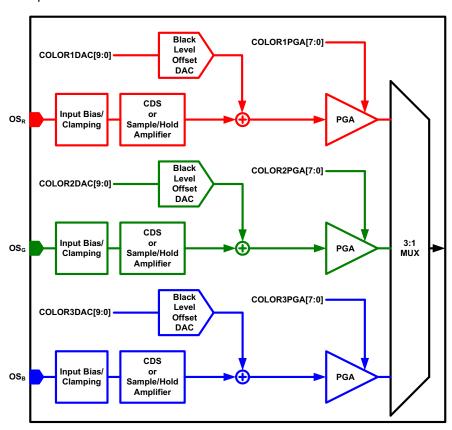

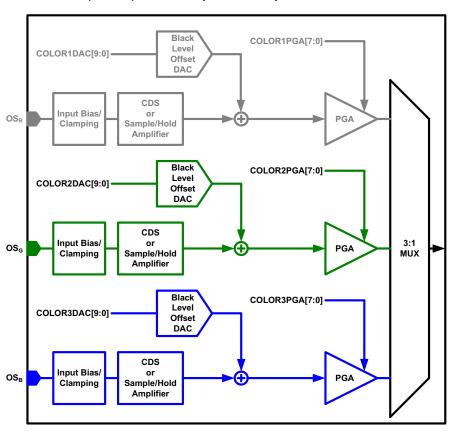

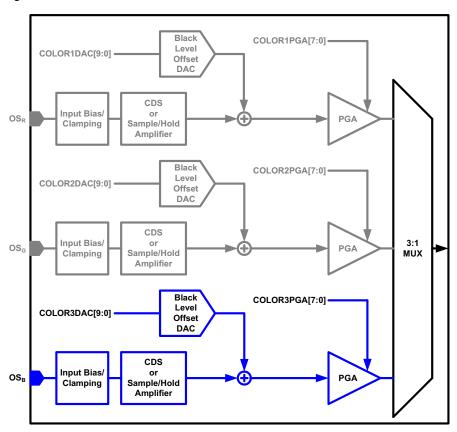

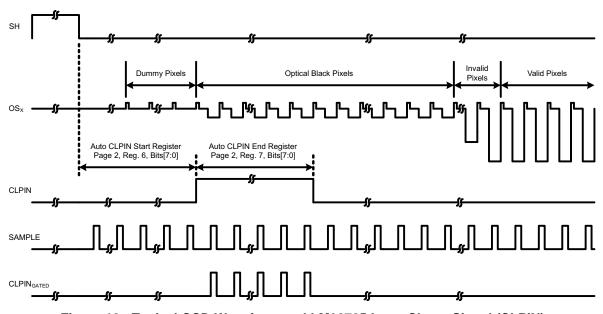

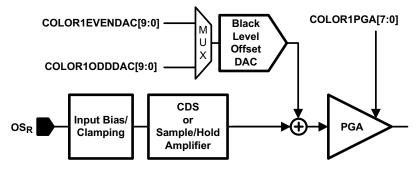

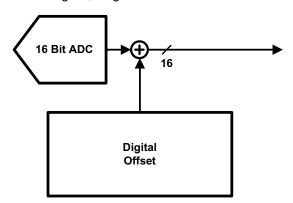

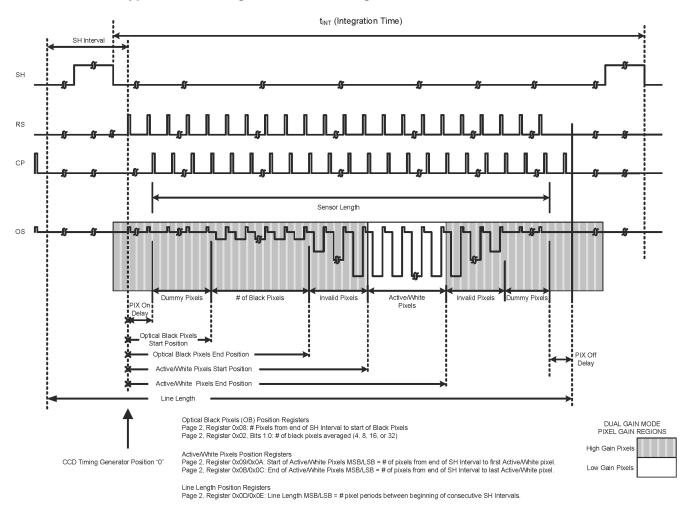

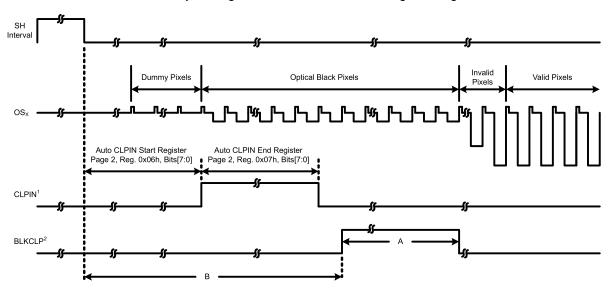

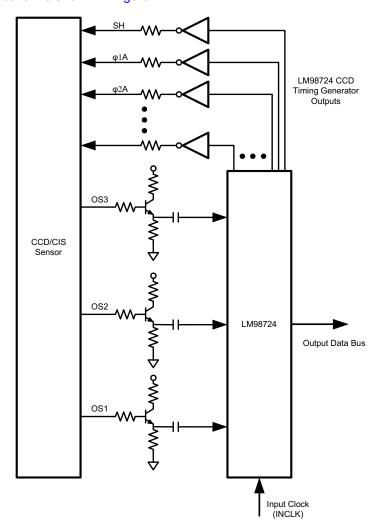

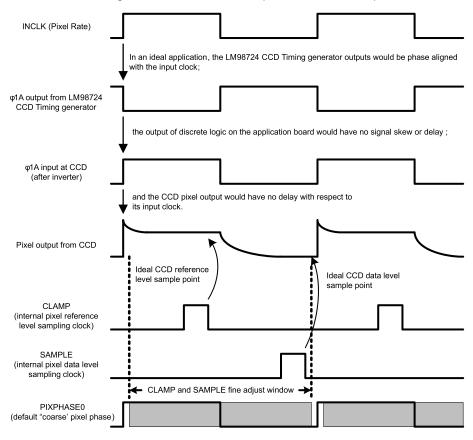

The LM98725 is a 16-bit, three-input, complete Analog Front End (AFE) for digital color copier and Multi-Function Peripheral (MFP) applications. The system block diagram of the LM98725, shown in *LM98725 Overall Chip Block Diagram* highlights the main features of the device. Each input has its own Input Bias and Clamping Network which are routed through a selectable Sample/Hold (S/H) or Correlated Double Sampler (CDS) amplifier. A ±9-Bit Offset DAC applies independent offset correction for each channel. A -3 to 17.9dB Programmable Gain Amplifier (PGA) applies independent gain correction for each channel. The LM98725 also provides independent Digital Black Level Correction Feedback Loops for each channel. The Black Level Correction Loop can be configured to run in Manual Mode (where the user inputs their own values of DAC offset) or in Automatic Mode where the LM98725 calculates each channel's Offset DAC value during optical black pixels and then adjusts the Offset register accordingly. The signals are routed to a single high performance 16-bit, 81MHz analog-to-digital converter.

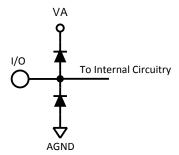

The analog inputs are protected as shown in Figure 2. Input voltage magnitude up to 500 mV beyond the supply rails will not damage this device. However, input errors will be generated if the input goes above VA and below AGND.

Figure 2. Analog Input Protection

## 7.2 Functional Block Diagrams

## 7.2.1 LM98725 Overall Chip Block Diagram

Figure 3. Chip Block Diagram

### **Functional Block Diagrams (continued)**

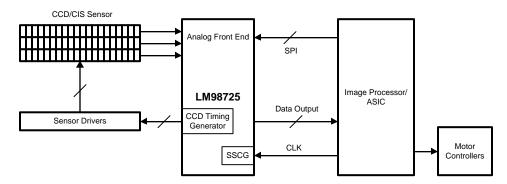

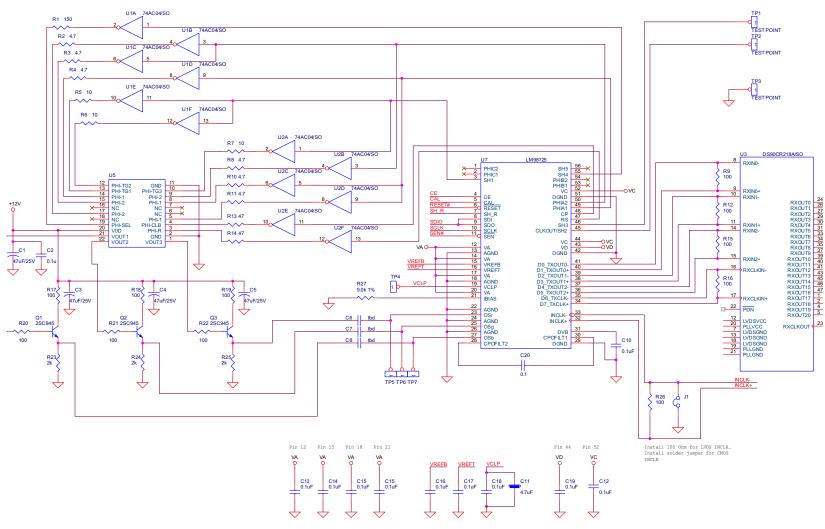

Figure 4. System Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Modes of Operation Introduction

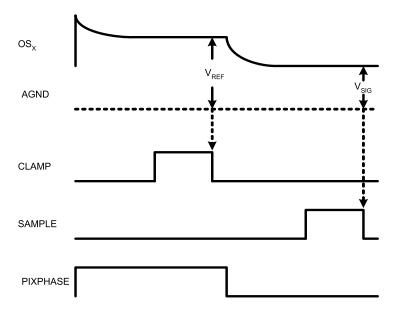

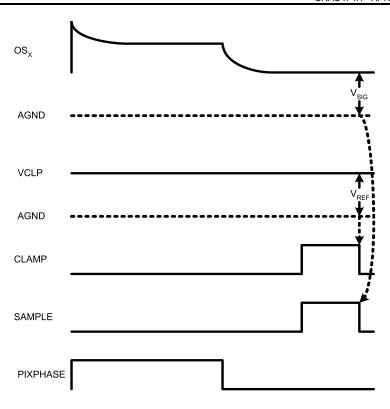

The LM98725 can be configured to operate in several different operating modes. The following sections are a brief introduction to these modes of operation. A more rigorous explanation of the operating modes is contained in the *Device Functional Modes* section, including input sampling diagrams for each mode as well as a description of the operating conditions.

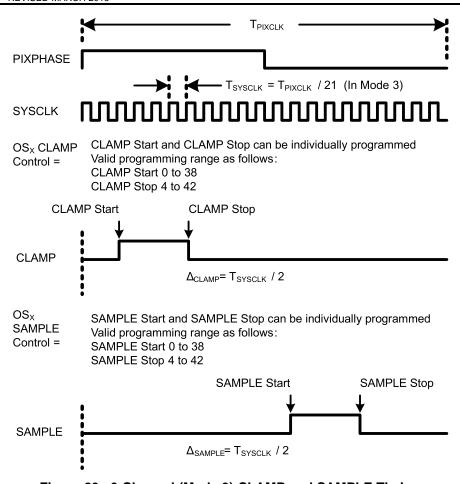

#### 7.3.2 Mode 3 - Three Channel Input/Synchronous Pixel Sampling

$OS_B$ ,  $OS_G$ , and  $OS_R$  inputs are sampled synchronously at a pixel rate. The sampled signals are processed with each channel's offset and gain adjusted independently via the control registers. The order in which pixels are processed from the input to the ADC is fully programmable and is synchronized by the SH pulse. In this mode, the maximum channel speed is 27MSPS per channel with the ADC running at 81MSPS yielding a three color throughput of 81MSPS.

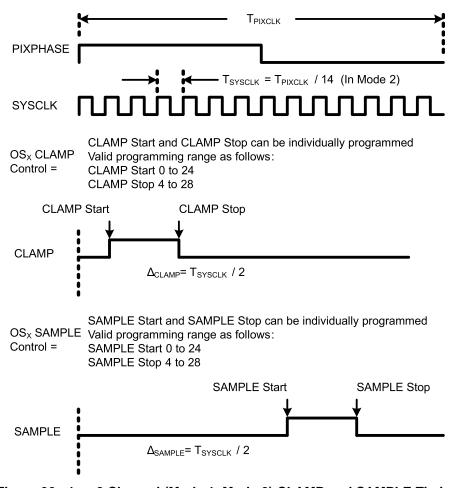

#### 7.3.3 Mode 2 - Two Channel Input/Synchronous Pixel Sampling

Mode 2 is useful for CCD sensors with a Black and White mode with Even and Odd outputs. In its default configuration, Mode 2 samples the Even output via the OSB channel input, and the Odd output via the OSG channel input. Sampling of the Even and Odd pixels is performed synchronously at a maximum sample rate of 30MSPS per input with the ADC running at 60MSPS.

#### 7.3.4 Mode 1 - One Channel Input

In Mode 1, all pixels are processed through a single input  $(OS_R, OS_G, or OS_B)$  chosen through the control register setup. This mode is useful in applications where only one input channel is used. The selected input is programmable through the control register.

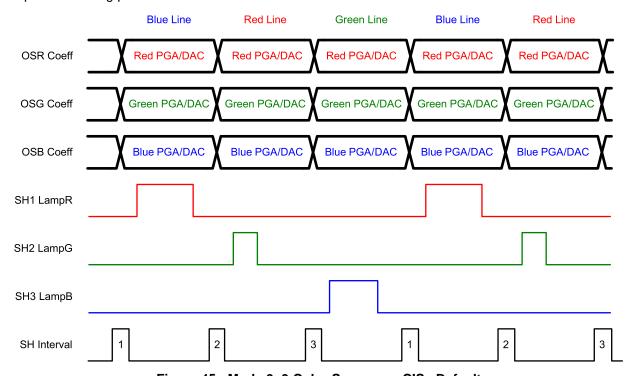

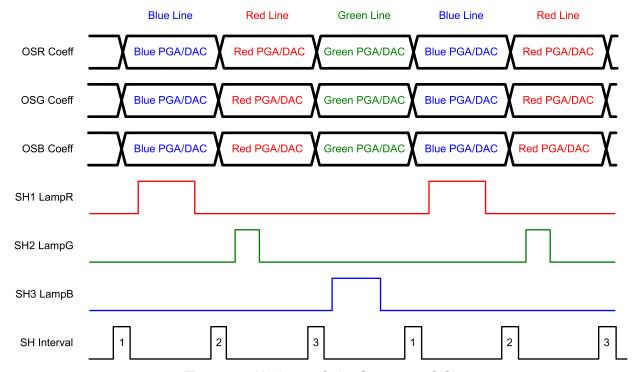

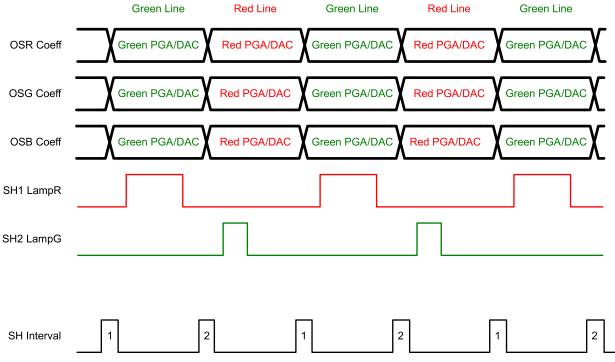

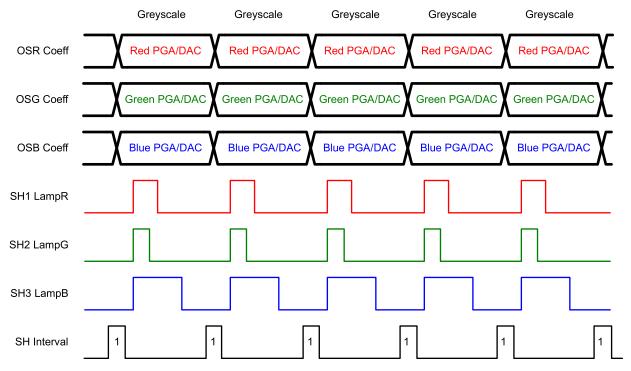

#### 7.3.5 CIS Lamp and Coefficient Modes

In additional to Modes 3, 2, and 1 above, two different CIS sensor modes (CISa and CISb) can be enabled. These allow color sequential lamp control, as well as synchronized color sequential gain/offset coefficient usage for multi-output color sequential sensors.

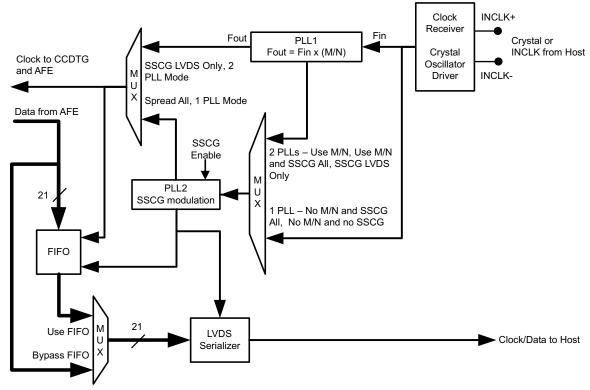

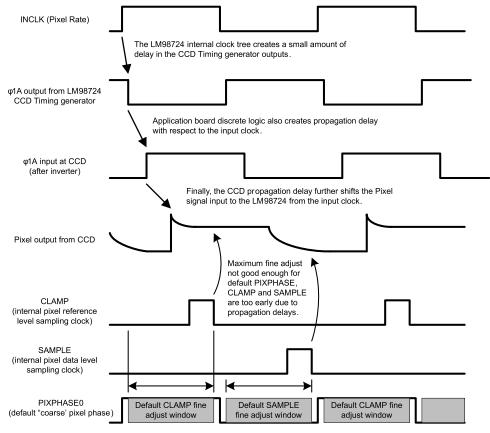

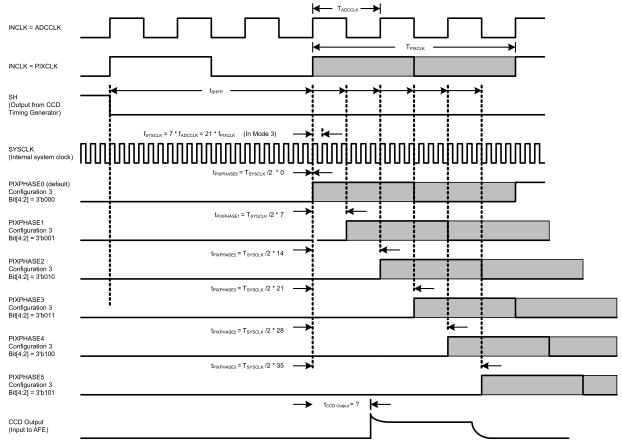

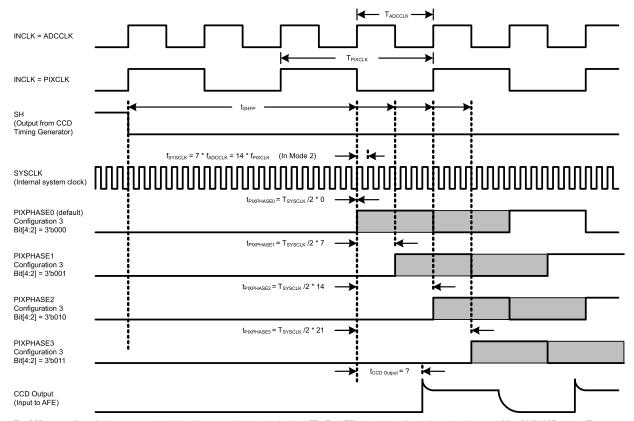

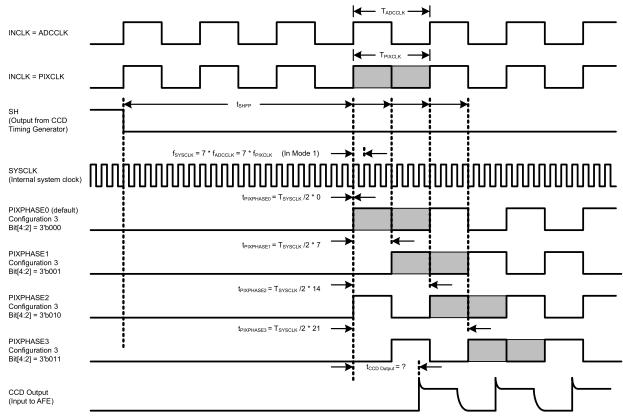

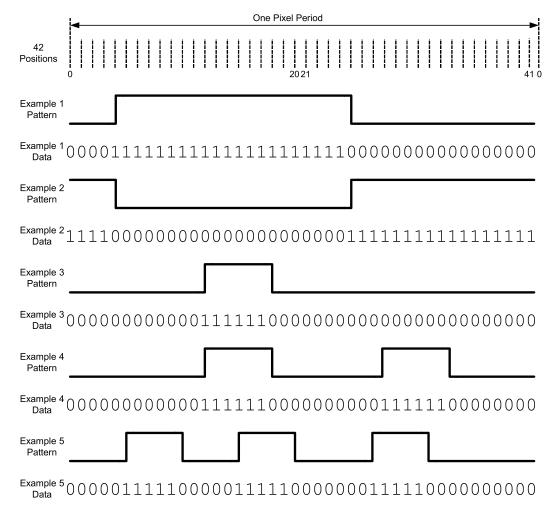

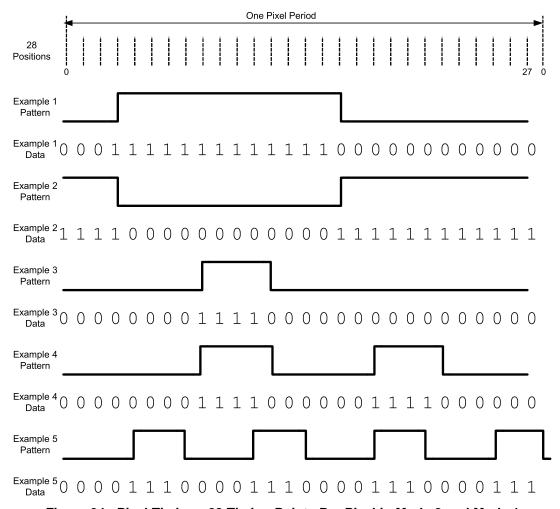

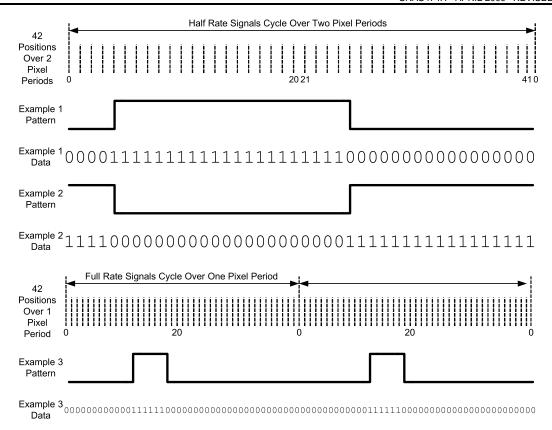

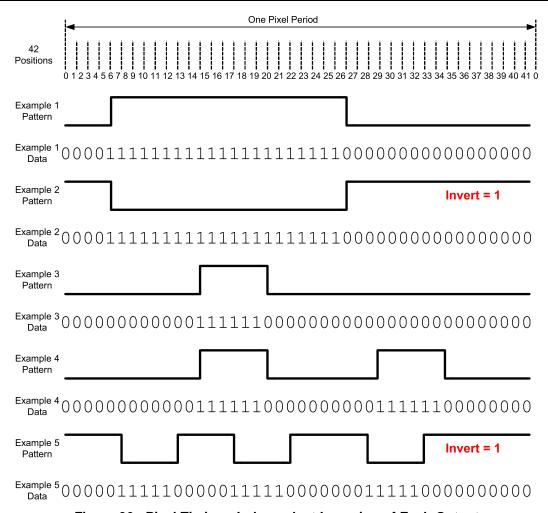

#### 7.3.6 Clock Sources