# LMH6734 Single Supply, Ultra High-Speed, Triple Selectable Gain Buffer

Check for Samples: LMH6734

## **FEATURES**

- (Typical Values Unless Otherwise Specified.)

- Supply Range 3V to 12V Single Supply

- Supply Range ±1.5V to ±6V Split Supply

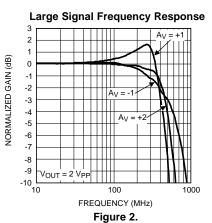

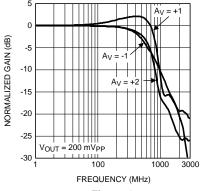

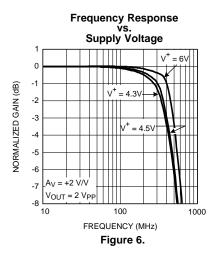

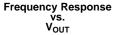

- 925 MHz -3 dB Small Signal Bandwidth (A<sub>V</sub> =  $+1, V_{s} = \pm 5V$

- 650 MHz -3 dB Small Signal Bandwidth (A<sub>V</sub> =  $+2, V_{S} = 5V$

- Low Supply Current (5.5 mA per op amp,  $V_{S}$  = 5V)

- 2.1 nV/VHz Input Noise Voltage

- 3750 V/ $\mu$ s Slew Rate (V<sub>S</sub> = ±5V)

- 70 mA Linear Output Current ( $A_V = +2$ ,  $V_S =$ ±5V)

- Input Range and Output Swing to 1V from each Supply Rail

## **APPLICATIONS**

- **HDTV Component Video Driver** •

- **CAT5** Component Video Driver

- **High Resolution Projectors** ٠

- Wide Dynamic Range IF Amp

- **DDS Post-amps**

- Wideband Inverting Summer

- Line Driver

## DESCRIPTION

The LMH6734 is a high speed monolithic selectable gain buffer designed specifically for ultra high resolution video systems as well as wide dynamic range systems requiring exceptional signal fidelity. Benefiting from TI's current feedback architecture, the LMH6734 offers gains of -1, +1 and +2. At a gain of +2 the LMH6734 supports ultra high resolution video systems with a 560 MHz 2 V<sub>PP</sub>3 dB bandwidth. With this large signal bandwidth and 2.1 nV/√Hz of input referred noise, the LMH6734 is ideal for driving component video over CAT5 cable up to 200 ft without frequency and gain equalization. The LMH6734 is offered in a space saving 16-Pin SSOP package.

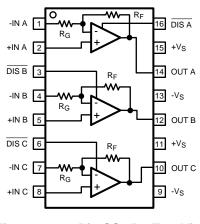

## **Connection Diagram**

Figure 1. 16-Pin SSOP - Top View  $R_F = R_G = 327\Omega$

Ā

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# LMH6734

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings<sup>(1)(2)</sup>

| ESD Tolerance <sup>(3)</sup>                      | Human Body Model                 | 2000V              |

|---------------------------------------------------|----------------------------------|--------------------|

|                                                   | Machine Model                    | 200V               |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |                                  | 13.2V              |

| I <sub>OUT</sub>                                  |                                  | See <sup>(4)</sup> |

| Common Mode Input Voltage                         |                                  | ±V <sub>CC</sub>   |

| Maximum Junction Temperature                      |                                  | +150°C             |

| Storage Temperature Range                         |                                  | −65°C to +150°C    |

| Soldering Information                             | Infrared or Convection (20 sec.) | 235°C              |

|                                                   | Wave Soldering (10 sec.)         | 260°C              |

| Storage Temperature Range                         |                                  | -65°C to +150°C    |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDECField-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(4) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations. See the POWER DISSIPATION section of the Application Information for more details.

## **Operating Ratings**<sup>(1)</sup>

| Temperature Range <sup>(2)</sup>                  |                    | −40°C to +85°C     |  |

|---------------------------------------------------|--------------------|--------------------|--|

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 3V to 1            |                    |  |

| Thermal Resistance                                |                    |                    |  |

| Package                                           | (θ <sub>JC</sub> ) | (θ <sub>JA</sub> ) |  |

| 16-Pin SSOP                                       | 36°C/W             | 120°C/W            |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

## 5V Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $A_V = +2$ ,  $R_L = 100\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol                       | Parameter            | Conditions                                          | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|------------------------------|----------------------|-----------------------------------------------------|--------------------|--------------------|--------------------|-------|

| Frequency Domain Performance |                      |                                                     |                    |                    |                    |       |

| UGBW                         | −3 dB Bandwidth      | Unity Gain, V <sub>OUT</sub> = 200 mV <sub>PP</sub> |                    | 870                |                    | MHz   |

| SSBW                         | -3 dB Bandwidth      | $V_{OUT}$ = 200 m $V_{PP}$ , $R_L$ = 100 $\Omega$   |                    | 650                |                    |       |

| SSBW                         |                      | $V_{OUT}$ = 200 m $V_{PP}$ , $R_L$ = 150 $\Omega$   |                    | 685                |                    | MHz   |

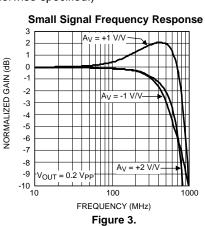

| LSBW                         |                      | V <sub>OUT</sub> = 2 V <sub>PP</sub>                |                    | 480                |                    |       |

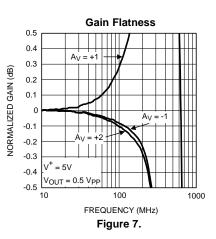

| 0.1 dB BW                    | 0.1 dB Gain Flatness | $V_{OUT}$ = 200 m $V_{PP}$                          |                    | 130                |                    | MHz   |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . See Application Information for information on temperature de-rating of this device. Min/Max ratings are based on product characterization and simulation. Individual parameters are tested as noted.

(2) Limits are 100% production tested at 25C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

SNOSAY0C -JUNE 2007-REVISED APRIL 2013

www.ti.com

# 5V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $A_V = +2$ ,  $R_L = 100\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                              | Conditions                                                                  | Min <sup>(2)</sup>            | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units  |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------|-------------------------------|--------------------|--------------------|--------|

| Time Dom          | ain Response                           | · ·                                                                         |                               |                    |                    |        |

| TRS               | Rise and Fall Time<br>(10% to 90%)     | 2V Step                                                                     |                               | 0.7                |                    | ns     |

| SR                | Slew Rate                              | 2V Step                                                                     |                               | 1900               |                    | V/µs   |

| ts                | Settling Time to 0.1%                  | 2V Step                                                                     |                               | 10                 |                    | ns     |

| t <sub>e</sub>    | Enable Time                            | From Disable = Rising Edge                                                  |                               | 10                 |                    | ns     |

| t <sub>d</sub>    | Disable Time                           | From Disable = Falling Edge                                                 |                               | 15                 |                    | ns     |

| Distortion        |                                        |                                                                             | 1                             |                    |                    | I      |

| HD2L              | 2 <sup>nd</sup> Harmonic Distortion    | 2 V <sub>PP</sub> , 10 MHz                                                  |                               | -63                |                    | dBc    |

| HD3L              | 3 <sup>rd</sup> Harmonic Distortion    | 2 V <sub>PP</sub> , 10 MHz                                                  |                               | -73                |                    | dBc    |

| Equivalen         | t Input Noise                          | -                                                                           | 1                             |                    |                    |        |

| V <sub>N</sub>    | Non-Inverting Voltage                  | >10 MHz                                                                     |                               | 2.1                |                    | nV/√Hz |

| I <sub>CN</sub>   | Inverting Current                      | >10 MHz                                                                     |                               | 18.6               |                    | pA/√Hz |

| N <sub>CN</sub>   | Non-Inverting Current                  | >10 MHz                                                                     |                               | 26.9               |                    | pA/√Hz |

| Video Per         | formance                               |                                                                             |                               |                    |                    |        |

| DG                | Differential Gain                      | 4.43 MHz, R <sub>L</sub> = 150Ω                                             |                               | 0.03               |                    | %      |

| DP                | Differential Phase                     | 4.43 MHz, R <sub>L</sub> = 150Ω                                             |                               | 0.025              |                    | deg    |

| Static, DC        | Performance                            |                                                                             |                               |                    |                    |        |

| V <sub>IO</sub>   | Input Offset Voltage                   |                                                                             |                               | 0.4                | 2.0<br><b>2.5</b>  | mV     |

| BN                | Input Bias Current                     | Non-Inverting                                                               | 2                             | 16.7               | 28<br><b>32</b>    | μA     |

| PSRR              | Power Supply Rejection Ratio           | +PSRR                                                                       | 59<br><b>59</b>               | 61                 |                    | ٦Ŀ     |

|                   |                                        | -PSRR                                                                       | 58<br><b>56</b>               | 61                 |                    | dB     |

| CMRR              | Common Mode Rejection Ratio            |                                                                             | 52<br><b>52</b>               | 54.5               |                    | dB     |

| XTLK              | Crosstalk                              | Input Referred, f = 10 MHz, Drive<br>Channels A, C and Measure<br>Channel B |                               | -80                |                    | dB     |

| l <sub>cc</sub>   | Supply Current                         | All three amps Enabled, No Load                                             | 15<br><b>15</b>               | 16.7               | 18<br><b>19</b>    | mA     |

|                   | Supply Current Disabled V <sup>+</sup> | R <sub>L</sub> = ∞                                                          |                               | 1.54               | 1.8                | mA     |

|                   | Supply Current Disabled V              | R <sub>L</sub> = ∞                                                          |                               | 0.75               | 1.8                | mA     |

|                   | Gain Error                             | R <sub>L</sub> = ∞                                                          |                               | 0.2                | 1.25               | %      |

|                   | Gain                                   | A <sub>V</sub> = +2                                                         | 1.975                         | 1.996              | 2.025              |        |

|                   |                                        | A <sub>V</sub> = +1                                                         |                               | 0.998              |                    | V/V    |

|                   |                                        | A <sub>V</sub> = -1                                                         | -0.9875                       | -0.998             | -1.0125            |        |

| Miscellane        | eous Performance                       | •                                                                           |                               | •                  |                    |        |

| R <sub>IN</sub> + | Non-Inverting Input Resistance         |                                                                             |                               | 200                |                    | kΩ     |

| C <sub>IN</sub> + | Non-Inverting Input Capacitance        |                                                                             |                               | 1                  |                    | pF     |

| R <sub>O</sub>    | Output Impedance                       | DC                                                                          |                               | 0.05               |                    | Ω      |

| Vo                | Output Voltage Range                   | R <sub>L</sub> = 100Ω                                                       | 1.25-3.75<br><b>1.3-3.7</b>   | 1.12-3.88          |                    | .,     |

|                   |                                        | R <sub>L</sub> = ∞                                                          | 1.11-3.89<br><b>1.15-3.85</b> | 1.03-3.97          |                    | V      |

| CMIR              | Input Range                            | Driving input +INA, CMRR > 40 dB                                            | 1.1-3.9<br><b>1.2-3.8</b>     | 1.0-4.0            |                    | V      |

## 5V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $A_V = +2$ ,  $R_L = 100\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol            | Parameter                     | Conditions                                                      | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|-------------------|-------------------------------|-----------------------------------------------------------------|--------------------|--------------------|--------------------|-------|

| lo                | Linear Output Current         | $V_{IN} = 0V, V_{OUT} < \pm 42 \text{ mV}^{(4)}$                | ±50                | ±60                |                    | mA    |

| I <sub>SC</sub>   | Short Circuit Current         | V <sub>IN</sub> = 2V Output Shorted to<br>Ground <sup>(5)</sup> |                    | 170                |                    | mA    |

| I <sub>IH</sub>   | Disable Pin Bias Current High | Disable Pin = V <sup>+</sup>                                    |                    | -72                |                    | μA    |

| IIL               | Disable Pin Bias Current Low  | Disable Pin = 0V                                                |                    | -360               |                    | μA    |

| V <sub>DMAX</sub> | Voltage for Disable           | Disable Pin ≤ V <sub>DMAX</sub>                                 |                    | 3.2                |                    | V     |

| V <sub>DMIM</sub> | Voltage for Enable            | Disable Pin ≥ V <sub>DMIN</sub>                                 |                    | 3.6                |                    | V     |

The maximum output current (IOUT) is determined by device power dissipation limitations. See the POWER DISSIPATION section of the (4) Application Information for more details. Short circuit current should be limited in duration to no more than 10 seconds. See the POWER DISSIPATION section of the Application

(5)Information for more details.

## ±5V Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $A_V = +2$ ,  $R_L = 100\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol          | Parameter                           | Conditions                                          | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units  |

|-----------------|-------------------------------------|-----------------------------------------------------|--------------------|--------------------|--------------------|--------|

| Frequency       | Domain Performance                  | · ·                                                 |                    |                    |                    |        |

| UGBW            | -3 dB Bandwidth                     | Unity Gain, V <sub>OUT</sub> = 200 mV <sub>PP</sub> |                    | 925                |                    | MHz    |

| SSBW            | -3 dB Bandwidth                     | $V_{OUT} = 200 \text{ mV}_{PP}, R_L = 100\Omega$    |                    | 730                |                    |        |

| SSBW            |                                     | $V_{OUT}$ = 200 m $V_{PP}$ , $R_L$ = 150 $\Omega$   |                    | 760                |                    | MHz    |

| LSBW            |                                     | V <sub>OUT</sub> = 2 V <sub>PP</sub>                |                    | 560                |                    |        |

| 0.1 dB BW       | 0.1 dB Gain Flatness                | V <sub>OUT</sub> = 200 mV <sub>PP</sub>             |                    | 270                |                    | MHz    |

| Time Doma       | ain Response                        |                                                     |                    |                    |                    |        |

| TRS             | Rise and Fall Time                  | 2V Step                                             |                    | 0.7                |                    |        |

| TRL             | (10% to 90%)                        | 5V Step                                             |                    | 0.8                | n                  |        |

| SR              | R Slew Rate 2V Step                 |                                                     | 3750               |                    | V/µs               |        |

| t <sub>s</sub>  | Settling Time to 0.1% 2V Step       |                                                     | 10                 |                    | ns                 |        |

| t <sub>e</sub>  | Enable Time                         | From Disable = Rising Edge                          |                    | 10                 |                    | ns     |

| t <sub>d</sub>  | Disable Time                        | From Disable = Falling Edge                         |                    | 15                 |                    | ns     |

| Distortion      |                                     |                                                     |                    |                    |                    |        |

| HD2L            | 2 <sup>nd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 10 MHz                          |                    | -72                |                    | dBc    |

| HD3L            | 3 <sup>rd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 10 MHz                          |                    | -63                |                    | dBc    |

| Equivalent      | Input Noise                         |                                                     |                    |                    |                    |        |

| V <sub>N</sub>  | Non-Inverting Voltage               | >10 MHz                                             |                    | 2.1                |                    | nV/√Hz |

| I <sub>CN</sub> | Inverting Current >10 MHz 18.6      |                                                     | 18.6               |                    | pA/√Hz             |        |

| N <sub>CN</sub> | Non-Inverting Current               | >10 MHz 26.9                                        |                    | 26.9               |                    | pA/√Hz |

| Video Perf      | ormance                             |                                                     |                    |                    |                    |        |

| DG              | Differential Gain                   | 4.43 MHz, $R_L = 150\Omega$                         |                    | 0.03               |                    | %      |

| DP              | Differential Phase                  | 4.43 MHz, R <sub>L</sub> = 150Ω                     |                    | 0.03               |                    | deg    |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub>> T<sub>A</sub>. See Application Information for information on temperature de-rating of this device. Min/Max ratings are based on product characterization and simulation. Individual parameters are tested as noted.

Limits are 100% production tested at 25C. Limits over the operating temperature range are specified through correlation using Statistical (2) Quality Control (SQC) methods.

Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary (3) over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

www.ti.com

# ±5V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $A_V = +2$ ,  $R_L = 100\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol            | Parameter                              | Conditions                                                                  | Min <sup>(2)</sup>   | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------|----------------------|--------------------|--------------------|-------|

| Static, DC        | Performance                            |                                                                             |                      |                    |                    |       |

| V <sub>IO</sub>   | Input Offset Voltage                   |                                                                             |                      | 0.6                | 2.4<br><b>3.4</b>  | mV    |

| I <sub>BN</sub>   | Input Bias Current                     | Non-Inverting                                                               | -14<br><b>-19</b>    | 3.5                | 19<br><b>24</b>    | μΑ    |

| PSRR              | Power Supply Rejection Ratio           | +PSRR                                                                       | 59<br><b>59</b>      | 61.5               |                    | ٩D    |

|                   |                                        | -PSRR                                                                       | 58<br><b>58</b>      | 61                 |                    | dB    |

| CMRR              | Common Mode Rejection Ratio            |                                                                             | 53<br><b>53</b>      | 55                 |                    | dB    |

| XTLK              | Crosstalk                              | Input Referred, f = 10 MHz, Drive<br>Channels A, C and Measure<br>Channel B |                      | -80                |                    | dB    |

| I <sub>CC</sub>   | Supply Current                         | All three amps Enabled, No Load                                             | 18<br><b>18</b>      | 19.5               | 20.8<br><b>22</b>  | mA    |

|                   | Supply Current Disabled V <sup>+</sup> | R <sub>L</sub> = ∞                                                          |                      | 1.54               | 1.8                | mA    |

|                   | Supply Current Disabled V <sup>−</sup> | R <sub>L</sub> = ∞                                                          |                      | 0.75               | 1.8                | mA    |

|                   | Gain Error                             | R <sub>L</sub> = ∞                                                          |                      | 0.2                | 1.25               | %     |

|                   | Gain                                   | A <sub>V</sub> = +2                                                         | 1.975                | 1.996              | 2.025              |       |

|                   |                                        | A <sub>V</sub> = +1                                                         |                      | 0.998              |                    | V/V   |

|                   |                                        | A <sub>V</sub> = -1                                                         | -0.9875              | -0.998             | -1.0125            |       |

| Miscellane        | ous Performance                        |                                                                             |                      |                    | - <u> </u>         |       |

| R <sub>IN</sub> + | Non-Inverting Input Resistance         |                                                                             |                      | 200                |                    | kΩ    |

| C <sub>IN</sub> + | Non-Inverting Input Capacitance        |                                                                             |                      | 1                  |                    | pF    |

| R <sub>O</sub>    | Output Impedance                       | DC                                                                          |                      | 0.05               |                    | Ω     |

| Vo                | Output Voltage Range                   | R <sub>L</sub> = 100Ω                                                       | ±3.55<br><b>±3.5</b> | ±3.7               |                    | V     |

|                   |                                        | R <sub>L</sub> = ∞                                                          | ±3.85                | ±4.0               |                    |       |

| CMIR              | Input Range                            | Driving input +INA, CMRR > 40 dB                                            | ±3.9<br><b>±3.8</b>  | ±4.0               |                    | V     |

| I <sub>O</sub>    | Linear Output Current                  | $V_{IN} = 0V, V_{OUT} < \pm 43 \text{ mV}^{(4)}$                            | 70                   | ±80                |                    | mA    |

| I <sub>SC</sub>   | Short Circuit Current                  | $V_{IN}$ = 2V Output Shorted to Ground <sup>(5)</sup>                       |                      | 237                |                    | mA    |

| I <sub>IH</sub>   | Disable Pin Bias Current High          | Disable Pin = V <sup>+</sup>                                                |                      | -72                |                    | μA    |

| IIL               | Disable Pin Bias Current Low           | Disable Pin = 0V                                                            |                      | -360               |                    | μA    |

| V <sub>DMAX</sub> | Voltage for Disable                    | Disable Pin ≤ V <sub>DMAX</sub>                                             |                      | 3.2                |                    | V     |

| V <sub>DMIM</sub> | Voltage for Enable                     | Disable Pin ≥ V <sub>DMIN</sub>                                             |                      | 3.6                |                    | V     |

The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations. See the POWER DISSIPATION section of the Application Information for more details. Short circuit current should be limited in duration to no more than 10 seconds. See the POWER DISSIPATION section of the Application (4)

(5) Information for more details.

TEXAS INSTRUMENTS

#### SNOSAY0C-JUNE 2007-REVISED APRIL 2013

www.ti.com

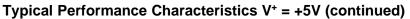

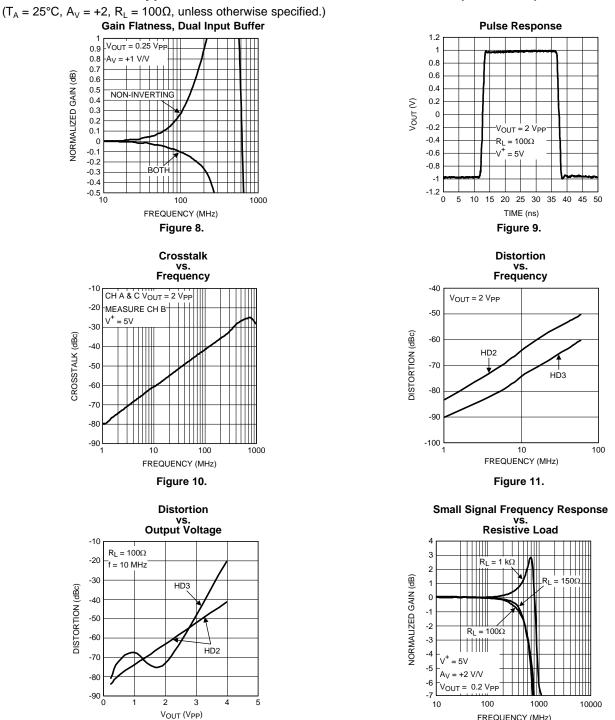

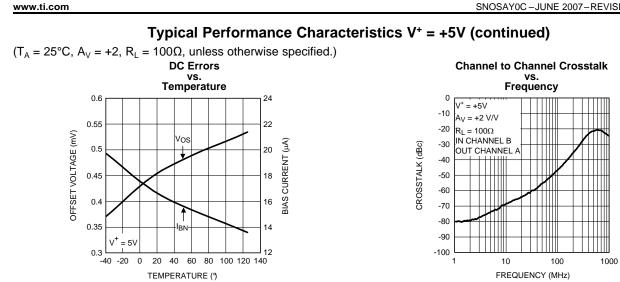

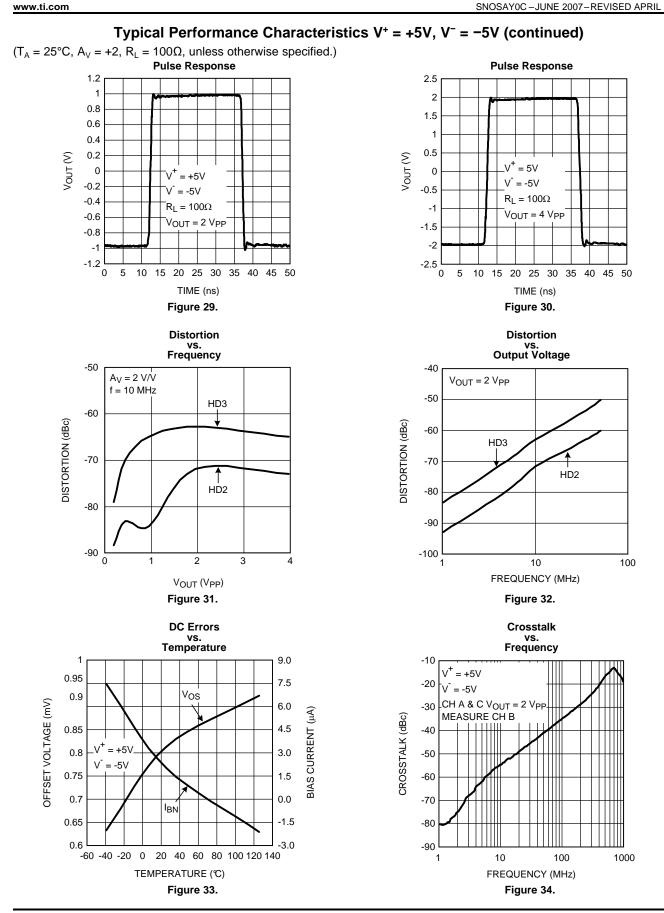

$(T_A = 25^{\circ}C, A_V = +2, R_L = 100\Omega$ , unless otherwise specified.)

#### OBSOLETE

www.ti.com

Figure 12.

FREQUENCY (MHz)

Figure 13.

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

8

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

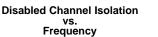

Figure 21.

TEXAS INSTRUMENTS

www.ti.com

SNOSAY0C - JUNE 2007 - REVISED APRIL 2013

#### Copyright © 2007-2013, Texas Instruments Incorporated

Submit Documentation Feedback 11

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

www.ti.com

## APPLICATION INFORMATION

### **GENERAL INFORMATION**

The LMH6734 is a high speed current feedback selectable gain buffer (SGB), optimized for very high speed applications. With its internal feedback and gain-setting resistors,  $R_F = R_G = 327\Omega$ , the LMH6734 offers excellent AC performance while simplifying board layout and minimizing the effects of layout related parasitic components. The LMH6734 has no internal ground reference so single or split supply configurations are both equally useful.

## SETTING THE CLOSED LOOP GAIN

The LMH6734 can be configured with gain settings of  $A_V = +2$ , +1, or -1. Table 1 shows the non-inverting and inverting pin connections to achieve the desired closed loop gain.

| GAIN A <sub>V</sub> |               | INPUT CONNECTIONS |  |  |

|---------------------|---------------|-------------------|--|--|

|                     | Non-Inverting | Inverting         |  |  |

| -1 V/V              | Ground        | Input Signal      |  |  |

| +1 V/V              | Input Signal  | NC (Open)         |  |  |

| +2 V/V              | Input Signal  | Ground            |  |  |

#### Table 1. Setting the Closed Loop Gain

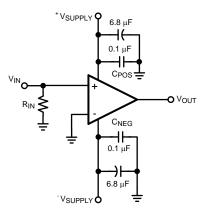

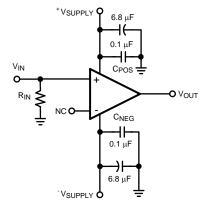

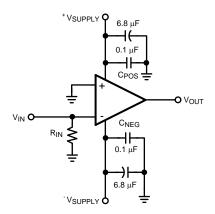

## SPLIT SUPPLY APPLICATION

The recommended split supply circuit applications are shown in Figure 35, Figure 36, and Figure 37. In all three configurations the input signal is DC coupled with a termination resister input  $R_{IN} = 50\Omega$ . In Figure 35 the inverting input is connected to ground completing the internal feedback loop to set the gain to +2 V/V. In Figure 36 the inverting input is open (no-connect), thus providing a buffer configuration of +1 V/V. Figure 37 shows a buffer configuration with a gain of -1 V/V. In this configuration an input resistor of 59 $\Omega$  was used to balance the internal  $R_G$  resistor of 327 $\Omega$  and to provide a 50 $\Omega$  termination.

Figure 35. Recommended Split Supply Non-Inverting Gain Circuit, Gain = +2 V/V

Figure 37. Recommended Split Supply Inverting Gain Circuit, Gain = -1 V/V

## SINGLE SUPPLY APPLICATION

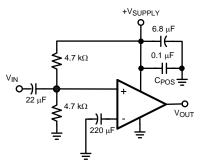

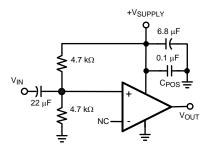

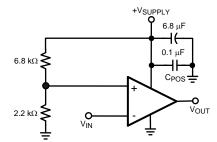

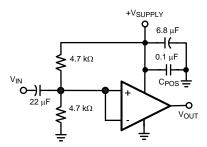

The LMH6734 can also be configured for single supply applications as shown in Figure 38, Figure 39, and Figure 40. In Figure 38, the 220  $\mu$ F capacitor was chosen to satisfy low frequency input signals and to provide an open for the internal feedback network path, thus setting the gain to +1 V/V. With an AC signal present, this 220  $\mu$ F capacitor is shunted to ground and completes the feedback resistor network to set the AC coupled gain of +2 V/V. The input is AC coupled with the 22  $\mu$ F capacitor and the two 4.7 k $\Omega$  resistors to set the input DC bias voltage. Figure 39 shows the single supply buffer configuration with the inverting input open (no-connect) creating an open to the internal feedback network giving a gain of +1 V/V. The input voltage is AC coupled with the 22  $\mu$ F capacitor along with two 4.7 k $\Omega$  resistors to set the input DC bias voltage. Figure 40 shows the single supply buffer configuration for a gain of -1 V/V. In this circuit, the input signal is DC coupled into the inverting input closing the internal feedback network and creating a gain of -1 V/V while an AC gain of +2 V/V is present at the non-inverting input. Thus, the 6.8 k $\Omega$  and the 2.2 k $\Omega$  resistors were chosen to set the input DC bias voltage to 1/4 the supply voltage such that at high frequencies the output voltage is gained up by +2 V/V.

TEXAS INSTRUMENTS

www.ti.com

SNOSAY0C-JUNE 2007-REVISED APRIL 2013

Figure 39. Recommended Single Supply Non-Inverting Gain Circuit, Gain = +1 V/V

The gain of the LMH6734 is accurate to  $\pm 1\%$  and stable over temperature. The internal gain setting resistors, R<sub>F</sub> and R<sub>G</sub>, match very well. However, over process and temperature their absolute value will change. Using external resistors in series with R<sub>G</sub> to change the gain will result in poor gain accuracy over temperature and from part to part.

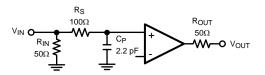

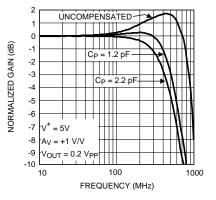

### UNITY GAIN COMPENSATION

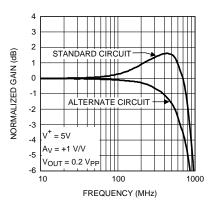

With a current feedback Selectable Gain Buffer like the LMH6734, the feedback resistor is a compromise between the value needed for stability at unity gain and the optimized value used at a gain of two. The result of this compromise is substantial peaking at unity gain. If this peaking is undesirable a simple RC filter at the input of the buffer will smooth the frequency response as shown in Figure 41. Figure 42 shows the results of a simple filter placed on the non-inverting input. See Figure 43 and Figure 44 for another method of reducing unity gain peaking.

Figure 41. Correction for Unity Gain Peaking

Figure 42. Frequency Response for Circuit in Figure 41

Figure 43. Alternate Unity Gain Compensation

Figure 44. Frequency Response for Circuit in Figure 43 (Standard Circuit Figure 39)

### **COMPONENT DRIVER**

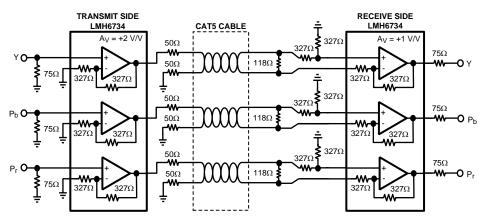

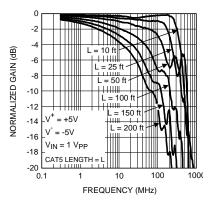

The LMH6734 is capable of transmitting and receiving component video over short to moderate unshielded twisted-pair (UTP) CAT5 cables, as shown in Figure 45. The component signals Y, Pb, and Pr are connected to the LMH6734 transmit side inputs with a 75 $\Omega$  termination. The LMH6734 transmit amplifiers are configured for a gain of +2 V/V before driving the CAT5 cable. Only three out of the four pairs in the standard CAT5 are utilized, the fourth pair is available for audio. The output of the LMH6734 transmit amplifier drives a 50 $\Omega$  transmission system with one side of the twisted pair terminated 50 $\Omega$  to ground. Note this system, without signal equalization, will satisfy transmission up to 200 ft. For longer cable lengths, frequency and gain equalization to compensate for signal degradation is recommended.

The LMH6734 receive side is configured for a unity gain buffer for the component signals received through the CAT5 cable. The inputs of the receiver channels are 100 $\Omega$  differentially terminated. The two 327 $\Omega$  external resisters were chosen to match the internal R<sub>F</sub> and R<sub>G</sub> value of 327 $\Omega$ . Figure 46, shows the LMH6734 transceiver frequency response over various lengths of CAT5 cable with a 1 V<sub>PP</sub> input signal at ±5 supply voltage. The CMRR of the LMH6734 receive side at low frequencies is 55 dB at best with a split power supply of ±5V.

Figure 45. Component Video Transmission Over UTP (CAT5)

Figure 46. Frequency Response vs. Normalized Gain and CAT5 Cable Length

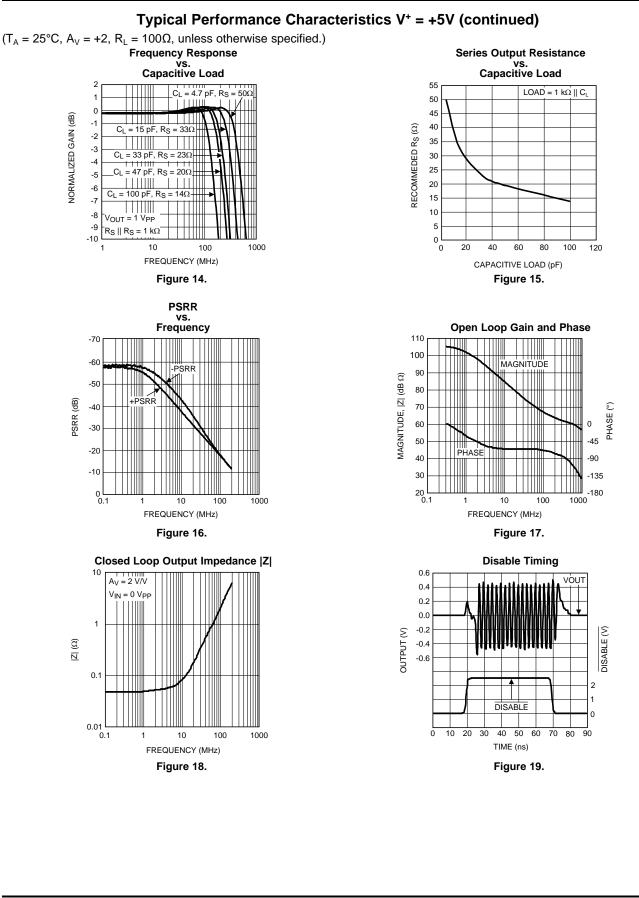

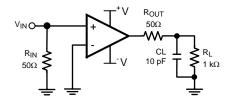

## DRIVING CAPACITIVE LOADS

Capacitive output loading applications will benefit from the use of a series output resistor  $R_{OUT}$ . Figure 47 shows the use of a series output resistor,  $R_{OUT}$ , to stabilize the amplifier output under capacitive loading. Capacitive loads of 5 to 120 pF are the most critical, causing ringing, frequency response peaking and possible oscillation. The charts "Suggested  $R_{OUT}$  vs. Cap Load" give a recommended value for selecting a series output resistor for mitigating capacitive loads. The values suggested in the charts are selected for 0.5 dB or less of peaking in the frequency response. This gives a good compromise between settling time and bandwidth. For applications where maximum frequency response is needed and some peaking is tolerable, the value of  $R_{OUT}$  can be reduced slightly from the recommended values.

Figure 47. Decoupling Capacitive Loads

## LAYOUT CONSIDERATIONS

Whenever questions about layout arise, use the evaluation board as a guide. The LMH730275 is the evaluation board supplied with samples of the LMH6734.

To reduce parasitic capacitances, ground and power planes should be removed near the input and output pins. For long signal paths controlled impedance lines should be used, along with impedance matching elements at both ends.

Bypass capacitors should be placed as close to the device as possible. Bypass capacitors from each rail to ground are applied in pairs. The larger electrolytic bypass capacitors can be located farther from the device, the smaller ceramic capacitors should be placed as close to the device as possible. The LMH6734 has multiple power and ground pins for enhanced supply bypassing. Every pin should ideally have a separate bypass capacitor. Sharing bypass capacitors may slightly degrade second order harmonic performance, especially if the supply traces are thin and /or long. In Figure 35, Figure 36, and Figure 37 it is recommended an optional capacitor,  $C_{SS}$ = 0.01 µF, be connected between the split supplies for best second harmonic distortion. Another option to using  $C_{SS}$  is to use pairs of 0.01 µF and 0.1 µF ceramic capacitors for each supply bypass.

## SNOSAY0C-JUNE 2007-REVISED APRIL 2013

#### VIDEO PERFORMANCE

The LMH6734 has been designed to provide excellent performance with production quality video signals in a wide variety of formats such as HDTV and High Resolution VGA. NTSC and PAL performance is nearly flawless. Best performance will be obtained with back terminated loads. The back termination reduces reflections from the transmission line and effectively masks transmission line and other parasitic capacitances from the amplifier output stage. Figure 41 shows a typical configuration for driving a 75 $\Omega$  cable. The amplifier is configured for a gain of two to make up for the 6 dB of loss in R<sub>OUT</sub>.

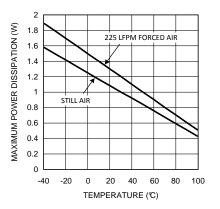

#### POWER DISSIPATION

The LMH6734 is optimized for maximum speed and performance in the small form factor of the standard 16-Pin SSOP package. To achieve its high level of performance, the LMH6734 consumes an appreciable amount of quiescent current which cannot be neglected when considering the total package power dissipation limit. The quiescent current contributes to about 40° C rise in junction temperature when no additional heat sink is used ( $V_s = \pm 5V$ , all three channels on). Therefore, it is easy to see the need for proper precautions in order to make sure the junction temperature's absolute maximum rating of 150°C is not violated.

To ensure maximum output drive and highest performance, thermal shutdown is not provided. Therefore, it is of utmost importance to make sure that the  $T_{JMAX}$  is never exceeded due to the overall power dissipation (all three channels).

With the LMH6734 used in a back-terminated  $75\Omega$  RGB analog video system (with 2 V<sub>PP</sub> output voltage), the total power dissipation is around 305 mW of which 220 mW is due to the quiescent device dissipation (output black level at 0V). With no additional heat sink used, the junction temperature rises to about 120°C when operated at 85°C ambient.

To reduce the junction temperature many options are available. Forced air cooling is the easiest option. An external add-on heat-sink can be added to the 16-Pin SSOP package, or alternatively, additional board metal (copper) area can be utilized as heat-sink.

An effective way to reduce the junction temperature for the 16-Pin SSOP package (and other plastic packages) is to use the copper board area to conduct heat. With no enhancement the major heat flow path in this package is from the die through the metal lead frame (inside the package) and onto the surrounding copper through the interconnecting leads. Since high frequency performance requires limited metal near the device pins the best way to use board copper to remove heat is through the bottom of the package. A gap filler with high thermal conductivity can be used to conduct heat from the bottom of the package to copper on the circuit board. Vias to a ground or power plane on the back side of the circuit board will provide additional heat dissipation. A combination of front side copper and vias to the back side can be combined as well.

Follow these steps to determine the maximum power dissipation for the LMH6734:

- 1. Calculate the quiescent (no-load) power:  $P_{AMP} = I_{CC} X (V_S) V_S = V^+ V^-$

- 2. Calculate the RMS power dissipated in the output stage:

- $P_D$  (rms) = rms ((V<sub>S</sub> V<sub>OUT</sub>) X I<sub>OUT</sub>) where V<sub>OUT</sub> and I<sub>OUT</sub> are the voltage and current across the external load and V<sub>S</sub> is the total supply current

- 3. Calculate the total RMS power:  $P_T = P_{AMP} + P_D$

The maximum power that the LMH6734 package can dissipate at a given temperature (See Figure 48) can be derived with the following equation:

$P_{MAX} = (150^{\circ} \text{ C/W} - T_{AMB})/\theta_{JA}$ , where  $T_{AMB} = \text{Ambient temperature (°C) and } \theta_{JA} = \text{Thermal resistance, from junction to ambient, for a given package (°C/W). For the SSOP package <math>\theta_{JA}$  is 120°C/W.

Figure 48. Maximum Power Dissipation

#### ESD PROTECTION

The LMH6734 is protected against electrostatic discharge (ESD) on all pins. The LMH6734 will survive 2000V Human Body Model and 200V Machine Model events.

Under closed loop operation the ESD diodes have no affect on circuit performance. There are occasions, however, when the ESD diodes will be evident. If the LMH6734 is driven by a large signal while the device is powered down the ESD diodes will conduct.

The current that flows through the ESD diodes will either exit the chip through the supply pins or will flow through the device, hence it is possible to power up a chip with a large signal applied to the input pins. Shorting the power pins to each other will prevent the chip from being powered up through the input.

### **EVALUATION BOARDS**

Texas Instruments provides the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization. Many of the datasheet plots were measured with these boards.

| Device    | Package | Evaluation Board Part Number |

|-----------|---------|------------------------------|

| LMH6734MQ | SSOP    | LMH730275                    |

A bare evaluation board can be ordered when a sample request is placed with Texas Instruments.

# **REVISION HISTORY**

| Cł | hanges from Revision B (April 2013) to Revision C  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 19   |

www.ti.com

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated