#### LMN6184DF 60V N-Channel Enhancement Mode MOSFET

#### **Features**

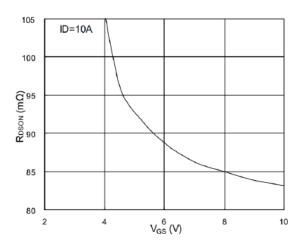

- $R_{DS(ON)}=92m\Omega@V_{GS}=10V$

- $R_{DS(ON)}=100m\Omega@V_{GS}=4.5V$

- Improved dv/dt capability

- Fast switching

- 100% EAS guaranteed.

#### **Product Description**

These N-Channel enhancement mode power field effect transistors are using trench DMOS technology. This advanced technology has

been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode.

These devices are well suited for high efficiency fast switching applications.

#### **Applications**

- Motor Drive

- Power Tools

- LED Lighting

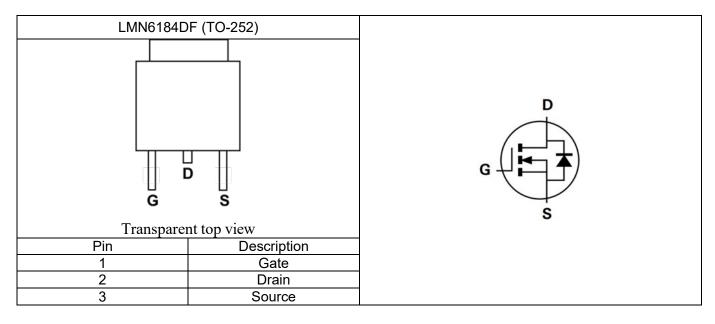

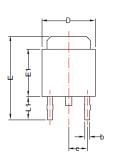

### **Pin Configuration**

## **Ordering Information**

| Ordering Information |         |          |              |         |          |  |

|----------------------|---------|----------|--------------|---------|----------|--|

| Part Number          | P/N     | PKG code | Pb Free code | Package | Quantity |  |

| LMN6184DF            | LMN4184 | D        | F            | TO-252  | 2500 PCS |  |

## **Marking Information**

# **Absolute Maximum Ratings**

(T<sub>C</sub>=25°C Unless otherwise noted)

| Symbol           | Parameter                                           | Parameter                                         |      | Unit  |

|------------------|-----------------------------------------------------|---------------------------------------------------|------|-------|

| $V_{DSS}$        | Drain-Source Voltage                                | Drain-Source Voltage                              |      | V     |

| V <sub>GSS</sub> | Gate-Source Voltage                                 | Gate-Source Voltage                               |      | V     |

|                  | Continuous Drain Current <sup>1</sup>               | T <sub>C</sub> =25°C                              | 10   |       |

| •                |                                                     | T <sub>C</sub> =100°C                             | 6    | Δ.    |

| l <sub>D</sub>   |                                                     | T <sub>A</sub> =25°C                              | 3    | A     |

|                  |                                                     | T <sub>A</sub> =70°C                              | 2    |       |

| I <sub>DM</sub>  | Pulsed Drain Current <sup>2</sup>                   |                                                   | 20   | A     |

| I <sub>AS</sub>  | Single Pulse Avalanche Curr                         | Single Pulse Avalanche Current                    |      | А     |

| E <sub>AS</sub>  | Single Pulse Avalanche Ene                          | Single Pulse Avalanche Energy <sup>3</sup>        |      | mJ    |

|                  | Total Power Dissipation <sup>4</sup>                | T <sub>C</sub> =25°C                              | 20.8 |       |

| <u></u>          |                                                     | T <sub>C</sub> =100°C                             | 8.3  | 10/   |

| $P_{D}$          |                                                     | T <sub>A</sub> =25°C                              | 2    | W     |

|                  |                                                     | T <sub>A</sub> =70°C                              | 1.2  |       |

| TJ               | Operating Junction Tempera                          | Operating Junction Temperature                    |      | °C    |

| $T_{STG}$        | Storage Temperature Range                           | Storage Temperature Range                         |      | °C    |

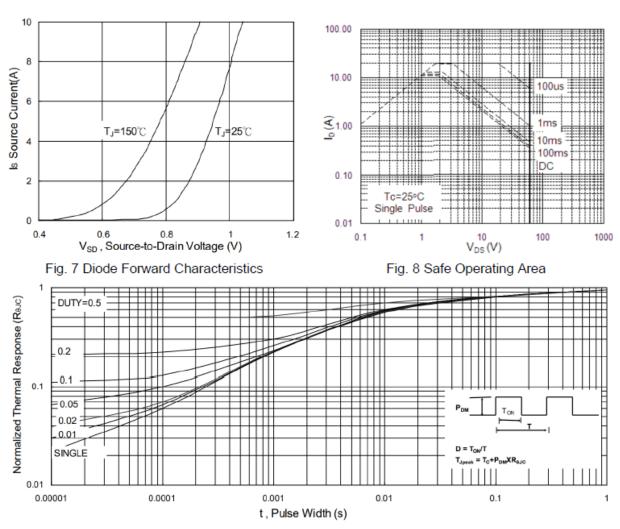

| R <sub>θJC</sub> | Thermal Resistance, Junctio                         | Thermal Resistance, Junction to Case <sup>1</sup> |      | °C /W |

| $R_{\theta JA}$  | Thermal Resistance-Junction to Ambient <sup>1</sup> |                                                   | 62   | °C /W |

#### **Electrical Characteristics**

#### (T<sub>C</sub>=25°C Unless otherwise noted)

| Symbol                | Parameter                               | Conditions                                   | Min | Тур | Max  | Unit |  |

|-----------------------|-----------------------------------------|----------------------------------------------|-----|-----|------|------|--|

|                       | Static                                  |                                              |     |     |      |      |  |

| BV <sub>DSS</sub>     | Drain-Source Breakdown Voltage          | $V_{GS}$ =0 $V$ , $I_D$ =250 $u$ A           | 60  |     |      | V    |  |

| $V_{GS(th)}$          | Gate Threshold Voltage                  | $V_{DS}=V_{GS}$ , $I_{D}=250uA$              | 1   |     | 3    | V    |  |

| $I_{GSS}$             | Gate Leakage Current                    | $V_{DS}$ =0V, $V_{GS}$ =±20V                 |     |     | ±100 | nΑ   |  |

| I <sub>DSS</sub>      | Zero Gate Voltage Drain Current         | $V_{DS}$ =60V, $V_{GS}$ =0V                  |     |     | 1    | uA   |  |

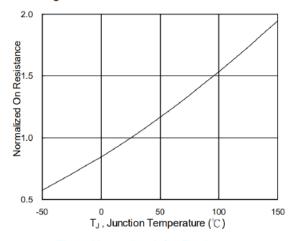

| R <sub>DS(on)</sub>   | Drain-Source On-Resistance <sup>2</sup> | $V_{GS}$ =10V, $I_D$ =6A                     |     | 85  | 92   | mΩ   |  |

| 1 (DS(on)             |                                         | $V_{GS}$ =4.5V, $I_D$ =3A                    |     | 90  | 100  |      |  |

| <b>9</b> FS           | Forward Transconductance                | $V_{DS}$ =10V, $I_{D}$ =3A                   |     | 3.6 |      | S    |  |

|                       |                                         | Dynamic                                      |     |     |      |      |  |

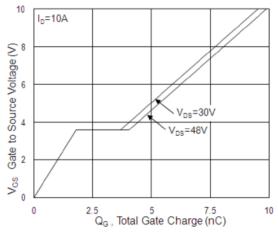

| $Q_g$                 | Total Gate Charge                       | V <sub>DS</sub> =48V, V <sub>GS</sub> =4.5V, |     | 4.9 |      | nC   |  |

| $Q_gs$                | Gate-Source Charge                      | $I_{D}=10A$                                  |     | 1.8 |      |      |  |

| $Q_gd$                | Gate-Drain Charge                       | ID-TOA                                       |     | 2.2 |      |      |  |

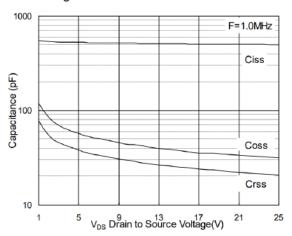

| C <sub>iss</sub>      | Input Capacitance                       | \/ -15\/ \/ -0\/                             |     | 511 |      | pF   |  |

| Coss                  | Output Capacitance                      | $V_{DS}$ =15V, $V_{GS}$ =0V, f=1MHz          |     | 38  |      |      |  |

| C <sub>rss</sub>      | Reverse Transfer Capacitance            | 1-11/11/12                                   |     | 25  |      |      |  |

| t <sub>d(on)</sub>    | Turn-On Time <sup>2,3</sup>             |                                              |     | 6   |      | ns   |  |

| t <sub>r</sub>        | Tum-On Time-,                           | $V_{DD}$ =30V, $I_{D}$ =3A,                  |     | 9   |      |      |  |

| $t_{d(off)}$          | Turn-Off Time <sup>2,3</sup>            | $V_{GS}$ =4.5V, $R_{G}$ =3.3 $\Omega$        |     | 18  |      |      |  |

| t <sub>f</sub>        | Turn-Oil Time <sup>2,9</sup>            |                                              |     | 5   |      |      |  |

| Diode characteristics |                                         |                                              |     |     |      |      |  |

| V <sub>SD</sub>       | Diode Forward Voltage <sup>2</sup>      | V <sub>GS</sub> =0V, I <sub>S</sub> =10A     |     |     | 1.4  | V    |  |

| I <sub>S</sub>        | Continuous Source Current <sup>1</sup>  | $V_G=V_D=0V$ ,                               |     |     | 10   | А    |  |

| ıs                    | Continuous Source Current               | Force Current                                |     |     |      |      |  |

| trr                   | Reverse Recovery Time                   | $I_S=3A$ , $V_{GS}=0V$                       |     | 19  |      | nS   |  |

| Qrr                   | Reverse Recovery Charge                 | dI/dt=100A/μs                                |     | 28  |      | nC   |  |

#### Note:

- 1. The data tested by surface mounted on a 1 inch2 FR-4 board with 2OZ copper.

- 2. The data tested by pulsed, pulse width  $\leq$  300us, duty cycle  $\leq$  2%

- 3. The EAS data shows Max. rating. The test condition is VDD=25V, VGS=10V, L=0.1mH, IAS=11.2A

- 4. The power dissipation is limited by  $150\,^{\circ}\mathrm{C}$  junction temperature

- 5. The data is theoretically the same as ID and IDM, in real applications, should be limited by total power dissipation.

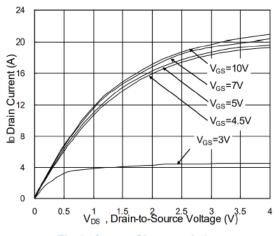

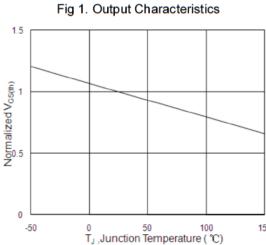

### **Typical Performance Characteristics**

Fig. 3 Normalized Gate Threshold Voltage

Fig. 5 Gate Charge Characteristics

Fig. 2 On-Resistance vs. Gate Source

Fig. 4 Normalized On-Resistance

Fig. 6 Typical Capacitance

## **Typical Performance Characteristics**

Fig. 9 Transient Thermal Impedance

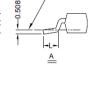

# Package Dimension:

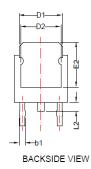

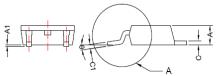

# TO-252

# **Package Dimension**

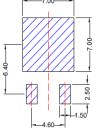

# Recommended Land Pattern

|          | Dimensions  |       |           |       |  |

|----------|-------------|-------|-----------|-------|--|

| Compleal | Millimeters |       | Inches    |       |  |

| Symbol   | Min         | Max   | Min       | Max   |  |

| Α        | 2.18        | 2.40  | 0.086     | 0.094 |  |

| A1       | 0.00        | 0.15  | 0.000     | 0.006 |  |

| b        | 0.50        | 0.90  | 0.020     | 0.035 |  |

| С        | 0.45        | 0.89  | 0.018     | 0.035 |  |

| c1       | 0.40        | 0.61  | 0.016     | 0.024 |  |

| D        | 6.35        | 6.80  | 0.250     | 0.268 |  |

| D1       | 4.95        | 5.50  | 0.195     | 0.217 |  |

| D2       | 3.81        | -     | 0.150     | -     |  |

| E        | 9.40        | 10.41 | 0.370     | 0.410 |  |

| E1       | 5.33        | 5.80  | 0.210     | 0.228 |  |

| E2       | 4.57        | -     | 0.180     | -     |  |

| е        | 2.286 BSC   |       | 0.090 BSC |       |  |

| L        | 1.40        | 1.78  | 0.055     | 0.070 |  |

| L1       | 2.40        | 3.00  | 0.094     | 0.118 |  |

| θ        | 0°          | 8°    | 0°        | 8°    |  |

#### NOTICE

LFC Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all LFC Semiconductor products described or contained herein. LFC Semiconductor products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

Applications shown on the herein document are examples of standard use and operation. Customers are responsible in comprehending the suitable use in particular applications. LFC Semiconductor makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Information furnished is believed to be accurate and reliable. However LFC Semiconductor assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of LFC Semiconductor. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information without express written approval of LFC Semiconductor.