# LMT035KDH03

# LCD Module User Manual

| Checked by: | Approved by:       |

|-------------|--------------------|

| ,           |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

| Date:       | Date:              |

|             | Checked by:  Date: |

| Rev. | Descriptions                                                                      | Release Date |

|------|-----------------------------------------------------------------------------------|--------------|

| 0.1  | Preliminary                                                                       | 2009-09-27   |

| 0.2  | Typing Correction on Terminals Table                                              | 2010-04-03   |

| 0.3  | Update Parameters                                                                 | 2012-01-31   |

| 0.4  | Add T <sub>VS</sub> timing details and typical input data timing diagram in 5.3.1 | 2012-04-17   |

|      |                                                                                   |              |

URL: www.topwaydisplay.com www.topwaysz.com Page: 1 of 23

# **Table of Content**

| 1.  | General Specification                                                                                                                     | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|

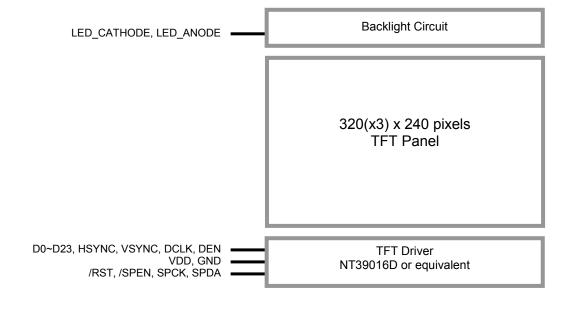

| 2.  | Block Diagram                                                                                                                             | 3  |

| 3.  | Terminal Functions                                                                                                                        | 4  |

| 3.1 | Interface                                                                                                                                 | 4  |

| 4.  | Absolute Maximum Ratings                                                                                                                  | 5  |

| 5.  | Electrical Characteristics                                                                                                                | 5  |

| 5.1 | DC Characteristics (MCU terminal)                                                                                                         | 5  |

| 5.2 | 2 LED Backlight Circuit Characteristics                                                                                                   | 5  |

| 5.3 | B AC Characteristics                                                                                                                      | 6  |

|     | <ul><li>5.3.1 Display Data Input Timing</li><li>5.3.2 Active Display Timing</li><li>5.3.3 Serial Command Interface (SPI) Timing</li></ul> | 8  |

| 6.  | Optical Characteristics                                                                                                                   | 10 |

| 7.  | Function Specifications                                                                                                                   | 12 |

| 7.1 | SPI interface Data Packet                                                                                                                 | 12 |

| 7.2 | SPI interface Commands Summary                                                                                                            | 13 |

| 7.3 | SPI interface Commands Details                                                                                                            | 13 |

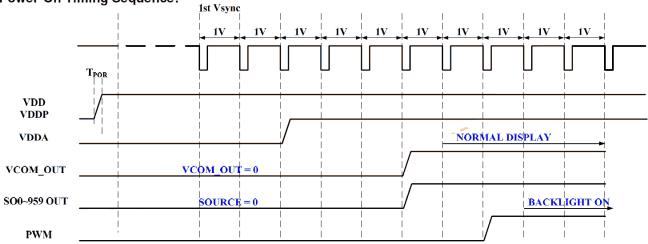

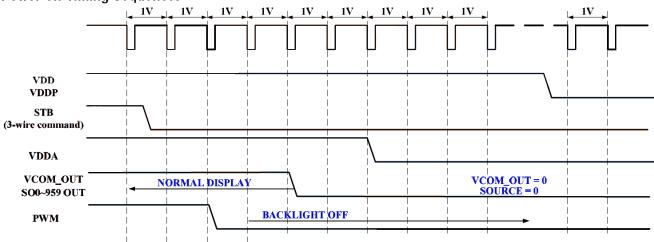

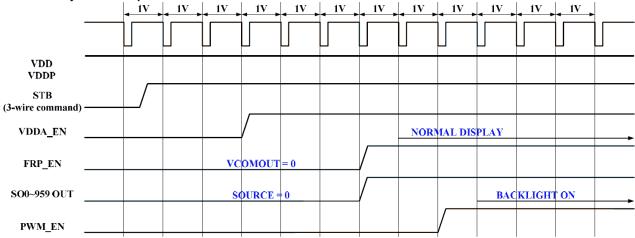

| 7.4 | Power On/Off Sequence                                                                                                                     | 20 |

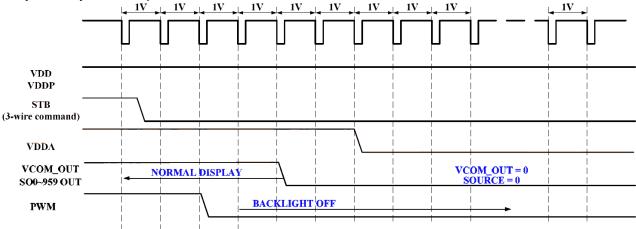

| 7.5 | Standby Sequence                                                                                                                          | 21 |

| 7.6 | Reset Function                                                                                                                            | 21 |

| 8.  | Precautions of using LCD Modules                                                                                                          | 22 |

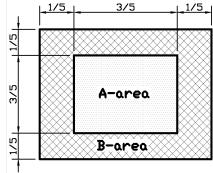

| 9.  | Appendix A < Inspection items and criteria for appearance defect>                                                                         | 23 |

# 1. General Specification

Screen Size(Diagonal): 3.5 inch

Resolution: 320(RGB) x 240

Signal Interface: 24bit parallel bus / CCIR656 / 601

Color Depth: 16.7M color (24bit) \*1

Dot Pitch: 0.219 x 0.219 (mm)

Pixel Configuration : RGB Stripe

Display Mode : Transmissive / Positive Surface Treatment : Anti-Glare Treatment

Viewing Direction: 12 o'clock

Outline Dimension : 76.9 x 63.9 x 3.15 (mm)

(exclude FPC, see attached drawing for details)

Active Area: 70.08 x 52.56 (mm)

Weight: (29.3g)

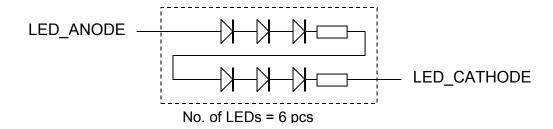

Backlight: 6 LEDs (in series)

Driver IC NT39016D Operating Temperature :  $-20 \sim +70^{\circ}$ C Storage Temperature :  $-30 \sim +80^{\circ}$ C

Note:

# 2. Block Diagram

Document Name: LMT035KDH03-Rev04.DOC Page: 3 of 23

<sup>\*1</sup> Color tune may slightly changed by temperature and driving voltage.

# 3. Terminal Functions

### 3.1 Interface

| Pin<br>No. | Pin<br>Name | I/O | Descriptions                                  |

|------------|-------------|-----|-----------------------------------------------|

| 1          | LED_CATHODE | Р   | Backlight LED Cathode supply                  |

| 2          |             |     |                                               |

| 3 4        | LED_ANODE   | Р   | Backlight LED Anode supply                    |

| 5          | NC          | -   | No Connection                                 |

| 6          | NC          | -   |                                               |

| 7          | NC          | -   |                                               |

| 8          | /RST        | 1   | Reset signal active LOW                       |

| 9          | /SPEN       | 1   | SPI enable signal, active LOW, normal HI (*1) |

| 10         | SPCK        | I   | SPI clock signal, rising edge trigger(*1)     |

| 11         | SPDA        | I/O | SPI data signal (*1)                          |

| 12         | D0          | 1   | B0~B7,                                        |

| •          | :           |     | Blue data input(*2)                           |

| 19         | D7          |     | ,                                             |

| 20         | D8          | 1   | G0~G7                                         |

| :          | :           |     | Green data input (*2)                         |

| 27         | D15         |     | ,                                             |

| 28         | D16         | 1   | R0~R7(*2)                                     |

| :          | :           |     | Read data input (*2)                          |

| 35         | D23         |     |                                               |

| 36         | HSYNC       | I   | Horizontal Sync Signal                        |

| 37         | VSYNC       | I   | Vertical Sync Signal                          |

| 38         | DCLK        | I   | Data Clock Input                              |

| 39         | NC          |     | No Connection                                 |

| 40         | NC          |     |                                               |

| 41         | VDD         | Р   | Positive Power Supply                         |

| 42         | VDD         |     | ,                                             |

| 43         | NC          |     | No Connection                                 |

| :          | :           |     |                                               |

| 51         | NC          |     |                                               |

| 52         | DEN         | I   | Data Enable Input (*3)                        |

| 53         | GND         | Р   | Power Ground Supply                           |

| 54         | GND         |     |                                               |

| Note:      | •           | •   | ·                                             |

#### Note:

URL:

- \*1. /SPEN, SPCK, SPDA must be connected to referenced control pins to enable the SPI initialization. It may necessary to config the TFT Driver through SPI interface to provide best display result.

- \*2. For CCIR601/CCIR656 Interface, only R0-R7 is used. For unused pins (B0-B7,G0-G7), please connect to GND or floating. The interface is selected by the SPI initial code. Default setting is parallel 24-bit RGB interface.

| Mode         | D(23:16) | D(15:08) | D(07:00)     | HSYNC   | VSYNC  | DEN              |

|--------------|----------|----------|--------------|---------|--------|------------------|

| ITU-R BT 656 | D(23:16) | GND      | GND          | NC      | NC     | NC               |

| ITU-R BT 601 | D(23:16) | GND      | GND          | HSYNC   | VSYNC  | NC               |

| 8 Bit RGB    | D(23:16) | GND      | GND          | HSYNC   | VSYNC  | NC for HV Mode   |

| O DIL INOD   | D(23.10) | OND      | OND          | 1131110 | VOTING | DEN for Den Mode |

| 24 Bit RGB   | R(7:0)   | G(7:0)   | B(7:0)       | HSYNC   | VSYNC  | NC for HV Mode   |

| 24 bit NGb   | K(7.0)   | G(7.0)   | B(7:0) HSYNC |         | VSTNC  | DEN for Den Mode |

\*3: For digital RGB input data format, both SYNC mode and DE+SYNC mode are supported. If DEN signal is fixed low. SYNC mode is used. Otherwise, DE+SYNC is used

www.topwaydisplay.com Document Name: LMT035KDH03-Rev04.DOC www.topwaysz.com Page: 4 of 23

# 4. Absolute Maximum Ratings

| Items                 | Symbol          | Min. | Max. | Unit | Condition       |

|-----------------------|-----------------|------|------|------|-----------------|

| Supply Voltage        | $V_{DD}$        | -0.3 | +4.0 | V    | GND = 0V        |

| Input Voltage         | $V_{IN}$        | -0.3 | +4.0 | V    | GND = 0V        |

| Operating Temperature | T <sub>OP</sub> | -20  | +70  | °C   | No Condensation |

| Storage Temperature   | T <sub>ST</sub> | -30  | +80  | °C   | No Condensation |

Cautions:

Any Stresses exceeding the Absolute Maximum Ratings may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# 5. Electrical Characteristics

# **DC Characteristics (MCU terminal)**

GND=0V. VDD =3.3V. TOP =25°C

| Items                 | Symbol              | MIN.   | TYP. | MAX.   | Unit | Applicable Pin |

|-----------------------|---------------------|--------|------|--------|------|----------------|

| Operating Voltage     | $V_{DD}$            | 3.0    | 3.3  | 3.6    | V    | VDD            |

| Input High Voltage    | V <sub>IH</sub>     | 0.8VDD | -    | VDD    | V    | Input pins     |

| Input Low Voltage     | V <sub>IL</sub>     | GND    | -    | 0.2VDD | V    | Input pins     |

| Frame Freq            | F <sub>FRAME</sub>  | -      | 60   | -      | Hz   |                |

| Dot Data Clock(*1)    | f <sub>DOTCLK</sub> | -      | 6.5  | -      | MHz  |                |

| Operating Current(*2) | I <sub>DD</sub>     | 6.5    | 7.4  | 9.4    | mA   | VDD            |

#### Note.

- \*1. DOTCLK must be adapted to 19.5MHz in 8-bit mode

- \*2. test image is 16-grayscaly graphic

#### 5.2 **LED Backlight Circuit Characteristics**

If IFD ANODE = 20mA, Top = 25°C

| TELD ANOBE TO THE TELEPROPERTY OF THE TELEPROP |                         |      |         |      |      |      |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|---------|------|------|------|--|--|--|--|

| Items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Symbol                  | MIN. | TYP.    | MAX. | Unit | Note |  |  |  |  |

| Forward Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vf <sub>LED ANODE</sub> | -    | 19.2    | -    | V    |      |  |  |  |  |

| Forward Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | If <sub>LED ANODE</sub> | -    | 20      | 25   | mA   |      |  |  |  |  |

| Life Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                       | -    | (50000) | -    | hr   |      |  |  |  |  |

Cautions:

Exceeding the recommended driving current could cause substantial damage to the backlight and shorten its lifetime.

Document Name: LMT035KDH03-Rev04.DOC www.topwaydisplay.com www.topwaysz.com Page: 5 of 23

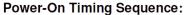

# 5.3 AC Characteristics

# 5.3.1 Display Data Input Timing

| Parameter                                           | Symbol            | Min.     | Тур.  | Max. | Unit  | Conditions                                                                     |

|-----------------------------------------------------|-------------------|----------|-------|------|-------|--------------------------------------------------------------------------------|

| VDD power source slew time                          | T <sub>POR</sub>  |          |       | 1000 | us    | From 0V to 90% VDD                                                             |

| RSTB active pulse width                             | T <sub>RSTB</sub> | 40       |       |      | us    | VDD = 3.3V                                                                     |

| CLKIN clock time                                    | Tclk              | 33.3/125 | 1     | -    | ns    | Please refer to timing table(p.32)                                             |

| HSD to CLKIN                                        | Thc               | -        | -     | 1    | CLKIN |                                                                                |

| HSD width                                           | Thwh              | 1        |       | -    | CLKIN |                                                                                |

| VSD width                                           | Tvwh              | 1        | 1     | -    | Th    |                                                                                |

| HSD period time                                     | Th                | 60       | 63.56 | 67   | us    |                                                                                |

| VSD setup time                                      | Tvst              | 8        | -     | -    | ns    |                                                                                |

| VSD hold time                                       | Tvhd              | 10       | -     | -    | ns    |                                                                                |

| HSD setup time                                      | Thst              | 8        | -     | -    | ns    |                                                                                |

| HSD hold time                                       | Thhd              | 10       | -     | -    | ns    |                                                                                |

| Data set-up time                                    | Tdsu              | 8        | -     | -    | ns    | DIN[23:0] to CLKIN                                                             |

| Data hold time                                      | Tdhd              | 10       | -     | -    | ns    | DIN[23:0] to CLKIN                                                             |

| DEN setup time                                      | Tesd              | 12       | -     |      | ns    | DEN to CLKIN                                                                   |

| Time that VSD to 1 <sup>st</sup> line<br>data input | Tvs               | 2        | 13    | 127  | Th    | @CCIR601 / 8bit RGB HV mode<br>Control by HDLY[6:0] setting<br>Tvs = HDLY[6:0] |

| Time that CCIR_V to 1 <sup>st</sup> line data input | Tvs               | 12       | 20    | 28   | Th    | @CCIR656 NTSC mode<br>Control by HDLY[6:0] setting<br>Tvs = HDLY[6:0]          |

| Time that CCIR_V to 1 <sup>st</sup> line data input | Tvs               | 17       | 25    | 33   | Th    | @CCIR656 PAL mode<br>Control by HDLY[6:0] setting<br>Tvs = HDLY[6:0]           |

| Time that VSD to 1 <sup>st</sup> line data input    | Tvs               | 2        | 13    | 127  | Th    | @24bit RGB HV mode<br>Control by HDLY[6:0] setting<br>Tvs = HDLY[6:0]          |

Signal naming references:

| Terminal Name | Signal Name |

|---------------|-------------|

| D23~D0        | DIN[23:0]   |

| DCLK          | CLKIN       |

| HSYNC         | HSD         |

| VSYNC         | VSD         |

| DEN           | DEN         |

URL: www.topwaydisplay.com www.topwaysz.com Document Name: LMT035KDH03-Rev04.DOC Page: 6 of 23

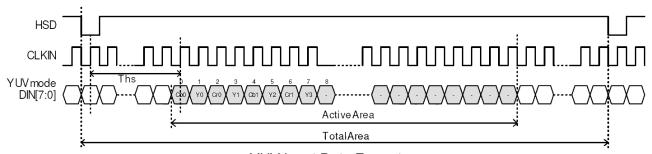

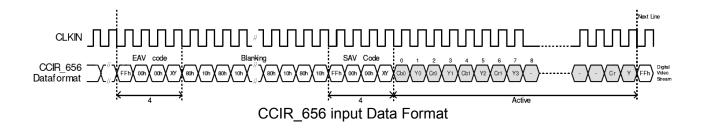

### CCIR601 mode A/B

| Parameter                               | Symbol | Min. | Тур.         | Max. | Unit  | Conditions                       |

|-----------------------------------------|--------|------|--------------|------|-------|----------------------------------|

| CLKIN frequency                         | Fclk   | -    | 24.54<br>/27 | 30   | MHz   | VDD = 3.0 ~3.6V                  |

| CLKIN cycle time                        | Tclk   | -    | 40/37        |      | ns    |                                  |

| CLKIN pulse duty                        | Tcwh   | 40   | 50           | 60   | %     | Tclk                             |

| Time from HSD to 1'st data input (PAL)  | Ths    | 128  | 264          | -    | CLKIN | DDLY = 136, Offset = 128 (fixed) |

| Time from HSD to 1'st data input (NTSC) | Ths    | 128  | 244          | -    | CLKIN | DDLY = 116, Offset = 128 (fixed) |

#### CCIR656 mode A/B

| Parameter                               | Symbol | Min. | Тур. | Max. | Unit  | Conditions                       |

|-----------------------------------------|--------|------|------|------|-------|----------------------------------|

| CLKIN frequency                         | Fclk   | -    | 27   | 30   | MHz   | VDD = 3.0 ~3.6V                  |

| CLKIN cycle time                        | Tclk   | -    | 37   |      | ns    |                                  |

| CLKIN pulse duty                        | Tcwh   | 40   | 50   | 60   | %     | Tclk                             |

| Time from EAV to 1'st data input (PAL)  | Ths    | 128  | 288  |      | CLKIN | DDLY = 152, Offset = 128 (fixed) |

| Time from EAV to 1'st data input (NTSC) | Ths    | 128  | 276  |      | CLKIN | DDLY = 140, Offset = 128 (fixed) |

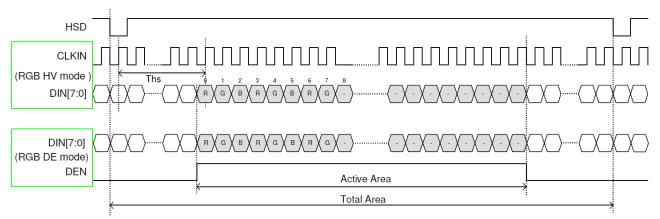

### 8bit RGB 960 CH Mode

| Parameter                              | Symbol | Min.                 | Тур. | Max. | Unit  | Conditions                    |

|----------------------------------------|--------|----------------------|------|------|-------|-------------------------------|

| CLKIN frequency                        | Fclk   | , <sup>, , ,</sup> - | 27   | 30   | MHz   | VDD = 3.0 ~3.6V               |

| CLKIN cycle time                       | Tclk   | -                    | 37   |      | ns    |                               |

| CLKIN pulse duty                       | Tcwh   | 40                   | 50   | 60   | %     | Tclk                          |

| Time that HSD to 1'st data input(NTSC) | Ths    | 35                   | 70   | 255  | CLKIN | DDLY = 70, Offset = 0 (fixed) |

# 24bit RGB mode (SEL[3:0]=1100 or 1101)

| Parameter                              | Symbol | Min. | Тур. | Max. | Unit  | Conditions                   |

|----------------------------------------|--------|------|------|------|-------|------------------------------|

| CLKIN frequency                        | Fclk   | 6.1  | 6.4  | 8.0  | MHz   | VDD = 3.0 ~3.6V              |

| CLKIN cycle time                       | Tclk   | 125  | 156  | 164  | ns    |                              |

| CLKIN pulse duty                       | Tcwh   | 40   | 50   | 60   | %     | Tclk                         |

| Time that HSD to 1 st data input(NTSC) | Ths    | 40   | 70   | 255  | CLKIN | DDLY =70, Offset = 0 (fixed) |

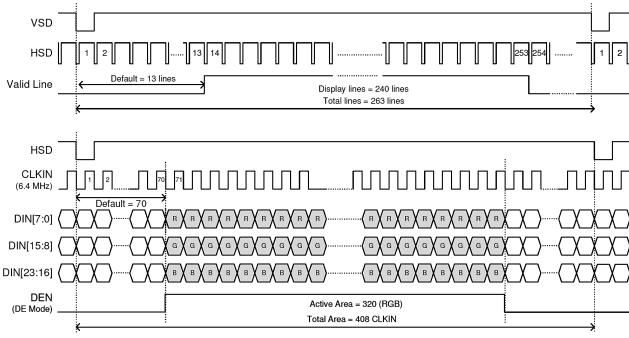

Typical Input Data Timing Diagram (24bit RGB mode SEL[3:0]=1100)

Document Name: LMT035KDH03-Rev04.DOC Page: 7 of 23

URL:

# 5.3.2 Active Display Timing

| Input Format | Format Standard | CLKIN (MHz) | HSD (CLKIN) | Total Area<br>(CLKIN) | Active Area (CLKIN) | Note    |

|--------------|-----------------|-------------|-------------|-----------------------|---------------------|---------|

|              | CCIR_601        | 27          | 1           | 1716                  | 1440                |         |

| YUV          | CCIR_656        | 21          | 1           | 1728                  | 1440                |         |

|              | CCIR_601        | 24.54       | 1           | 1560                  | 1280                |         |

| 8bit RGB     | 8 bit RGB       | 27          | 1           | 1716                  | 960                 | 960x240 |

| 24bit RGB    | 24 bit RGB      | 6.4         | 1           | 408                   | 320                 |         |

**RGB** input Data Format

YUV input Data Format

Document Name: LMT035KDH03-Rev04.DOC

URL:

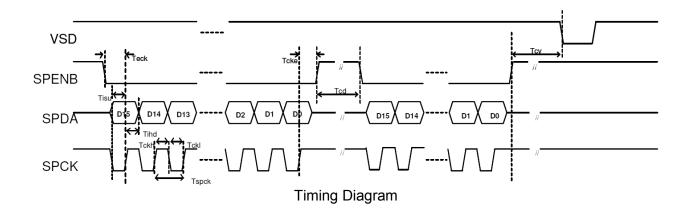

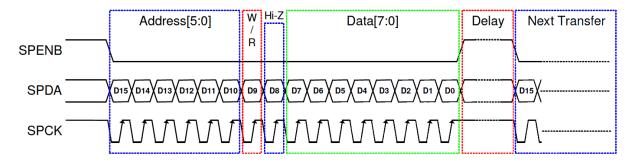

# 5.3.3 SPI Interface Timing

| Parameter               | Symbol | Min. | Тур. | Max. | Unit | Conditions   |

|-------------------------|--------|------|------|------|------|--------------|

| Serial clock            | Tspck  | 320  | -    | -    | ns   |              |

| SPCK pulse duty         |        | 40   | 50   | 60   | %    | Tckh / Tspck |

| Serial data setup time  | Tisu   | 120  | -    | -    | ns   |              |

| Serial data hold time   | Tihd   | 120  | -    | -    | ns   |              |

| Serial clock high/low   | Tckh/l | 120  | -    | -    | ns   |              |

| Chip select distinguish | Tcd    | 1    | -    | -    | us   |              |

| SPENB to VSD            | Tcv    | 1    | -    | -    | us   |              |

| SPENB input setup time  | Teck   | 150  | -    | -    | ns   |              |

| SPENB input hold time   | Tcke   | 150  | -    | -    | ns   |              |

Signal naming references:

| Terminal Name | Signal Name |

|---------------|-------------|

| SPDA          | SPDA        |

| SPCK          | SPCK        |

| VSYNC         | VSD         |

| /PSEN         | PSENB       |

| /RST          | RSTB        |

# 6. Optical Characteristics

| Item              | Sy                      | mbol           | Condition               | Min. | Тур.                 | Max. | Unit              | Note |   |

|-------------------|-------------------------|----------------|-------------------------|------|----------------------|------|-------------------|------|---|

| Brightness        |                         | Зр             | <i>θ</i> =0°            | -    | 250                  | -    | Cd/m <sup>2</sup> | 1    |   |

| Uniformity        | Δ                       | ∆Вр            | Ф=0°                    | 80%  | -                    | -    |                   | 1,2  |   |

| Viewing<br>Angle  | θ1<br>(Φ=90°<br>or270°) |                | (Φ=90°<br>or270°)<br>θ2 |      | r=90°<br>270°)<br>θ2 |      | -25~+6<br>-45~+4  | Deg  | 3 |

|                   | 180                     | I              |                         |      |                      |      |                   |      |   |

| Contrast<br>Ratio |                         | Cr             | <i>θ</i> =0°            | -    | 300                  | -    | -                 | 4    |   |

| Response          |                         | T <sub>r</sub> | Φ=0°                    | -    | 25                   | 40   | ms                | 5    |   |

| Time              |                         | T <sub>f</sub> |                         | -    | 25                   | 40   | ms                | 3    |   |

|                   | W                       | х              |                         | -    | 0.29                 | -    | -                 |      |   |

|                   | VV                      | у              |                         | -    | 0.31                 | -    | -                 |      |   |

|                   | В                       | х              |                         | -    | 0.60                 | -    | -                 |      |   |

| Color of<br>CIE   | R                       | у              |                         | -    | 0.37                 | -    | -                 |      |   |

| Coordinate        |                         | х              | <i>θ</i> =0°            | -    | 0.34                 | -    | -                 | 1,6  |   |

|                   | G                       | у              | Ф=0°                    | -    | 0.57                 | -    | -                 |      |   |

|                   | В                       | x              |                         | -    | 0.15                 | -    | -                 |      |   |

|                   | В                       | у              |                         | -    | 0.09                 | -    | -                 |      |   |

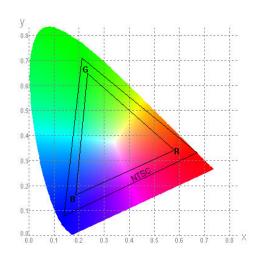

| NTSC<br>Ratio     |                         | S              |                         | 50   | -                    |      | %                 |      |   |

Note: The parameter is slightly changed by temperature, driving voltage and materiel.

# TOPWAY

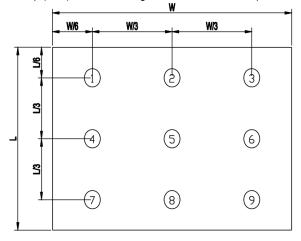

#### Note 1:

The data are measured after LEDs are turned on for 5 minutes. LCM displays full white. The brightness is the average value of 9 measured spots. Measurement equipment PR-705 (Φ8mm) Measuring condition:

- Measuring surroundings: Dark room

- Measuring temperature: Ta=25℃.

- Adjust operating voltage to get optimum contrast at the center of the display.

Measured value at the center point of LCD panel after more than 5 minutes while backlight turning on.

Note 2:

The luminance uniformity is calculated by using following formula.

$\triangle$ Bp = Bp (Min.) / Bp (Max.)×100 (%)

Bp (Max.) = Maximum brightness in 9 measured spots

Bp (Min.) = Minimum brightness in 9 measured spots.

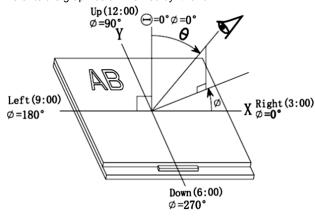

Note 3:

The definition of viewing angle:

Refer to the graph below marked by  $\theta$  and  $\Phi$

The definition of contrast ratio (Test LCM using PR-705):

Luminance When LCD is at "White"

state Contrast Ratio(CR)=

Luminance When LCD is at "Black"

state

(Contrast Ratio is measured in optimum common electrode voltage)

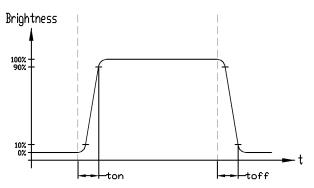

Note 5:

URL:

Definition of Response time. (Test LCD using DMS501):

The output signals of photo detector are measured when the input signals are changed from

"black" to "white" (falling time)

and from "white" to "black" (rising time), respectively.

The response time is defined as

www.topwaydisplay.com

www.topwaysz.com

the time interval between the 10% and 90% of amplitudes. Refer to figure as below.

Note 6:

Definition of Color of CIE Coordinate and NTSC Ratio.

Color gamut:

Document Name: LMT035KDH03-Rev04.DOC

# 7. Function Specifications

### **SPI Interface Command Packet**

The LMT035KDH03 terminal equipped with a SPI interface, which is for receiving command to adjust the TFT display to the best display result.

Command packet is in 16bit format, which include Register Address and Register Data.

/SPEN works as a chip enable pin and also for init the communication.

PSDA is the serial data line

SPCK is the serial clock, data bit latches into the TFT driver at rising edge

#### 3-Wire Command Format:

| Bit     | Description                                                                            |

|---------|----------------------------------------------------------------------------------------|

| D15-D10 | Register Address [5:0].                                                                |

| D9      | W/R control bit. "1" for Write; "0" for Read                                           |

| D8      | Hi-Z bit during read mode. Any data within this bits will be ignored during write mode |

| D7-D0   | Data for the W/R operation to the address indicated by Address phase                   |

#### 3-Wire Writer Format:

| MSB |     |          |         |      |     |    |    |    |    |          |          |         |          |         | LSB |

|-----|-----|----------|---------|------|-----|----|----|----|----|----------|----------|---------|----------|---------|-----|

| D15 | D14 | D13      | D12     | D11  | D10 | D9 | D8 | D7 | D6 | D5       | D4       | D3      | D2       | D1      | D0  |

|     | Reg | ister Ad | dress [ | 5:0] | ,   | 1  | Х  |    | D/ | ATA (Iss | sue by e | xternal | controll | <br>er) |     |

#### 3-Wire Read Format:

| MSB |     |          |          |      |     |    |      |    |    |      |        |        |       |    | LSB |

|-----|-----|----------|----------|------|-----|----|------|----|----|------|--------|--------|-------|----|-----|

| D15 | D14 | D13      | D12      | D11  | D10 | D9 | D8   | D7 | D6 | D5   | D4     | D3     | D2    | D1 | D0  |

|     | Reg | ister Ad | dress [5 | 5:0] | •   | 0  | Hi-Z |    |    | DATA | (Issue | by NT3 | 9016) |    |     |

Document Name: LMT035KDH03-Rev04.DOC

www.topwaydisplay.com www.topwaysz.com

# 7.2 SPI Interface Commands Summary

| 3-Wire   | Registers |       |     | Register Description                          |  |  |

|----------|-----------|-------|-----|-----------------------------------------------|--|--|

| D[15:10] | Name      | Init. | R/W | Function Description                          |  |  |

| 000000b  | R00       | 07h   | R/W | System control register                       |  |  |

| 000001b  | R01       | 00h   | R/W | Timing Controller function register           |  |  |

| 000010b  | R02       | 03h   | R/W | Operation control register                    |  |  |

| 000011b  | R03       | CCh   | R/W | Input data Format control register            |  |  |

| 000100b  | R04       | 46h   | R/W | Source Timing delay control register          |  |  |

| 000101b  | R05       | 0Dh   | R/W | Gate Timing delay control register            |  |  |

| 000110b  | R06       | 00h   | R/W | Reserved                                      |  |  |

| 000111b  | R07       | 00h   | R/W | Internal function control register            |  |  |

| 001000b  | R08       | 08h   | R/W | RGB Contrast control register                 |  |  |

| 001001b  | R09       | 40h   | R/W | RGB Brightness control register               |  |  |

| 001010b  | R0A       | 88h   | R/W | Hue / Saturation control register             |  |  |

| 001011b  | R0B       | 88h   | R/W | R / B Sub-Contrast control register           |  |  |

| 001100b  | R0C       | 20h   | R/W | R Sub-Brightness control register             |  |  |

| 001101b  | R0D       | 20h   | R/W | B Sub-Brightness control register             |  |  |

| 001110b  | R0E       | 10h   | R/W | VCOMDC Level Control Register                 |  |  |

| 001111b  | R0F       | A4h   | R/W | VCOMAC Level Control Register                 |  |  |

| 010000b  | R10       | 04h   | R/W | VGAM2 level control register                  |  |  |

| 010001b  | R11       | 24h   | R/W | VGAM3/4 level control register                |  |  |

| 010010b  | R12       | 24h   | R/W | VGAM5/6 level control register                |  |  |

| 100000b  | R20       | 00h   | R/W | Wide and narrow display mode control register |  |  |

# 7.3 SPI Interface Commands Details

**R00: System Control Register**

URL:

www.topwaydisplay.com www.topwaysz.com

| Bit       | Name      | Initial | R/W        | Description                                                                                                                           |

|-----------|-----------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7:4] | PAT[3:0]  | 0000b   | R/W        | Internal Test Pattern Selection                                                                                                       |

| Dit [7.4] | 1 7 [5.0] | 00000   | 1000       | PAT[3:0] : Select chip embedded test pattern.                                                                                         |

|           |           |         | (R)        | Internal PWM controller Power Down bit                                                                                                |

| Bit [3]   | PWMPDB    | 0b      | R/W        | PWMPDB = "0", internal PWM controller will be shut down                                                                               |

|           |           |         | □/ V V     | PWMPDB = "1", internal PWM controller normal operating                                                                                |

| Bit [2]   | -         | -       | -          | Reserve                                                                                                                               |

| Bit [1]   | STBYB     | 1b      | (R)<br>R/W | Standby Mode function control.  STBYB = "0", TCON, Source output will turn off and outputs are High-Z.  STBYB = "1", Normal operation |

| Bit [0]   | RESETB    | 1b      | R/W        | Global Reset Register.<br>Write "0" to reset whole chip. This bit will set to "1" automatically after chip was reset.                 |

PAT[3:0]: Embedded Auto Test Pattern Selection Register

| PAT[3:0] | Test Pattern                           | Note    |

|----------|----------------------------------------|---------|

| 00H      | Disable Internal Test Pattern Function | Default |

| 01H      | White                                  |         |

| 02H      | Black                                  |         |

| 03H      | Red                                    |         |

| 04H      | Green                                  |         |

| 05H      | Blue                                   |         |

| 06H      | Yellow                                 |         |

| 07H      | Cyan                                   |         |

| 08H      | Magenta                                |         |

| 09H      | Gray Level 8                           |         |

| 0AH      | Gray Level 16                          |         |

| 0BH      | Color Bar                              |         |

| 0CH      | Checker Board                          |         |

| 0DH      | Cross Talk Pattern                     |         |

| 0EH      | Horizontal Flick Pattern               |         |

| 0FH      | Test Pattern Auto Run Mode             |         |

Note: WNSEL[1:0] will be disabled under Internal Test Pattern mode.

Document Name: LMT035KDH03-Rev04.DOC Page: 13 of 23

**R01: Timing Controller Function Register**

| Bit       | Name      | Initial | R/W | Description                                                                                                                                                                                                                                                                                          |

|-----------|-----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [4:2] | SWD[2:0]  | 000b    | R/W | Control and switch the relationship between the R,G,B and outputs.                                                                                                                                                                                                                                   |

| DIL [4.2] | 3000[2.0] | GOOD    |     | This register is used to match different types of color filters on LCD panel                                                                                                                                                                                                                         |

| Bit [1]   | DITHB     | 0b      | R/W | Dithering enable. Active low DITHB = "0", Dithering on, (Pseudo 8-bits resolution). (Default mode) DITHB = "1", Dithering off, (6-bits resolution, truncation last 2-bits of the input data) Note 1: Recommend user to enable this function under all modes except for 18 bit RGB input application. |

| Bit [0]   | CFTYP     | 0b      | R/W | Color Filter Type Select. Select Delta or Stripe mode for data arrangement.  CFTYP = "0", Stripe mode, Data arrangement keep in the "odd line" state of SWD[2:0] selection.  CFTYP = "1", Delta mode, Data arrangement controlled by SWD[2:0] setting.                                               |

### SWD[2:0] function control:

| SWD2  | SWD1 | SWD0 |      | Out  | out (n=0 t | o 319)    | Condition |

|-------|------|------|------|------|------------|-----------|-----------|

| 30002 | SWDI | 3000 | 3n+1 | 3n+2 | 3n+3       |           |           |

| 0     | 0    | 0    | R    | G    | В          | Odd Line  |           |

| U     | U    | U    | G    | В    | R          | Even Line |           |

| 0     | 0    | 4    | G    | В    | R          | Odd Line  |           |

| 0     | U    | '    | В    | R    | G          | Even Line |           |

| 0     | 1    | Х    | В    | R    | G          | Odd Line  | SHLR="1"  |

| 0     | '    | _ ^  | R    | G    | В          | Even Line | UPDN="1"  |

| 1     | 0    | 0    | G    | В    | R          | Odd Line  | OI DINE I |

| l     | U    | U    | R    | G    | В          | Even Line |           |

| 4     | 0    | 4    | В    | R    | G          | Odd Line  |           |

| '     | U    | '    | G    | В    | R          | Even Line |           |

| 1     | 1    | Х    | R    | G    | В          | Odd Line  |           |

|       | 1 2  | ^    | В    | R    | G          | Even Line |           |

Note 1: X = Don't care

URL:

Note 2: Data arrangement will keep in the "odd line" state when CFTYP = 0 for stripe mode.

**R02: Operation Control Register**

| Bit       | Name      | Initial | R/W        | Description                                                                                                                                                                                                                      |

|-----------|-----------|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7]   | SKIPMOD   | 0b      | (R)<br>R/W | Horizontal data processing algorithms select register.  SKIPMOD = "0": Horizontal data weighting skip mode. (Default mode)  SKIPMOD = "1": Horizontal data direct skip mode.                                                     |

| Bit [6:5] | HDNC[1:0] | 00b     | (R)<br>R/W | Horizontal Data scaling mode select register. This function is active under CCIR601 and CCIR656 mode only.                                                                                                                       |

| Bit [4]   | -         | 1       | -          | Reserve                                                                                                                                                                                                                          |

| Bit [3]   | FPOL      | 0b      | R/W        | VCOMOUT polarity inverse control.  FPOL = "0": VCOMOUT normal polarity (Default mode).  FPOL = "1": VCOMOUT inverse polarity.                                                                                                    |

| Bit [2]   | VSET      | 0b      | R/W        | Gamma correction source select.  VSET = "0", used internal Gamma Reference voltage (VDDA). (Default mode)  VSET = "1", used external Gamma Reference Input (V1~V7).                                                              |

| Bit [1]   | UPDN      | 1b      | (R)<br>R/W | Gate Driver Up/down scan control of gate driver.  UPDN = "0", Shift from down to up, First line=L240->L239->,,->L2->L1= Last line  UPDN = "1", Shift from up to down, First line=L1->L2->,,->239->240= Last line  (Default mode) |

| Bit [0]   | SHLR      | 1b      | (R)<br>R/W | Right/Left sequence control of source driver.  SHLR = "0", shift left: Last data = S1 < S2 < S3                                                                                                                                  |

HDNC[1:0] function setting for different horizontal data skip mode

| Tibro[1.0] function setting for unferent nonzontal data skip mode |       |                   |                                                                                                |  |  |  |  |  |  |  |

|-------------------------------------------------------------------|-------|-------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| HDNC1                                                             | HDNC0 | Source Data       | Data Skip Mode                                                                                 |  |  |  |  |  |  |  |

| 0                                                                 | 0     | 1440 / 1280 clock | 1440 clock -> 720 RGB -> (scale down) 320 RGB<br>1280 clock -> 640 RGB -> (scale down) 320 RGB |  |  |  |  |  |  |  |

| 0                                                                 | 1     | 1440 clock        | 1440 clock -> 720 RGB -> (Skip Right/Left 10 RGB) 700 RGB -> (scale down) 320 RGB              |  |  |  |  |  |  |  |

| 1                                                                 | 0     | 1440 clock        | 1440 clock -> 720 RGB -> (Skip Right/Left 20 RGB) 680 RGB -> (scale down) 320 RGB              |  |  |  |  |  |  |  |

| 1                                                                 | 1     | 1440 clock        | 1440 clock -> 720 RGB -> (Skip Right/Left 40 RGB) 640 RGB -> (scale down) 320 RGB              |  |  |  |  |  |  |  |

Note: HDNC function is active under CCIR601/656 mode only

www.topwaydisplay.com Document Name: LMT035KDH03-Rev04.DOC www.topwaysz.com Page: 14 of 23

R03: Input Data Format Control Register

| Bit       | Name           | Initial | R/W                       | Description                                                        |  |

|-----------|----------------|---------|---------------------------|--------------------------------------------------------------------|--|

|           |                |         |                           | DEN input pin polarity control.                                    |  |

| Bit [7]   | DENPOL         | 1b      | R/W                       | DENPOL = "0", DEN negative polarity.                               |  |

|           |                |         |                           | DENPOL = "1", DEN positive polarity. (Default mode)                |  |

|           |                |         |                           | CLKIN pin polarity control.                                        |  |

| Bit [6]   | CLKPOL         | 1b      | R/W                       | CLKPOL = "0", CLKIN negative edge latch data.                      |  |

|           |                |         |                           | CLKPOL = "1", CLKIN positive edge latch data. (Default mode)       |  |

|           | ] HSDPOL 0b R/ |         | HSD pin polarity control. |                                                                    |  |

| Bit [5]   |                | 0b      | R/W                       | HSDPOL = "0", HSD negative polarity. (Default mode)                |  |

|           |                |         |                           | HSDPOL = "1", HSD positive polarity.                               |  |

|           |                |         |                           | VSD pin polarity control.                                          |  |

| Bit [4]   | VSDPOL         | 0b      | R/W                       | VSDPOL = "0", VSD negative polarity. (Default mode)                |  |

|           |                |         |                           | VSDPOL = "1", VSD positive polarity                                |  |

| Dit [3:0] | SEI [3:0]      | 1100b   | o (R)<br>R/W              | Input data format selection.                                       |  |

| Bit [3:0] | SEL[3:0]       | 11000   |                           | Note: Different SEL [3:0] setting resolute in different AC timing. |  |

SEL[3:0]: Data input mode

| SEL3 | SEL2 | SEL1 | SEL0 | Data input format                                               | Operating frequency |

|------|------|------|------|-----------------------------------------------------------------|---------------------|

| 0    | 0    | 0    | 0    | CCIR601 YUV 1280 input format (YUV mode A)                      | 24.54 MHz           |

| 0    | 0    | 0    | 1    | CCIR601 YUV 1280 input format (YUV mode B)                      | 24.54 MHz           |

| 0    | 0    | 1    | 0    | CCIR601 YUV 1440 input format (YUV mode A)                      | 27 MHz              |

| 0    | 0    | 1    | 1    | CCIR601 YUV 1440 input format (YUV mode B)                      | 27 MHz              |

| 0    | 1    | 0    | 0    | CCIR656 YCbCr input format (YcbCr mode A)                       | 27 MHz              |

| 0    | 1    | 0    | 1    | CCIR656 YCbCr input format (YcbCr mode B)                       | 27 MHz              |

| 0    | 1    | 1    | 0    | -                                                               | -                   |

| 0    | 1    | 1    | 1    | -                                                               | -                   |

| 1    | 0    | 0    | 0    | 8-bit digital RGB input format HV Mode (NTSC only)              | 27 MHz              |

| 1    | 0    | 0    | 1    | 8-bit digital RGB input format DE Mode (NTSC only)              | 27 MHz              |

| 1    | 0    | 1    | 0    | 8-bit digital RGB through mode input format HV Mode (NTSC only) | 27 MHz              |

| 1    | 0    | 1    | 1    | 8-bit digital RGB through mode input format DE Mode (NTSC only) | 27 MHz              |

| 1    | 1    | 0    | 0    | 24-bit digital RGB input format HV Mode (NTSC only)             | 6.4 MHz             |

| 1    | 1    | 0    | 1    | 24-bit digital RGB input format DE Mode (NTSC only)             | 6.4 MHz             |

| 1    | 1    | 1    | 0    | -                                                               |                     |

| 1    | 1    | 1    | 1    | -                                                               |                     |

Note: Hsync and Vsync will be floated in CCIR656 and DE mode

Remark:

YUV mode A: Data sequence are "Cb\_Y\_Cr\_Y...". YUV mode B: Data sequence are "Cr\_Y\_Cb\_Y...".

RGB through mode will bypass 3-wire SWD[2:0] function;TCON will not arrange data color mapping.

**R04: Source Timing Delay Control Register**

| Bit       | Name      | Initial | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7:0] | DDLY[7:0] | 46h     | R/W | Select the HSD signal to 1'st input data delay timing Under CCIR601 mode, Ths = DDLY[7:0] + 128, (Unit = CLKIN) Under CCIR656 mode, Ths = DDLY[7:0] + 136, (Unit = CLKIN) Under RGB 8/24 bit mode, Ths = DDLY[7:0], (Unit = CLKIN) The register value will be update to the different default value each time when SEL[3:0] changed. Read the section of "Timing Table" for the detail, please. |

Note: DDLY function will be disabled under 8/24bit DE mode and PINCTLB = 0 condition. The default value list in the timing table will be used when PINCTLB = 0.

**R05: Gate Timing Delay Control Register**

| Bit       | Name      | Initial | R/W | Description                                                                                                                                                                                                                                |

|-----------|-----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7]   | -         | -       | -   | Reserve                                                                                                                                                                                                                                    |

| Bit [6:0] | HDLY[6:0] | 0Dh     | R/W | Select the Gate start pulse output delay timing Tvs = HDLY[6:0], (Unit = HSD) The register value will be update to the different default value each time when SEL[3:0] changed. Read the section of "Timing Table" for the detail, please. |

Note: HDLY function will be disabled under 8/24bit DE mode and PINCTLB = 0 condition. The default value list in the timing table will be used when PINCTLB = 0.

#### R06: Reserved

| 11001110001100 |           |      |         |     |             |  |  |  |

|----------------|-----------|------|---------|-----|-------------|--|--|--|

|                | Bit       | Name | Initial | R/W | Description |  |  |  |

|                | Bit [7:0] | -    | -       | -   | Reserve     |  |  |  |

URL: <a href="https://www.topwaydisplay.com">www.topwaydisplay.com</a>

Document Name: LMT035KDH03-Rev04.DOC

www.topwaysz.com

Page: 15 of 23

**R07: Internal Function Control Register**

| Bit       | Name       | Initial | R/W        | Description                                                                                                                                                                                       |

|-----------|------------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7:6] | FRAD[1:0]  | 00b     | R/W        | Odd frame or Even frame advance control                                                                                                                                                           |

| Bit [5:4] | INVSL[1:0] | 00b     | R/W        | Source Driving Mode Selection Register                                                                                                                                                            |

| Bit [3]   | PAL        | 0b      | (R)<br>R/W | NTSC or PAL mode selection. Only for 601 and 656 mode. PAL = "0", Select NTSC interface mode. (Default mode) PAL = "1", Select PAL interface mode.                                                |

| Bit [2]   | PALM       | 0b      | (R)<br>R/W | PAL mode input data format selection PALM = "0", Select PAL 280 line mode. (Default mode) PALM = "1", Select PAL 288 line mode                                                                    |

| Bit [1]   | -          | -       | -          | Reserve                                                                                                                                                                                           |

| Bit [0]   | AVGY       | 0b      | R/W        | Average YUV interface Luminance Y.  AVGY = "0"; Only used odd Y sample for YUV conversion,  AVGY = "1"; Used odd and even Y sample for YUV conversion.  This function active under YUV mode only! |

INVSL[1:0]

| INVSL1 | INVSL0 | Driving Mode       | Notes   |

|--------|--------|--------------------|---------|

| 0      | 0      | 1 - Line Inversion | Default |

| 0      | 1      | 2 - Line Inversion |         |

| 1      | 0      | Frame Inversion    |         |

| 1      | 1      | Reserved           |         |

FRAD[1:0]

| FRAD1 | FRAD0 | Advance Frame | Notes                             |         |

|-------|-------|---------------|-----------------------------------|---------|

| 0     | 0     | Default       | Odd/Even frame Tstv are the same  |         |

| 0     | 1     | Odd frame     | Even frame Tstv = HDLY setting +1 | Unit: H |

| 1     | 0     | Even frame    | ODD frame Tstv = HDLY setting +1  |         |

| 1     | 1     | Reserve       | Reserve                           |         |

Note: Remark: This function is available under CCIR601 and CCIR656 mode only.

**R08: Contrast Control Register**

| Bit       | Name     | Initial | R/W | Description                                                                                                                                      |

|-----------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7:5] | -        | -       | -   | Reserve                                                                                                                                          |

| Bit [4:0] | CON[4:0] | 08h     | R/W | Display Contrast level adjustment register. (0.125/Step) Adjust range from 0x00(level = 0) to 0x1F(level = 3.875) Default value 08h(level = 1.0) |

**R09: Brightness Control Register**

| Bit       | Name     | Initial | R/W | Description                                                                                                                                      |

|-----------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7]   | -        | -       | -   | Reserve                                                                                                                                          |

| Bit [6:0] | BRI[6:0] | 40h     | R/W | Display Brightness level adjustment register. (2/Step) Adjust range from 0x00(level = -128) to 0x7F(level = +126) Default value 0x40(level = +0) |

**R0A: Hue and Saturation Control Register**

| Bit       | Name     | Initial | R/W | Description                                                                                                                                                                                                                                    |  |

|-----------|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit [7:4] | HUE[3:0] | 08h     | R/W | YUV Hue level adjustment register. (5 Deg/Step) Adjust range from 0x00(level = -40 Deg) to 0x0F(level = +35 Deg) Default value 0x08(level = 0 Deg) Cb' = Cb * $\cos \theta$ + Cr * $\sin \theta$ Cr' = Cr * $\cos \theta$ + Cb * $\sin \theta$ |  |

| Bit [3:0] | SAT[3:0] | 08h     | R/W | YUV saturation level adjustment register. (0.125/Step) Adjust range from 0x00(level = 0) to 0x0F(level = 1.875) Default value 0x08(level = 1.00)                                                                                               |  |

Note: Hue and Saturation function was available under YUV input mode only.

www.topwaydisplay.com Document Name: LMT035KDH03-Rev04.DOC www.topwaysz.com Page: 16 of 23

R0B: R / B Sub-Contrast Control Register

| Bit       | Name       | Initial | R/W | Description                                                     |  |

|-----------|------------|---------|-----|-----------------------------------------------------------------|--|

|           |            |         |     | B Data Contrast level adjustment register. (0.125/Step)         |  |

| Bit [7:6] | SCONB[1:0] | 02h     | R/W | Adjust range from 0x00(level = 0.75) to 0x0F(level = 1.125)     |  |

|           |            |         |     | Default value 08h(level = 1.0)                                  |  |

|           |            |         |     | R Data Contrast level adjustment register. (0.125/Step)         |  |

| Bit [3:2] | SCONR[1:0] | 02h     | R/W | Adjust range from $0x00(level = 0.75)$ to $0x0F(level = 1.125)$ |  |

|           |            |         |     | Default value 08h(level = 1.0)                                  |  |

R0C: R Sub-Brightness Control Register

| Bit       | Name       | Initial | R/W | Description                                                                                                                                 |

|-----------|------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| Bit [7:6] | -          | -       | -   | Reserve                                                                                                                                     |

| Bit [5:0] | SBRIR[5:0] | 20h     | R/W | R Data Brightness level adjustment register. (1/Step) Adjust range from 0x00(level = -32) to 0x3F(level = +31) Default value 20h(level = 0) |

R0D: B Sub-Brightness Control Register

| Bit        | Name       | Initial | R/W                   | Description                                                                                                                                 |  |

|------------|------------|---------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit [7:6]  | =          | -       | -                     | Reserve                                                                                                                                     |  |

| Di+ [E :0] | ODDIDIE:01 | 00h     |                       | B Data Brightness level adjustment register. (1/Step) Adjust range from 0x00(level = -32) to 0x3F(level = +31) Default value 20h(level = 0) |  |

| Bit [5:0]  | SBRIB[5:0] | 20h     | <b>□</b> / <b>V V</b> |                                                                                                                                             |  |

**R0E: VCOMDC Level Control Register**

| Bit       | Name            | Initial | R/W | Description                                                                                                                                                                                                                                                                                             |  |

|-----------|-----------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit [7]   | -               | -       | -   | Reserve                                                                                                                                                                                                                                                                                                 |  |

| Bit [6]   | OTP_BYPS        | 0h      | R/W | VCDCSL[5:0] data source selection register OTP_BYPS ="0", VCDCSL[5:0] is read from OTP memory. OTP_BYPS ="1", VCDCSL[5:0] is switch to the 3-wire register memory when user want to adjust the VCOMDC level for test propose. Refer to the "TRMEN" control register for the proper OTP write operation. |  |

| Bit [5:0] | VCDCSL<br>[5:0] | 10h     | R/W | VCOMDC level control register (20mV/Step @ VDDA = 5.0V) VCDCSL[5:0] = 00h, VCOMDC = 1.00V VCDCSL[5:0] = 01h, VCOMDC = 1.02V VCDCSL[5:0] = 10h, VCOMDC = 1.32V VCDCSL[5:0] = 3eh, VCOMDC = 2.24V VCDCSL[5:0] = 3fh, VCOMDC = 2.26V                                                                       |  |

Note: .VCOMDC always keep 1.7V When VPSW = "1". The OTP value effect in VPSW=0.

Document Name: LMT035KDH03-Rev04.DOC www.topwaydisplay.com www.topwaysz.com Page: 17 of 23

**R0F VCOMAC Level Control Register**

| Bit       | Name      | Initial | R/W    | Description                              |

|-----------|-----------|---------|--------|------------------------------------------|

| Bit [7:6] | VGLSL     | 10      | R/W    | VGLSL level control register             |

| Ы: [7.0]  | VGLSL     | 10      | TV VV  | VGLSL Level = 1V / Step                  |

| Bit [5:4] | VGHSL     | 10      | R/W    | VGHSL level control register             |

| ы [5.4]   | VGHSL     | 10      | IT/ VV | VGHSL Level = 1V / Step                  |

| Bit [3:0] | VCACSL[3: | 0100    | R/W    | VCOMAC level control register            |

| Dit [3.0] | 0]        | 0100    | IT/ VV | VCOMAC Level = 0.1V / Step @ VDDA = 5.0V |

**VCACSL** [3:0]

| VCSL3 | VCSL2 | VCSL1 | VCSL0 | Level (V)     |

|-------|-------|-------|-------|---------------|

| 0     | 0     | 0     | 0     | 4.6           |

| 0     | 0     | 0     | 1     | 4.7           |

| 0     | 0     | 1     | 0     | 4.8           |

| 0     | 0     | 1     | 1     | 4.9           |

| 0     | 1     | 0     | 0     | 5.0 (Default) |

| 0     | 1     | 0     | 1     | 5.1           |

| 0     | 1     | 1     | 0     | 5.2           |

| 0     | 1     | 1     | 1     | 5.3           |

| 1     | 0     | 0     | 0     | 5.4           |

| 1     | 0     | 0     | 1     | 5.5           |

| 1     | 0     | 1     | 0     | 5.6           |

| 1     | 0     | 1     | 1     | 5.7           |

| 1     | 1     | 0     | 0     | 5.8           |

| 1     | 1     | 0     | 1     | 5.9           |

| 1     | 1     | 1     | 0     | 6.0           |

| 1     | 1     | 1     | 1     | 6.1           |

Note: When VPSW = "1". The register can't be used

VGHSL[5:4]

| VGHSL1 | VGHSL0 | VGH(V) |

|--------|--------|--------|

| 0      | 0      | 12     |

| 0      | 1      | 13     |

| 1      | 1      | 14     |

| 1      | 0      | 15     |

When VPSW = "1" .The register can't be used

| ۷G | LSL | [7: | 6] |

|----|-----|-----|----|

|    |     |     |    |

| VGLSL1 | VGLSL0 | VGL(V) |

|--------|--------|--------|

| 0      | 0      | -7     |

| 0      | 1      | -8     |

| 1      | 1      | -9     |

| 1      | 0      | -10    |

When VPSW = "1" .The register can't be used

R10: VGAM2 Level Control Register

| Bit       | Name           | Initial  | R/W    | Description                                                                                                                                                            |  |  |  |

|-----------|----------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dit       | Hame           | militiai | 11/ 44 | Description                                                                                                                                                            |  |  |  |

| Bit [7:5] | -              | -        | -      | Reserve                                                                                                                                                                |  |  |  |

| Bit [4]   | GAMEN          | 0b       |        | GAMMA adjustment enable control register.(adjustable voltage for V2-V6) GAEN="0" or VSET = 1, Gamma correction disabled. GAEN="1" & VSET="0", Gamma correction enabled |  |  |  |

| Bit [3]   | -              | -        | -      | Reserve                                                                                                                                                                |  |  |  |

| Bit [2:0] | V2GAM<br>[2:0] | 100b     | R/W    | V2 GAMMA voltage level setting. Function enabled when VSET="0" Adjust level = 22mV / Step                                                                              |  |  |  |

R11: VGAM3/4 Level Control Register

| Bit       | Name                  | Initial | R/W         | Description                                                                               |  |  |

|-----------|-----------------------|---------|-------------|-------------------------------------------------------------------------------------------|--|--|

| Bit [7:6] | -                     | -       | -           | Reserve                                                                                   |  |  |

| Bit [5:3] | V4GAM<br>[2:0]        | 100b    | I H/VV      | V4 GAMMA voltage level setting. Function enabled when VSET="0" Adjust level = 22mV / Step |  |  |

| Bit [2:0] | BILLYOL   TOON   B/W/ |         | I H / / / / | '3 GAMMA voltage level setting. Function enabled when VSET="0" djust level = 22mV / Step  |  |  |

www.topwaydisplay.com Document Name: LMT035KDH03-Rev04.DOC www.topwaysz.com Page: 18 of 23

R12: VGAM5/6 Level Control Register

| Bit        | Name           | Initial | R/W    | Description                                                                               |  |

|------------|----------------|---------|--------|-------------------------------------------------------------------------------------------|--|

| Bit [10:6] | -              | -       | -      | Reserve                                                                                   |  |

| Bit [5:3]  | V6GAM<br>[2:0] | 100b    | I B/VV | V6 GAMMA voltage level setting. Function enabled when VSET="0" Adjust level = 22mV / Step |  |

| Bit [2:0]  |                |         |        | V5 GAMMA voltage level setting. Function enabled when VSET="0" Adjust level = 22mV / Step |  |

V2GAM/ V3GAM/ V4GAM/ V5GAM./ V6GAM Level Control Register Setting Table

| VxGMA2 | VxGMA1 | VxGMA0 | Voltage level | Unit | Note                                                           |  |