# **150-mW STEREO AUDIO POWER AMPLIFIER**

## General Description

LN4812 is a differential input stereo audio power amplifier circuit for mobile phones and other portable audio devices built-in speaker. It provides a stable output power of 150mW 16 $\Omega$  loads.

The shutdown current of the LN4812 is less than 100nA, that can save energy for the system. At the same time the amplifier gain can be set by external resistors, that it is easy to use.

The LN4812 using small MSOP-10 package, to facilitate high-density mounting .

## Applications

- Mobile Phones

- PDA

- Bluetooth headset

## Key Specifications

- 150mW Stereo Output

- Differential Inputs

- Ordering Information

- shutdown current is less than 0.1uA

- Built-in " wave " sound canceling circuit

- Wide input voltage range : 2.2V-5.0V

#### Package

MSOP-10

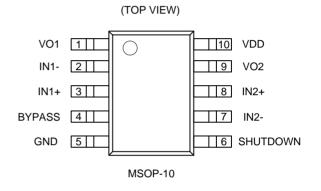

## Pin Configuration

| Ordering Number | Package |  |  |

|-----------------|---------|--|--|

| LN4812SR        | MSOP-10 |  |  |

#### Pin Function Description

| Pin Number | Pin Name | Function Description                            |  |

|------------|----------|-------------------------------------------------|--|

| 1          | VO1      | VO1 is the audio output for channel 1.          |  |

| 2          | IN1-     | IN1- is the negative input for channel 1.       |  |

| 3          | IN1+     | IN1+is the positive input for channel 1.        |  |

| 4          | BYPASS   | Bypass Capacitance Input Pin                    |  |

| 5          | GND      | GND is the ground connection.                   |  |

| 6          | SHUTDOWN | Puts the device in a low quiescent current mode |  |

|            |          | when held high.                                 |  |

| 7          | IN2+     | IN2+ is the positive input for channel 2.       |  |

| 8          | IN2-     | IN2- is the negative input for channel 2.       |  |

| 9          | VO2      | VO2 is the audio output for channel 2.          |  |

| 10         | VDD      | VDD is the supply voltage terminal.             |  |

# Marking Rule

MSOP-10

The second behavior wafer version

The third production information behavior

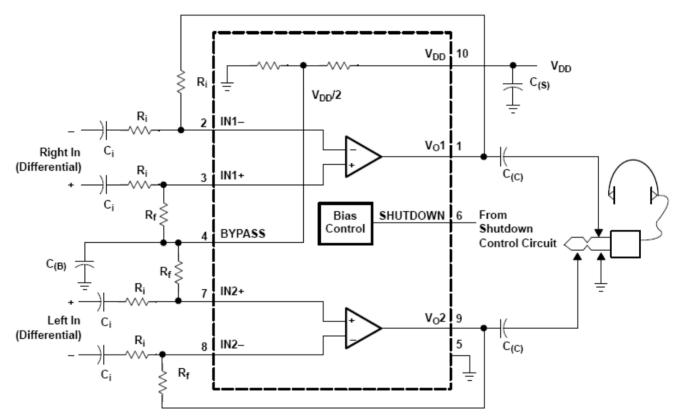

## Typical Application Circuit

## Absolute Maximum Ratings

| Parameter                      | Symbol | Value        | Unit |

|--------------------------------|--------|--------------|------|

| Supply Voltage                 | VDD    | -0.3—5.0     | V    |

| Input Voltage                  | VIN    | -0.3—VDD+0.3 | V    |

| Operating Free-air Temperature | Topr   | -40—85       | °C   |

| Storage Temperature Range      | Tstg   | -65—150      | °C   |

| ESD (HBM)                      | -      | 4000         | V    |

## **Electrical Characteristics**

| VDD=5V            | (Unless otherwise specified. Limits apply for TA = 25°C.) |                                                           |     |      |     |      |

|-------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----|------|-----|------|

| Parameter         | Symbol                                                    | Condition                                                 | Min | Тур  | Max | Unit |

| I <sub>DD</sub>   | Supply Current                                            |                                                           | _   | 1.5  | 3   | mA   |

| I <sub>SD</sub>   | Supply Current in SHUTDOWN<br>Mode                        | Vshutdown=5V                                              | _   |      | 0.1 | μA   |

| V <sub>SDIH</sub> | Shutdown Voltage<br>Input High                            |                                                           | 1.2 | _    | _   | V    |

| V <sub>SDIL</sub> | Shutdown Voltage<br>Input Low                             |                                                           |     | _    | 0.4 | V    |

| V <sub>OS</sub>   | Output Offset Voltage                                     | AV=2V/V                                                   | _   |      | 15  | mV   |

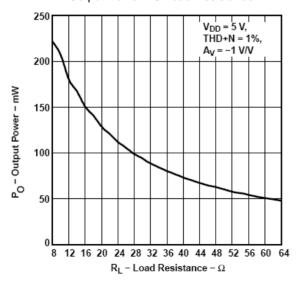

| Po                | Output Power (each channel)                               | THD = 1% (max); f = 1 kHz<br>16Ω Load                     |     | 150  |     | mW   |

| T <sub>WU</sub>   | Wake-up time                                              |                                                           |     | 170  | 220 | ms   |

| T <sub>SD</sub>   | Thermal Shutdown Temperature                              |                                                           | 150 | 170  | 190 | °C   |

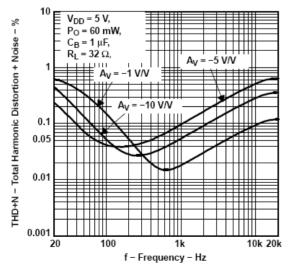

| THD+N             | Total harmonic distortion + noise                         | Po = 100mWrms;<br>20-20KHz                                | _   | 0.06 | _   | %    |

| Bom               | Maximum Output Power BW                                   | G=10,THD<5%                                               | 20  |      |     | KHz  |

| PSRR              | Supply Current                                            | V <sub>ripple</sub> = 200mV <sub>sine p-p</sub><br>f=1kHz | 55  | 60   | _   | dB   |

| PCS               | Channel Isolation                                         | 1KHz                                                      |     | 90   |     | dB   |

| T <sub>SDT</sub>  | Shut Down Time                                            | 16Ω Load                                                  |     | 1.0  | —   | ms   |

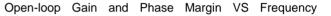

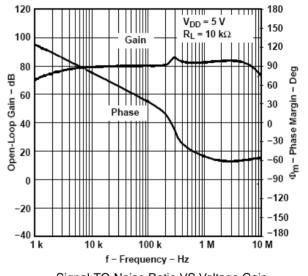

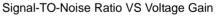

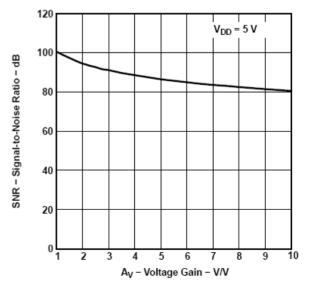

#### **Typical Performance Characteristics**

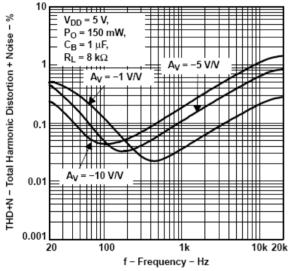

Total Harmonic Distortion + Noise VS Frequency

10 THD+N – Total Harmonic Distortion + Noise – %  $A_{V} = -1 V/V$ , 20 Hz C<sub>B</sub> = 1 μF 20 kHz 0.1 1 kHz 0.01 П 0.001 10 100 500 Po - Output Power - mW

Total Harmonic Distortion + Noise VS Output Power

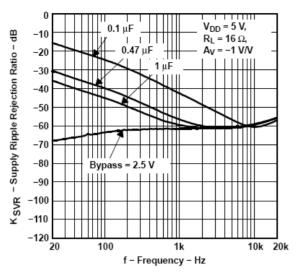

#### Supply Ripple Rejection Ratio VS Frequency

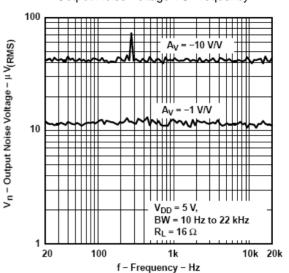

**Output Noise Voltage VS Frequency**

LN4812

## Application Information

• Gain Setting Resistors

The gain for the LN4812 is set by resistors Rf and Ri according to GAIN= - (Rf/Ri), and Ri is usually selected for resistance 5K-20K.

When Rf> 50K, recommended to use metal film resistors, so that we can get better performance. Meanwhile, in order to prevent system instability, it is recommended Rf in parallel with a capacitor Cf, to forming a low -pass filter network together with Rf, and the cutoff frequency of the low pass filter is fc = 1 /  $(2\pi$ RfCf).

For example, if Rf is 100 k $\Omega$  and CF is 5 pF then fc(lowpass) is 318kHz, which is well outside the audio range.

• Input Capacitor, Ci

Input resistance Ri and the input capacitance Ci form a high -pass filter. Fc(highpass)= fc=1/( $2\pi$ RiCi). The value of Ci directly affects the bass (low fre-quency) performance of the circuit. Consider the example where Ri is 10k $\Omega$  and the specification calls for a flat bass response down to 20Hz, and Ci is 1uF.

ESR additional parasitic capacitance of the resistor will affect the audio signal, so we recommend using a low ESR ceramic capacitor.

• Power Coupling Capacitor C(s)

For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F, placed as close as possible to the device VDD lead, works best. For filtering lower-frequency noise signals, a larger aluminum

• BYPASS Capacitor C<sub>(B)</sub>

BYPASS circuit is a voltage divider network through an internal resistor to achieve, and the internal resistor is designed to in series 100K. To get a good job is usually the characteristics required to meet the CB \* 100K> RiCi.

For example, Ri = 10K, Ci = 1uF, the CB value preferably greater than 0.1uF, 1uF select more suggestions

• Output Coupling Capacitors C<sub>(C)</sub>

In atypical single-supply, single-ended(SE) configuration, an output coupling capacitor ( $C_{(C)}$ ) is required to block the dc bias at the output of the amplifier, thus preventing dc currents in the load. As with the input coupling capacitor, the output coupling capacitor and impedance of the load form a high-pass filter Fc=1/( $2\pi$ RLCc).

The main disadvantage, from a performance stand-point, is that the typically-small load impedance drives the low-frequency corner higher. Large values of  $C_{(C)}$  are required to pass low frequencies into the load. The output coupling capacitor required in single-supply SE mode also places additional constraints on the selection of other components in the amplifier circuit. With the rules described earlier still valid, add the following relationship:  $C_B*100K>RiCi>>RLC_C$ .

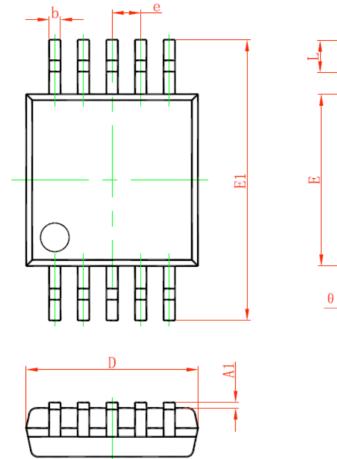

## Package Information

• MSOP-10

| Querch et l | Dimensions In Millimeters |        | Dimensions In Inches |        |  |

|-------------|---------------------------|--------|----------------------|--------|--|

| Symbol      | Min                       | Max    | Min                  | Max    |  |

| A           | 0.820                     | 1. 100 | 0.032                | 0.043  |  |

| A1          | 0. 020                    | 0. 150 | 0.001                | 0.006  |  |

| A2          | 0.750                     | 0.950  | 0.030                | 0.037  |  |

| b           | 0. 180                    | 0. 280 | 0.007                | 0.011  |  |

| с           | 0.090                     | 0. 230 | 0.004                | 0.009  |  |

| D           | 2.900                     | 3. 100 | 0.114                | 0. 122 |  |

| е           | 0.50(BSC)                 |        | 0.020(BSC)           |        |  |

| E           | 2.900                     | 3. 100 | 0.114                | 0. 122 |  |

| E1          | 4. 750                    | 5.050  | 0. 187               | 0. 199 |  |

| L           | 0. 400                    | 0. 800 | 0.016                | 0. 031 |  |

| θ           | 0°                        | 6°     | 0°                   | 6°     |  |