### LP5551

# PowerWise<sup>™</sup> Technology Compliant Energy Management Unit

### **General Description**

The LP5551 is a PWI 1.0 compliant Energy Management System for reducing power consumption of stand-alone mobile phone processors such as base-band or applications processors.

The LP5551 contains two advanced, digitally controlled switching regulators for supplying variable voltage to processor core and memory. Two regulators provide P- and N- well biasing for threshold scaling applications. The device also integrates 4 programmable LDO-regulators for powering I/O, PLLs and maintaining memory retention in shutdown-mode.

The device is controlled via the PWI open-standard interface. The LP5551 operates cooperatively with PowerWise™ technology compatible processors to optimize supply voltages adaptively over process and temperature variations or dynamically using frequency/voltage pre-characterized look-up tables and provides P- and N-well biasing for threshold scaling.

### **Features**

- 2 300 mA buck regulators operate 180 degrees out of phase for reduced EMI

- 1 MHz PWM switching frequency

- 4 programmable LDOs ideal for I/O (two of these), PLL, and memory retention supply generation.

- Supports high-efficiency PowerWise Technology Adaptive Voltage Scaling

- PWI open standard interface for system power management

- Digitally controlled intelligent voltage scaling

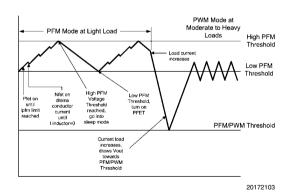

- Auto or PWI controlled PFM mode transition

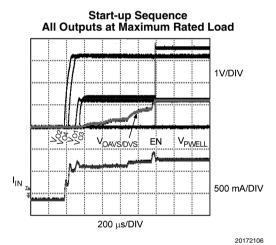

- Internal soft start/startup sequencing.

- Adjustable P- and N- well bias supply for threshold scaling

- Power OK output.

### **Applications**

- Dual core processors

- GSM/GPRS/EDGE & UMTS cellular handsets

- Hand-held radios

- PDAs

- Battery powered devices

- Portable instruments

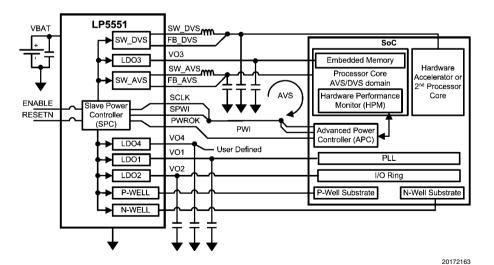

## **System Diagram**

FIGURE 1. System Diagram

www.DataSheet4U.com

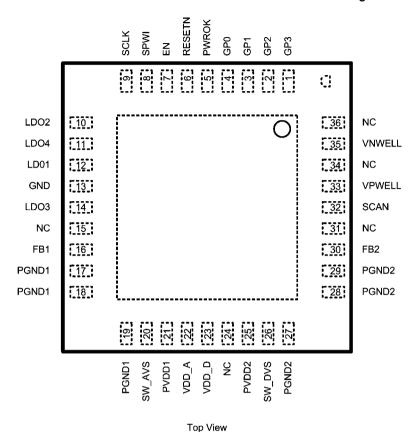

## **Connection Diagrams and Package Mark Information**

36 - Pin LLP

**NS Package Number SQA36A**

20172102

FIGURE 2. LP5551 Pinout

Package Mark

2017214

Note: The actual physical placement of the package marking will vary from part to part.

FIGURE 3. Top View

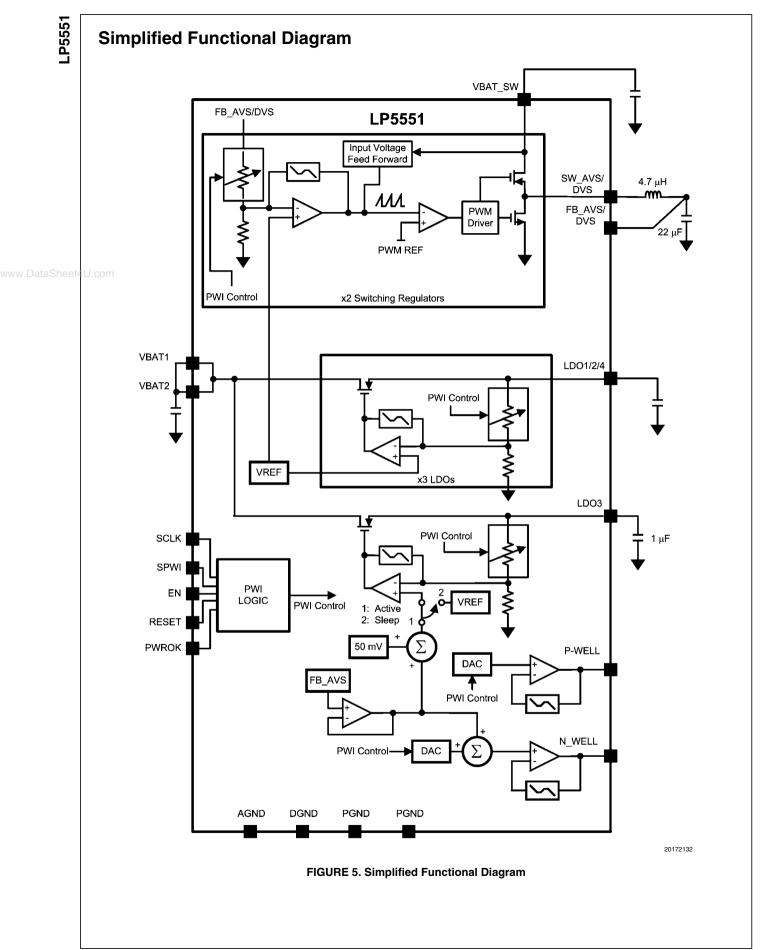

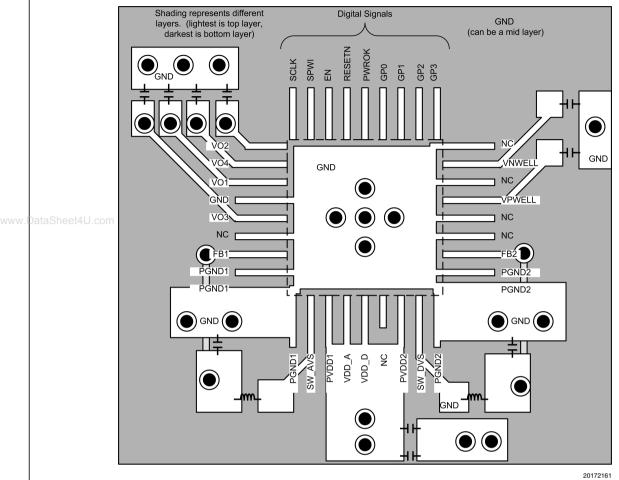

#### **Typical Application** Advanced System Power Controller Connect Die Attach Pad Controller (DAP) to GND DAP 8 6 5 3 SCLK **PWROK** GPO1 GPO3 ΕN SPWI RESETN GPO0 GPO2 1.5 - 3.3V 10 LDO2 NC 36 250 mA O 4.7 μF **1** -0.3 - +1.0V offset 1.5 - 3.3V 250 mA 11 LDO4 VNWELL 35 • (w.r.t. AVS) 10 uA 4.7 μF 2.2V - لم 100 mA NC 34 **12** LD01 -1 - +0.3V offset 13 NC VPWELL 33 (w.r.t. GND) LP5551 10 uA 0.6 - 1.35V 25 mA 14 LDO3 SCAN 32 **LLP-36** 1.0 μF 15 NC NC 31 FB2 30 **16** FB1 PGND2 29 **17** PGND1 PGND2 28 **18** PGND1 SW\_AVS VDD\_A SW\_DVS PVDD1 VDD\_D PVDD2 PGND1 PGND2 23 22 μF 22 μF AVS DVS Supply o Supply 0.6V - 1.2V 0.6V - 1.2V 4.7 μΗ $4.7~\mu\text{H}$ 300 mA 300 mA VIN **⋢** 0.1 μF 0.1 μF 22 μF 0.1 μF 2.7V - 5.5 V 20172130

FIGURE 4. Typical Application Circuit

## **Pin Descriptions**

| Pin # | Name  | I/O | Туре | Description                         |

|-------|-------|-----|------|-------------------------------------|

| 0     | DAP   | G   | G    | Connect Die Attach Pad to ground    |

| 1     | GP3   | 0   | D    | General purpose output pin          |

| 2     | GP2   | 0   | D    | General purpose output pin          |

| 3     | GP1   | 0   | D    | General purpose output pin          |

| 4     | GP0   | 0   | D    | General purpose output pin          |

| 5     | PWROK | 0   | D    | Power OK, active high output signal |

Pin #

Name

RESETN

I/O

Туре

D

Description

Reset, active low

N-well bias voltage

|               |        | _  |        | •   | _ | . 10001, 401.10 1011                                                |

|---------------|--------|----|--------|-----|---|---------------------------------------------------------------------|

| _             |        | 7  | EN     | I   | D | Enable, active high                                                 |

|               |        | 8  | SPWI   | I/O | D | PowerWise Interface (PWI) bi-directional data                       |

|               |        | 9  | SCLK   | I   | D | PowerWise Interface (PWI) clock input                               |

|               |        | 10 | LDO2   | Р   | Р | LDO2 output, for supplying the I/O voltage on the SoC               |

|               |        | 11 | LDO4   | Р   | Р | LDO4 output, for supplying a fixed voltage to a PLL etc. on the SoC |

|               |        | 12 | LDO1   | Р   | Р | LDO1 output, user defined                                           |

|               |        | 13 | NC     |     |   |                                                                     |

|               |        | 14 | LDO3   | Р   | Р | LDO3 output, on-chip memory supply voltage                          |

|               |        | 15 | NC     |     |   |                                                                     |

|               |        | 16 | FB1    | Р   | Р | AVS switcher feedback                                               |

|               |        | 17 | PGND1  | G   | G | Power ground for the AVS switcher                                   |

| www.DataSheet | ll I c | 18 | PGND1  | G   | G | Power ground for the AVS switcher                                   |

| www.bataoneer | .0.0   | 19 | PGND1  | G   | G | Power ground for the AVS switcher                                   |

|               |        | 20 | SW1    | Р   | Р | AVS Switcher switch node; connected to inductor                     |

|               |        | 21 | PVDD1  | Р   | Р | Battery supply voltage for the AVS switcher                         |

|               |        | 22 | VDD_D  | Р   | Р | Battery supply voltage for digital                                  |

|               |        | 23 | VDD_A  | Р   | Р | Battery supply voltage for analog                                   |

|               |        | 24 | NC     |     |   |                                                                     |

|               |        | 25 | PVDD2  | Р   | Р | Battery supply voltage for the DVS switcher                         |

|               |        | 26 | SW2    | Р   | Р | DVS Switcher switch node; connected to inductor                     |

|               |        | 27 | PGND2  | G   | G | Power ground for the DVS switcher                                   |

|               |        | 28 | PGND2  | G   | G | Power ground for the DVS switcher                                   |

|               |        | 29 | PGND2  | G   | G | Power ground for the DVS switcher                                   |

|               |        | 30 | FB2    | Р   | Р | DVS switcher feedback                                               |

|               |        | 31 | NC     |     |   |                                                                     |

|               |        | 32 | SCAN   |     |   |                                                                     |

|               |        | 33 | VPWELL | Р   | Р | P-well bias voltage                                                 |

|               |        | 34 | NC     |     |   |                                                                     |

|               |        |    |        |     |   |                                                                     |

A: Analog Pin

35

36

VNWELL

NC

D: Digital Pin

I: Input Pin

O: Output Pin

I/O: Input/Output Pin

P: Power Pin

G: Ground Pin

## **Ordering Information**

| Voltage Option | Order Number | Package Marking | Supplied As               |

|----------------|--------------|-----------------|---------------------------|

|                | LP5551SQ     | LP5551SQ        | 1000 units, Tape-and-Reel |

|                | LP5551SQX    | LP5551SQ        | 4500 units, Tape-and-Reel |

$<sup>^*</sup>$ Released. Samples available.

(Note 4)

### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

VDD\_A, VDD\_D, PVDD1, and

-0.3 to +6.0V

PVDD2

LDO1, LDO2, LDO3, LDO4, -0.3 to VDD\_A + 0.3V

VNWELL to GND, VPwell, ENABLE, RESETN, FB1, FB2, SW\_AVS, SW\_DVS,GP0, GP1, GP2, and GP3

-0.3 to VDD\_D + 0.3V SPWI, SCLK, PWROK GND, PGND1, PGND2, to GND ±0.3V

SLUG

Junction Temperature (TJ-MAX) Storage Temperature Range

150°C -65°C to 150°C

Maximum Continuous Power Dissipation (PD-MAX) (Note 5) TBD W

Maximum Lead Temperature

(Soldering) ESD Rating (Note 3)

Human Body Model:

All pins

2.0kV

### Operating Ratings (Notes 1, 2)

VDD\_A, VDD\_D, PVDD1, and PVDD2 2.7 V to 5.5 V Junction Temperature (T<sub>I</sub>) Range -40°C to +125°C Ambient Temperature (T<sub>△</sub>) Range(Note -40°C to +85°C

### Thermal Properties (Note 6)

Junction-to-Ambient Thermal 39.8°C/W

Resistance  $(\theta_{IA})$

3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8, 9)

| Symbol          | Parameter                             | Conditions                                                                                                                                                                                               | Min | Тур  | Max | Units |

|-----------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

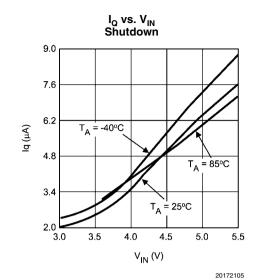

| I <sub>Q</sub>  | Shutdown Supply current               | $V_{DD\_A,\_D}$ , $P_{VDD1,2} = 3.6 \text{ V}$ , all circuits off.                                                                                                                                       |     | 0.44 | 4   | μА    |

|                 |                                       | $-40^{\circ}\text{C} \leq \text{TJ} \leq 125^{\circ}\text{C}$ $V_{\text{DD\_A, \_D}}, P_{\text{VDD1,2}} = 3.6 \text{ V, all circuits}$ off. $-40^{\circ}\text{C} \leq \text{TJ} \leq 85^{\circ}\text{C}$ |     | 1    | 12  | μΑ    |

|                 | Sleep State Supply Current            | V <sub>DD_A, _D</sub> , V <sub>PVDD1,2</sub> = 3.6 V, LDO3 on, LDO2 on (no load). All other circuits off.                                                                                                |     | 135  | 186 | μΑ    |

|                 | Acitve State Supply Current           | V <sub>DD_A, _D</sub> , V <sub>PVDD1,2</sub> = 3.6 V, all outputs on, no load                                                                                                                            |     | 431  | 742 | μΑ    |

| UVLO high       | Under Voltage Lockout, high threshold |                                                                                                                                                                                                          |     |      | 2.7 |       |

| UVLO low        | Under Voltage Lockout, low threshold  |                                                                                                                                                                                                          | 2.5 |      |     |       |

| T <sub>SD</sub> | Thermal Shutdown Threshold            |                                                                                                                                                                                                          |     | 160  |     | °C    |

|                 | Thermal Shutdown Hysteresis           |                                                                                                                                                                                                          |     | 10   |     |       |

LDO1 (PLL/Fixed Voltage) Characteristics Unless otherwise noted, V<sub>DD A. D</sub>, V<sub>PVDD1.2</sub> RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                 | Parameter                   | Conditions                                                                   | Min   | Тур | Max  | Units |

|------------------------|-----------------------------|------------------------------------------------------------------------------|-------|-----|------|-------|

| V <sub>OUT</sub>       | Output Voltage              | I <sub>OUT</sub> = 50 mA,                                                    | -3.5% | 1.2 | 3.1% | V     |

| Accuracy               |                             | V <sub>OUT</sub> = 1.2 V,                                                    |       |     |      |       |

|                        |                             | $2.7 \text{ V} \le \text{V}_{DD A. D}, \text{V}_{PVDD1.2} \le 5.5 \text{ V}$ |       |     |      |       |

| V <sub>OUT</sub> Range | Programmable Output Voltage | Programming Resolution=100 mV                                                | 0.7   | 1.2 | 2.2  | V     |

|                        | Range                       |                                                                              |       |     |      |       |

| I <sub>OUT</sub>       | Rated Output Current        | 2.7 V ≤ V <sub>DD_A, _D</sub> ,P <sub>VDD1,2</sub> ≤ 5.5 V                   | 0     |     | 100  | mA    |

|                        | Output Current Limit        | V <sub>OUT</sub> = 0 V                                                       |       |     | 347  |       |

| I <sub>Q</sub>         | Quiescent Current           | I <sub>OUT</sub> = 0 mA(Note 11)                                             |       | 35  |      | μΑ    |

www.DataSheet4

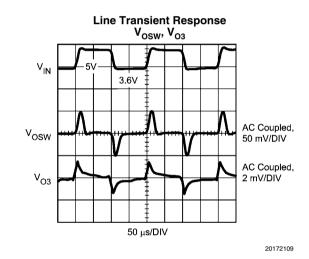

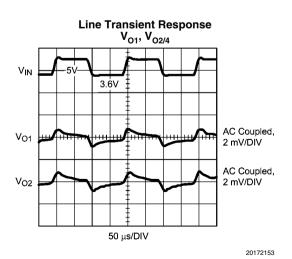

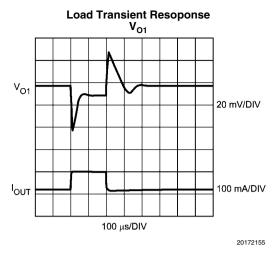

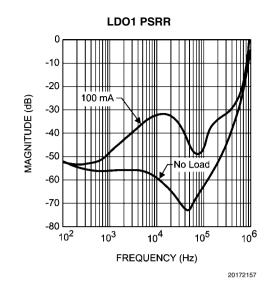

Symbol **Parameter** Conditions Min Тур Max Units Line Regulation  $\Delta V_{OUT}$ -0.083 0.316 %/V  $2.7 \text{ V} \le \text{V}_{\text{DD\_A, }_{-}\text{D}}, \text{V}_{\text{PVDD1,2}} \le 5.5 \text{ V},$  $I_{OUT} = 50 \text{ mA}$ Load Regulation -0.013 0.013 %/mA  $V_{DD_A, D}, V_{PVDD1,2} = 3.6 \text{ V}, 1 \text{ mA} \le$ I<sub>OUT</sub> ≤ 100 mA  $3.6 \text{ V} \le \text{V}_{\text{DD}\_A, \_D}, \text{V}_{\text{PVDD1},2} \le 3.9 \text{ V},$ Line Transient Regulation 27 mV TRISE,FALL = 10 µs Load Transient Regulation  $V_{DD A, D}, V_{PVDD1,2} = 3.6 V,$ mV 86 10 mA  $\leq$  I<sub>OUT</sub>  $\leq$  90 mA,  $T_{RISE,FALL} = 100 \text{ ns}$ eΝ Output Noise Voltage 10 Hz ≤ f ≤ 100 kHz, 0.103 mVRM S  $C_{OUT} = 2.2 \mu F$ PSRR Power Supply Ripple Rejection f = 1 kHz,dΒ 56 Ratio  $C_{OUT} = 2.2 \mu F$ f = 10 kHz,dB 36  $C_{OUT} = 2.2 \mu F$ C<sub>OUT</sub> **Output Capacitance** 2.2 20 μF  $0 \text{ mA} \le I_{OUT} \le 100 \text{ mA}$ **Output Capacitor ESR** 500  $\mathsf{m}\Omega$ Start-Up Time from Shut-down  $C_{OUT} = 1 \mu F$ , 54 μs t<sub>START-UP</sub>

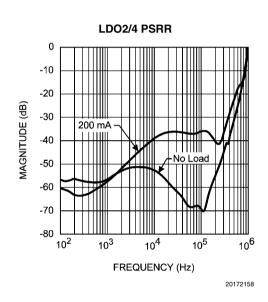

**LDO2 (I/O Voltage) Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$  RESETN, ENABLE = 3.6 V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

$I_{OUT} = 100 \text{ mA}$

| Symbol                    | Parameter                     | Conditions                                                                                    | Min    | Тур   | Max   | Units |

|---------------------------|-------------------------------|-----------------------------------------------------------------------------------------------|--------|-------|-------|-------|

| V <sub>OUT</sub> Accuracy | Output Voltage                | I <sub>OUT</sub> = 125 mA,                                                                    | -3.7%  | 3.3   | 2.8%  | V     |

|                           |                               | V <sub>OUT</sub> = 3.3 V,                                                                     |        |       |       |       |

|                           |                               | $3.6 \text{ V} \le \text{V}_{\text{DD A. D}} \le 5.5 \text{ V}$                               |        |       |       |       |

| V <sub>OUT</sub> Range    | Programmable Output Voltage   | 1.5-2.3 V =100 mV step, 2.5 V, 2.8 V,                                                         | 1.5    | 3.3   | 3.3   | V     |

|                           | Range                         | 3.0 V and 3.3 V                                                                               |        |       |       |       |

| I <sub>OUT</sub>          | Rated Output Current          | $3.6 \text{ V} \le \text{V}_{\text{DD\_A}, \_D}, \text{V}_{\text{PVDD1},2} \le 5.5 \text{ V}$ | 0      |       | 250   | mA    |

|                           | Output Current Limit          | V <sub>OUT</sub> = 0V                                                                         |        |       | 615   |       |

|                           | Dropout Voltage(Note 10)      | I <sub>OUT</sub> = 125 mA                                                                     |        | 65    | 192   | mV    |

| I <sub>Q</sub>            | Quiescent Current             | I <sub>OUT</sub> = 0 mA (Note 11)                                                             |        | 55    |       | μA    |

| $\Delta V_{OUT}$          | Line Regulation               | $3.6 \text{ V} \le \text{V}_{\text{DD A, D}} \le 5.5 \text{ V},$                              | -0.08  |       | 0.312 | %/V   |

|                           |                               | I <sub>OUT</sub> = 125 mA                                                                     |        |       |       |       |

|                           | Load Regulation               | $V_{DD_A, D}, V_{PVDD1,2} = 3.6 \text{ V}, 1 \text{ mA} \le$                                  | -0.018 |       | 0.018 | %/mA  |

|                           |                               | I <sub>OUT</sub> ≤ 250 mA                                                                     |        |       |       |       |

|                           | Line Transient Regulation     | $3.6 \text{ V} \le \text{V}_{\text{DD A. D}}, \text{V}_{\text{PVDD1.2}} \le 3.9 \text{ V},$   |        | 24    |       | mV    |

|                           |                               | $T_{RISE,FALL} = 10 \text{ us}$                                                               |        |       |       |       |

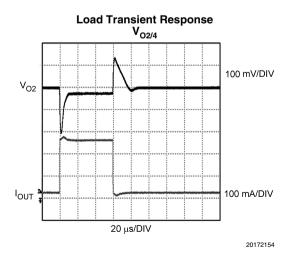

|                           | Load Transient Regulation     | V <sub>DD A, D</sub> , V <sub>PVDD1,2</sub> = 3.6 V,                                          |        | 246   |       | mV    |

|                           |                               | 25 mA ≤ I <sub>OUT</sub> ≤ 225 mA,                                                            |        |       |       |       |

|                           |                               | T <sub>RISE,FALL</sub> = 100 ns                                                               |        |       |       |       |

| eN                        | Output Noise Voltage          | 10 Hz ≤ f ≤ 100 kHz,                                                                          |        | 0.120 |       | mVRM  |

|                           |                               | C <sub>OUT</sub> = 4.7 μF                                                                     |        |       |       | S     |

| PSRR                      | Power Supply Ripple Rejection |                                                                                               |        | 46    |       | dB    |

|                           | Ratio                         | C <sub>OUT</sub> = 4.7 μF                                                                     |        |       |       |       |

|                           |                               | f = 10 kHz,                                                                                   |        | 34    |       |       |

|                           |                               | C <sub>OUT</sub> = 4.7 μF                                                                     |        |       |       |       |

| Symbol                | Parameter                    | Conditions                                           | Min | Тур | Max | Units |

|-----------------------|------------------------------|------------------------------------------------------|-----|-----|-----|-------|

| C <sub>OUT</sub>      | Output Capacitance           | 0 mA ≤ I <sub>OUT</sub> ≤ 250 mA                     | 2   | 4.7 | 20  | μF    |

|                       | Output Capacitor ESR         |                                                      | 5   |     | 500 | mΩ    |

| t <sub>START-UP</sub> | Start-Up Time from Shut-down | C <sub>OUT</sub> = 4.7 μF, I <sub>OUT</sub> = 250 mA |     | 144 |     | μs    |

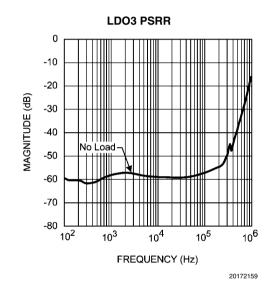

**LDO3 (Memory Retention Voltage) Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$  RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                 | Parameter                                 | Conditions                                                                                             | Min   | Тур    | Max  | Units |

|------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|--------|------|-------|

| V <sub>OFFSET</sub>    | Active State Buffer offset (=             | 25 mA≤I <sub>OUT</sub> ≤ 50 mA,                                                                        | 0     | 12     | 82   | mV    |

|                        | V <sub>O3</sub> -V <sub>FB</sub> ) Output | V <sub>DD_A, _D</sub> , V <sub>PVDD1,2</sub> = 3.6V,                                                   |       |        |      |       |

|                        |                                           | AVS switcher V <sub>OUT</sub> = 1.2 V,                                                                 |       |        |      |       |

|                        |                                           | 200 mA ≤ AVS switcher I <sub>OUT</sub> ≤ 300 mA                                                        |       |        |      |       |

| SIQUTt4U.com           | Sleep state: Memory retention             | $I_{OUT} = 5 \text{ mA}, V_{OUT} = 1.2 \text{ V},$                                                     | -3.6% | 1.2    | 3.6% | V     |

| Accuracy               | voltage regulation                        | $2.7 \text{ V} \le \text{V}_{DD A. D}, \text{V}_{PVDD1.2} \le 5.5 \text{ V}$                           |       |        |      |       |

| V <sub>OUT</sub> Range | Programmable Output Voltage               | Programming Resolution=50 mV                                                                           | 0.6   | 1.2    | 1.35 | V     |

|                        | Range                                     |                                                                                                        |       |        |      |       |

|                        | (Sleep state)                             |                                                                                                        |       |        |      |       |

| I <sub>o</sub>         | Quiescent Current                         | Active mode,                                                                                           |       | 33     | 44   | μΑ    |

|                        |                                           | I <sub>OUT</sub> = 10 μA (Note 11)                                                                     |       |        |      |       |

|                        |                                           | Sleep mode,                                                                                            |       | 10     | 16   | μΑ    |

|                        |                                           | I <sub>OUT</sub> = 10 μA (Note 11)                                                                     |       |        |      |       |

| I <sub>OUT</sub>       | Rated Output Current, Active state        | $2.7 \text{ V} \le \text{V}_{\text{DD\_A, }_{-}\text{D}}, \text{V}_{\text{PVDD1,2}} \le 5.5 \text{ V}$ |       |        | 50   | mA    |

|                        | Rated Output Current, Sleep state         | $2.7 \text{ V} \le \text{V}_{\text{DD\_A, }_{-}\text{D}}, \text{V}_{\text{PVDD1,2}} \le 5.5 \text{ V}$ |       |        | 5    |       |

|                        | Output Current Limit, Active state        | V <sub>OUT</sub> = 0 V                                                                                 |       |        | 397  |       |

| eN                     | Output Voltage Noise                      | 10 Hz ≤ f ≤ 100 kHz,                                                                                   |       | 0.0158 |      | mVRMS |

|                        |                                           | C <sub>OUT</sub> = 1μF                                                                                 |       |        |      |       |

| PSRR                   | Power Supply Ripple Rejection Ratio       |                                                                                                        |       | 36     |      | dB    |

| C <sub>OUT</sub>       | Output Capacitance                        | 0 mA ≤ I <sub>OUT</sub> ≤ 5 mA                                                                         | 0.7   | 1      | 2.2  | μF    |

|                        | Output Capacitor ESR                      |                                                                                                        | 5     |        | 500  | mΩ    |

**LDO4 Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$  RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                    | Parameter                   | Conditions                                                                                    | Min   | Тур | Max  | Units |

|---------------------------|-----------------------------|-----------------------------------------------------------------------------------------------|-------|-----|------|-------|

| V <sub>OUT</sub> Accuracy | Output Voltage              | I <sub>OUT</sub> = 125 mA,                                                                    | -3.7% | 3.3 | 3.1% | V     |

|                           |                             | V <sub>OUT</sub> = 3.3 V,                                                                     |       |     |      |       |

|                           |                             | $3.6 \text{ V} \le \text{V}_{DD A. D}, \text{V}_{PVDD1,2} \le 5.5 \text{ V}$                  |       |     |      |       |

| V <sub>OUT</sub> Range    | Programmable Output Voltage | 1.5-2.3 V =100 mV step, 2.5 V, 2.8V,                                                          | 1.5   | 3.3 | 3.3  | V     |

|                           | Range                       | 3.0 V and 3.3 V                                                                               |       |     |      |       |

| I <sub>OUT</sub>          | Rated Output Current        | $3.6 \text{ V} \le \text{V}_{\text{DD\_A}, \_D}, \text{V}_{\text{PVDD1},2} \le 5.5 \text{ V}$ | 0     |     | 250  | mA    |

|                           | Output Current Limit        | V <sub>OUT</sub> = 0 V                                                                        |       |     | 629  |       |

|                           | Dropout Voltage(Note 10)    | I <sub>OUT</sub> = 125 mA                                                                     |       | 65  | 246  | mV    |

| I <sub>Q</sub>            | Quiescent Current           | I <sub>OUT</sub> = 0 mA (Note 11)                                                             |       | 55  |      | μΑ    |

| 555             | Symbol                | Parameter                     | Conditions                                                                                     | Min    | Тур   | Max   | Units |

|-----------------|-----------------------|-------------------------------|------------------------------------------------------------------------------------------------|--------|-------|-------|-------|

| LP.             | $\Delta V_{OUT}$      | Line Regulation               | $3.6 \text{ V} \le \text{V}_{\text{DD\_A, \_D}}, \text{V}_{\text{PVDD1,2}} \le 5.5 \text{ V},$ | -0.081 |       | 0.306 | %/V   |

|                 |                       |                               | I <sub>OUT</sub> = 125 mA                                                                      |        |       |       |       |

|                 |                       | Load Regulation               | $V_{IN} = 3.6 \text{ V}, 1 \text{ mA} \le I_{OUT} \le 250 \text{ mA}$                          | -0.018 |       | 0.018 | %/mA  |

|                 |                       | Line Transient Regulation     | $3.6 \text{ V} \le \text{V}_{\text{DD\_A, \_D}}, \text{V}_{\text{PVDD1,2}} \le 3.9 \text{ V},$ |        | 24    |       | mV    |

|                 |                       |                               | T <sub>RISE,FALL</sub> = 10 us                                                                 |        |       |       |       |

|                 |                       | Load Transient Regulation     | $V_{DD_A, D}, V_{PVDD1,2} = 3.6 V,$                                                            |        | 246   |       | mV    |

|                 |                       |                               | 25 mA ≤ I <sub>OUT</sub> ≤ 225 mA,                                                             |        |       |       |       |

|                 |                       |                               | T <sub>RISE,FALL</sub> = 100 ns                                                                |        |       |       |       |

|                 | eN                    | Output Noise Voltage          | 10 Hz ≤ f ≤ 100 kHz,                                                                           |        | 0.120 |       | mVRM  |

|                 |                       |                               | C <sub>OUT</sub> = 4.7 μF                                                                      |        |       |       | S     |

|                 | PSRR                  | Power Supply Ripple Rejection | f = 1 kHz,                                                                                     |        | 46    |       | dB    |

|                 |                       | Ratio                         | C <sub>OUT</sub> = 4.7 μF                                                                      |        |       |       |       |

| www.DataSheet4U | J.com                 |                               | f = 10 kHz,                                                                                    |        | 34    |       |       |

|                 |                       |                               | C <sub>OUT</sub> = 4.7 μF                                                                      |        |       |       |       |

|                 | C <sub>OUT</sub>      | Output Capacitance            | 0 mA ≤ I <sub>OUT</sub> ≤ 250 mA                                                               | 2      | 4.7   | 20    | μF    |

|                 |                       | Output Capacitor ESR          |                                                                                                | 5      |       | 500   | mΩ    |

| 1               | t <sub>START-UP</sub> | Start-Up Time from Shut-down  | C <sub>OUT</sub> = 4.7 μF, I <sub>OUT</sub> = 250 mA                                           |        | 144   |       | μs    |

**AVS/DVS Switcher Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$ , RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                    | Parameter                                | Conditions                                                  | Min   | Тур   | Max  | Units |

|---------------------------|------------------------------------------|-------------------------------------------------------------|-------|-------|------|-------|

| V <sub>OUT</sub> Accuracy | Output Voltage                           | I <sub>OUT</sub> = 200 mA, V <sub>OUT</sub> = 1.2 V,        | -4.1% | 1.2   | 4.3% | V     |

|                           |                                          | $V_{DD A. D}, V_{PVDD1.2} = 3.6 V$                          |       |       |      |       |

| V <sub>OUT</sub> Range    | Programmable Output Voltage              | Programming Resolution = 4.7 mV                             | 0.6   | 1.2   | 1.2  | V     |

|                           | Range                                    |                                                             |       |       |      |       |

| $\Delta V_{OUT}$          | Line regulation                          | 2.7V < V <sub>DD_A, _D</sub> , V <sub>PVDD1,2</sub> <5.5 V, |       | 0.18  |      | %/V   |

|                           |                                          | I <sub>OUT</sub> = 10 mA                                    |       |       |      |       |

|                           | Load regulation                          | $V_{DD_A, D}, V_{PVDD1,2} = 3.6 \text{ V}$                  |       | 0.011 |      | %/mA  |

|                           |                                          | I <sub>OUT</sub> = 100-300 mA                               |       |       |      |       |

| IQ                        | Quiescent current consumption            | I <sub>OUT</sub> = 0 mA                                     |       | 15    |      | μΑ    |

| R <sub>DSON(P)</sub>      | P-FET resistance                         | $V_{DD_A, D}, V_{PVDD1,2} = VGS = 3.6 V$                    |       | 425   | 690  | mΩ    |

| R <sub>DSON(N)</sub>      | N-FET resistance                         | $V_{DD_A, D}, V_{PVDD1,2} = VGS = 3.6 V$                    |       | 345   | 635  | mΩ    |

| I <sub>LIM</sub>          | Switch peak current limit                | 2.7 V < V <sub>DD_A, _D</sub> <5.5 V                        | 350   | 520   | 750  | mA    |

| f <sub>OSC</sub>          | Internal oscillator frequency            | PWM-mode                                                    | 805   | 1000  | 1125 | kHz   |

| C <sub>OUT</sub>          | Output Capacitance                       | 0 mA ≤ I <sub>OUT</sub> ≤ 300 mA                            |       | 22    |      | μF    |

|                           | Output Capacitor ESR                     |                                                             | 5     |       | 500  | mΩ    |

| L                         | Inductor inductance                      | 0 mA ≤ I <sub>OUT</sub> ≤ 300 mA                            |       | 4.7   |      | μН    |

| R <sub>VFB</sub>          | V <sub>FB</sub> pin resistance to ground |                                                             | 150   |       | 440  | kΩ    |

**N-Well Bias Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$ , RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                          | Parameter                                                             | Conditions                                                                                                                                                           | Min    | Тур    | Max    | Units |

|---------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|

| V <sub>OFFSET</sub><br>Accuracy | Output Voltage Offset Tolerance                                       | $V_{AVS} = 1.2 \text{ V}$ $V_{OFFSET} = -0.3 \text{ V}$ $Iout = 10 \mu A$                                                                                            | -0.363 | -0.3   | -0.266 | V     |

|                                 | Line Regulation                                                       | $2.7 \le V_{DD\_A,\_D}, P_{VDD1,2} \le 5.5 \text{ V}$ $I_{OUT} = 10 \text{ uA}, V_{OFFSET} = -0.315$ $2.7 \text{ V} \le V_{DD\_A,\_D}, P_{VDD1,2} \le 5.5 \text{ V}$ |        | 0.321  |        | %/V   |

|                                 | Load Regulation                                                       | $V_{DD\_A,\_D}, P_{VDD1,2} = 3.6 \text{ V}$ $VAVS = 1.2 \text{ V}$ $0.1 \text{ uA} \leq IOUT \leq 10 \text{ uA}$                                                     |        | -0.107 |        | %/mA  |

| V <sub>OFFSET</sub>             | Programmable Output Voltage<br>Offset: Referenced to V <sub>AVS</sub> | Programming Resolution: See<br>Register Table                                                                                                                        | -0.315 | 0      | 1      | V     |

| lα                              | Quiescent Current                                                     |                                                                                                                                                                      |        | 50     |        | uA    |

| I <sub>SOURCE/SINK</sub>        | Output Sourcing and Sinking<br>Capability                             | $V_{DD\_A,\_D}$ , $P_{VDD1,2} = 3.6 \text{ V}$ , $V_{OFFSET} = 1 \text{ V}$ $V_{OFFSET} > V_{OFFSET(NOM)} - 15 \text{ mV}$ Steady State                              | 3      |        |        | mA    |

| I <sub>SC (SOURCE)</sub>        | Output Source Short Circuit Limit                                     | V <sub>DD_A, _D</sub> , P <sub>VDD1,2</sub> = 3.6 V,<br>V <sub>NWELL</sub> = 0 V<br>Steady State                                                                     |        |        | 42     | mA    |

| I <sub>SC (SINK)</sub>          | Output Sink Short Circuit Limit                                       | $V_{DD\_A,\_D}$ , $P_{VDD1,2} = 3.6 \text{ V}$ , $V_{NWELL} = V_{DD\_A}$ Steady State                                                                                |        |        | 65     | mA    |

| C <sub>LOAD</sub>               | Output Capacitance Of Load                                            | 0 μA ≤I <sub>OUT</sub> ≤ 3 uA                                                                                                                                        | 0.1    | 1      | 5      | nF    |

**P-Well Characteristics** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$ , RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8)

| Symbol                       | Parameter                                                      | Conditions                                                                                                                    | Min    | Тур   | Max   | Units |

|------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|

| V <sub>OUT</sub><br>Accuracy | Output Voltage Tolerance                                       | $V_{OUT} = 0 V$ $I_{OUT} = 10 \mu A$                                                                                          | -0.035 | 0     | 0.035 | V     |

|                              |                                                                | $2.7 \le V_{DD\_A,\_D}$ , $P_{VDD1,2} \le 5.5 \text{ V}$<br>Bias Current Control bits = 00                                    |        |       |       |       |

|                              | Line Regulation                                                | $I_{OUT} = 10 \text{ uA}$ $V_{OUT} = 0.3 \text{ V}$ $2.7\text{V} \le V_{DD\_A,\_D}, P_{VDD1,2} \le 5.5 \text{ V}$             |        | 0.159 |       | %/V   |

|                              | Load Regulation                                                | $V_{DD\_A,\_D}$ , $P_{VDD1,2} = 3.6 \text{ V}$<br>$V_{OUT} = 0.3 \text{ V}$<br>$0.1 \text{ uA} \le I_{OUT} \le 10 \text{ uA}$ |        | 0.011 |       | %/µA  |

| V <sub>OUT</sub> Range       | Programmable Output Voltage<br>Offset:<br>Referenced to Ground | 0 mA ≤ I <sub>OUT</sub> ≤ 10 uA<br>Programming Resolution: See<br>Register Table                                              | -1     | 0     | 0.3   | V     |

| IQ                           | Quiescent Current                                              | IOUT = 0, P-well Bias Current Control bits = 00                                                                               |        | 150   | 270   | uA    |

| Symbol              | Parameter                  | Conditions                                                                                                                    | Min | Тур | Max | Units |

|---------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>SINK</sub>   | Output Sinking Capability  | V <sub>DD_A, _D</sub> , P <sub>VDD1,2</sub> = 3.6 V<br>Bias Current Control bits = 00                                         | 8   |     |     | uA    |

|                     |                            | V <sub>OUT</sub> > V <sub>OUT(NOM)</sub> - 15 mV(Note 12)                                                                     |     |     |     |       |

|                     |                            | V <sub>DD_A, _D</sub> , P <sub>VDD1,2</sub> = 3.6 V<br>Bias Current Control bits = 01                                         | 36  |     |     |       |

|                     |                            | $V_{OUT} > V_{OUT(NOM)} - 15 \text{ mV(Note 12)}$                                                                             |     |     |     |       |

|                     |                            | V <sub>DD_A, _D</sub> , P <sub>VDD1,2</sub> = 3.6 V<br>Bias Current Control bits = 10                                         | 52  |     |     |       |

|                     |                            | $V_{OUT} > V_{OUT(NOM)} - 15 \text{ mV(Note 12)}$                                                                             |     |     |     |       |

|                     |                            | $V_{DD\_A,\_D}$ , $P_{VDD1,2} = 3.6 \text{ V}$<br>Bias Current Control bits = 11<br>$V_{OUT} > V_{OUT(NOM)}$ - 15 mV(Note 12) | 80  |     |     |       |

| I <sub>SOURCE</sub> | Output Source Capability   | V <sub>DD_A, _D</sub> , P <sub>VDD1,2</sub> = 2.7 V                                                                           | 100 |     |     | uA    |

| C <sub>LOAD</sub>   | Output Capacitance of Load | 0μA ≤ I <sub>OUT</sub> ≤ 3 uA                                                                                                 | 0.1 | 1   | 5   | nF    |

**Logic and Control Inputs** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$ , RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8, 9)

| Symbol               | Parameter                                      | Conditions                                                                                           | Min                   | Тур | Max | Units |

|----------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| PWI <sub>CLOCK</sub> | Rated frequency                                | $2.7 \text{ V} \le \text{V}_{\text{DD\_A, }\_\text{D}}, \text{V}_{\text{PVDD1,2}} \le 5.5 \text{ V}$ |                       |     | 15  | MHz   |

| V <sub>IL</sub>      | Input Low Level                                | ENABLE, RESETN, SPWI, SCLK 2.7                                                                       |                       |     | 0.4 | V     |

|                      |                                                | $V \le V_{DD_A, D}, V_{PVDD1,2} \le 5.5 V$                                                           |                       |     |     |       |

| $V_{IH}$             | Input High Level                               | ENABLE, RESETN 2.7 V $\leq$ V <sub>DD_A, _D</sub> ,                                                  | 2                     |     |     | V     |

|                      |                                                | $V_{PVDD1,2} \le 5.5 \text{ V}$                                                                      |                       |     |     |       |

| $V_{IH\_PWI}$        | Input High Level, PWI                          | SPWI, SCLK, 1.5 V ≤V <sub>O2</sub> ≤ 3.3 V                                                           | V <sub>02</sub> -0.4V |     |     | V     |

| I <sub>IL</sub>      | Logic Input Current                            | ENABLE, RESETN, 0 V ≤ V <sub>DD A, D</sub> ,                                                         | -5                    |     | 5   | μА    |

|                      |                                                | V <sub>PVDD1,2</sub> ≤ 5.5 V                                                                         |                       |     |     |       |

| I <sub>IL_PWI</sub>  | Logic Input Current, PWI                       | SPWI, SCLK, 1.5 V ≤ V <sub>O2</sub> ≤ 3.3 V                                                          | -5                    |     | 15  | μΑ    |

| R <sub>PD_PWI</sub>  | Pull-down resistance for PWI signals           |                                                                                                      | 0.5                   | 1   | 2   | МΩ    |

| T <sub>EN_LOW</sub>  | Minimum low pulse width to enter STARTUP state | ENABLE pulsed high - low - high                                                                      |                       | 10  |     | µsec  |

**Logic and Control Outputs** Unless otherwise noted,  $V_{DD\_A,\_D}$ ,  $V_{PVDD1,2}$ , RESETN, ENABLE = 3.6V. Typical values and limits appearing in normal type apply for TJ = 25°C. Limits appearing in boldface type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 7, 8, 9)

| Symbol              | Parameter              | Conditions                              | Min                     | Тур | Max | Units |

|---------------------|------------------------|-----------------------------------------|-------------------------|-----|-----|-------|

| V <sub>OL</sub>     | Output low level       | PWROK, GPOx, SPWI,                      |                         |     | 0.4 | ٧     |

|                     |                        | I <sub>SINK</sub> ≤ 1 mA                |                         |     |     |       |

| V <sub>OH</sub>     | Output high level      | PWROK, GPOx, I <sub>SOURCE</sub> ≤ 1 mA | V <sub>BAT1</sub> -0.4V |     |     | ٧     |

| V <sub>OH_PWI</sub> | Output high level, PWI | SPWI, I <sub>SOURCE</sub> ≤ 1 mA        | V <sub>O2</sub> -0.4V   |     |     | V     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: The Human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula  $P = (TJ - TA)/\theta_{JA}$ , (1) where TJ is the junction temperature, TA is the ambient temperature, and JA is the junction-to-ambient thermal resistance.

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at TJ=150°C (typ.) and disengages at TJ=140°C (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note 1187: Leadless Leadframe Package (LLP) (AN-1187).

**Note 5:** In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP = 125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation: TA-MAX = TJ-MAX-OP - ( $\theta_{JA}$  × PD-MAX).

Note 6: Junction-to-ambient thermal resistance (θJA) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 102mm x 76mm x 1.6mm with a 2x1 array of thermal vias. The ground plane on the board is 50mm x 50mm. Thickness of copper layers are 36μm/18μm/36μm (1.5oz/1oz/1.5oz). Ambient temperature in simulation is 22°C, still air. Power dissipation is 1W.

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

The value of  $\theta_{JA}$  of this product can vary significantly, depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high VIN, high IOUT), special care must be paid to thermal dissipation issues. For more information on these topics, please refer to Application Note 1187: Leadless Leadframe Package (LLP) and the Power Efficiency and Power Dissipation section of this datasheet.

**Note 7:** All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TJ = 25C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control

Note 8: Capacitors: Low-ESR Surface-Mount Ceramic Capacitors are (MLCCs) used in setting electrical characteristics

Note 9: Guaranteed by design.

Note 10: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.7V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V

Note 11: Quiescent current for LDO1, LDO2, LDO3, and LDO4 do not include shared functional blocks such as the bandgap reference.

Note 12: The output voltage is guaranteed not to drop more than 15 mV (V<sub>OUT</sub> < V<sub>OUT(NOM)</sub> - 15 mV) while sinking the specified current.

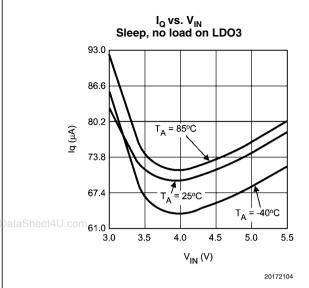

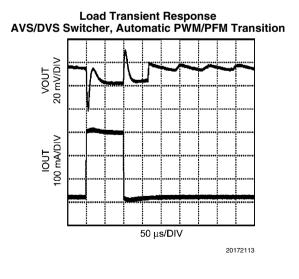

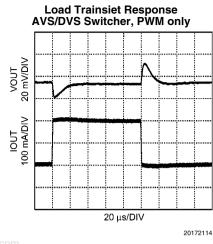

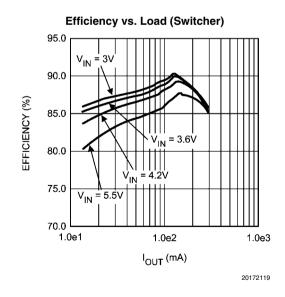

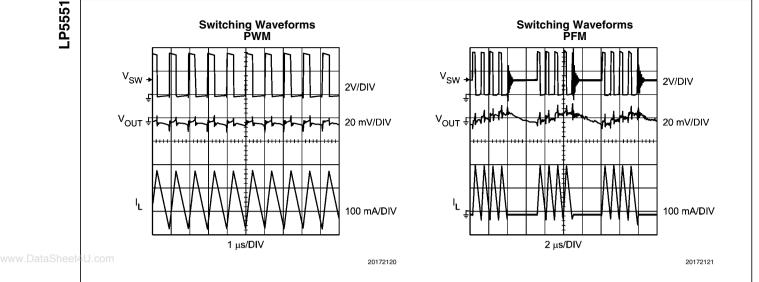

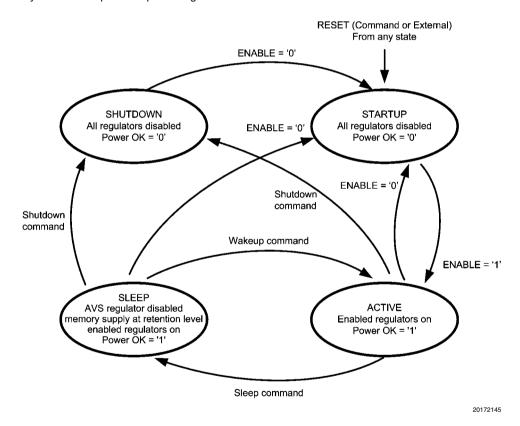

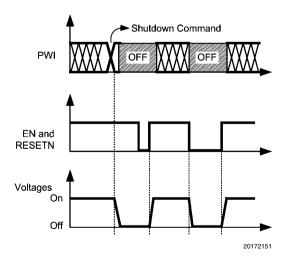

## **Typical Performance Characteristics** Unless otherwise stated: V<sub>IN</sub>=3.6V

www.DataSheet4U.com

Switching Frequency vs. V<sub>IN</sub>

1.10M

T<sub>A</sub> = 85°C

T<sub>A</sub> = 85°C

T<sub>A</sub> = 25°C

T<sub>A</sub> = -40°C

970.00k

3.0

3.5

4.0

4.5

5.0

5.5

V<sub>IN</sub> (V)

www.DataSheet4U.com

Switch Current Limit vs. V<sub>IN</sub> 570.0 = 85°C  $T_A = 25^{\circ}C$ 554.0 (YE) 538.0 - 522.0 538.0 = -40°C 506.0 490.0 <del>-</del> 3.0 3.5 4.0 4.5 5.0 5.5  $V_{|N|}(V)$ 20172118

## **LP5551 PWI Register Map**

The PWI standard supports sixteen 8-bit registers on the PWI slave. The table below summarizes these registers and shows default register bit values after reset. The following sub-sections provide additional detail on the use of each individual register.

## **Summary**

| Register | Register | Register Usage           | Туре | Res | Reset Default Value |   |    |   |   |   |    |

|----------|----------|--------------------------|------|-----|---------------------|---|----|---|---|---|----|

| Address  | Name     |                          |      | 7   | 6                   | 5 | 4  | 3 | 2 | 1 | 0  |

| 0x0      | R0       | Core voltage             | R/W  | 0   | 1                   | 1 | 1  | 1 | 1 | 1 | 1  |

| 0x1      | R1       | Unused                   | R/W  | -   | -                   | - | -  | - | - | - | ]- |

| 0x2      | R2       | Memory retention voltage | R/W  | 0   | 1                   | 1 | 0  | 0 | - | - | -  |

| 0x3      | R3       | Status register          | R/O  | 0   | 0                   | 0 | 0  | 1 | 1 | 1 | 1  |

| 0x4      | R4       | PWI version number       | R/O  | 0   | 0                   | 0 | 0  | 0 | 0 | 0 | 1  |

| 0x5      | R5       | N-well Bias              | R/W  | 0   | 0                   | 0 | 0  | 0 | 0 | - | -  |

| 0x6      | R6       | P-well Bias              | R/W  | 0   | 0                   | 0 | 0  | 0 | 0 | - | -  |

| 0x7      | R7       | LDO2 voltage             | R/W  | 0   | 1                   | 1 | 1  | 1 | - | - | -  |

| 0x8      | R8       | LDO1 voltage             | R/W  | 0   | 0                   | 1 | 0  | 1 | - | - | -  |

| 0x9      | R9       | PFM/PWM force            | R/W  | 0   | 0                   | - | Ī- | - | - | - | -  |

| 0xA      | R10      | SW_DVS voltage           | R/W  | -   | -                   | - | -  | - | - | - | -  |

| 0xB      | R11      | Enable Control           | R/W  | -   | <b>-</b>            | 1 | 1  | 1 | 1 | 1 | 1  |

| 0xC      | R12      | LDO 4 voltage            | R/W  | 0   | 1                   | 1 | 1  | 1 | - | - | ]- |

| 0xD      | R13      | GPO Control              | R/W  | 0   | 0                   | 0 | 0  | 0 | 0 | 0 | 0  |

| 0xE      | R14      | Reserved                 | R/W  | -   | -                   | - | -  | - | - | - | -  |

| 0xF      | R15      | Reserved                 | R/W  | -   | <b>-</b>            | - | Ī- | - | - | - | Ī- |

## **R0 - Core Voltage Register**

Address 0x0

Type R/W

| Bit | Field Name | Description or Comment            | Description or Comment                                                                                                                                |  |  |

|-----|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | Sign       |                                   | This bit is fixed to '0'. Reading this bit will result in a '0'. Any data written into this bit position using the Register Write command is ignored. |  |  |

| 6:0 | Voltage    | Core voltage value. Default value | e is in <b>bold</b> .                                                                                                                                 |  |  |

|     |            | Voltage Data Code [7:0]           | Voltage Value (V)                                                                                                                                     |  |  |

|     |            | 7h'00                             | 0.6                                                                                                                                                   |  |  |

|     |            | 7h'xx                             | Linear scaling                                                                                                                                        |  |  |

|     |            | 7h'7f                             | 1.2 (default)                                                                                                                                         |  |  |

## **R1 - Unused Register**

Address 0x1

Type R/W

Reset Default 8h'00

| Bit | Field Name | Description or Comment                                                  |  |

|-----|------------|-------------------------------------------------------------------------|--|

| 7:0 | Unused     | Write transactions to this register are ignored. Read transactions will |  |

|     |            | return a "No Response Frame." A no response frame contains all zeros    |  |

|     |            | (see PWI 1.0 specification).                                            |  |

## **R2 – VO3 Voltage Register (Memory Retention Voltage)**

Address 0x2

Type R/W

| Bit | Field Name | Description or Comment                          | Description or Comment                                |  |  |  |  |

|-----|------------|-------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| 7   | Sign       | This bit is fixed to '0'. Reading this bit will | result in a '0'. Any data written into this bit       |  |  |  |  |

|     |            | position using the Register Write comma         | position using the Register Write command is ignored. |  |  |  |  |

| 6:3 | Voltage    | Fixed voltage value. A code of all ones in      | dicates maximum voltage while a code of               |  |  |  |  |

|     |            | all zero indicates minimum voltage. Defa        | ult value is in <b>bold</b> .                         |  |  |  |  |

|     |            | Voltage Data Code [6:3]                         | Voltage Value (volts)                                 |  |  |  |  |

|     |            | 4h'0                                            | 0.6                                                   |  |  |  |  |

|     |            | 4h'1                                            | 0.65                                                  |  |  |  |  |

|     |            | 4h'2                                            | 0.7                                                   |  |  |  |  |

|     |            | 4h'3                                            | 0.75                                                  |  |  |  |  |

|     |            | 4h'4                                            | 0.8                                                   |  |  |  |  |

|     |            | 4h'5                                            | 0.85                                                  |  |  |  |  |

|     |            | 4h'6                                            | 0.9                                                   |  |  |  |  |

|     |            | 4h'7                                            | 0.95                                                  |  |  |  |  |

|     |            | 4h'8                                            | 1                                                     |  |  |  |  |

|     |            | 4h'9                                            | 1.05                                                  |  |  |  |  |

|     |            | 4h'A                                            | 1.1                                                   |  |  |  |  |

|     |            | 4h'B                                            | 1.15                                                  |  |  |  |  |

|     |            | 4h'C                                            | 1.20 (default)                                        |  |  |  |  |

|     |            | 4h'D                                            | 1.25                                                  |  |  |  |  |

|     |            | 4h'E                                            | 1.3                                                   |  |  |  |  |

|     |            | 4h'F                                            | 1.35                                                  |  |  |  |  |

| 2:0 | Unused     | These bits are fixed to '0'. Reading these      |                                                       |  |  |  |  |

|     |            | bits will result in a '000'. Any data written   |                                                       |  |  |  |  |

|     |            | into these bits using the Register Write        |                                                       |  |  |  |  |

|     |            | command is ignored.                             |                                                       |  |  |  |  |

www.DataSheet4U.

## R3 - Status Register

Address 0x3

Type Read Only

Reset Default 8h'0F

| Bit | Field Name | Description or Comment   |

|-----|------------|--------------------------|

| 7   | Reserved   | Reserved, read returns 0 |

| 6   | Reserved   | Reserved, read returns 0 |

| 5   | User Bit   | Unused, read returns 0   |

| 4   | User Bit   | Unused, read returns 0   |

| 3   | Fixed OK   | Unused, read returns 1   |

| 2   | ю ок       | Unused, read returns 1   |

| 1   | Memory OK  | Unused, read returns 1   |

| 0   | Core OK    | Unused, read returns 1   |

## **R4 - PWI Version Number Register**

Address 0x4

Type Read Only

Reset Default 8h'01

| Bit | Field Name | Description or Comment                                                     |

|-----|------------|----------------------------------------------------------------------------|

| 7:0 | Version    | Read transaction will return 8h'01 indicating PWI 1.0 specification. Write |

|     |            | transactions to this register are ignored.                                 |

## **R5 - N-Well Bias Register**

Address 0x5

Type R/W

Reset Default 8h'00

| Bit | Field Name | Description or Comr                      | Description or Comment  |                                  |  |  |

|-----|------------|------------------------------------------|-------------------------|----------------------------------|--|--|

| 7   | Sign       | 1: Negative offset<br>0: Positive offset |                         |                                  |  |  |

| 6:2 | Voltage    | Sign Data Code [7]                       | Voltage Data Code [6:2] | Voltage Offset from core voltage |  |  |

|     |            | 0                                        | 5h'19 – 5h'1f           | 1 V                              |  |  |

|     |            |                                          | 5h'01 – 5h'18           | 0.042 - 1 V, 0.042 V steps       |  |  |

|     |            |                                          | 5h'00                   | Active clamp to SW_AVS (default) |  |  |

|     |            | 1                                        | 5h'00                   | 0V                               |  |  |

|     |            |                                          | 5h'01 – 5h'0f           | -0.0210.315V, -0.021<br>V steps  |  |  |

|     |            |                                          | 5h'10 -5h'1f            | -0.315 V                         |  |  |

| 0:1 | Unused     |                                          | •                       | •                                |  |  |

18

## R6 - P-Well Bias Register

Address 0x6

Type R/W

| Bit                         | Field Name | Description or Commen | t                       |                                  |

|-----------------------------|------------|-----------------------|-------------------------|----------------------------------|

| 7                           | Sign       | 1: Negative offset    |                         |                                  |

|                             |            | 0: Positive offset    |                         |                                  |

| 6:2                         | Voltage    | Sign Data Code [7]    | Voltage Data Code [6:2] | Voltage Offset from              |

|                             |            |                       |                         | ground                           |

|                             |            | 0                     | 5h'10 -5h'1f            | 0.3 V                            |

|                             |            |                       | 5h'01 – 5h'0f           | 0.021 - 0.3V, 0.021 V            |

|                             |            |                       |                         | steps                            |

|                             |            |                       | 5h'00                   | Active clamp to ground (default) |

|                             |            | 1                     | 5h'00                   | 0 V                              |

|                             |            |                       | 5h'01 - 5h'18           | -0.0421 V, -0.042 V              |

|                             |            |                       |                         | steps                            |

|                             |            |                       | 5h'19 – 5h'1f           | -1 V                             |

| <b>0</b> h <b>l</b> eet4U.c | com Unused |                       | •                       | •                                |

## R7 – VO2 Voltage Register (I/O Voltage)

Address 0x7

Type R/W

Reset Default 8h'78

| Bit | Field Name | Description or Comment                                                                                                                                |                                                                                  |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| 7   | Sign       | This bit is fixed to '0'. Reading this bit will result in a '0'. Any data written into this bit position using the Register Write command is ignored. |                                                                                  |  |

| 6:3 | Voltage    | Fixed voltage value. A code of al all zero indicates minimum voltage                                                                                  | Il ones indicates maximum voltage while a code of ge. Default value is in bold.  |  |

|     |            | Voltage Data Code [6:3]                                                                                                                               | Voltage Value (volts)                                                            |  |

|     |            | 4h'0                                                                                                                                                  | 1.5                                                                              |  |

|     |            | 4h'1                                                                                                                                                  | 1.5                                                                              |  |

|     |            | 4h'2                                                                                                                                                  | 1.5                                                                              |  |

|     |            | 4h'3                                                                                                                                                  | 1.5                                                                              |  |

|     |            | 4h'4                                                                                                                                                  | 1.6                                                                              |  |

|     |            | 4h'5                                                                                                                                                  | 1.7                                                                              |  |

|     |            | 4h'6                                                                                                                                                  | 1.8                                                                              |  |

|     |            | 4h'7                                                                                                                                                  | 1.9                                                                              |  |

|     |            | 4h'8                                                                                                                                                  | 2                                                                                |  |

|     |            | 4h'9                                                                                                                                                  | 2.1                                                                              |  |

|     |            | 4h'A                                                                                                                                                  | 2.2                                                                              |  |

|     |            | 4h'B                                                                                                                                                  | 2.3                                                                              |  |

|     |            | 4h'C                                                                                                                                                  | 2.5                                                                              |  |

|     |            | 4h'D                                                                                                                                                  | 2.8                                                                              |  |

|     |            | 4h'E                                                                                                                                                  | 3                                                                                |  |

|     |            | 4h'F                                                                                                                                                  | 3.3 (default)                                                                    |  |

| 2:0 | Unused     | These bits are fixed to '0'. Readii into these bits using the Register                                                                                | ng these bits will result in a '000'. Any data written write command is ignored. |  |

## R8 – VO1 Voltage Register (PLL/Fixed Voltage)

Address 0x8

Type R/W

-P555

www.DataSheet4U.

| Bit | Field Name | Description or Comment                                                                                                                  |                                                                                |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| 7   | Sign       | This bit is fixed to '0'. Reading this bit will result in a '0'. Any data written position using the Register Write command is ignored. |                                                                                |  |

| 6:3 | Voltage    | Fixed voltage value. A code of al all zero indicates minimum voltage                                                                    | l ones indicates maximum voltage while a code of ge. Default value is in bold. |  |

|     |            | Voltage Data Code [6:3]                                                                                                                 | Voltage Value (volts)                                                          |  |

|     |            | 4h'0                                                                                                                                    | 0.7                                                                            |  |

|     |            | 4h'1                                                                                                                                    | 0.8                                                                            |  |

|     |            | 4h'2                                                                                                                                    | 0.9                                                                            |  |

|     |            | 4h'3                                                                                                                                    | 1                                                                              |  |

|     |            | 4h'4                                                                                                                                    | 1.1                                                                            |  |

|     |            | 4h'5                                                                                                                                    | 1.2 (default)                                                                  |  |

|     |            | 4h'6                                                                                                                                    | 1.3                                                                            |  |

|     |            | 4h'7                                                                                                                                    | 1.4                                                                            |  |

| om  |            | 4h'8                                                                                                                                    | 1.5                                                                            |  |

|     |            | 4h'9                                                                                                                                    | 1.6                                                                            |  |

|     |            | 4h'A                                                                                                                                    | 1.7                                                                            |  |

|     |            | 4h'B                                                                                                                                    | 1.8                                                                            |  |

|     |            | 4h'C                                                                                                                                    | 1.9                                                                            |  |