# <u>180KHz, 5A Step-down Converter With</u> <u>Cable Dropout Compensation</u>

### **General Description**

The LP6491 is a compact, high efficiency, high speed synchronous monolithic step-down switching regulator designed to power 5V USB applications. A precise output voltage and programmable cable drop compensation maintain accurate 5V regulation at the USB socket connected to the end of a long cable. Forced continuous operation allows the LP6491 to sink current, further enhancing accurate 5V regulation during load transients. Accurate and programmable input/output current limit, an input current monitor pin and an output current monitor pin improve system reliability and safety, allow the user to implement latch-off or auto-retry functionality and can eliminate the need for a USB switch IC. Dual feedback allows regulation on the output of a USB switch, protecting USB devices during fault conditions. Thermal shutdown provides additional protection by limiting power dissipation in the IC during an over temperature fault.

LowPowerSemi 微源半導體

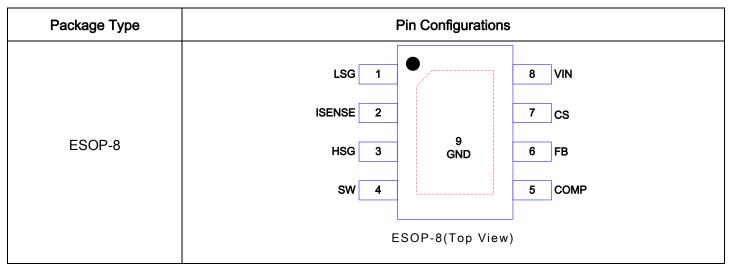

The LP6491 is available in an ESOP8 package and is rated over the -40°C to 85°C temperature range.

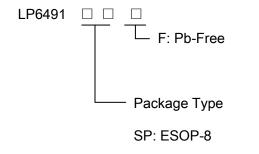

### **Order Information**

#### **Features**

- Input Voltage Range: 9V to 35V

- Max Load Current : 5A

- Programmable Input and Output Current Limit

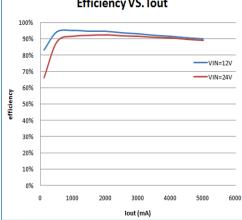

- Up to 95% Efficiency

- 100% Duty Cycle in Dropout

- 180KHz Switching Frequency

- Soft star Function

- Short Circuit Protection

- Current Mode Operation

- Thermal Fault Protection

- ESOP-8 Package

- RoHS Compliant and 100% Lead (Pb)-Free

### **Applications**

- ♦ Portable Media Players

- ♦ Cellular and Smart mobile phone

- ♦ PDA/DSC

- ♦ GPS Applications

### **Marking Information**

| Device                                        | Marking | Package | Shipping  |  |

|-----------------------------------------------|---------|---------|-----------|--|

| LP6491                                        | LPS     | ESOP-8  | 2.5K/REEL |  |

|                                               | LP6491  |         |           |  |

|                                               | YWX     |         |           |  |

| Y: Year code, W: Week code, X: Batch numbers. |         |         |           |  |

# **Functional Pin Description**

## **Pin Description**

| Pin | Name   | Description                                                                                                                                                                                                    |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | LSG    | Low side NMOS driver pin.                                                                                                                                                                                      |  |  |

| 2   | ISENSE | Input current limit detection.                                                                                                                                                                                 |  |  |

| 3   | HSG    | High side PMOS driver pin.                                                                                                                                                                                     |  |  |

| 4   | SW     | Connection to Inductor. This pin connects to the drains of the external main PMOS and synchronous internal power NMOS switches.                                                                                |  |  |

| 5   | COMP   | Loop compensation input. Connect a series RC network from COMP to GND to Compensate the regulation control loop.                                                                                               |  |  |

| 6   | FB     | Feedback Input. Connect FB to the center point of the external resistor divider. Normal voltage for this pin is 0.8V.                                                                                          |  |  |

| 7   | CS     | Output current limit detection. When $V_{CS}$ > 120mV, the chip would disable the output and detect the output current by a fixed cycle. Cooperating with FB pin to achieve output cable dropout compensation. |  |  |

| 8   | VIN    | Supply Input.                                                                                                                                                                                                  |  |  |

| 9   | GND    | Power Ground.                                                                                                                                                                                                  |  |  |

LP6491

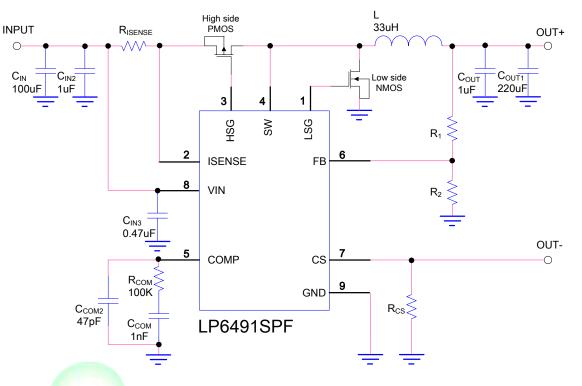

# **Typical Application Circuit**

# Absolute Maximum Ratings Note 1

| $\diamond$ |                                                       | 36V                |

|------------|-------------------------------------------------------|--------------------|

| $\diamond$ | HSG,ISENSE,SW to GND                                  | -0.3V to VIN +0.3V |

| $\diamond$ | Other pin to GND                                      | 0.3V to 6V         |

| $\diamond$ | Maximum Junction Temperature                          | 150°C              |

| $\diamond$ | Operating Ambient Temperature Range (T <sub>A</sub> ) | 40°C to 85°C       |

| $\diamond$ | Storage Temperature                                   | 65°C to 165°C      |

| $\diamond$ | Maximum Soldering Temperature (at leads, 10 sec)      | 260°C              |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

| $\diamond$ | Maximum Power Dissipation (ESOP-8, P <sub>D</sub> ,T <sub>A</sub> =25°C) 2 <sup>v</sup> | W |

|------------|-----------------------------------------------------------------------------------------|---|

| $\diamond$ | Thermal Resistance (ESOP-8, θ <sub>JA</sub> ) 50°C/                                     | W |

# **ESD Susceptibility**

| $\diamond$ | HBM(Human Body Mode) | 2KV  |

|------------|----------------------|------|

| $\diamond$ | MM(Machine Mode)     | 200V |

### **Electrical Characteristics**

(VIN=12V, VEN=5V, L=33uH, CIN=100uF+1uF, COUT=100uF+1uF typical values are TA=25℃)

| Symbol                | Parameter                            | Condition                                     | Min | Тур | Max | Units |

|-----------------------|--------------------------------------|-----------------------------------------------|-----|-----|-----|-------|

| Vin                   | Input Voltage                        |                                               | 9   |     | 35  | V     |

| Vuvlo                 | Input under voltage lock out         | V <sub>IN</sub> fall                          |     | 7   |     | V     |

| V <sub>UVLO_HYS</sub> | UVLO Voltage Hysteresis              |                                               | 0.7 |     |     | V     |

| VILIMT                | Input Current Limit Detection        | VIN-VISENSE                                   |     | 150 |     | mV    |

| lq                    | Quiescent Current                    | V <sub>IN</sub> =12V                          |     | 10  |     | mA    |

| Vlsg                  | LSG HIGH Voltage                     |                                               |     | 5   |     | V     |

| VHSG                  | HSG HIGH Voltage                     |                                               |     | 5   |     | V     |

| Vcs                   | Output Limit Current Detection       |                                               |     | 120 |     | mV    |

| I <sub>LX_LEAK</sub>  | LX Leakage Current                   | V <sub>SW</sub> =0 or 5V, V <sub>IN</sub> =0V |     |     | 0.1 | μA    |

| V <sub>FB</sub>       | Feedback Threshold Voltage Accuracy  | V <sub>IN</sub> =12V                          |     | 0.8 |     | V     |

| fosc                  | Oscillator Frequency                 |                                               |     | 200 |     | KHz   |

| T <sub>SD</sub>       | Over-Temperature Shutdown Threshold  |                                               |     | 150 |     | °C    |

| THYS                  | Over-Temperature Shutdown Hysteresis |                                               |     | 20  |     | °C    |

Note: Output Voltage:  $V_{OUT} = V_{FB} \times (1 + R_1 / R_2)$  Volts;

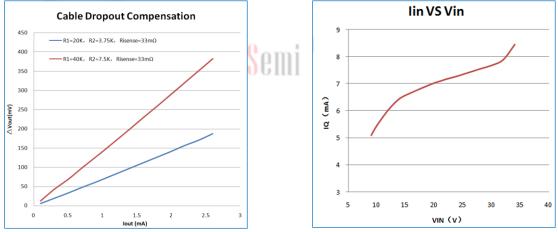

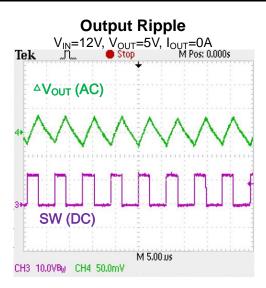

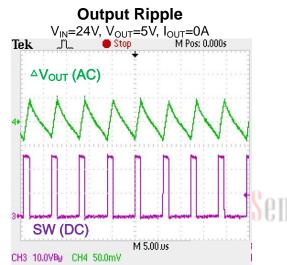

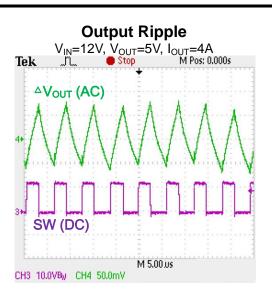

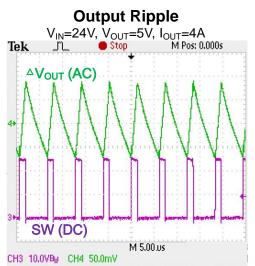

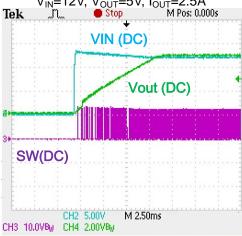

# **Typical Operating Characteristics**

Efficiency VS. lout

### Preliminary Datasheet LP6491

Power ON Waveform

VIN=12V, VOUT=5V, IOUT=2.5A

M Post: 0.000s

#### **Functional Description**

**P**Semi

The LP6491 is a monolithic, constant frequency, current mode step-down DC/DC converter. An oscillator turns on the external top power switch at the beginning of each clock cycle. Current in the inductor then increases until the top switch current comparator trips and turns off the switch. The limit input current is controlled by the voltage between VIN and ISESE pin which should be less than 140mV. When the top power switch turns off, the synchronous power switch turns on until the next clock cycle begins or inductor current falls to zero. And the output current is programmable by V<sub>CS</sub> which is less than 140mV. Whether overload conditions occur to input or output, it will result in the delay of the next clock cycle until circuit current returns to a safe level.

LowPowerSemi 微源半導體

To control the output voltage, the LP6491 error amplifier servos the FB node by comparing the voltage on the USB 5V pin, divided down about 5.25:1, with an internal 0.8V reference. To implement cable drop compensation, it causes an increase in the feedback voltage relative to the reference by CS pin when the load current increases. This differential error makes the error amplifier raise the FB voltage which raises the output voltage, creating an output offset above the 5V output voltage through R<sub>CS</sub> that is proportional to the load current. The output voltage therefore increases with increasing load current. This negative output impedance compensates for resistive drops in wiring for remote loads.

#### Setting the Output Voltage

The LP6491 can be externally programmed. Feedback resistors R1 and R2 program the output to regulate at a voltage higher than 0.8V. Although a larger value will further reduce quiescent current, it will also increase the impedance of the feedback node, making it more sensitive to external noise and interference. The LP6491, combined with FB and CS pin, delivers enhanced transient response and cable dropout compensation for extreme pulsed load applications. The external resistor sets the output voltage according to the following equation:

**Preliminary Datasheet**

Consider the cable dropout compensation, setting VOUT should be calculated with lo and R<sub>CS</sub> which is show in Cable Drop Compensation. Then the complete process is: Setting the output current limit would get Rcs; confirm the terminal output voltage when circuit achieve the max lo to get  $\Delta V_{OUT}$ ; Calculate the R1 and R2 by

LP6491

$\Delta V_{OUT} = I_O \times R_{CS} \times G_M \times R1$

Vout=0.8V×(1+R1/R2)

#### **Cable Drop Compensation**

The LP6491 includes the necessary circuitry to implement cable drop compensation. Cable drop compensation allows the regulator to maintain 5V regulation on the USB despite high cable resistance. The LP6491 increases its local output voltage V<sub>OUT</sub> above 5V as the load increases to keep terminal output voltage regulated to 5V. This compensation does not require running an additional pair of Kelvin sense wires from the regulator to the load, but does require the system designer to know the function of cable resistance Rcs.

Program the cable drop compensation using the following ratio:

> Vo`=(R1+R2)/R2×VFB×Io×Rcs×GM×R1  $\Delta V_{OUT} = I_O \times R_{CS} \times G_M \times R1$

Vo` is the terminal output voltage, R1 is output pull up resistor, R2 is output pull down resistor, G<sub>M</sub> is chip output current error amplifier transconductance which is 5.5x10<sup>-6</sup>Ω<sup>-1</sup>, V<sub>FB</sub> is fix at 0.8V(The FB pin voltage would increase when Cable Dropout Compensation work. This VFB value is used for calculation.)

Rcs is typically chosen based on the desired current limit and is typically  $25m\Omega$  for 5A systems. See the Setting the Current Limit section for more information.

The current flowing to the USB 5V is identical to the current flowing through the Rcs resistor. While the ratio of output divide two resistors should be chosen per the equation above, choose the absolute values of these resistors to keep terminal output voltage above designed voltage by designer. So the actual output voltage between OUT+ and OUT- is:

#### Vout=Vo'-lo×(RDROP+Rcs)

RDROP is the equivalent resistance in the USB line.

Vout=0.8V×(1+R1/R2)

R1=(V<sub>OUT</sub>/0.8V-1)×R2

LowPowerSemi 微源半導體

#### **Current Limit and Over-Temperature Protection**

For overload conditions, the peak input current is limited to (140mV/R<sub>ISENSE</sub>)(A) and the output current limit is (120mV/R<sub>CS</sub>) (A). To minimize power dissipation and stresses under current limit and short-circuit conditions, switching is terminated after entering current limit condition. The termination lasts for several consecutive clock cycles after a current limit has been sensed. Thermal protection completely disables switching when internal dissipation becomes excessive. The junction over-temperature threshold is 150°C with 20°C of hysteresis. Once an over-temperature or over-current fault conditions is removed, the output voltage automatically recovers.

#### **Dropout Operation**

When input voltage decreases near the value of the output voltage, the LP6491 allows the main switch to remain on for more than one switching cycle and increases the duty cycle until it reaches 100%. The duty cycle D of a step-down converter is defined as:

$$D = t_{ON} \times f_{OSC} \times 100\% = \frac{V_{OUT}}{V_{IN}} \times 100\%$$

Where ton is the main switch on time and fosc is the oscillator frequency.

#### **Inductor Selection**

For most designs, the LP6491 operates with inductor values of  $33\mu$ H. Low inductance values are physically smaller but require faster switching, which results in some efficiency loss. The inductor value can be derived from the following equation:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times f_{OSC}}$$

Where  $\Delta I_L$  is inductor ripple current. Large value inductors lower ripple current and small value inductors result in high ripple currents. Choose inductor ripple current approximately 30% of the maximum load current. Manufacturer's specifications list both the inductor DC current rating, which is a thermal limitation, and the peak current rating, which is determined by the saturation characteristics. The inductor should not show any appreciable saturation under normal load conditions. Some inductors may meet the peak and average current ratings yet result in excessive losses due to a high DCR. Always consider the losses associated with the DCR and its effect on the total converter efficiency when selecting an inductor. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the  $1m\Omega$  to  $100m\Omega$  range. For higher efficiency at heavy loads, the resistance should be kept below  $100m\Omega$ . The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation.

#### **Output Capacitor Selection**

The function of output capacitance is to store energy to attempt to maintain a constant voltage. The energy is stored in the capacitor's electric field due to the voltage applied. The value of output capacitance is generally selected to limit output voltage ripple to the level required by the specification. Since the ripple current in the output inductor is usually determined by L, VOUT and VIN, the series impedance of the capacitor primarily determines the out-put voltage ripple. The three elements of the capacitor that contribute to its impedance (and output voltage ripple) are equivalent series resistance (ESR), equivalent series inductance (ESL), and capacitance(C). The output voltage droop due to a load transient is dominated by the capacitance of the ceramic output capacitor. During a step increase in load current, the ceramic output capacitor alone supplies the load current until the loop responds.

Ripple current flowing through a capacitor's ESR causes power dissipation in the capacitor. This power dissipation causes a temperature increase internal to the capacitor. Excessive temperature can seriously shorten the expected life of a capacitor.

### LP6491

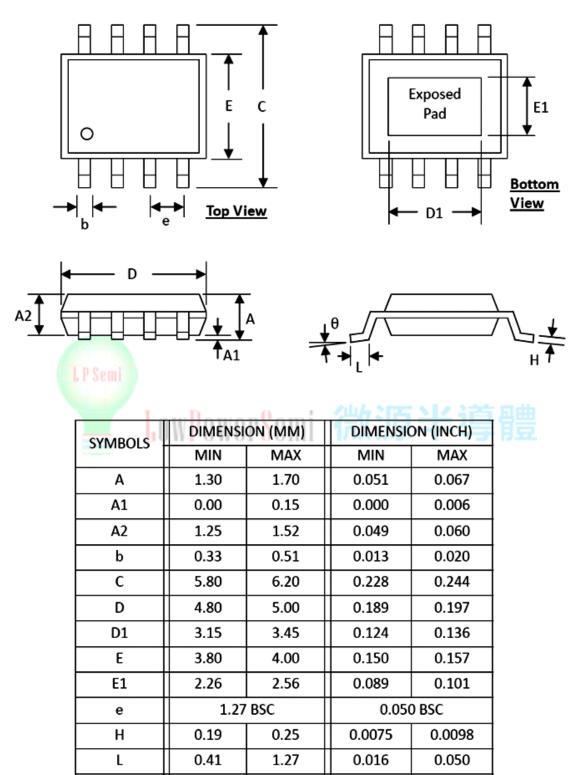

# **Packaging Information**

8°

0°

8°

θ

0°