### **LPV521**

# Nanopower, 1.8V, RRIO, CMOS Input, Operational Amplifier

### **General Description**

The LPV521 is a single nanopower 552 nW amplifier designed for ultra long life battery applications. The operating voltage range of 1.6V to 5.5V coupled with typically 351 nA of supply current make it well suited for RFID readers and remote sensor nanopower applications. The device has input common mode voltage 0.1V over the rails, guaranteed TCV $_{\rm OS}$  and voltage swing to the rail output performance. The LPV521 has a carefully designed CMOS input stage that outperforms competitors with typically 40 fA  $\rm I_{BIAS}$  currents. This low input current significantly reduces  $\rm I_{BIAS}$  and  $\rm I_{OS}$  errors introduced in megohm resistance, high impedance photodiode, and charge sense situations. The LPV521 is a member of the PowerWise® family and has an exceptional power-to-performance ratio.

The wide input common mode voltage range, guaranteed 1 mV  $V_{OS}$  and 3.5  $\mu$ V/°C  $TCV_{OS}$  enables accurate and stable measurement for both high side and low side current sensing. EMI protection was designed into the device to reduce sensitivity to unwanted RF signals from cell phones or other RFID readers.

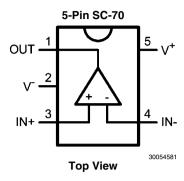

The LPV521 is offered in the 5-pin SC-70 package.

### **Features**

(For V<sub>S</sub> = 5V, Typical unless otherwise noted)

| ■ Supply current at v <sub>CM</sub> = 0.3v  | 400 nA (max)    |

|---------------------------------------------|-----------------|

| <ul> <li>Operating voltage range</li> </ul> | 1.6V to 5.5V    |

| ■ Low TCV <sub>OS</sub>                     | 3.5 µV/°C (max) |

| ■ V <sub>OS</sub>                           | 1 mV (max)      |

| <ul><li>Input bias current</li></ul>        | 40 fA           |

| ■ PSRR                                      | 109 dB          |

| ■ CMRR                                      | 102 dB          |

| ■ Open loop gain                            | 132 dB          |

| <ul><li>Gain bandwidth product</li></ul>    | 6.2 kHz         |

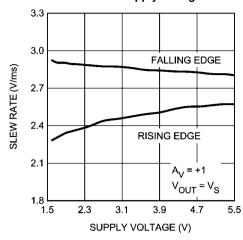

| ■ Slew rate                                 | 2.4 V/ms        |

| ■ Input voltage noise at f = 100 Hz         | 255 nV/√Hz      |

| ■ Temperature range                         | -40°C to 125°C  |

### **Applications**

- Wireless remote sensors

- Powerline monitoring

- Power meters

- Battery powered industrial sensors

- Micropower oxygen sensor and gas sensor

- Active RFID readers

- Zigbee based sensors for HVAC control

- Sensor network powered by energy scavenging

### **Typical Application**

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

ESD Tolerance (Note 2)

Storage Temperature Range -65°C to 150°C Junction Temperature (*Note 3*) 150°C Mounting Temperature

Infrared or Convection (30 sec.)

Wave Soldering Lead Temp. (4 sec.) 260°C

260°C

### **Operating Ratings** (Note 1)

Temperature Range (Note 3)  $-40^{\circ}$ C to 125°C Supply Voltage (V<sub>S</sub> = V+ - V-) 1.6V to 5.5V

Package Thermal Resistance (θ<sub>JA</sub>) (Note 3)

5-Pin SC-70 456 °C/W

### 1.8V DC Electrical Characteristics (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 1.8V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                                                               | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)   | Units       |

|-------------------|-------------------------------------|------------------------------------------------------------------------------------------|-----------------|-----------------|-------------------|-------------|

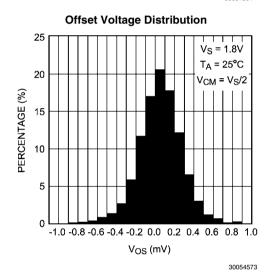

| V <sub>OS</sub>   | Input Offset Voltage                | V <sub>CM</sub> = 0.3V                                                                   | (11616-6)       | 0.1             | ±1.0<br>±1.23     |             |

|                   |                                     | V <sub>CM</sub> = 1.5V                                                                   |                 | 0.1             | ±1.0<br>±1.23     | mV          |

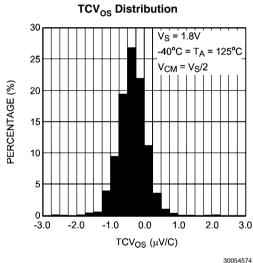

| TCV <sub>OS</sub> | Input Offset Voltage Drift (Note 9) |                                                                                          |                 | ±0.4            | ±3                | μV/°C       |

| I <sub>BIAS</sub> | Input Bias Current                  |                                                                                          |                 | 0.01            | ±1<br><b>±50</b>  | pA          |

| I <sub>os</sub>   | Input Offset Current                |                                                                                          |                 | 10              |                   | fA          |

| CMRR              | Common Mode Rejection Ratio         | 0V ≤ V <sub>CM</sub> ≤ 1.8V                                                              | 66<br><b>60</b> | 92              |                   |             |

|                   |                                     | 0V ≤ V <sub>CM</sub> ≤ 0.7V                                                              | 75<br><b>74</b> | 101             |                   | dB          |

|                   |                                     | 1.2V ≤ V <sub>CM</sub> ≤ 1.8V                                                            | 75<br><b>53</b> | 120             |                   |             |

| PSRR              | Power Supply Rejection Ratio        | $1.6V \le V^{+} \le 5.5V$<br>$V_{CM} = 0.3V$                                             | 85<br><b>76</b> | 109             |                   | dB          |

| CMVR              | Common Mode Voltage Range           | CMRR ≥ 67 dB<br>CMRR ≥ 60 dB                                                             | 0<br><b>0</b>   |                 | 1.8<br><b>1.8</b> | V           |

| A <sub>VOL</sub>  | Large Signal Voltage Gain           | $V_{O} = 0.5V \text{ to } 1.3V$ $R_{L} = 100 \text{ k}\Omega \text{ to } V^{+}/2$        | 74<br><b>73</b> | 125             |                   | dB          |

| V <sub>O</sub>    | Output Swing High                   | $R_L = 100 \text{ k}\Omega \text{ to V} + /2$<br>$V_{IN}(\text{diff}) = 100 \text{ mV}$  |                 | 2               | 50<br><b>50</b>   | mV from     |

|                   | Output Swing Low                    | $R_L = 100 \text{ k}\Omega \text{ to V} + /2$<br>$V_{IN}(\text{diff}) = -100 \text{ mV}$ |                 | 2               | 50<br><b>50</b>   | either rail |

| I <sub>O</sub>    | Output Current (Note 7)             | Sourcing, V <sub>O</sub> to V <sup>-</sup><br>V <sub>IN</sub> (diff) = 100 mV            | 1<br><b>0.5</b> | 3               |                   |             |

|                   |                                     | Sinking, $V_O$ to V+<br>$V_{IN}(diff) = -100 \text{ mV}$                                 | 1<br>0.5        | 3               |                   | mA mA       |

| I <sub>S</sub>    | Supply Current                      | V <sub>CM</sub> = 0.3V                                                                   |                 | 345             | 400<br><b>580</b> | nA          |

|                   |                                     | V <sub>CM</sub> = 1.5V                                                                   |                 | 472             | 600<br><b>850</b> | IIA.        |

### 1.8V AC Electrical Characteristics (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 1.8V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                            | Conditions                                           |              | Min<br>(Note 6) | Typ      | Max      | Units            |

|----------------|--------------------------------------|------------------------------------------------------|--------------|-----------------|----------|----------|------------------|

|                |                                      |                                                      |              |                 | (Note 5) | (Note 6) |                  |

| GBW            | Gain-Bandwidth Product               | $C_L = 20 \text{ pF}, R_L = 10$                      | 00 kΩ        |                 | 6.1      |          | kHz              |

| SR             | Slew Rate                            | $A_V = +1,$                                          | Falling Edge |                 | 2.9      |          | V/ms             |

|                |                                      | $V_{IN} = 0V \text{ to } 1.8V$                       | Rising Edge  |                 | 2.3      |          | V/IIIS           |

| θ <sub>m</sub> | Phase Margin                         | $C_L = 20 \text{ pF}, R_L = 100 \text{ k}\Omega$     |              |                 | 72       |          | deg              |

| G <sub>m</sub> | Gain Margin                          | $C_{L} = 20 \text{ pF}, R_{L} = 100 \text{ k}\Omega$ |              |                 | 19       |          | dB               |

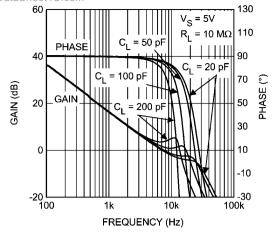

| e <sub>n</sub> | Input-Referred Voltage Noise Density | f = 100 Hz                                           |              |                 | 265      |          | nV/√Hz           |

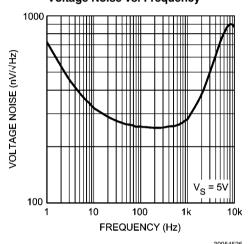

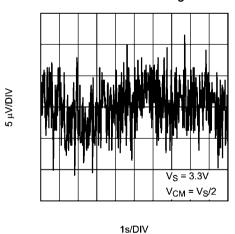

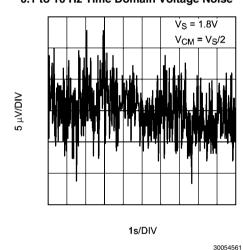

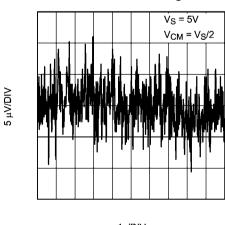

|                | Input-Referred Voltage Noise         | 0.1 Hz to 10 Hz                                      |              |                 | 24       |          | μV <sub>PP</sub> |

| i <sub>n</sub> | Input-Referred Current Noise         | f = 100 Hz                                           |              |                 | 100      |          | fA/√Hz           |

### 3.3V DC Electrical Characteristics (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 3.3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                      | Min             | Тур      | Max              | Units              |

|-------------------|-------------------------------------|-------------------------------------------------|-----------------|----------|------------------|--------------------|

|                   |                                     |                                                 | (Note 6)        | (Note 5) | (Note 6)         |                    |

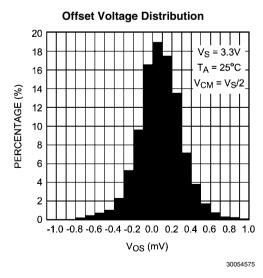

| V <sub>os</sub>   | Input Offset Voltage                | $V_{CM} = 0.3V$                                 |                 | 0.1      | ±1.0             |                    |

|                   |                                     |                                                 |                 |          | ±1.23            | mV                 |

|                   |                                     | $V_{CM} = 3V$                                   |                 | 0.1      | ±1.0             |                    |

| TOV               | land to Office to Vielland Doils    |                                                 |                 | .0.4     | ±1.23            | 1400               |

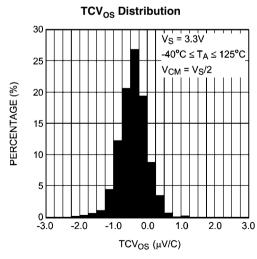

| TCV <sub>OS</sub> | Input Offset Voltage Drift (Note 9) |                                                 |                 | ±0.4     | ±3               | μV/°C              |

| BIAS              | Input Bias Current                  |                                                 |                 | 0.01     | ±1<br><b>±50</b> | pA                 |

| l <sub>os</sub>   | Input Offset Current                |                                                 |                 | 20       |                  | fA                 |

| CMRR              | Common Mode Rejection Ratio         | 0V ≤ V <sub>CM</sub> ≤ 3.3V                     | 72<br><b>70</b> | 97       |                  |                    |

|                   |                                     | 0V ≤ V <sub>CM</sub> ≤ 2.2V                     | 78<br><b>75</b> | 106      |                  | dB                 |

|                   |                                     | $2.7V \le V_{CM} \le 3.3V$                      | 77<br><b>76</b> | 121      |                  |                    |

| PSRR              | Power Supply Rejection Ratio        | 1.6V ≤ V+ ≤ 5.5V                                | 85              | 109      |                  |                    |

|                   |                                     | $V_{CM} = 0.3V$                                 | 76              |          |                  | dB                 |

| CMVR              | Common Mode Voltage Range           | CMRR ≥ 72 dB                                    | -0.1            |          | 3.4              | .,                 |

|                   |                                     | CMRR ≥ 70 dB                                    | 0               |          | 3.3              | V                  |

| A <sub>VOL</sub>  | Large Signal Voltage Gain           | $V_0 = 0.5V \text{ to } 2.8V$                   | 82              | 120      |                  |                    |

| 102               |                                     | $R_{L} = 100 \text{ k}\Omega \text{ to V+/2}$   | 76              |          |                  | dB                 |

| V <sub>O</sub>    | Output Swing High                   | $R_1 = 100 \text{ k}\Omega \text{ to V} + /2$   |                 | 3        | 50               |                    |

|                   |                                     | $V_{IN}(diff) = 100 \text{ mV}$                 |                 |          | 50               | mV                 |

|                   | Output Swing Low                    | $R_{L} = 100 \text{ k}\Omega \text{ to V} + /2$ |                 | 2        | 50               | from eithe<br>rail |

|                   |                                     | $V_{IN}$ (diff) = -100 mV                       |                 |          | 50               | Iali               |

| I <sub>o</sub>    | Output Current (Note 7)             | Sourcing, V <sub>O</sub> to V-                  | 5               | 11       |                  |                    |

|                   |                                     | $V_{IN}(diff) = 100 \text{ mV}$                 | 4               |          |                  |                    |

|                   |                                     | Sinking, V <sub>O</sub> to V+                   | 5               | 12       |                  | mA                 |

|                   |                                     | $V_{IN}(diff) = -100 \text{ mV}$                | 4               |          |                  |                    |

| <b>Symbol</b><br>aSheet4U.co | <b>Parameter</b><br>m | Conditions      | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)   | Units |

|------------------------------|-----------------------|-----------------|-----------------|-----------------|-------------------|-------|

| I <sub>S</sub>               | Supply Current        | $V_{CM} = 0.3V$ |                 | 346             | 400<br><b>600</b> | n A   |

|                              |                       | $V_{CM} = 3V$   |                 | 471             | 600<br><b>860</b> | nA    |

### 3.3V AC Electrical Characteristics (Note 4)

Unless otherwise is specified, all limits guaranteed for  $T_A = 25$  °C,  $V^+ = 3.3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                            | Conditions                                      |              | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units        |

|----------------|--------------------------------------|-------------------------------------------------|--------------|-----------------|-----------------|-----------------|--------------|

| GBW            | Gain-Bandwidth Product               | $C_L = 20 \text{ pF}, R_L = 1$                  | 00 kΩ        |                 | 6.2             |                 | kHz          |

| SR             | Slew Rate                            | A <sub>V</sub> = +1,                            | Falling Edge |                 | 2.9             |                 | V/ms         |

|                |                                      | $V_{IN} = 0V \text{ to } 3.3V$                  | Rising Edge  |                 | 2.5             |                 | V/IIIS       |

| θ <sub>m</sub> | Phase Margin                         | $C_L = 20 \text{ pF}, R_L = 10 \text{ k}\Omega$ |              |                 | 73              |                 | deg          |

| G <sub>m</sub> | Gain Margin                          | $C_L = 20 \text{ pF}, R_L = 1$                  | 0 kΩ         |                 | 19              |                 | dB           |

| e <sub>n</sub> | Input-Referred Voltage Noise Density | f = 100 Hz                                      |              |                 | 259             |                 | nV/√Hz       |

|                | Input-Referred Voltage Noise         | 0.1 Hz to 10 Hz                                 |              |                 | 22              |                 | $\mu V_{PP}$ |

| i <sub>n</sub> | Input-Referred Current Noise         | f = 100 Hz                                      |              |                 | 100             |                 | fA/√Hz       |

### **5V DC Electrical Characteristics** (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A$  = 25°C,  $V^+$  = 5V,  $V^-$  = 0V,  $V_{CM}$  =  $V_O$  =  $V^+/2$ , and  $R_L$  > 1M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                    | Min      | Тур      | Max              | Units     |

|-------------------|-------------------------------------|-----------------------------------------------|----------|----------|------------------|-----------|

|                   |                                     |                                               | (Note 6) | (Note 5) | (Note 6)         |           |

| V <sub>os</sub>   | Input Offset Voltage                | $V_{CM} = 0.3V$                               |          | 0.1      | ±1.0             |           |

|                   |                                     |                                               |          |          | ±1.23            | mV        |

|                   |                                     | $V_{CM} = 4.7V$                               |          | 0.1      | ±1.0             | 1110      |

|                   |                                     |                                               |          |          | ±1.23            |           |

| TCV <sub>OS</sub> | Input Offset Voltage Drift (Note 9) |                                               |          | ±0.4     | ±3.5             | μV/°C     |

| I <sub>BIAS</sub> | Input Bias Current                  |                                               |          | 0.04     | ±1<br><b>±50</b> | pA        |

| I <sub>os</sub>   | Input Offset Current                |                                               |          | 60       |                  | fA        |

| CMRR              | Common Mode Rejection Ratio         | 0V ≤ V <sub>CM</sub> ≤ 5.0V                   | 75       | 102      |                  |           |

|                   |                                     | <u> </u>                                      | 74       |          |                  | _         |

|                   |                                     | 0V ≤ V <sub>CM</sub> ≤ 3.9V                   | 84       | 108      |                  | dB        |

|                   |                                     |                                               | 80       |          |                  | GD.       |

|                   |                                     | $4.4V \le V_{CM} \le 5.0V$                    | 77       | 115      |                  |           |

|                   |                                     |                                               | 76       |          |                  |           |

| PSRR              | Power Supply Rejection Ratio        | 1.6V ≤ V+ ≤ 5.5V                              | 85       | 109      |                  | dB        |

|                   |                                     | $V_{CM} = 0.3V$                               | 76       |          |                  | GD.       |

| CMVR              | Common Mode Voltage Range           | CMRR ≥ 75 dB                                  | -0.1     |          | 5.1              | V         |

|                   |                                     | CMRR ≥ 74 dB                                  | 0        |          | 5                | V         |

| A <sub>VOL</sub>  | Large Signal Voltage Gain           | V <sub>O</sub> = 0.5V to 4.5V                 | 84       | 132      |                  | dB        |

|                   |                                     | $R_L = 100 \text{ k}\Omega \text{ to V} + /2$ | 76       |          |                  |           |

| $\overline{V_0}$  | Output Swing High                   | $R_1 = 100 \text{ k}\Omega \text{ to V} + /2$ |          | 3        | 50               |           |

| -                 |                                     | $V_{IN}(diff) = 100 \text{ mV}$               |          |          | 50               | mV fror   |

|                   | Output Swing Low                    | $R_1 = 100 \text{ k}\Omega \text{ to V} + /2$ |          | 3        | 50               | either ra |

|                   |                                     | $V_{IN}$ (diff) = -100 mV                     |          |          | 50               |           |

| Symbol<br>www.Datas | Parameter<br>heet4U.com | Conditions                                                        | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)   | Units |

|---------------------|-------------------------|-------------------------------------------------------------------|-----------------|-----------------|-------------------|-------|

| I <sub>O</sub>      | Output Current (Note 7) | Sourcing, V <sub>O</sub> to V-<br>V <sub>IN</sub> (diff) = 100 mV | 15<br><b>8</b>  | 23              |                   |       |

|                     |                         | Sinking, $V_O$ to V+<br>$V_{IN}$ (diff) = -100 mV                 | 15<br><b>8</b>  | 22              |                   | mA    |

| I <sub>S</sub>      | Supply Current          | V <sub>CM</sub> = 0.3V                                            |                 | 351             | 400<br><b>620</b> | Λ     |

|                     |                         | V <sub>CM</sub> = 4.7V                                            |                 | 475             | 600<br><b>870</b> | nA    |

### **5V AC Electrical Characteristics** (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A = 25$ °C,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                                 | Conditions                                       |                                        | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units        |

|----------------|-------------------------------------------|--------------------------------------------------|----------------------------------------|-----------------|-----------------|-----------------|--------------|

| GBW            | Gain-Bandwidth Product                    | $C_L = 20 \text{ pF}, R_L = \frac{1}{2}$         | 100 kΩ                                 |                 | 6.2             |                 | kHz          |

| SR             | Slew Rate                                 | $A_V = +1,$ Falling Edge $V_{IN} = 0V$ to $5V$   |                                        | 1.1<br>1.2      | 2.7             |                 | \//          |

|                |                                           |                                                  | Rising Edge                            | 1.1<br>1.2      | 2.4             |                 | V/ms         |

| θ <sub>m</sub> | Phase Margin                              | $C_L = 20 \text{ pF}, R_L = \frac{1}{2}$         | 100 kΩ                                 |                 | 73              |                 | deg          |

| G <sub>m</sub> | Gain Margin                               | $C_L = 20 \text{ pF}, R_L = 100 \text{ k}\Omega$ |                                        |                 | 20              |                 | dB           |

| e <sub>n</sub> | Input-Referred Voltage Noise Density      | f = 100 Hz                                       |                                        |                 | 255             |                 | nV/√Hz       |

|                | Input-Referred Voltage Noise              | 0.1 Hz to 10 Hz                                  |                                        |                 | 22              |                 | $\mu V_{PP}$ |

| i <sub>n</sub> | Input-Referred Current Noise              | f = 100 Hz                                       |                                        |                 | 100             |                 | fA/√Hz       |

| EMIRR          | EMI Rejection Ratio, IN+ and IN- (Note 8) | V <sub>RF_PEAK</sub> = 100 m<br>f = 400 MHz      | V <sub>P</sub> (–20 dB <sub>P</sub> ), |                 | 121             |                 |              |

|                |                                           | V <sub>RF_PEAK</sub> = 100 m<br>f = 900 MHz      | V <sub>P</sub> (–20 dB <sub>P</sub> ), |                 | 121             |                 | dB           |

|                |                                           | V <sub>RF_PEAK</sub> = 100 m<br>f = 1800 MHz     | $V_P$ (–20 dB <sub>P</sub> ),          |                 | 124             |                 | ив           |

|                |                                           | $V_{RF\_PEAK} = 100 \text{ m}$<br>f = 2400 MHz   | $V_P (-20 \text{ dB}_P),$              |                 | 142             |                 |              |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

**Note 3:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

**Note 4:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

Note 5: Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 6: All limits are guaranteed by testing, statistical analysis or design.

Note 7: The short circuit test is a momentary open loop test.

Note 8: The EMI Rejection Ratio is defined as EMIRR = 20log ( $V_{RF\_PEAK}/\Delta V_{OS}$ ).

Note 9: The offset voltage average drift is determined by dividing the change in  $V_{OS}$  at the temperature extremes by the total temperature change.

# www and a Sh Connection Diagram

### **Ordering Information**

| Package     | Part Number | Package Marking | Transport Media         | NSC Drawing |

|-------------|-------------|-----------------|-------------------------|-------------|

|             | LPV521MG    |                 | 1k Units Tape and Reel  |             |

| 5-Pin SC-70 | LPV521MGE   | AHA             | 250 Units Tape and Reel | MAA05A      |

|             | LPV521MGX   |                 | 3k Units Tape and Reel  |             |

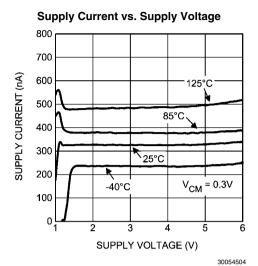

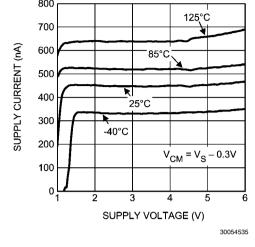

## **Typical Performance Characteristics** At T<sub>J</sub> = 25°C, unless otherwise specified. www.DataSheet4U.com

Supply Current vs. Supply Voltage

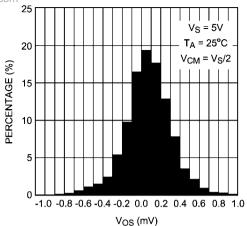

### aSheet4U.com Offset Voltage Distribution

30054568

### \_\_\_\_\_\_

30054506

30054507

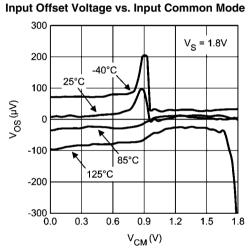

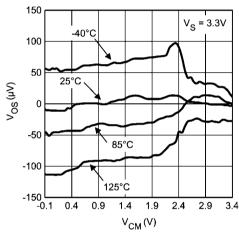

### Input Offset Voltage vs. Input Common Mode

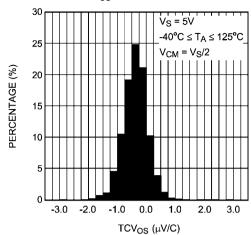

TCV<sub>OS</sub> Distribution

30054569

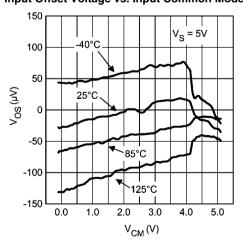

### Input Offset Voltage vs. Input Common Mode

30054505

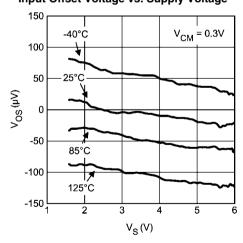

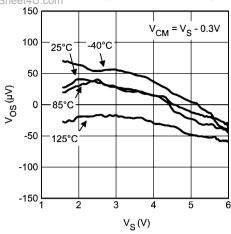

### Input Offset Voltage vs. Supply Voltage

### Input Offset Voltage vs. Supply Voltage

30054538

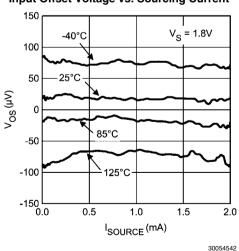

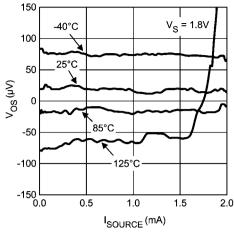

### Input Offset Voltage vs. Sourcing Current

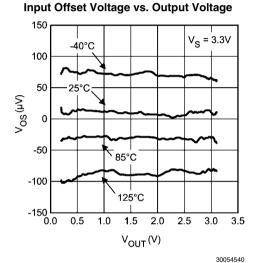

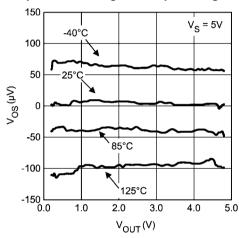

### Input Offset Voltage vs. Output Voltage

### Input Offset Voltage vs. Output Voltage

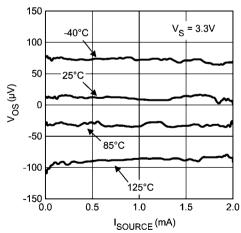

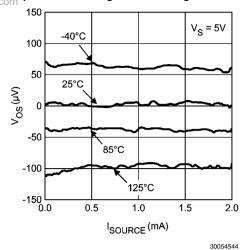

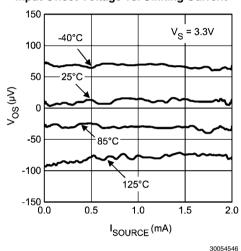

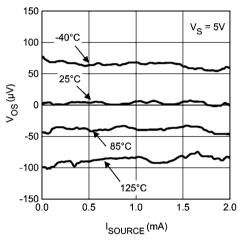

### Input Offset Voltage vs. Sourcing Current

30054543

### Input Offset Voltage vs. Sourcing Current

#### . . . . .

### Input Offset Voltage vs. Sinking Current

30054545

### Input Offset Voltage vs. Sinking Current

Input Offset Voltage vs. Sinking Current

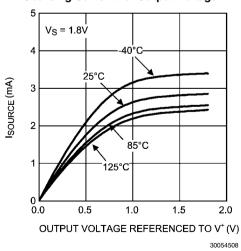

### Sourcing Current vs. Output Voltage

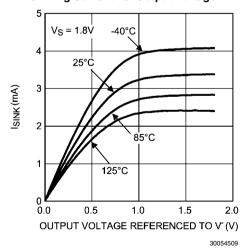

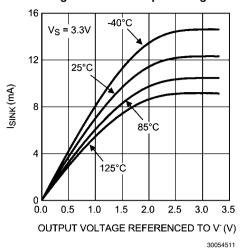

### Sinking Current vs. Output Voltage

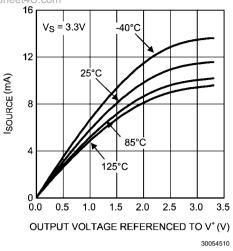

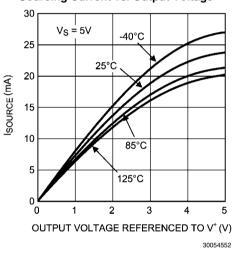

## Sourcing Current vs. Output Voltage

### Sourcing Current vs. Output Voltage

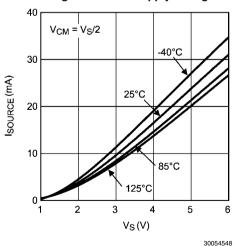

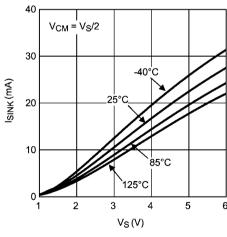

### Sourcing Current vs. Supply Voltage

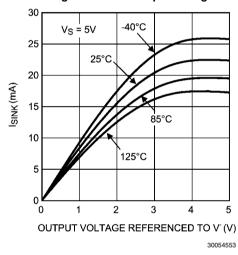

### Sinking Current vs. Output Voltage

### Sinking Current vs. Output Voltage

### Sinking Current vs. Supply Voltage

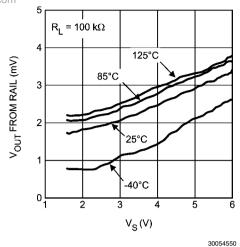

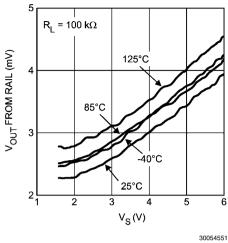

### aSheet4U.com Output Swing High vs. Supply Voltage

### Output Swing Low vs. Supply Voltage

30054514

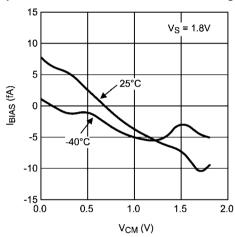

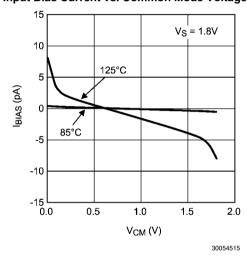

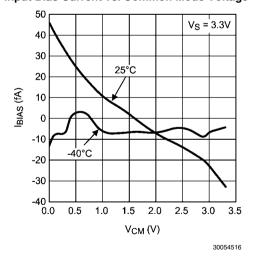

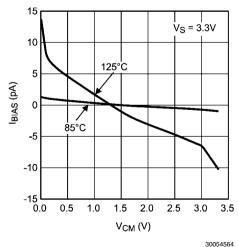

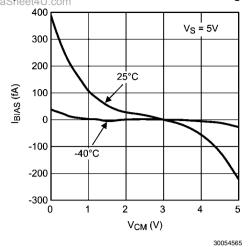

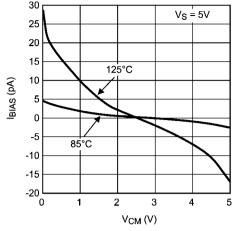

### Input Bias Current vs. Common Mode Voltage

Input Bias Current vs. Common Mode Voltage

Input Bias Current vs. Common Mode Voltage

Input Bias Current vs. Common Mode Voltage

### Input Bias Current vs. Common Mode Voltage

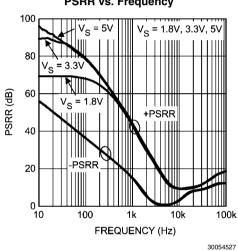

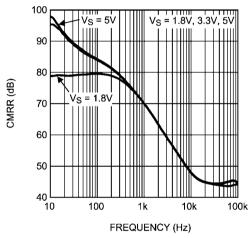

### **PSRR vs. Frequency**

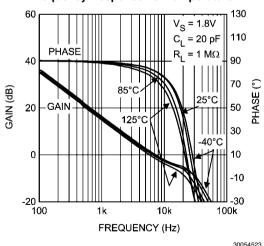

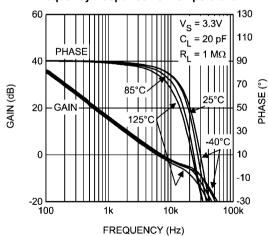

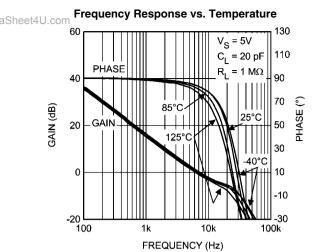

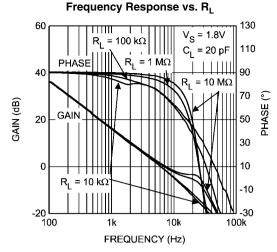

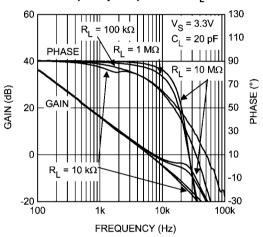

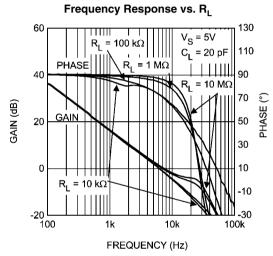

### Frequency Response vs. Temperature

### Input Bias Current vs. Common Mode Voltage

#### 30054566

### CMRR vs. Frequency

### 30054560

### Frequency Response vs. Temperature

30054520

### 30054521

30054519

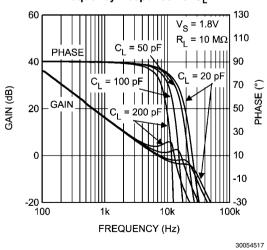

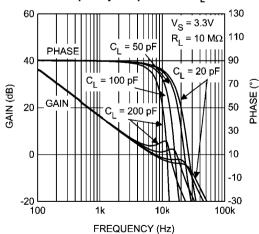

### Frequency Response vs. C<sub>L</sub>

### Frequency Response vs. C<sub>L</sub>

### www.DataSheet4U.com

### 30054513

### Voltage Noise vs. Frequency

### 0.1 to 10 Hz Time Domain Voltage Noise

### Slew Rate vs. Supply Voltage

### 0.1 to 10 Hz Time Domain Voltage Noise

### 0.1 to 10 Hz Time Domain Voltage Noise

1s/DIV

30054563

aSheet4U.com

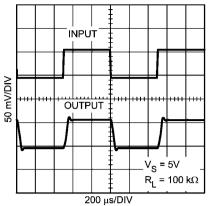

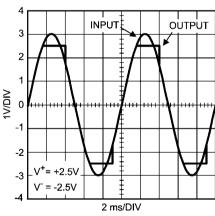

### **Small Signal Pulse Response**

30054531

30054532

### **Overload Recovery Waveform**

30054534

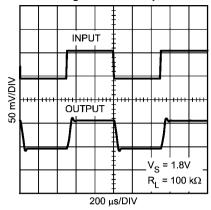

### **Small Signal Pulse Response**

30054530

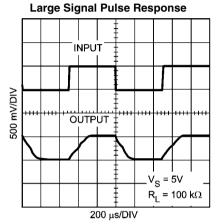

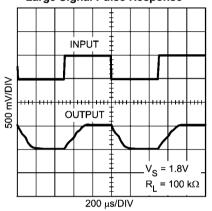

### Large Signal Pulse Response

30054533

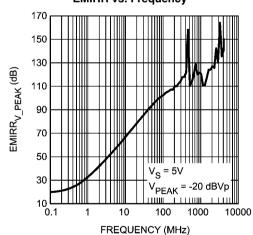

### **EMIRR vs. Frequency**

### **Application Information**

The LPV521 is fabricated with National Semiconductor's state-of-the-art VIP50 process. This proprietary process dramatically improves the performance of National Semiconductor's low-power and low-voltage operational amplifiers. The following sections showcase the advantages of the VIP50 process and highlight circuits which enable ultralow power consumption.

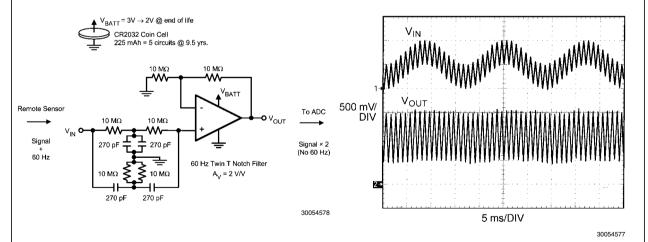

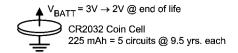

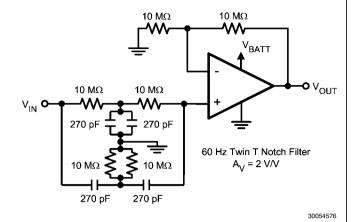

#### **60 HZ TWIN T NOTCH FILTER**

Small signals from transducers in remote and distributed sensing applications commonly suffer strong 60 Hz interference from AC power lines. The circuit of *Figure 1* notches out the 60 Hz and provides a gain  $A_V=2$  for the sensor signal represented by a 1 kHz sine wave. Similar stages may be cascaded to remove  $2^{nd}$  and  $3^{rd}$  harmonics of 60 Hz. Thanks to the nA power consumption of the LPV521, even 5 such circuits can run for 9.5 years from a small CR2032 lithium cell. These batteries have a nominal voltage of 3V and an end of life voltage of 2V. With an operating voltage from 1.6V to 5.5V the LPV521 can function over this voltage range.

The notch frequency is set by  $F_0=1/2\pi RC$ . To achieve a 60 Hz notch use  $R=10~M\Omega$  and C=270~pF. If eliminating 50 Hz noise, which is common in European systems, use  $R=11.8~M\Omega$  and C=270~pF.

The Twin T Notch Filter works by having two separate paths from  $V_{\rm IN}$  to the amplifier's input. A low frequency path through the resistors R - R and another separate high frequency path through the capacitors C - C. However, at frequencies around the notch frequency, the two paths have opposing phase angles and the two signals will tend to cancel at the amplifier's input.

To ensure that the target center frequency is achieved and to maximize the notch depth (Q factor) the filter needs to be as balanced as possible. To obtain circuit balance, while overcoming limitations of available standard resistor and capacitor values, use passives in parallel to achieve the 2C and R/2 circuit requirements for the filter components that connect to ground.

To make sure passive component values stay as expected clean board with alcohol, rinse with deionized water, and air dry. Make sure board remains in a relatively low humidity environment to minimize moisture which may increase the conductivity of board components. Also large resistors come with considerable parasitic stray capacitance which effects can be reduced by cutting out the ground plane below components of concern.

Large resistors are used in the feedback network to minimize battery drain. When designing with large resistors, resistor thermal noise, op amp current noise, as well as op amp voltage noise, must be considered in the noise analysis of the circuit. The noise analysis for the circuit in *Figure 1* can be done over a bandwidth of 5 kHz, which takes the conservative approach of overestimating the bandwidth (LPV521 typical GBW/A<sub>V</sub> is lower). The total noise at the output is approximately 800  $\mu$ Vpp, which is excellent considering the total consumption of the circuit is only 540 nA. The dominant noise terms are op amp voltage noise (550  $\mu$ Vpp), current noise through the feedback network (430  $\mu$ Vpp), and current noise through the notch filter network (280  $\mu$ Vpp). Thus the total circuit's noise is below 1/2 LSB of a 10 bit system with a 2 V reference, which is 1 mV.

FIGURE 1. 60 Hz Notch Filter

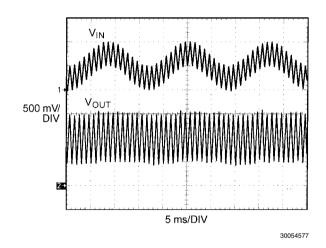

FIGURE 2. 60 Hz Notch Filter Waveform

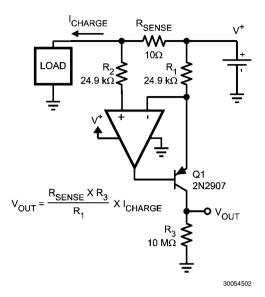

### **BATTERY CURRENT SENSING**

The rail-to-rail common mode input range and the very low quiescent current make the LPV521 ideal to use in high side and low side battery current sensing applications. The high side current sensing circuit in Figure 3 is commonly used in a battery charger to monitor the charging current in order to prevent over charging. A sense resistor  $\mathbf{R}_{\text{SENSE}}$  is connected in series with the battery. The theoretical output voltage of the circuit is  $V_{OUT} = [(R_{SENSE} \times R_3) / R_1] \times I_{CHARGE}$ . In reality, however, due to the finite Current Gain,  $\beta$ , of the transistor the current that travels through R<sub>3</sub> will not be I<sub>CHARGE</sub>, but instead, will be  $\alpha \times I_{CHARGE}$  or  $\beta/(\beta+1) \times I_{CHARGE}$ . A Darlington pair can be used to increase the  $\beta$  and performance of the measuring circuit. Using the components shown in Figure 3 will result in  ${

m V_{OUT}}$  pprox 4000  ${

m \Omega}$   $\times$  I<sub>CHARGE</sub>. This is ideal to amplify a 1 mA  $I_{CHARGE}$  to near full scale of an ADC with  $V_{REF}$  at 4.1V. A resistor, R2 is used at the non-inverting input of the amplifier, with the same value as R1 to minimize offset voltage. Selecting values per Figure 3 will limit the current traveling through the  $R_1 - Q1 - R_3$  leg of the circuit to under 1  $\mu A$  which is on the same order as the LPV521 supply current. Increasing resistors R<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub> will decrease the measuring circuit supply current and extend battery life. Decreasing R<sub>SENSE</sub> will minimize error due to resistor tolerance, however, this will also decrease  $V_{SENSE} = I_{CHARGE} \times R_{SENSE}$ , and in turn the amplifier offset voltage will have a more significant contribution to the total error of the circuit. With the components shown in *Figure 3* the measurement circuit supply current can be kept below 1.5  $\mu$ A and measure 100  $\mu$ A to 1 mA..

FIGURE 3. High Side Current Sensing

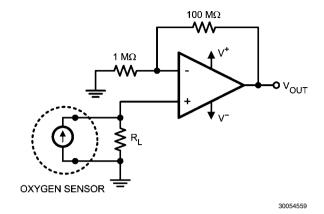

#### PORTABLE GAS DETECTION SENSOR

Gas sensors are used in many different industrial and medical applications. They generate a current which is proportional to the percentage of a particular gas sensed in an air sample. This current goes through a load resistor and the resulting voltage drop is measured. Depending on the sensed gas and sensitivity of the sensor, the output current can be in the order of tens of microamperes to a few milliamperes. Gas sensor datasheets often specify a recommended load resistor value or they suggest a range of load resistors to choose from.

Oxygen sensors are used when air quality or oxygen delivered to a patient needs to be monitored. Fresh air contains 20.9% oxygen. Air samples containing less than 18% oxygen are considered dangerous. Oxygen sensors are also used in industrial applications where the environment must lack oxygen. An example is when food is vacuum packed. There are two main categories of oxygen sensors, those which sense oxygen when it is abundantly present (i.e. in air or near an oxygen tank) and those which detect traces of oxygen in ppm. Figure 4 shows a typical circuit used to amplify the output of an oxygen detector. The LPV521 makes an excellent choice for this application as it only draws 345 nA of current and operates on supply voltages down to 1.6V. This application detects oxygen in air. The oxygen sensor outputs a known current through the load resistor. This value changes with the amount of oxygen present in the air sample. Oxygen sensors usually recommend a particular load resistor value or specify a range of acceptable values for the load resistor. Oxygen sensors typically have a life of one to two years. The use of the nanopower LPV521 means minimal power usage by the op amp and it enhances the battery life. With the components shown in *Figure 4* the circuit can consume less than 0.5 µA of current ensuring that even batteries used in compact portable electronics, with low mAh charge ratings, could last beyond the life of the oxygen sensor. The precision specifications of the LPV521, such as its very low offset voltage, low  ${\sf TCV}_{\sf OS}$ , low input bias current, high CMRR, and high PSRR are other factors which make the LPV521 a great choice for this application.

FIGURE 4. Precision Oxygen Sensor

#### **INPUT STAGE**

The LPV521 has a rail-to-rail input which provides more flexibility for the system designer. Rail-to-rail input is achieved by using in parallel, one PMOS differential pair and one NMOS differential pair. When the common mode input voltage ( $V_{CM}$ ) is near V+, the NMOS pair is on and the PMOS pair is off. When  $V_{CM}$  is near V-, the NMOS pair is off and the PMOS pair is on. When  $V_{CM}$  is between V+ and V-, internal logic decides how much current each differential pair will get. This special logic ensures stable and low distortion amplifier operation within the entire common mode voltage range.

Because both input stages have their own offset voltage ( $V_{OS}$ ) characteristic, the offset voltage of the LPV521 becomes a function of  $V_{CM}$ .  $V_{OS}$  has a crossover point at 1.0V below V+. Refer to the ' $V_{OS}$  vs.  $V_{CM}$ ' curve in the Typical Performance Characteristics section. Caution should be taken in situations where the input signal amplitude is comparable to the  $V_{OS}$  value and/or the design requires high accuracy. In these situations, it is necessary for the input signal to avoid the crossover point. In addition, parameters such as PSRR and CMRR which involve the input offset voltage will also be affected by changes in  $V_{CM}$  across the differential pair transition region.

### **OUTPUT STAGE**

The LPV521 output voltage swings 3 mV from rails at 3.3V supply, which provides the maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

The LPV521 Maximum Output Voltage Swing defines the maximum swing possible under a particular output load. The LPV521 output swings 50 mV from the rail at 5V supply with an output load of 100  $k\Omega$ .

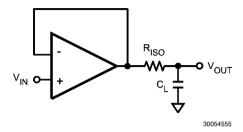

### **DRIVING CAPACITIVE LOAD**

The LPV521 is internally compensated for stable unity gain operation, with a 6.2 kHz typical gain bandwidth. However, the unity gain follower is the most sensitive configuration to capacitive load. The combination of a capacitive load placed at the output of an amplifier along with the amplifier's output impedance creates a phase lag, which reduces the phase margin of the amplifier. If the phase margin is significantly reduced, the response will be under damped which causes

peaking in the transfer and, when there is too much peaking, withe optamp might start oscillating.

In order to drive heavy capacitive loads, an isolation resistor,  $R_{\rm ISO}$ , should be used, as shown in *Figure 5*. By using this isolation resistor, the capacitive load is isolated from the amplifier's output. The larger the value of  $R_{\rm ISO}$ , the more stable the amplifier will be. If the value of  $R_{\rm ISO}$  is sufficiently large, the feedback loop will be stable, independent of the value of  $C_{\rm L}$ . However, larger values of  $R_{\rm ISO}$  result in reduced output swing and reduced output current drive.

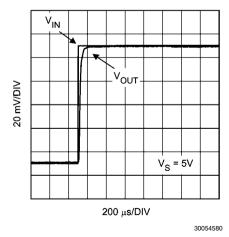

FIGURE 5. Resistive Isolation of Capacitive Load

Recommended minimum values for  $R_{ISO}$  are given in the following table, for 5V supply. Figure 6 shows the typical response obtained with the  $C_L = 50$  pF and  $R_{ISO} = 154$  k $\Omega$ . The other values of  $R_{ISO}$  in the table were chosen to achieve similar dampening at their respective capacitive loads. Notice that for the LPV521 with larger  $C_L$  a smaller  $R_{ISO}$  can be used for stability. However, for a given  $C_L$  a larger  $R_{ISO}$  will provide a more damped response. For capacitive loads of 20 pF and below no isolation resistor is needed.

| C <sub>L</sub> | R <sub>ISO</sub> |

|----------------|------------------|

| 0 – 20 pF      | not needed       |

| 50 pF          | 154 kΩ           |

| 100 pF         | 118 kΩ           |

| 500 pF         | 52.3 kΩ          |

| 1 nF           | 33.2 kΩ          |

| 5 nF           | 17.4 kΩ          |

| 10 nF          | 13.3 kΩ          |

FIGURE 6. Step Response

#### **EMI SUPPRESSION**

The near-ubiquity of cellular, bluetooth, and Wi-Fi signals and the rapid rise of sensing systems incorporating wireless radios make electromagnetic interference (EMI) an evermore important design consideration for precision signal paths. Though RF signals lie outside the op amp band, RF carrier switching can modulate the DC offset of the op amp. Also some common RF modulation schemes can induce down-converted components. The added DC offset and the induced signals are amplified with the signal of interest and thus corrupt the measurement. The LPV521 uses on chip filters to reject these unwanted RF signals at the inputs and power supply pins; thereby preserving the integrity of the precision signal path.

Twisted pair cabling and the active front-end's common-mode rejection provide immunity against low frequency noise (i.e. 60 Hz or 50 Hz mains) but are ineffective against RF interference. Even a few centimeters of PCB trace and wiring for sensors located close to the amplifier can pick up significant 1 GHz RF. The integrated EMI filters of the LPV521 reduce or eliminate external shielding and filtering requirements, thereby increasing system robustness. A larger EMIRR means more rejection of the RF interference. For more information on EMIRR, please refer to AN-1698.

### **POWER SUPPLIES AND LAYOUT**

The LPV521 operates from a single 1.6V to 5.5V power supply. It is recommended to bypass the power supplies with a 0.1  $\mu\text{F}$  ceramic capacitor placed close to the V+ and V- pins. Ground layout improves performance by decreasing the amount of stray capacitance and noise at the op amp's inputs and outputs. To decrease stray capacitance, minimize PC board trace lengths and resistor leads, and place external components close to the op amps' pins.

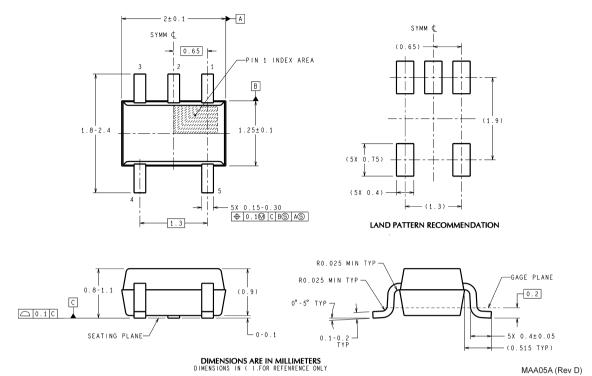

## Physical Dimensions inches (millimeters) unless otherwise noted

5-Pin SC-70 NS Package Number MAA05A

| www.DataSheet4U.com | Notes | LPV521 |

|---------------------|-------|--------|

|                     |       | -<br>  |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support                  |                                |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com