## Precision, Wide Voltage Range, Gain Selectable Funnel Amplifier

#### **FEATURES**

- Precision Attenuation: Gain = 0.1, 0.2, 0.25

- ±255V Common Mode Voltage Range

- 105dB Minimum CMRR (Gain = 0.1)

- 0.006% (60ppm) Maximum Gain Error

- 1ppm/°C Maximum Gain Error Drift

- 2ppm Maximum Gain Nonlinearity

- Wide Supply Voltage Range: 3.3V to 50V

- Rail-to-Rail Output

- 350µA Supply Current

- 80µV Maximum Op Amp Offset Voltage

- 1MHz –3dB Bandwidth (Gain = 0.1)

- Low Power Shutdown: 20µA

- Space-Saving MSOP and DFN Packages

#### **APPLICATIONS**

- High Voltage to Low Voltage Level Translation

- ADC Driver

- Bidirectional Wide Common Mode Range Voltage and Current Sensing

- Industrial Data-Acquisition Front-Ends

- Replacement for Isolation Circuits

- Differential to Single-Ended Conversion

All registered trademarks and trademarks are the property of their respective owners.

#### DESCRIPTION

The LT®1997-2 is an attenuating (funnel) difference amplifier that can be used to translate large differential signals to the low voltage range compatible with ADCs. It combines a precision operational amplifier with highly-matched resistors to form a one-chip solution to attenuate and level shift voltages accurately using no external components. It comes with three standard pin-selectable gain options (0.1, 0.2 and 0.25), which can be further combined to form gains from 0.0455 to 0.55 (attenuations of 1.82 to 22) with accuracy of 0.006% (60ppm). The LT1997-2 also works across a very wide input common-mode voltage range (±255V), enabling robust operation in demanding industrial environments. Its excellent resistor matching results in a common mode rejection ratio of greater than 105dB.

The resistors maintain their excellent matching over temperature; the matching temperature coefficient is guaranteed less than 1ppm/°C. The resistors are extremely linear with voltage, resulting in a gain nonlinearity of less than 2ppm.

The LT1997-2 is fully specified at 5V and ±15V supplies and from –40°C to 125°C. The device is available in space saving 16-lead MSOP and 4mm × 4mm DFN14 packages.

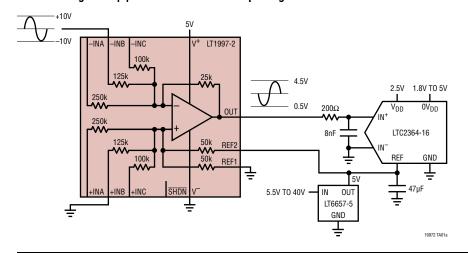

## TYPICAL APPLICATION

Interfacing a 20V<sub>P-P</sub> Ground-Referenced Input Signal to a 5V ADC

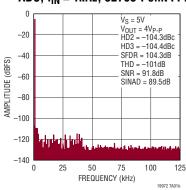

LT1997-2 Driving LTC2364-16, ADC, f<sub>IN</sub> = 1kHz, 32768-Point FFT

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltages (V+ to V <sup>-</sup> ) | 60V                                  |

|-----------------------------------------|--------------------------------------|

| +INA, -INA, +INB, -INB,                 |                                      |

| +INC, -INC (Note 2)                     | V <sup>-</sup> ±270V                 |

| REF, REF1, REF2                         | $(V^{-} + 60V)$ to $(V^{-} - 0.3V)$  |

| SHDN                                    | $(V^{+} + 0.3V)$ to $(V^{-} - 0.3V)$ |

| Output Current (Continuous)             | (Note 6)50mÁ                         |

| <b>Output Short-Circuit Duration</b>    | ·                                    |

| (Note 3)                                | Thermally Limited                    |

| Temperature Range (Notes 4, 5)  |                 |

|---------------------------------|-----------------|

| LT1997I-2                       | 40 to 85°C      |

| LT1997H-2                       | 40 to 125°C     |

| Maximum Junction Temperature    | 150°C           |

| Storage Temperature Range       | 65 to 150°C     |

| MSOP Lead Temperature (Solderin | g, 10 sec)300°C |

|                                 |                 |

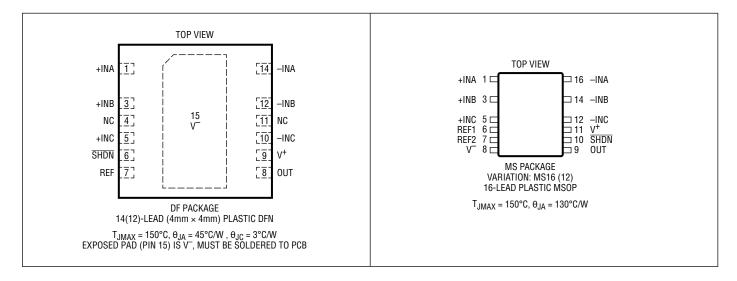

### PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | NG* PACKAGE DESCRIPTION SPECIFIED TEMPE |                |

|------------------|-------------------|---------------|-----------------------------------------|----------------|

| LT1997IDF-2#PBF  | LT1997IDF-2#TRPBF | 19972         | 14-Lead (4mm × 4mm) Plastic DFN         | -40°C to 85°C  |

| LT1997HDF-2#PBF  | LT1997HDF-2#TRPBF | 19972         | 14-Lead (4mm × 4mm) Plastic DFN         | -40°C to 125°C |

| LT1997IMS-2#PBF  | LT1997IMS-2#TRPBF | 19972         | 16-Lead Plastic MSOP                    | -40°C to 85°C  |

| LT1997HMS-2#PBF  | LT1997HMS-2#TRPBF | 19972         | 16-Lead Plastic MSOP                    | -40°C to 125°C |

<sup>\*</sup>The temperature grade is identified by a label on the shipping container. Consult ADI Marketing for parts specified with wider operating temperature ranges. Parts ending with PBF are RoHS and WEEE compliant.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, $-40^{\circ}C < T_A < 85^{\circ}C$ for I-grade parts, $-40^{\circ}C < T_A < 125^{\circ}C$ for H-grade parts, otherwise specifications are at $T_A = 25^{\circ}C$ . Difference Amplifier Configuration, $V^+ = 15V$ , $V^- = -15V$ , $V_{CM} = V_{OUT} = V_{REF} = V_{REF1} = V_{REF2} = 0V$ . $V_{CMOP}$ is the common mode voltage of the internal op amp.

| SYMBOL                   | PARAMETER                                                        | CONDITIONS                                          |   | MIN                  | TYP                 | MAX               | UNITS          |

|--------------------------|------------------------------------------------------------------|-----------------------------------------------------|---|----------------------|---------------------|-------------------|----------------|

| $\Delta G$               | Gain Error                                                       | V <sub>OUT</sub> = ±2.8V<br>G = 0.1                 | • |                      | ±0.001              | ±0.006<br>±0.008  | %<br>%         |

|                          |                                                                  | V <sub>OUT</sub> = ±5.6V<br>G = 0.2                 | • |                      | ±0.001              | ±0.006<br>±0.008  | %<br>%         |

|                          |                                                                  | V <sub>OUT</sub> = ±7V<br>G = 0.25                  | • |                      | ±0.001              | ±0.006<br>±0.008  | %<br>%         |

| $\Delta G/\Delta T$      | Gain Drift vs Temperature (Note 6)                               | $V_{OUT} = \pm 7V$                                  | • |                      | ±0.2                | ±1                | ppm/°C         |

| GNL                      | Gain Nonlinearity                                                | $V_{OUT} = \pm 7V$                                  | • |                      | ±1                  | ±2<br>±3          | ppm<br>ppm     |

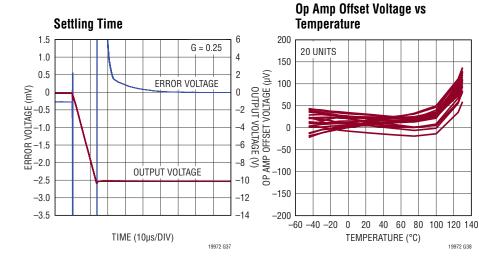

| V <sub>OS</sub>          | Op Amp Offset Voltage (Note 9)                                   | $V^- < V_{CMOP} < V^+ - 1.75V$                      | • |                      | ±20                 | ±80<br>±200       | μV<br>μV       |

| $\Delta V_{OS}/\Delta T$ | Op Amp Offset Voltage Drift (Note 6)                             | $V^- < V_{CMOP} < V^+ - 1.75V$                      | • |                      | ±0.5                | ±1.5              | μV/°C          |

| I <sub>B</sub>           | Op Amp Input Bias Current                                        | $V^- + 0.25V < V_{CMOP} < V^+ - 1.75V$              | • | <i>–</i> 5<br>−15    | ±2                  | 5<br>15           | nA<br>nA       |

| I <sub>OS</sub>          | Op Amp Input Offset Current                                      | $V^- + 0.25V < V_{CMOP} < V^+ - 1.75V$              | • | −3<br>−10            | ±0.5                | 3<br>10           | nA<br>nA       |

| R <sub>IN</sub>          | Input Impedance (Note 8)                                         | Common Mode<br>G = 0.1<br>G = 0.2<br>G = 0.25       | • | 115<br>63<br>52      | 137.5<br>75<br>62.5 | 160<br>87<br>73   | kΩ<br>kΩ<br>kΩ |

|                          |                                                                  | Differential     G = 0.1     G = 0.2     G = 0.25   | • | 420<br>210<br>168    | 500<br>250<br>200   | 580<br>290<br>232 | kΩ<br>kΩ<br>kΩ |

| CMRR                     | Common Mode Rejection Ratio,<br>Referred to Output, MS16 Package | $G = 0.1, V_{CM} = \pm 28V$                         | • | 105<br>103           | 120                 |                   | dB<br>dB       |

|                          |                                                                  | $G = 0.2, V_{CM} = \pm 28V$                         | • | 101<br>99            | 118                 |                   | dB<br>dB       |

|                          |                                                                  | G = 0.25, V <sub>CM</sub> = ±28V                    | • | 101<br>98            | 118                 |                   | dB<br>dB       |

| CMRR                     | Common Mode Rejection Ratio,<br>Referred to Output, DF14 Package | G = 0.1, V <sub>CM</sub> = ±28V                     | • | 103<br>101           | 118                 |                   | dB<br>dB       |

|                          |                                                                  | $G = 0.1$ , $V_{CM} = \pm 255V$ , $V_{S} = \pm 25V$ | • | 103<br>101           | 118                 |                   | dB<br>dB       |

|                          |                                                                  | G = 0.2, V <sub>CM</sub> = ±28V                     | • | 99<br>97             | 116                 |                   | dB<br>dB       |

|                          |                                                                  | $G = 0.2, V_{CM} = \pm 140V, V_{S} = \pm 25V$       | • | 99<br>97             | 116                 |                   | dB<br>dB       |

|                          |                                                                  | G = 0.25, V <sub>CM</sub> = ±28V                    | • | 99<br>97             | 116                 |                   | dB<br>dB       |

|                          |                                                                  | $G = 0.25, V_{CM} = \pm 115V, V_{S} = \pm 25V$      | • | 99<br>97             | 116                 |                   | dB<br>dB       |

| V <sub>CM</sub>          | Input Voltage Range (Note 7)                                     | +INA/-INA<br>+INB/-INB<br>+INC/-INC                 | • | -255<br>-140<br>-115 |                     | 255<br>140<br>115 | V<br>V<br>V    |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range,  $-40^{\circ}\text{C} < \text{T}_A < 85^{\circ}\text{C}$  for I-grade parts,  $-40^{\circ}\text{C} < \text{T}_A < 125^{\circ}\text{C}$  for H-grade parts, otherwise specifications are at  $\text{T}_A = 25^{\circ}\text{C}$ . Difference Amplifier Configuration,  $\text{V}^+ = 15\text{V}$ ,  $\text{V}^- = -15\text{V}$ ,  $\text{V}_{\text{CM}} = \text{V}_{\text{OUT}} = \text{V}_{\text{REF}} = \text{V}_{\text{REF}} = \text{V}_{\text{REF}} = 0\text{V}$ .  $\text{V}_{\text{CMOP}}$  is the common mode voltage of the internal op amp.

| SYMBOL            | PARAMETER                                                                                     | CONDITIONS                                                                                                                                                                                                                                                       |   | MIN      | TYP              | MAX                    | UNITS                                                       |

|-------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------------|------------------------|-------------------------------------------------------------|

| ΔR/R              | $\frac{\Delta R}{R} = \frac{R_{REF1} - R_{REF2}}{\left(\frac{R_{REF1} + R_{REF2}}{2}\right)}$ | Available in MS16 Package Only                                                                                                                                                                                                                                   | • |          | ±0.002           | ±0.009<br>±0.011       | %<br>%                                                      |

| PSRR              | Power Supply Rejection Ratio (Note 9)                                                         | $V_S = \pm 1.65V$ to $\pm 25V$ , $V_{CM} = V_{OUT} = Mid-Supply$                                                                                                                                                                                                 | • | 114      | 124              |                        | dB                                                          |

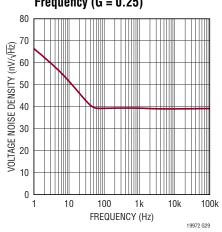

| e <sub>ni</sub>   | Output Noise Voltage Density                                                                  | f = 1kHz<br>G = 0.1<br>G = 0.2<br>G = 0.25                                                                                                                                                                                                                       |   |          | 37<br>39<br>40   |                        | nV/√Hz<br>nV/√Hz<br>nV/√Hz                                  |

|                   | Output Noise Voltage                                                                          | f = 0.1Hz to 10Hz<br>G = 0.1<br>G = 0.2<br>G = 0.25                                                                                                                                                                                                              |   |          | 0.9<br>0.95<br>1 |                        | μV <sub>P-P</sub><br>μV <sub>P-P</sub><br>μV <sub>P-P</sub> |

| V <sub>0L</sub>   | Output Voltage Swing Low (Referred to V <sup>-</sup> )                                        | No Load<br>I <sub>SINK</sub> = 5mA                                                                                                                                                                                                                               | • |          | 50<br>280        | 150<br>500             | mV<br>mV                                                    |

| V <sub>OH</sub>   | Output Voltage Swing High (Referred to V <sup>+</sup> )                                       | No Load<br>I <sub>SOURCE</sub> = 5mA                                                                                                                                                                                                                             | • |          | 50<br>450        | 150<br>900             | mV<br>mV                                                    |

| I <sub>SC</sub>   | Short-Circuit Output Current                                                                  | $50\Omega$ to V <sup>+</sup> $50\Omega$ to V <sup>-</sup>                                                                                                                                                                                                        | • | 10<br>10 | 30<br>32         |                        | mA<br>mA                                                    |

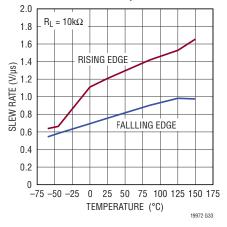

| SR                | Slew Rate                                                                                     | $\Delta V_{OUT} = \pm 7V$                                                                                                                                                                                                                                        | • | 0.45     | 0.75             |                        | V/µs                                                        |

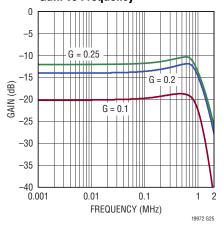

| BW                | Small Signal –3dB Bandwidth                                                                   | G = 0.1<br>G = 0.2<br>G = 0.25                                                                                                                                                                                                                                   |   |          | 1<br>1.2<br>1.1  |                        | MHz<br>MHz<br>MHz                                           |

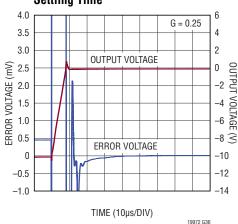

| t <sub>S</sub>    | Settling Time                                                                                 | $ G = 0.1 \\ 0.1\%,  \Delta V_{OUT} = 10V \\ 0.01\%,  \Delta V_{OUT} = 10V $                                                                                                                                                                                     |   |          | 15<br>19         |                        | μs<br>μs                                                    |

|                   |                                                                                               | $\begin{tabular}{ll} $G = 0.2$ & 0.1\%, $\Delta V_{OUT} = 10V$ & \\ $0.01\%, $\Delta V_{OUT} = 10V$ & \\ \end{tabular}$                                                                                                                                          |   |          | 16.9<br>20.6     |                        | μs<br>μs                                                    |

|                   |                                                                                               | $ \begin{cases} G = 0.25 \\ 0.1\%,  \Delta V_{OUT} = 10V \\ 0.01\%,  \Delta V_{OUT} = 10V \end{cases} $                                                                                                                                                          |   |          | 17.1<br>20.9     |                        | μs<br>μs                                                    |

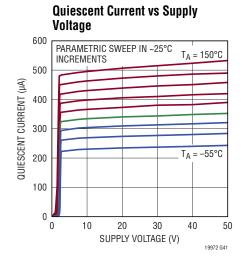

| V <sub>S</sub>    | Supply Voltage                                                                                |                                                                                                                                                                                                                                                                  | • | 3<br>3.3 |                  | 50<br>50               | V                                                           |

| $t_{ON}$          | Turn-On Time                                                                                  |                                                                                                                                                                                                                                                                  |   |          | 16               |                        | μs                                                          |

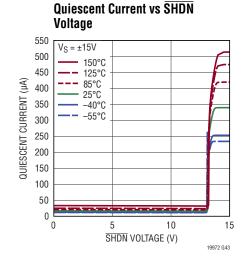

| $V_{IL}$          | SHDN Input Logic Low (Referred to V+)                                                         |                                                                                                                                                                                                                                                                  | • |          |                  | -2.5                   | V                                                           |

| V <sub>IH</sub>   | SHDN Input Logic High (Referred to V+)                                                        |                                                                                                                                                                                                                                                                  | • | -1.2     |                  |                        | V                                                           |

| I <sub>SHDN</sub> | SHDN Pin Current                                                                              |                                                                                                                                                                                                                                                                  | • |          | -10              | -15                    | μA                                                          |

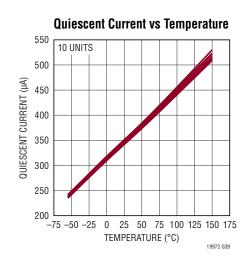

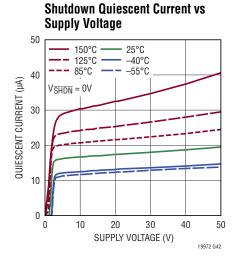

| I <sub>S</sub>    | Supply Current                                                                                | $ \begin{array}{l} \text{Active, } V_{\overline{SHDN}} \geq V^+ - 1.2V \\ \text{Active, } V_{\overline{SHDN}} \geq V^+ - 1.2V \\ \text{Shutdown, } V_{\overline{SHDN}} \leq V^+ - 2.5V \\ \text{Shutdown, } V_{\overline{SHDN}} \leq V^+ - 2.5V \\ \end{array} $ | • |          | 350<br>20        | 400<br>600<br>25<br>70 | μΑ<br>μΑ<br>μΑ                                              |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range,  $-40^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$  for I-grade parts,  $-40^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$  for H-grade parts, otherwise specifications are at  $T_A = 25^{\circ}\text{C}$ . Difference Amplifier Configuration,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{OUT} = V_{REF} = V_{REF1} = V_{REF2} = \text{Mid-Supply. } V_{CMOP}$  is the common mode voltage of the internal op amp.

| SYMBOL                   | PARAMETER                                                                                                                      | CONDITIONS                                                          |   | MIN               | TYP                 | MAX               | UNITS                      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---|-------------------|---------------------|-------------------|----------------------------|

| $\Delta G$               | Gain Error                                                                                                                     | V <sub>OUT</sub> = 1V to 4V<br>G = 0.1                              | • |                   | ±0.001              | ±0.006<br>±0.008  | %<br>%                     |

|                          |                                                                                                                                | G = 0.2                                                             | • |                   | ±0.001              | ±0.006<br>±0.008  | %<br>%                     |

|                          |                                                                                                                                | G = 0.25                                                            | • |                   | ±0.001              | ±0.006<br>±0.008  | %<br>%                     |

| $\Delta G/\Delta T$      | Gain Drift vs Temperature (Note 6)                                                                                             | V <sub>OUT</sub> = 1V to 4V                                         | • |                   | ±0.2                | ±1                | ppm/°C                     |

| GNL                      | Gain Nonlinearity                                                                                                              | V <sub>OUT</sub> = 1V to 4V                                         |   |                   | ±1                  |                   | ppm                        |

| V <sub>OS</sub>          | Op Amp Offset Voltage (Note 9)                                                                                                 | V <sup>-</sup> < V <sub>CMOP</sub> < V <sup>+</sup> – 1.75V         | • |                   | ±20                 | ±80<br>±200       | μV<br>μV                   |

| $\Delta V_{OS}/\Delta T$ | Op Amp Offset Voltage Drift (Note 6)                                                                                           | $V^- < V_{CMOP} < V^+ - 1.75V$                                      | • |                   | ±0.5                | ±1.5              | μV/°C                      |

| I <sub>B</sub>           | Op Amp Input Bias Current                                                                                                      | V <sup>-</sup> + 0.25V < V <sub>CMOP</sub> < V <sup>+</sup> – 1.75V | • | −5<br>−15         | ±2                  | 5<br>15           | nA<br>nA                   |

| I <sub>OS</sub>          | Op Amp Input Offset Current                                                                                                    | V <sup>-</sup> + 0.25V < V <sub>CMOP</sub> < V <sup>+</sup> - 1.75V | • | −3<br>−10         | ±0.5                | 3<br>10           | nA<br>nA                   |

| R <sub>IN</sub>          | Input Impedance (Note 8)                                                                                                       | Common Mode<br>G = 0.1<br>G = 0.2<br>G = 0.25                       | • | 115<br>63<br>52   | 137.5<br>75<br>62.5 | 160<br>87<br>73   | kΩ<br>kΩ<br>kΩ             |

|                          |                                                                                                                                | Differential     G = 0.1     G = 0.2     G = 0.25                   | • | 420<br>210<br>168 | 500<br>250<br>200   | 580<br>290<br>232 | kΩ<br>kΩ<br>kΩ             |

| CMRR                     | Common Mode Rejection Ratio, Referred to Output, MS16 Package                                                                  | G = 0.1, V <sub>CM</sub> = -25V to 10.75V                           | • | 104<br>102        | 120                 |                   | dB<br>dB                   |

|                          |                                                                                                                                | G = 0.2, V <sub>CM</sub> = -12.5V to 7V                             | • | 100<br>98         | 118                 |                   | dB<br>dB                   |

|                          |                                                                                                                                | G = 0.25, V <sub>CM</sub> = -10V to 6.25V                           | • | 100<br>98         | 118                 |                   | dB<br>dB                   |

| CMRR                     | Common Mode Rejection Ratio, Referred to Output, DF14 Package                                                                  | G = 0.1, V <sub>CM</sub> = -25V to 10.75V                           | • | 102<br>100        | 118                 |                   | dB<br>dB                   |

|                          |                                                                                                                                | G = 0.2, V <sub>CM</sub> = -12.5V to 7V                             | • | 98<br>96          | 116                 |                   | dB<br>dB                   |

|                          |                                                                                                                                | $G = 0.25$ , $V_{CM} = -10V$ to $6.25V$                             | • | 98<br>96          | 116                 |                   | dB<br>dB                   |

| ΔR/R                     | Reference Divider Matching Error $\frac{\Delta R}{R} = \frac{R_{REF1} - R_{REF2}}{\left(\frac{R_{REF1} + R_{REF2}}{2}\right)}$ | Available in MS16 Package Only                                      | • |                   | ±0.002              | ±0.009<br>±0.011  | %<br>%                     |

| PSRR                     | Power Supply Rejection Ratio (Note 9)                                                                                          | $V_S = \pm 1.65V$ to $\pm 25V$ , $V_{CM} = V_{OUT} = Mid-Supply$    | • | 114               | 124                 |                   | dB                         |

| e <sub>ni</sub>          | Output Noise Voltage Density                                                                                                   | f = 1kHz<br>G = 0.1<br>G = 0.2<br>G = 0.25                          |   |                   | 37<br>39<br>40      |                   | nV/√Hz<br>nV/√Hz<br>nV/√Hz |

## **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating

common mode voltage of the internal op amp.

temperature range,  $-40^{\circ}$ C < T<sub>A</sub> < 85°C for I-grade parts,  $-40^{\circ}$ C < T<sub>A</sub> < 125°C for H-grade parts, otherwise specifications are at  $T_A = 25^{\circ}$ C. Difference Amplifier Configuration, V<sup>+</sup> = 5V, V<sup>-</sup> = 0V,  $V_{CM} = V_{OUT} = V_{REF} = V_{REF1} = V_{REF2} = Mid-Supply. <math>V_{CMOP}$  is the

| SYMBOL            | PARAMETER                                              | CONDITIONS                                                                                                                                                                                                           |   | MIN      | TYP              | MAX                    | UNITS                                                       |

|-------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------------|------------------------|-------------------------------------------------------------|

|                   | Output Noise Voltage                                   | f = 0.1Hz to 10Hz<br>G = 0.1<br>G = 0.2<br>G = 0.25                                                                                                                                                                  |   |          | 0.9<br>0.95<br>1 |                        | μV <sub>P-P</sub><br>μV <sub>P-P</sub><br>μV <sub>P-P</sub> |

| $V_{0L}$          | Output Voltage Swing Low (Referred to V <sup>-</sup> ) | No Load<br>I <sub>SINK</sub> = 5mA                                                                                                                                                                                   | • |          | 15<br>280        | 50<br>500              | mV<br>mV                                                    |

| V <sub>OH</sub>   | Output Voltage Swing High (Referred to V+)             | No Load<br>I <sub>SOURCE</sub> = 5mA                                                                                                                                                                                 | • |          | 15<br>450        | 50<br>800              | mV<br>mV                                                    |

| I <sub>SC</sub>   | Short-Circuit Output Current                           | 50Ω to V <sup>+</sup><br>50Ω to V <sup>-</sup>                                                                                                                                                                       | • | 10<br>10 | 30<br>28         |                        | mA<br>mA                                                    |

| SR                | Slew Rate                                              | $\Delta V_{OUT} = 3V$                                                                                                                                                                                                | • | 0.45     | 0.75             |                        | V/µs                                                        |

| BW                | Small signal –3dB Bandwidth                            | G = 0.1<br>G = 0.2<br>G = 0.25                                                                                                                                                                                       |   |          | 1<br>1.2<br>1.1  |                        | MHz<br>MHz<br>MHz                                           |

| t <sub>S</sub>    | Settling Time                                          | G = 0.1<br>0.1%, $\Delta V_{OUT} = 2V$<br>0.01%, $\Delta V_{OUT} = 2V$                                                                                                                                               |   |          | 7.5<br>11.7      |                        | μs<br>μs                                                    |

|                   |                                                        | G = 0.2<br>0.1%, $\Delta V_{OUT} = 2V$<br>0.01%, $\Delta V_{OUT} = 2V$                                                                                                                                               |   |          | 8.8<br>13.1      |                        | μs<br>μs                                                    |

|                   |                                                        | $ \begin{cases} G = 0.25 \\ 0.1\%, \ \Delta V_{OUT} = 2V \\ 0.01\%, \ \Delta V_{OUT} = 2V \end{cases} $                                                                                                              |   |          | 8.7<br>12.7      |                        | μs<br>μs                                                    |

| V <sub>S</sub>    | Supply Voltage                                         |                                                                                                                                                                                                                      | • | 3<br>3.3 |                  | 50<br>50               | V                                                           |

| t <sub>ON</sub>   | Turn-On Time                                           |                                                                                                                                                                                                                      |   |          | 22               |                        | μs                                                          |

| $V_{IL}$          | SHDN Input Logic Low (Referred to V+)                  |                                                                                                                                                                                                                      | • |          |                  | -2.5                   | V                                                           |

| V <sub>IH</sub>   | SHDN Input Logic High (Referred to V+)                 |                                                                                                                                                                                                                      | • | -1.2     |                  |                        | V                                                           |

| I <sub>SHDN</sub> | SHDN Pin Current                                       |                                                                                                                                                                                                                      | • |          | -10              | -15                    | μА                                                          |

| I <sub>S</sub>    | Supply Current                                         | $ \begin{array}{l} \text{Active, } V_{SHDN} \geq V^+ - 1.2V \\ \text{Active, } V_{SHDN} \geq V^+ - 1.2V \\ \text{Shutdown, } V_{SHDN} \leq V^+ - 2.5V \\ \text{Shutdown, } V_{SHDN} \leq V^+ - 2.5V \\ \end{array} $ | • |          | 330<br>15        | 370<br>525<br>20<br>40 | μΑ<br>μΑ<br>μΑ<br>μΑ                                        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: See Common Mode Voltage Range in the Applications Information section of this data sheet for other considerations when taking +INA/ -INA/+INB/-INB/+INC/-INC pins to ±270V.

Note 3: A heat sink may be required to keep the junction temperature below absolute maximum. This depends on the power supply, input voltages and the output current.

Note 4: The LT1997I-2 is guaranteed functional over the operating temperature range of -40°C to 85°C. The LT1997H-2 is guaranteed functional over the operating temperature range of -40°C to 125°C.

**Note 5:** The LT1997I-2 is guaranteed to meet specified performance from -40°C to 85°C. The LT1997H-2 is guaranteed to meet specified performance from -40°C to 125°C.

Note 6: This parameter is not 100% tested.

Note 7: The input voltage range is guaranteed by the ±25V CMRR tests. The Input Voltage Range numbers specified in the table guarantee that the internal op amp operates in its normal operating region. The Input voltage range can be higher if the internal op amp operates in its Over-The-Top® operating region. See Common Mode Voltage Range in the Applications Information section to determine the valid input voltage range under various operating conditions.

Note 8: Input impedance is tested by a combination of direct measurements and correlation to the CMRR and gain error tests.

Note 9: Offset voltage, offset voltage drift and PSRR are defined as referred to the internal op amp. The following shows the calculation of output offset: In the case of balanced source resistance,  $V_{OS,OLIT} = (V_{OS})$ • NOISEGAIN) +  $(I_{OS} \cdot 25k)$  +  $(I_{B} \cdot 25k \cdot (1 - R_P/R_N))$  where  $R_P$  and  $R_N$ are the total resistance at the op amp positive and negative terminal, respectively.

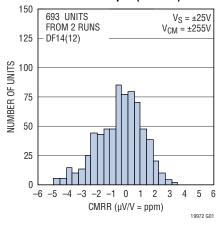

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_S = \pm 15$ V, Difference Amplifier

configuration, unless otherwise noted.

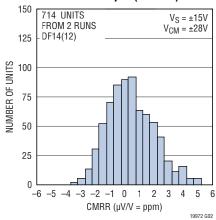

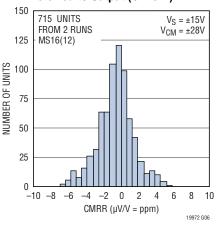

#### Typical Distribution of CMRR, Referred to Output (G = 0.1)

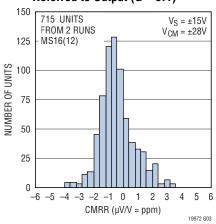

Typical Distribution of CMRR, Referred to Output (G = 0.1)

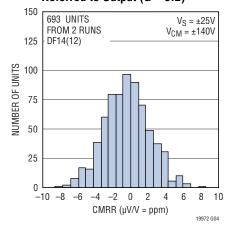

Typical Distribution of CMRR, Referred to Output (G = 0.1)

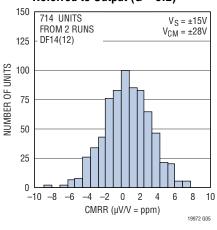

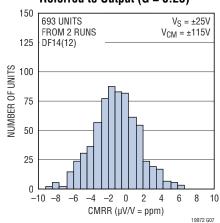

Typical Distribution of CMRR, Referred to Output (G = 0.2)

Typical Distribution of CMRR, Referred to Output (G = 0.2)

Typical Distribution of CMRR, Referred to Output (G = 0.2)

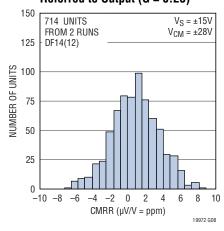

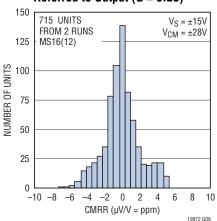

Typical Distribution of CMRR, Referred to Output (G = 0.25)

Typical Distribution of CMRR, Referred to Output (G = 0.25)

Typical Distribution of CMRR, Referred to Output (G = 0.25)

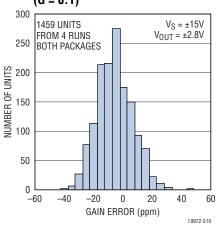

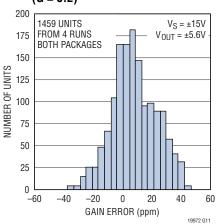

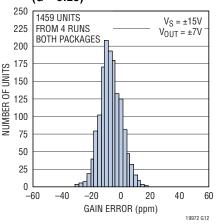

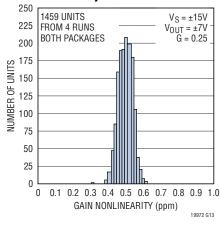

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_S = \pm 15$ V, Difference Amplifier

configuration, unless otherwise noted.

Typical Distribution of Gain Error (G = 0.2)

Typical Distribution of Gain Error (G = 0.25)

Typical Distribution of Gain Nonlinearity

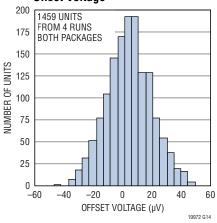

Typical Distribution of Op Amp Offset Voltage

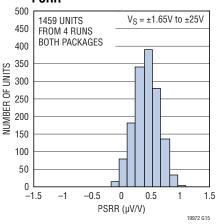

Typical Distribution of Op Amp PSRR

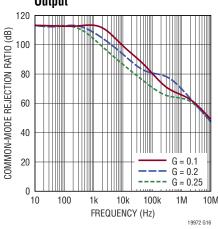

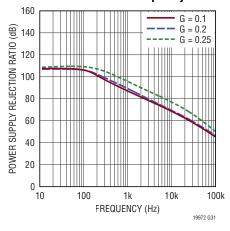

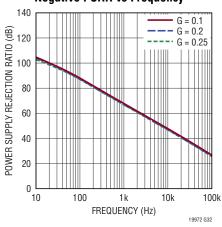

CMRR vs Frequency, Referred to Output

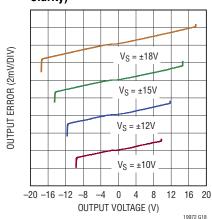

Typical Gain Error for  $R_L = 10k\Omega$ , (G = 0.25) (Curves Offset for Clarity)

Typical Gain Error for  $R_L = 5k\Omega$ , (G = 0.25) (Curves Offset for Clarity)

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , Difference Amplifier configuration, unless otherwise noted.

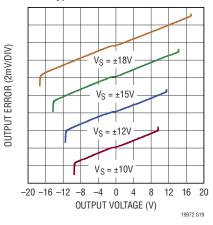

Typical Gain Error for  $R_L = 2k\Omega$ (G = 0.25) (Curves Offset for Clarity)

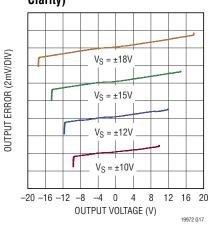

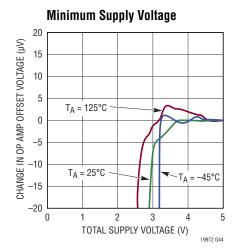

Typical Gain Error for Low Supply Voltages (G = 0.25) (Curves Offset for Clarity)

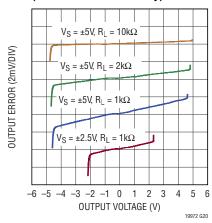

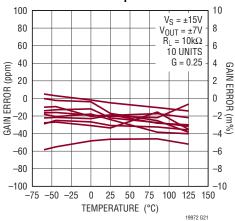

**Gain Error vs Temperature**

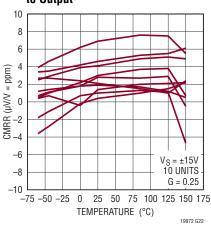

CMRR vs Temperature, Referred to Output

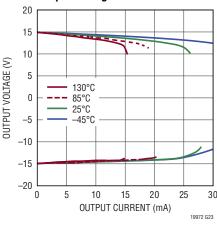

**Output Voltage vs Load Current**

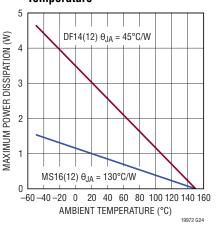

**Maximum Power Dissipation vs Temperature**

Gain vs Frequency

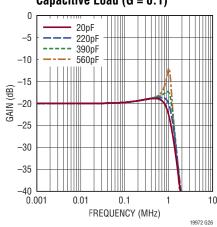

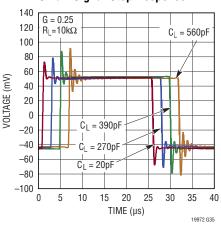

Frequency Response vs Capacitive Load (G = 0.1)

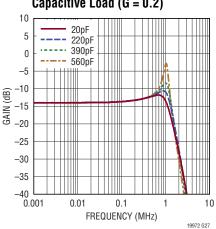

Frequency Response vs Capacitive Load (G = 0.2)

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , Difference Amplifier configuration, unless otherwise noted.

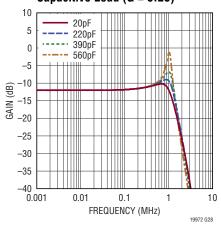

Frequency Response vs Capacitive Load (G = 0.25)

**Output Noise Density vs** Frequency (G = 0.25)

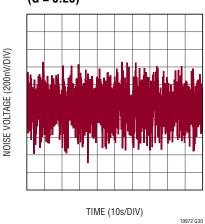

**Output 0.1Hz to 10Hz Noise** (G = 0.25)

Positive PSRR vs Frequency

**Negative PSRR vs Frequency**

Slew Rate vs Temperature

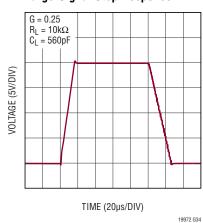

Large-Signal Step Response

**Small-Signal Step Response**

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , Difference Amplifier configuration, unless otherwise noted.

#### Thermal Shutdown vs Hysteresis 600 500 SUPPLY CURRENT (µA) 400 300 200 100 145 150 160 165 170 TEMPERATURE (°C) 19972 G40

19972 G38

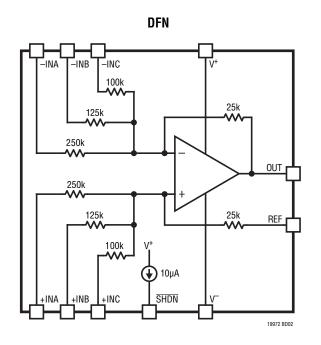

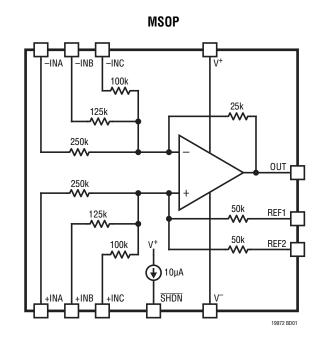

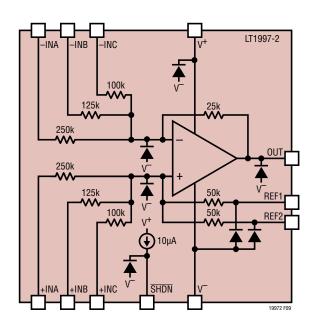

## PIN FUNCTIONS (DFN/MSOP)

V+ (Pin 9/Pin 11): Positive Supply Pin.

V<sup>-</sup> (EXPOSED PAD Pin 15/Pin 8): Negative Supply Pin.

OUT (Pin 8/Pin 9): Output Pin.

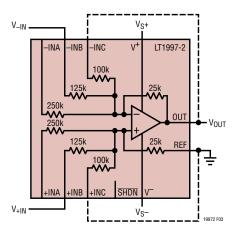

**+INA (Pin 1/Pin 1):** Noninverting Gain-of-0.1 Input Pin. Connects a 250k internal resistor to the internal op amp's noninverting input.

**+INB (Pin 3/Pin 3):** Noninverting Gain-of-0.2 Input Pin. Connects a 125k internal resistor to the internal op amp's noninverting input.

**+INC (Pin 5/Pin 5):** Noninverting Gain-of-0.25 Input Pin. Connects a 100k internal resistor to the internal op amp's noninverting input.

**-INA (Pin 14/Pin 16):** Inverting Gain-of-0.1 input Pin. Connects a 250k internal resistor to the internal op amp's inverting input.

**–INB (Pin 12/Pin 14):** Inverting Gain-of-0.2 input Pin. Connects a 125k internal resistor to the internal op amp's inverting input.

**–INC (Pin 10/Pin 12):** Inverting Gain-of-0.25 input Pin. Connects a 100k internal resistor to the internal op amp's inverting input.

**REF (Pin 7/NA):** Reference Input Pin. Sets the output level when the difference between the inputs is zero.

**REF1 (NA/Pin 6):** Reference 1 Input Pin. With REF2, sets the output level when the difference between the inputs is zero.

**REF2 (NA/Pin 7):** Reference 2 Input Pin. With REF1, sets the output level when the difference between the inputs is zero.

**SHDN** (**Pin 6/Pin 10**): Shutdown Pin. Amplifier is active when this pin is tied to V<sup>+</sup> or left floating. Pulling the pin more than 2.5V below V<sup>+</sup> causes the amplifier to enter a low power state.

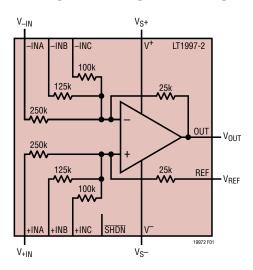

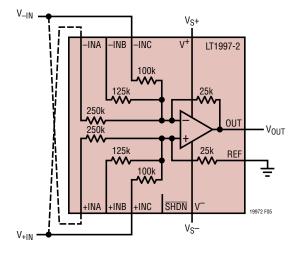

## **BLOCK DIAGRAM**

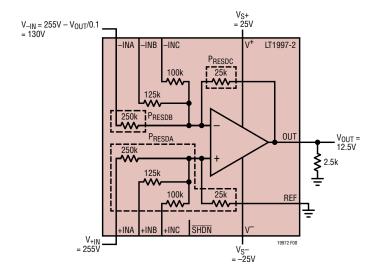

Figure 1. Difference Amplifier with Dual-Supply Operation (Gain = 0.1)

#### Introduction

The LT1997-2 is a precision, high voltage funnel amplifier combined with a highly-matched resistor network. It can easily be configured into many different gain circuits without adding external components, as it will be shown in this data sheet. The LT1997-2 provides the resistors and op amp together in a small package in order to save board space and reduce complexity. Highly accurate measurement circuits can be easily constructed with the LT1997-2. The circuits can be tailored to specific measurement applications.

#### Common Mode Voltage Range

The common mode voltage range of the LT1997-2 is set by the voltage range allowed on the LT1997-2's input pins and by the input voltage range of the internal op amp.

The internal op amp of LT1997-2 has 2 operating regions:

- a) if the common-mode voltage at the inputs of the internal op amp ( $V_{CMOP}$ ) is between  $V^-$  and  $V^+-1.75V$ , the op amp operates in its normal region;

- b) If  $V_{CMOP}$  is between  $V^+ 1.75V$  and  $V^- + 76V$ , the op amp continues to operate, but in its Over-The-Top (OTT) region with degraded performance (see Over-The-Top Operation section of this data sheet for more detail).

The LT1997-2 will not operate correctly if the common-mode voltage at the inputs of the internal op amp ( $V_{CMOP}$ )

is below  $V^-$ , but the part will not be damaged as long as  $V_{CMOP}$  is greater than  $V^- - 25V$  and the junction temperature of the LT1997-2 does not exceed 150°C.

The voltage on LT1997-2's input pins should never be higher than  $V^- + 270V$  or lower than  $V^- - 270V$  under any circumstances.

The common-mode voltage at the inputs of the internal op amp ( $V_{CMOP}$ ) is determined by the voltages on pins +INA, +INB, +INC and REF (see the Calculating Input Voltage Range section). This condition is true provided that the internal op amp's output is not clipped and feedback maintains the internal op amp's inputs at the same voltage.

In addition to the limits mentioned above, the common mode input voltage of the amplifier should be chosen so that the input resistors do not dissipate too much power. The power dissipated in a 250k resistor must be less than 1.8W. It must be less than 0.9W for the 125k resistor and less than 0.72W for the 100k resistor. For most applications, the pin voltage limitations will be reached before the resistor power limitation is reached.

#### **Calculating Input Voltage Range**

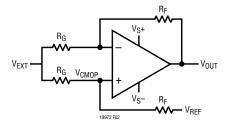

Figure 2 shows the LT1997-2 in the generalized case of a difference amplifier, with the inputs shorted for the common mode calculation. The values of  $R_F$  and  $R_G$  are dictated by how the positive inputs (+INA, +INB, +INC) and REF pin are connected.

By superposition we can write:

$$V_{CMOP} = V_{EXT} \bullet \frac{R_F}{R_F + R_G} + V_{REF} \bullet \frac{R_G}{R_F + R_G}$$

Or, solving for V<sub>FXT</sub>:

$$V_{EXT} = V_{CMOP} \bullet \left(1 + \frac{R_G}{R_F}\right) - V_{REF} \bullet \frac{R_G}{R_F}$$

But valid  $V_{CMOP}$  voltages are limited to  $V_S+-1.75V$  (or  $V_S-+76V$  for OTT) on the high side and  $V_S-$  on the low side, so:

MAX

$$V_{EXT} = (V_S + -1.75) \bullet \left(1 + \frac{R_G}{R_E}\right) - V_{REF} \bullet \frac{R_G}{R_E}$$

and:

$$\text{MIN V}_{EXT} = \left(V_S - \right) \bullet \left(1 + \frac{R_G}{R_F}\right) - V_{REF} \bullet \frac{R_G}{R_F}$$

Figure 2. Calculating the Common Mode Input Voltage Range

Exceeding the MAX V<sub>EXT</sub> limit will cause the amplifier to transition into the Over-The-Top region. The maximum input voltage for the Over-The-Top region is:

MAX

$$V_{EXTOTT} = (V_S - +76) \cdot \left(1 + \frac{R_G}{R_F}\right) - V_{REF} \cdot \frac{R_G}{R_F}$$

Keep in mind that the above MAX and MIN values for input voltage range should not exceed  $V^- \pm 270V$ , the ABSMAX voltage range specified earlier for LT1997-2's input pins.

The negative inputs (-INA, -INB, -INC) are not limited by the internal op amp common mode range ( $V_{CMOP}$ ) because they do not affect it. They are limited by the output swing of the amplifier (and obviously by the allowed voltage range for the input pins).

#### Over-The-Top Operation

When the input common mode voltage of the internal op amp ( $V_{CMOP}$ ) in the LT1997-2 is biased near or above the V<sup>+</sup> supply, the op amp is operating in the Over-The-Top (OTT) region. The op amp continues to operate with an input common mode voltage of up to 76V above V<sup>-</sup> (regardless of the positive power supply voltage V<sup>+</sup>), but its performance is degraded. The op amp's input bias currents change from under  $\pm 2nA$  to  $14\mu A$ . The op amp's input offset current rises to  $\pm 50nA$ , which adds  $\pm 1.25mV$  to the output offset voltage.

In addition, when operating in the Over-The-Top region, the differential input impedance of the internal op amp decreases from  $1M\Omega$  in normal operation to approximately  $3.7k\Omega$  in Over-The-Top operation. This resistance appears

across the summing nodes of the internal op amp and boosts noise and offset while decreasing speed. Noise and offset will increase by 80%. The bandwidth will be reduced by 45%. For more detail on Over-The-Top operation, consult the LT6015 data sheet.

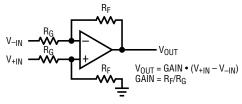

#### **Difference Amplifiers**

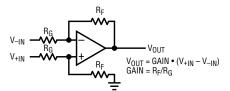

The LT1997-2 is ideally suited to be used as a difference amplifier. Figure 3 shows the basic 4-resistor difference amplifier and the LT1997-2. A difference gain of 0.2 (attenuation = 5) is shown, but can be altered by additional dashed connections. By connecting the 100k resistors in parallel with the 25k feedback resistors, the gain is reduced to 0.16 (attenuation = 6.25). Of course there are many possible gains and Figure 4 shows circuit schematics of some of those difference amplifier gains.

Note that the common mode voltage at the inputs of the internal op amp  $(V_{CMOP})$  is set by the voltages at pins +INA, +INB, +INC and REF.

DIFFERENCE AMPLIFIER CONFIGURATION

DIFFERENCE AMPLIFIER CONFIGURATION IMPLEMENTED WITH THE LT1997-2,  $R_F=25k,\ R_G=125k,\ GAIN=0.2$

ADDING THE DASHED CONNECTIONS CONNECT THE 100k RESISTOR IN PARALLEL WITH R $_{\rm F}$ , SO R $_{\rm F}$  IS REDUCED TO 20k. THE GAIN BECOMES 20k/125k = 0.16

Figure 3. The LT1997-2 Configured as a Difference Amplifier.

Gain Is Set by Connecting the Correct Resistors or Combinations of Resistors. Gain of 0.2 (Attenuation = 5) Is Shown, with Dashed Lines Modifying It to a Gain of 0.16 (Attenuation = 6.25)

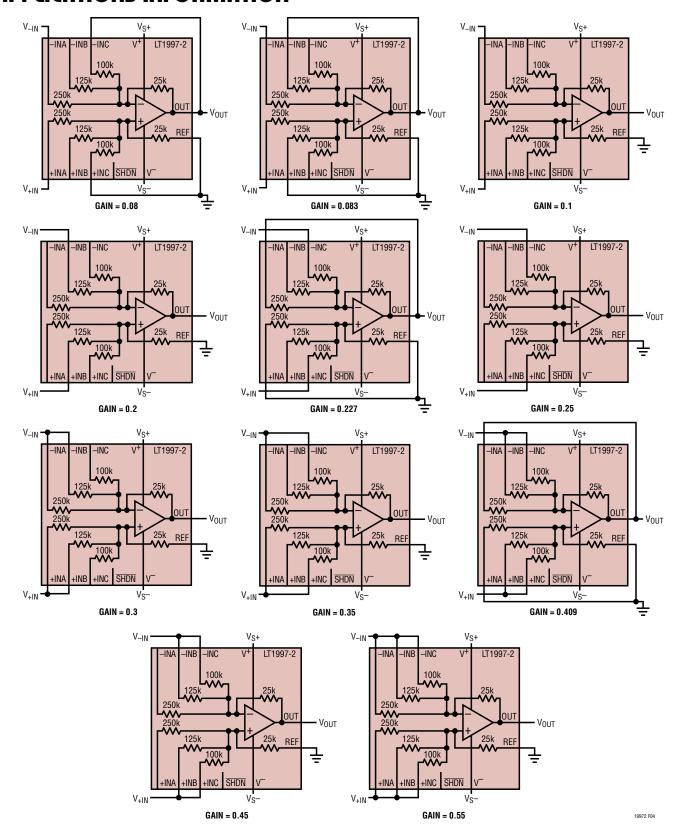

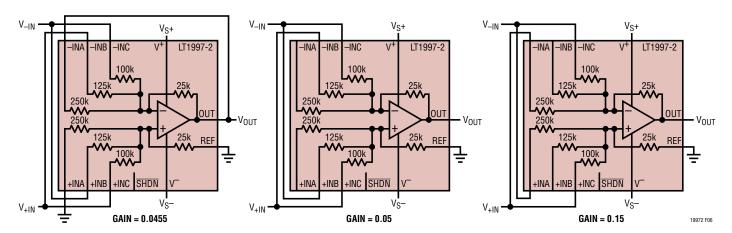

Figure 4. Many Difference Amplifier Gains Can Be Achieved by Strapping Pins

#### Difference Amplifier: Additional Gains Using Cross-Coupling

Figure 5 shows the basic difference amplifier as well as the LT1997-2 with cross-coupled inputs. The additional dashed connections reduce the differential gain from 0.25 to 0.15. Using this method, additional gains are achievable and a few example schematics of the difference amplifiers using cross-coupling are shown in Figure 6. To summarize, Table 1 shows a complete list of all difference amplifier gains (attenuations) and how they are constructed using (both conventional or cross-coupling) pin strapping. Note that there are 38 unique gains ranging from 0.0455 to 0.55 (corresponding to attenuations from 1.8182 to 22) which can be achieved with the LT1997-2 using no external components.

DIFFERENCE AMPLIFIER CONFIGURATION

DIFFERENCE AMPLIFIER CONFIGURATION IMPLEMENTED WITH THE LT1997-2,  $R_{\text{F}}$  = 25k,  $R_{\text{G}}$  = 100k, Gain = 0.25 Gain can be adjusted by cross-coupling the inputs. Making the dashed connections reduces the gain from 0.25 to 0.15

Figure 5. Cross-Coupling of the LT1997-2 Allows Additional Gains to Be Constructed

**Table 1. Difference Amplifier Gains (Attenuations)**

| lable 1. Difference Amplifier Gains (Attenuations) |             |                     |                     |            |            |  |  |

|----------------------------------------------------|-------------|---------------------|---------------------|------------|------------|--|--|

| GAIN                                               | ATTENUATION | V <sub>+IN</sub>    | V_IN                | GND (REF)  | OUT        |  |  |

| 0.0455                                             | 22          | -INB, +INC          | +INB, -INC          | +INA       | -INA       |  |  |

| 0.05                                               | 20          | -INB, +INC          | +INB, -INC          |            |            |  |  |

| 0.0556                                             | 18          | -INB, +INC          | +INB, -INC          | -INA       | +INA       |  |  |

| 0.069                                              | 14.5        | +INA                | -INA                | +INB, +INC | -INB, -INC |  |  |

| 0.08                                               | 12.5        | +INA                | -INA                | +INC       | -INC       |  |  |

| 0.0833                                             | 12          | +INA                | -INA                | +INB       | -INB       |  |  |

| 0.0952                                             | 10.5        | +INA                | -INA                | -INB, +INC | +INB, -INC |  |  |

| 0.1                                                | 10          | +INA                | -INA                |            |            |  |  |

| 0.1053                                             | 9.5         | +INA                | -INA                | +INB, -INC | -INB, +INC |  |  |

| 0.125                                              | 8           | +INA                | -INA                | -INB       | +INB       |  |  |

| 0.1333                                             | 7.5         | +INA                | -INA                | -INC       | +INC       |  |  |

| 0.1481                                             | 6.75        | +INB                | -INB                | +INA, +INC | -INA, -INC |  |  |

| 0.15                                               | 6.6667      | -INA, +INC          | +INA, -INC          |            |            |  |  |

| 0.16                                               | 6.25        | +INB                | -INB                | +INC       | -INC       |  |  |

| 0.1739                                             | 5.75        | +INB                | -INB                | -INA, +INC | +INA, -INC |  |  |

| 0.1818                                             | 5.5         | +INB                | -INB                | +INA       | -INA       |  |  |

| 0.1875                                             | 5.3333      | -INA, +INC          | +INA, -INC          | -INB       | +INB       |  |  |

| 0.1923                                             | 5.2         | +INC                | -INC                | +INA, +INB | -INA, -INB |  |  |

| 0.2                                                | 5           | +INB                | -INB                |            |            |  |  |

| 0.2083                                             | 4.8         | +INC                | -INC                | +INB       | -INB       |  |  |

| 0.2222                                             | 4.5         | +INB                | -INB                | -INA       | +INA       |  |  |

| 0.2273                                             | 4.4         | +INC                | -INC                | +INA       | -INA       |  |  |

| 0.24                                               | 4.1667      | +INA, +INB          | -INA, -INB          | +INC       | -INC       |  |  |

| 0.25                                               | 4           | +INC                | -INC                |            |            |  |  |

| 0.2667                                             | 3.75        | +INB                | -INB                | -INC       | +INC       |  |  |

| 0.2778                                             | 3.6         | +INC                | -INC                | -INA       | +INA       |  |  |

| 0.2917                                             | 3.4286      | +INA, +INC          | -INA, -INC          | +INB       | -INB       |  |  |

| 0.3                                                | 3.3333      | +INA, +INB          | -INA, -INB          |            |            |  |  |

| 0.3077                                             | 3.25        | +INB                | -INB                | -INA, -INC | +INA, +INC |  |  |

| 0.3125                                             | 3.2         | +INC                | -INC                | -INB       | +INB       |  |  |

| 0.35                                               | 2.8571      | +INA, +INC          | -INA, -INC          |            |            |  |  |

| 0.3571                                             | 2.8         | +INC                | -INC                | -INA, -INB | +INA, +INB |  |  |

| 0.4                                                | 2.5         | +INA, +INB          | -INA, -INB          | -INC       | +INC       |  |  |

| 0.4091                                             | 2.4444      | +INB, +INC          | -INB, -INC          | +INA       | -INA       |  |  |

| 0.4375                                             | 2.2857      | +INA, +INC          | -INA, -INC          | -INB       | +INB       |  |  |

| 0.45                                               | 2.2222      | +INB, +INC          | -INB, -INC          |            |            |  |  |

| 0.5                                                | 2           | +INB, +INC          | -INB, -INC          | -INA       | +INA       |  |  |

| 0.55                                               | 1.8182      | +INA, +INB,<br>+INC | -INA, -INB,<br>-INC |            |            |  |  |

Figure 6. Examples of More Difference Amplifier Gains That Can Be Achieved

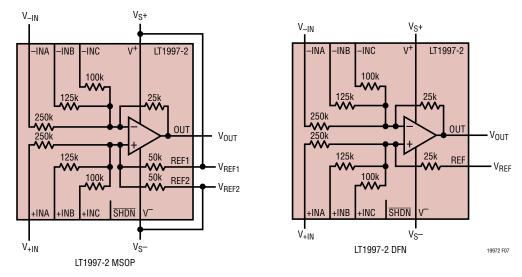

Figure 7. The LT1997-2 Reference Resistors: Split Resistors in the MSOP Package, Single Resistor in the DFN Package

#### **Amplifiers for a Single-Ended Input**

All of the difference amplifier configurations discussed in the preceding section can be used as noninverting or inverting amplifiers if the input is single-ended. For example, to achieve a positive attenuation for a single-ended input using the LT1997-2, simply ground  $V_{-\text{IN}}$  and connect the input signal to  $V_{+\text{IN}}$ . Similarly, to achieve a negative attenuation for a single-ended input using the LT1997-2 , simply ground  $V_{+\text{IN}}$  and connect the input signal to  $V_{-\text{IN}}$ .

#### **Reference Resistors**

In the preceding discussions, the Reference resistor is shown as a single 25k resistor. This is true in the DFN package. In the MSOP package the reference resistor is split into two 50k resistors (Figure 7). Tying the REF1 and REF2 pins to the same voltage produces the same reference voltage as tying the  $V_{REF}$  pin in the DFN package to that voltage. Connecting REF1 and REF2 to different voltages produces an effective reference voltage that is the average of  $V_{REF1}$  and  $V_{REF2}$ . This feature is especially useful when the desired reference voltage is half way between the sup-

plies. Tying REF1 to  $V_S+$  and REF2 to  $V_S-$  produces the desired mid-supply voltage without the help of another external reference voltage (Figure 7). The ratio of  $R_{REF1}$  to  $R_{REF2}$  is very precise:

$$\frac{\Delta R}{R} = \left| \frac{R_{REF1} - R_{REF2}}{\left(\frac{R_{REF1} + R_{REF2}}{2}\right)} \right| < 90 \text{ppm}$$

#### Shutdown

The LT1997-2 has a shutdown pin  $(\overline{SHDN})$ . Under normal operation this pin should be tied to V<sup>+</sup> or allowed to float. Tying this pin 2.5V or more below V<sup>+</sup> will cause the part to enter a low power state. The supply current is reduced to less than 25µA and the op amp output becomes high impedance. The voltages at the input pins can still be present even in shutdown mode.

#### **Supply Voltage**

The positive supply pin of the LT1997-2 should be bypassed with a small capacitor (typically  $0.1\mu\text{F}$ ) as close to the supply pins as possible. When driving heavy loads, an additional  $4.7\mu\text{F}$  electrolytic capacitor should be added. When using split supplies, the same is true for the V<sup>-</sup> supply pin.

#### Output

The output of the LT1997-2 can typically swing to within 50mV of either rail with no load and is capable of sourcing and sinking approximately 30mA at 25°C. The LT1997-2 is internally compensated to drive at least 0.5nF of capacitance under any output loading conditions. For larger capacitive loads, a 0.22µF capacitor in series with a 150 $\Omega$  resistor between the output and ground will compensate the amplifier to drive capacitive loads greater than 0.5nF.

#### Distortion

The LT1997-2 features excellent distortion performance when the internal op amp is operating in the normal operating region. Operating the LT1997-2 with the internal op amp in the over the top region will increase distortion due to the lower loop gain of the op amp. Operating the

LT1997-2 with input common mode voltages that go from the normal to Over-The-Top operation will significantly degrade the LT1997-2's linearity as the op amp must transition between two different input stages. Driving resistive loads significantly smaller than the 25k internal feedback resistor will also degrade the amplifier's linearity performance.

#### **High Voltage Pin Spacing**

For applications with very high input voltages, the LT1997-2 pinout eases the printed circuit board (PCB) layout burden. Voltages at +INA, -INA, +INB, and -INB input pins are separated from other pins by virtue of unpopulated pin locations, as illustrated in the Pin Configuration section of this data sheet.

#### **Power Dissipation Considerations**

Because of the ability of the LT1997-2 to operate on power supplies up to  $\pm 25$ V, to withstand very high input voltages and to drive heavy loads, there is a need to ensure the die junction temperature does not exceed 150°C. The LT1997-2 is housed in DF14 ( $\theta_{JA} = 45$ °C/W,  $\theta_{JC} = 3$ °C/W) and MS16 ( $\theta_{JA} = 130$ °C/W) packages.

In general, the die junction temperature  $(T_J)$  can be estimated from the ambient temperature  $(T_A)$ , the device's power dissipation  $(P_D)$  and the thermal resistance of the device and board  $(\theta_{JA})$ .

$$T_J = T_A + P_D \bullet \theta_{JA}$$

The thermal resistance from the junction to the ambient environment  $(\theta_{JA})$  is the sum of the thermal resistance from the junction to the exposed pad  $(\theta_{JC})$  and the thermal resistance from the exposed pad to the ambient environment  $(\theta_{CA})$ . The  $\theta_{CA}$  value depends on how much PCB metal is connected to the exposed pad in the board. The more PCB metal that is used, the lower  $\theta_{CA}$  and  $\theta_{JA}$  will be.

Power is dissipated by the amplifier's quiescent current, by the output current driving a resistive load, and by the input current driving the LT1997-2's internal resistor network.

$$P_D = ((V_S + - V_S -) \bullet I_S) + P_{OD} + P_{RESD}$$

For a given supply voltage, the worst-case output power dissipation  $P_{OD(MAX)}$  occurs with the output voltage at half of either supply voltage.  $P_{OD(MAX)}$  is given by:

$$P_{OD(MAX)} = \frac{\left(V_S/2\right)^2}{R_{LOAD}}$$

The power dissipated in the internal resistors ( $P_{RESD}$ ) depends on the manner the input resistors have been configured as well as the input voltage, the output voltage and the voltage on the REF pin. The following equations and Figure 8 show the different components of  $P_{RESD}$  corresponding to the different groups of the LT1997-2's internal resistors, assuming that the LT1997-2 is used with a dual supply configuration with REF pin at ground (refer to Figure 3 for resistor terminologies used in equations below).

$$P_{RESDA} = \frac{\left(V_{+IN}\right)^2}{R_G + R_F}$$

$$P_{RESDB} = \frac{\left(V_{-IN} - V_{+IN} \bullet \frac{R_F}{R_G + R_F}\right)^2}{R_G}$$

$$P_{RESDC} = \frac{\left(V_{+IN} \bullet \frac{R_F}{R_G + R_F} - V_{OUT}\right)^2}{R_F}$$

$P_{RESD} = P_{RESDA} + P_{RESDB} + P_{RESDC}$

In general,  $P_{RESD}$  increases with higher input voltage and lower output and REF pin voltages.

Example: For an LT1997-2 in a DFN package mounted on a PC board with a thermal resistance of 45°C/W, operating on  $\pm 25$ V supplies and driving a 2.5k $\Omega$  load to 12.5V with

$V_{+IN} = 255V$  and REF = 0V, the total power dissipation is given by:

$$P_{D} = (50 \cdot 0.6 \text{mA}) + \frac{12.5^{2}}{2.5 \text{k}} + \frac{255^{2}}{275 \text{k}}$$

$$+ \frac{\left(130 - \frac{255}{11}\right)^{2}}{250 \text{k}} + \frac{\left(\frac{255}{11} - 12.5\right)^{2}}{25 \text{k}}$$

$$= 0.38 \text{W}$$

Assuming a thermal resistance of 45°C/W, the die temperature will experience an 17°C rise above ambient. This implies that the maximum ambient temperature the LT1997-2 should operate under the above conditions is:

$$T_A = 150^{\circ}C - 17^{\circ}C = 133^{\circ}C$$

It is recommended that the exposed pad of the DFN package have as much PCB metal connected to it as reasonably available. The more PCB metal connected to the exposed

Figure 8. Power Dissipation Example

pad, the lower the thermal resistance. Connecting a large amount of PCB metal to the exposed pad can reduce the  $\theta_{JA}$  to even less than 45°C/W. Use multiple vias from the exposed pad to the  $V^-$  plane. The exposed pad is electrically connected to the  $V^-$  pin. In addition, a heat sink may be necessary if operating near maximum junction temperature.

The MSOP package has no exposed pad and a higher thermal resistance ( $\theta_{JA} = 130^{\circ}\text{C/W}$ ). It should not be used in applications which have a high ambient temperature, require driving a heavy load, or require an extreme input voltage.

#### Thermal Shutdown

For safety, the LT1997-2 will enter shutdown mode when the die temperature rises to approximately 163°C. This thermal shutdown has approximately 9°C of hysteresis requiring the die temperature to cool 9°C before enabling the amplifier again.

#### **ESD Protection**

The LT1997-2 is protected by a number of ESD structures. The structures are shown in Figure 9.

Figure 9. ESD Protection

The ESD structures serve to protect the internal circuitry but also limit signal swing on certain nodes. The structures on the internal op amp inputs limit the voltage on these nodes to 0.3V below V<sup>-</sup> and 80V above V<sup>-</sup>. The voltage on the REF (DFN), REF1 (MSOP) and REF2 (MSOP) pins are limited to 0.3V below V<sup>-</sup> and 60V above V<sup>-</sup>. The voltage on the SHDN pin is limited to 0.3V below V<sup>-</sup> and 0.3V above V<sup>+</sup>.

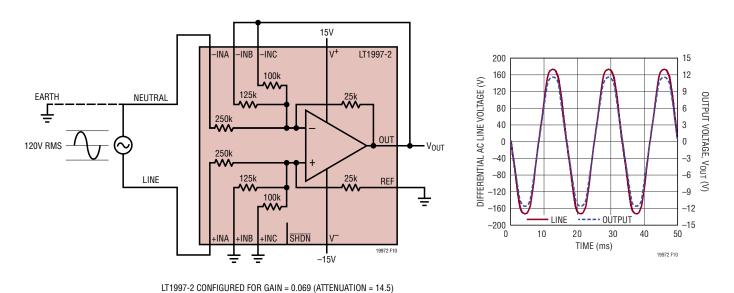

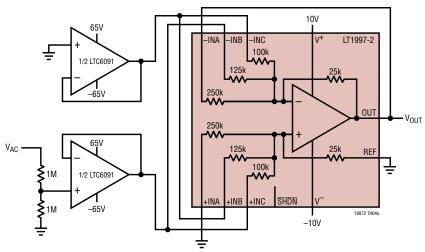

#### **Direct Line Voltage Measurement**

Since the LT1997-2 can withstand up to ±255V at its input pins, configurations with the highest attenuation factors allow for direct sensing of the 60Hz, 120VAC line voltage. The circuit shown in Figure 10 directly measures the line and neutral signals. The ground of the circuit can reasonably connect to earth ground. The neutral voltage level will typically hover near earth. The ability of the LT1997-2 to sense high voltages with varying common mode levels enables this extremely simple implementation.

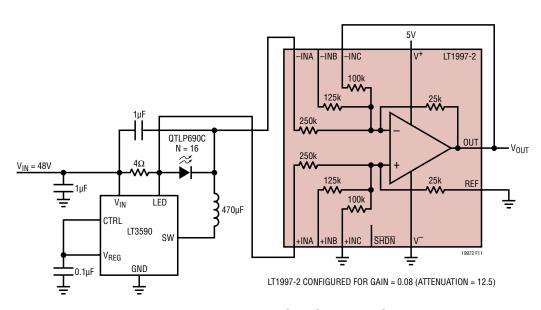

#### **High Side Large Voltage Measurement**

In some applications, an electrical potential develops relative to a high line voltage. As an example, some LED current control power conversion topologies place the LED at the high voltage. Even more interestingly, the high line may be moving. Off-line LED conversion such as in modern light bulbs sometimes use LEDs pegged to the rectified line voltage.

The circuit in Figure 11 uses the LT3590 to control LED current. A LT1997-2 configured for a gain of 0.08V/V can enable detection of an LED open circuit fault condition. With the LED open circuited, the voltage across the LED (which is being sensed by the LT1997-2) rises, and at 41.25V the LT1997-2 output rises above 3.3V, indicating a fault condition.

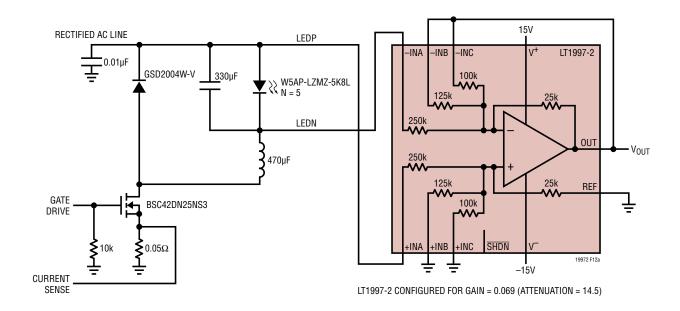

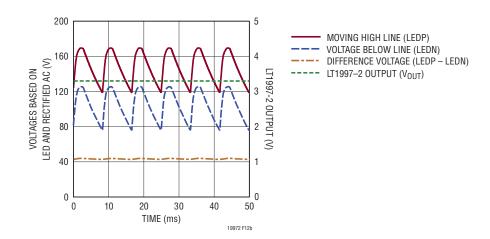

A large voltage referred to the rectified AC mains can be attenuated and shifted to a system's low voltage circuitry. Figure 12 shows this kind of function. Off-line LED lighting that employs nonisolated buck power conversion is one such example.

Figure 10. Direct Line Voltage (120VAC, 60Hz) Measurement

Figure 11. Detection of an LED Open Circuit Fault Condition

Figure 12. LED Common Mode Swings Relative to Rectified AC

## TYPICAL APPLICATIONS

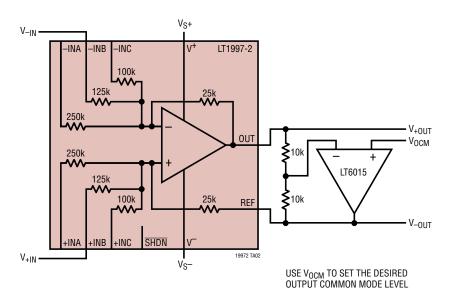

LT1997-2 Configured for Differential Output with Gain = 0.2

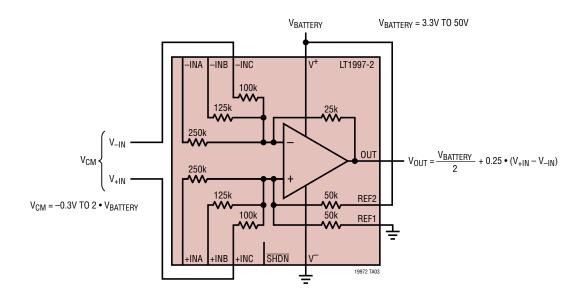

#### **Precision Over-The-Top Single-Supply Funnel Amplifier**

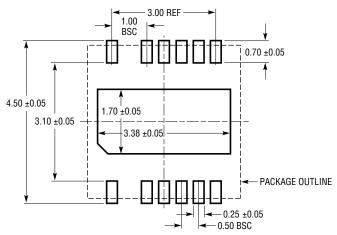

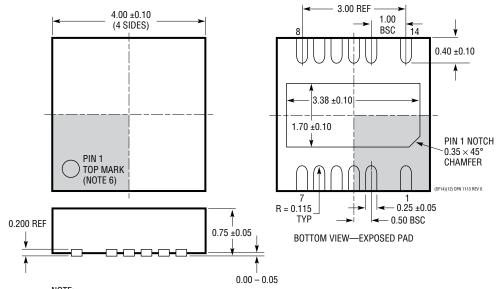

### PACKAGE DESCRIPTION

## $\begin{array}{c} \text{DF Package} \\ \text{14(12)-Lead Plastic DFN (4mm} \times \text{4mm)} \end{array}$

(Reference LTC DWG # 05-08-1963 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- NOTE:

- 1. PACKAGE OUTLINE DOES NOT CONFORM TO JEDEC MO-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

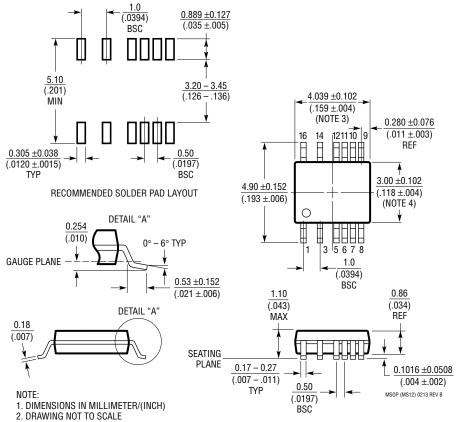

#### PACKAGE DESCRIPTION

#### **MS Package** 16 (12)-Lead Plastic MSOP with 4 Pins Removed

(Reference LTC DWG # 05-08-1847 Rev B)

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

## TYPICAL APPLICATION

#### **Funnel Instrumentation Amplifier for High Voltage Sensing**

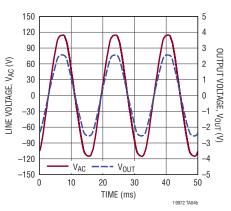

#### **Input and Output Voltage Waveforms**

#### LT1997-2 CONFIGURED FOR GAIN = 0.0455 (ATTENUATION = 22)

## **RELATED PARTS**

| PART NUMBER              | DESCRIPTION                                                                   | COMMENTS                                                                                                     |

|--------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Difference Amplifie      | rs                                                                            |                                                                                                              |

| LT1997-3                 | Precision, Wide Voltage Range Gain Selectable Amplifier                       | 3.3V to 50V Operation, CMRR > 91dB, Input Voltage = ±160V, Gain = 1, 3, 9                                    |

| LT6375                   | ±270V Common Mode Voltage Difference Amplifier                                | 3.3V to 50V Operation, CMRR > 97dB, Input Voltage = ±270V, Gain = 1                                          |

| LT6376                   | ±230V Common Mode Voltage G = 10 Difference Amplifier                         | 3.3V to 50V Operation, CMRR > 90dB, Input Voltage = ±230V, Gain = 10                                         |

| LT1990                   | ±250V Input Range Difference Amplifier                                        | 2.7V to 36V Operation, CMRR > 70dB, Input Voltage = ±250V, Gain = 1, 10                                      |

| LT1991                   | Precision, 100µA Gain Selectable Amplifier                                    | 2.7V to 36V Operation, 50µV Offset, CMRR > 75dB, Input Voltage = ±60V                                        |

| LT1996                   | Precision, 100µA Gain Selectable Amplifier                                    | Micropower, Pin Selectable Up to Gain = 118                                                                  |

| AD8275                   | G = 0.2, Level Translation, 16-Bit ADC Driver                                 | 3.3V to 15V Operation, CMRR > 86dB, Input Voltage = $-35$ V to 40V, Gain = 0.2                               |

| AD8475                   | Precision, Selectable Gain, Fully Differential Funnel<br>Amplifier            | 3.3V to 10V Operation, CMRR > 86dB, Input Voltage = ±15V, Gain = 0.4, 0.8                                    |

| Operational Amplifi      | ers                                                                           |                                                                                                              |

| LT6015/LT6016/<br>LT6017 | Single, Dual, and Quad Over-The-Top Precision Op Amp                          | 3.2MHz, 0.8V/ $\mu$ s, 50 $\mu$ V V $_{0S}$ , 3V to 50V V $_{S}$ , 0.335mA I $_{S}$ , RRIO                   |

| LT6018                   | 33V, Ultralow Noise, Precision Op Amp                                         | V <sub>0S</sub> : 50μV, GBW: 15MHz, SR: 30V/μs, en: 1.2nV/√Hz, I <sub>S</sub> : 7.2mA                        |

| LTC6090/LTC6091          | Single and Dual 140V Operational Amplifier                                    | 50pA I <sub>B</sub> , 1.6mV V <sub>OS</sub> , 9.5V to 140V V <sub>S</sub> , 4.5mA I <sub>S</sub> , RR Output |

| Current Sense Amp        | lifiers                                                                       |                                                                                                              |

| LT1999                   | High Voltage, Bidirectional Current Sense Amplifier                           | -5V to 80V, 750μV, CMRR 80dB at 100kHz, Gain = 10, 20, 50                                                    |

| LT6108                   | High Side Current Sense Amplifier with Reference and Comparator with Shutdown | 2.7V to 60V, 125μV, Resistor Set Gain, ±1.25% Threshold Error                                                |

| LT1787/LT1787HV          | Precision, Bidirectional High Side Current Sense Amplifier                    | 2.7V to 60V Operation, 75µV Offset, 60µA Current Draw                                                        |

| LT6100                   | Gain-Selectable High Side Current Sense Amplifier                             | 4.1V to 48V Operation,<br>Pin-Selectable Gain: 10V/V, 12.5V/V, 20V/V, 25V/V, 40V/V, 50V/V                    |

| LTC6101/<br>LTC6101HV    | High Voltage High Side Current Sense Amplifier                                | 4V to 60V/5V to 100V Operation, External Resistor Set Gain, SOT23                                            |

| LTC6102/<br>LTC6102HV    | Zero Drift High Side Current Sense Amplifier                                  | 4V to 60V/5V to 100V Operation, ±10μV Offset, 1μs Step Response, MSOP8/DFN Packages                          |

| LTC6104                  | Bidirectional, High Side Current Sense                                        | 4V to 60V, Gain Configurable, 8-Pin MSOP Package                                                             |