### Synchronous Rectifier Controller with Opto-Coupler Driver for Forward Converters **DESCRIPTION**

### FEATURES

- Wide Input Supply Range: 3.7V to 30V

- Preactive Mode:

- No Pulse Transformer Required

- DCM Operation at Light Load

- SYNC Mode:

- FCM or DCM Operation at Light Load

- Achieves Highest Efficiency

- 1.5% Feedback Voltage Reference

- 10mA Opto-Coupler Driver

- Output Power Good Indicator

- Integrated Soft-Start Function

### **APPLICATIONS**

- Offline and HV Car Battery Isolated Power Supplies

- 48V Isolated Power Supplies

- Industrial, Automotive and Military Systems

**Δ7**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

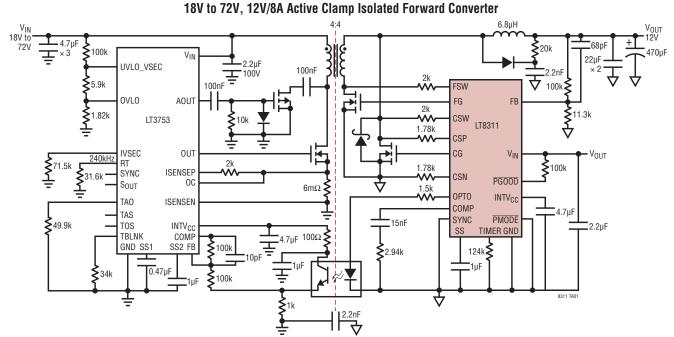

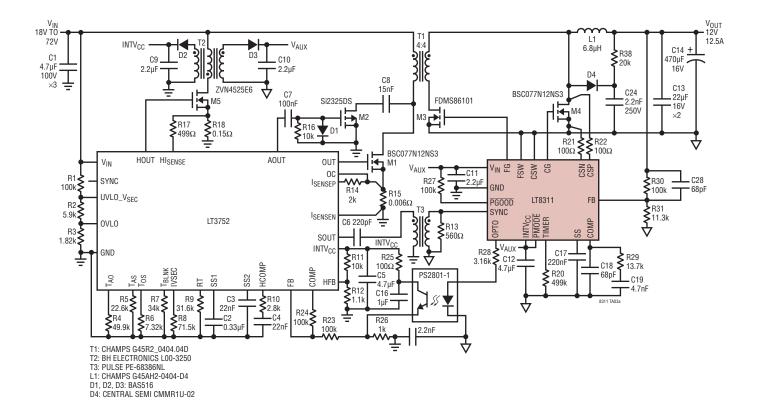

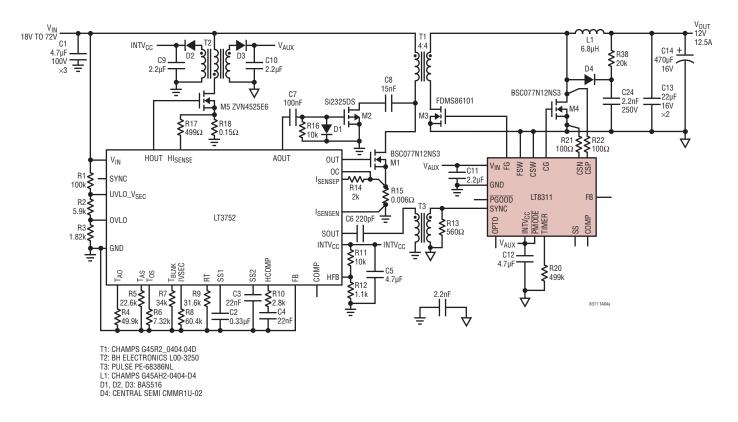

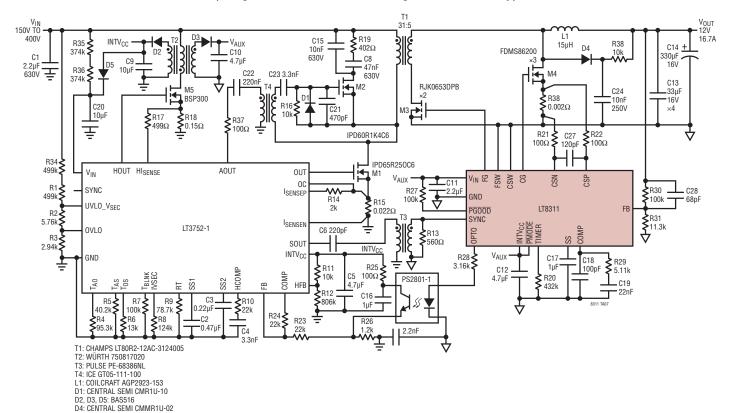

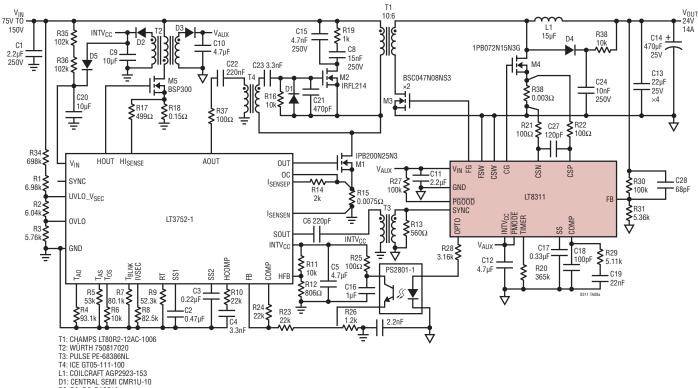

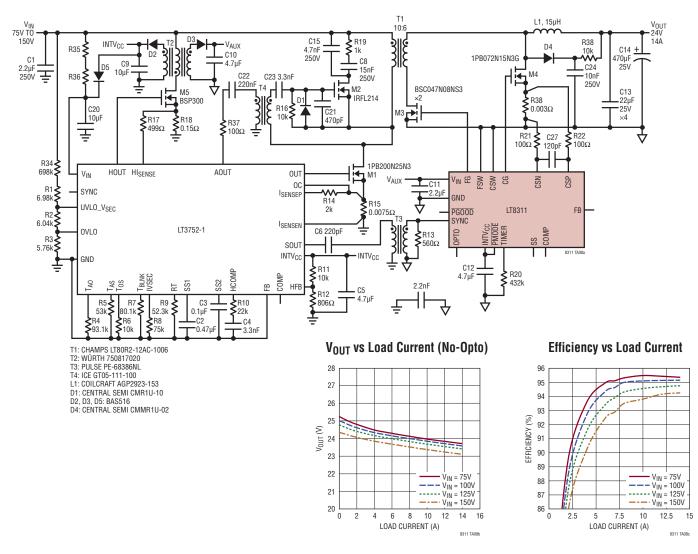

The LT®8311 is used on the secondary side of a forward converter to provide synchronous MOSFET control and output voltage feedback through an opto-coupler. The LT8311's unique preactive mode allows control of the secondary-side MOSFETs without requiring a traditional pulse transformer for primary- to secondary-side communication. In preactive mode, the output inductor current operates in discontinuous conduction mode (DCM) at light load. If forced continuous mode (FCM) operation is desired at light load, the LT8311 can, alternatively, be used in SYNC mode, where a pulse transformer is required to send synchronous control signals from the primary-side IC to the LT8311.

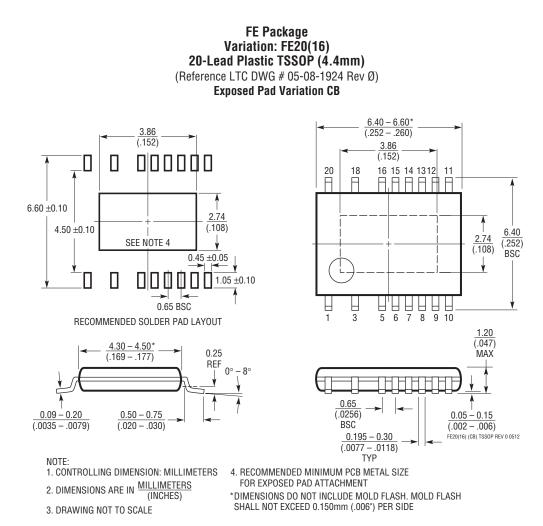

The LT8311 offers a full featured opto-coupler controller, incorporating a 1.5% reference, a transconductance error amplifier and a 10mA opto-driver. Power good monitoring and output soft-start/overshoot control are also included. The LT8311 is available in a 16-lead FE package with pins removed for high voltage spacing requirements.

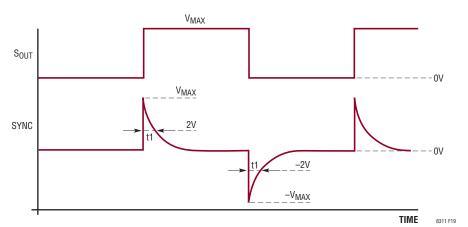

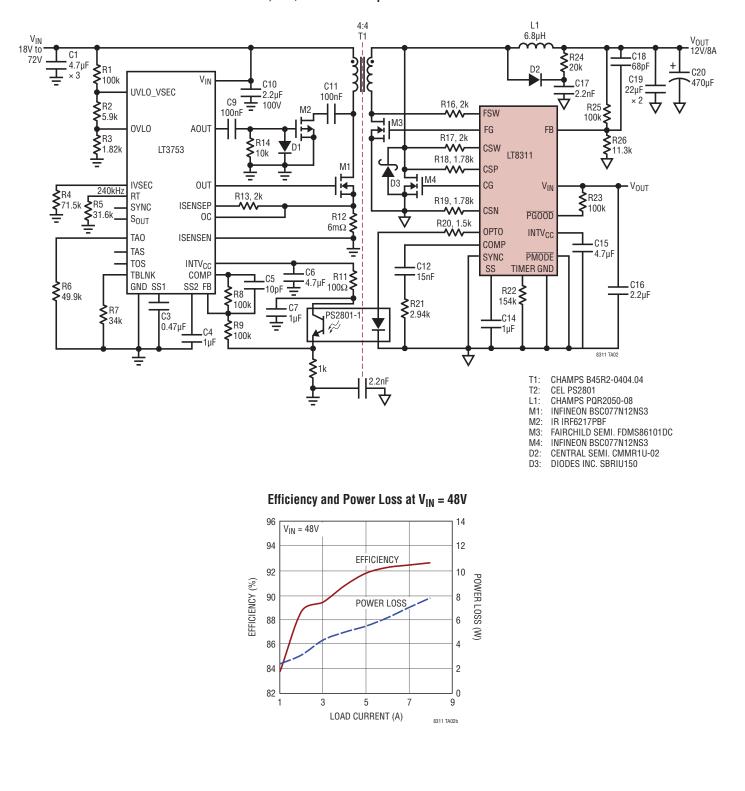

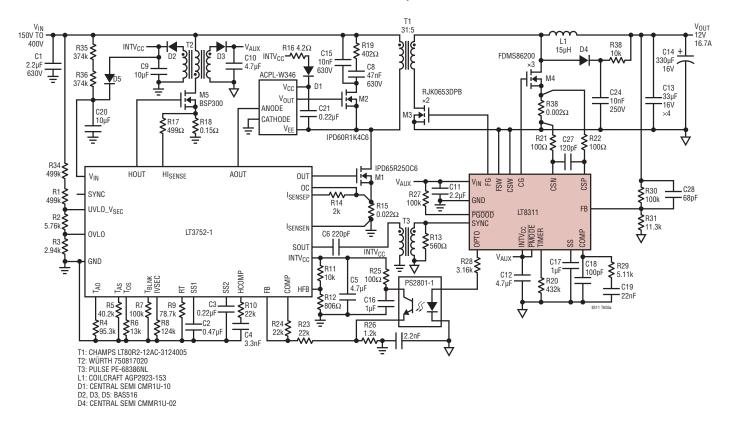

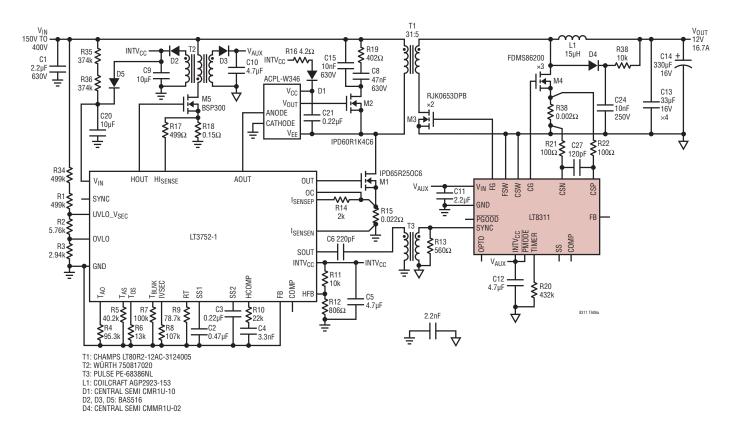

### TYPICAL APPLICATION

### TABLE OF CONTENTS

| Features                                           | 1  |

|----------------------------------------------------|----|

| Applications                                       | 1  |

| Typical Application                                | 1  |

| Description                                        | 1  |

| Absolute Maximum Ratings                           | 3  |

| Order Information                                  |    |

| Pin Configuration                                  | 3  |

| Electrical Characteristics                         | 4  |

| Typical Performance Characteristics                |    |

| Pin Functions                                      | 11 |

| Block Diagram                                      | 12 |

| Operation                                          |    |

| FUNDAMENTALS OF FORWARD CONVERTER OPERATION IN CCM | 13 |

| LT8311 SYNCHRONOUS CONTROL SCHEMES                 | 17 |

| PREACTIVE MODE SYNCHRONOUS CONTROL                 |    |

| SYNC MODE SYNCHRONOUS CONTROL                      |    |

| OPTO-COUPLER CONTROL                               |    |

| Applications Information                           |    |

| V <sub>IN</sub> BIAS SUPPLY                        |    |

| INTV <sub>CC</sub> BIAS SUPPLY                     |    |

| LT8311 OPTO CONTROL FUNDAMENTALS                   |    |

| LT8311 SYNCHRONOUS CONTROL FUNDAMENTALS            |    |

| PREACTIVE MODE SYNCHRONOUS CONTROL                 |    |

| SYNC MODE SYNCHRONOUS CONTROL                      |    |

| Typical Applications                               |    |

| Package Description                                |    |

| Typical Application                                |    |

| Related Parts                                      |    |

|                                                    |    |

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| CSW, FSW, CSP                                                                                                                     | –0.3V to 150V                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SYNC                                                                                                                              | –12V to 12V                                                                                                |

| V <sub>IN</sub> , <u>PGOOD</u>                                                                                                    | 0.3V to 30V                                                                                                |

| INTV <sub>CC</sub> , PMODE                                                                                                        |                                                                                                            |

| FB, SS, COMP                                                                                                                      |                                                                                                            |

| TIMER                                                                                                                             |                                                                                                            |

| CSN                                                                                                                               | 0.3V to 0.4V                                                                                               |

| OPTO, TIMER Short-Circuit                                                                                                         |                                                                                                            |

|                                                                                                                                   |                                                                                                            |

| Current Duration                                                                                                                  | Infinite (Note 5)                                                                                          |

| Current Duration<br>Operating Junction Temperature R                                                                              | ( )                                                                                                        |

|                                                                                                                                   | lange                                                                                                      |

| Operating Junction Temperature R<br>LT8311E (Notes 2, 3)                                                                          | ange<br>40°C to 125°C                                                                                      |

| Operating Junction Temperature R                                                                                                  | lange<br>40°C to 125°C<br>40°C to 125°C                                                                    |

| Operating Junction Temperature R<br>LT8311E (Notes 2, 3)<br>LT8311I (Notes 2, 3)<br>LT8311H (Notes 2, 3)                          | ange<br>40°C to 125°C<br>40°C to 125°C<br>40°C to 150°C                                                    |

| Operating Junction Temperature R<br>LT8311E (Notes 2, 3)<br>LT8311I (Notes 2, 3)<br>LT8311H (Notes 2, 3)<br>LT8311MP (Notes 2, 3) | ange<br>40°C to 125°C<br>40°C to 125°C<br>40°C to 150°C<br>55°C to 150°C                                   |

| Operating Junction Temperature R<br>LT8311E (Notes 2, 3)<br>LT8311I (Notes 2, 3)<br>LT8311H (Notes 2, 3)                          | ange<br>40°C to 125°C<br>40°C to 125°C<br>40°C to 125°C<br>55°C to 150°C<br>55°C to 150°C<br>65°C to 150°C |

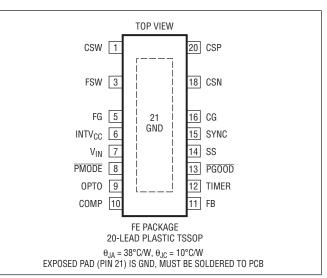

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|------------------|---------------|-----------------------|-------------------|

| LT8311EFE#PBF    | LT8311EFE#TRPBF  | LT8311FE      | 20-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8311IFE#PBF    | LT8311IFE#TRPBF  | LT8311FE      | 20-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8311HFE#PBF    | LT8311HFE#TRPBF  | LT8311FE      | 20-Lead Plastic TSSOP | -40°C to 150°C    |

| LT8311MPFE#PBF   | LT8311MPFE#TRPBF | LT8311FE      | 20-Lead Plastic TSSOP | –55°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C,  $V_{IN} = 12V$ ,  $V_{INTVCC} = 8V$ , PMODE = 5V,  $C_{CG} = C_{FG} = 100$ pF, unless otherwise noted. (Note 2)

| PARAMETER                                      | CONDITIONS                                                                                                                                                            |   | MIN   | ТҮР        | MAX        | UNITS      |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------|------------|------------|

| Supply                                         | ·<br>                                                                                                                                                                 |   |       |            |            | ·          |

| V <sub>IN</sub> Operating Range                |                                                                                                                                                                       |   | 3.7   |            | 30         | V          |

| V <sub>IN</sub> UVLO                           | V <sub>IN</sub> Rising<br>Hysteresis                                                                                                                                  | • | 50    | 3.6<br>100 | 3.7<br>150 | V<br>mV    |

| Quiescent Current                              | Not Switching                                                                                                                                                         |   |       | 4.5        | 5.5        | mA         |

| Error Amplifier                                |                                                                                                                                                                       |   |       |            |            |            |

| Feedback Reference Voltage                     | V <sub>IN</sub> = 12V                                                                                                                                                 |   | 1.209 | 1.227      | 1.245      | V          |

| Feedback Voltage Line Regulation               | $3.7V \le V_{IN} \le 30V$ , % of FB Ref Voltage                                                                                                                       |   |       | 0.015      | 0.1        | %          |

| Feedback Voltage Load Regulation               | $1.3V \le COMP \le 1.8V$ , % of FB Ref Voltage                                                                                                                        |   |       | 0.05       | 0.1        | %          |

| Feedback Pin Bias Current                      | Current Out of FB pin                                                                                                                                                 |   |       | 120        | 200        | nA         |

| Error Amplifier Transconductance               | $1.3V \le COMP \le 1.8V$                                                                                                                                              |   |       | 370        |            | µmhos      |

| Error Amplifier Voltage Gain                   | $1.3V \le COMP \le 1.8V$                                                                                                                                              |   |       | 65         |            | dB         |

| Error Amplifier Output Swing High              | FB = 1V                                                                                                                                                               |   | 1.9   | 2.3        | 2.8        | V          |

| Error Amplifier Output Swing Low               | FB = 1.5V                                                                                                                                                             |   | 0.75  | 1          | 1.25       | V          |

| Power Good                                     |                                                                                                                                                                       |   |       |            |            |            |

| Power NOT Good (Outside This Window)           | % Relative to FB Ref Voltage                                                                                                                                          |   | ±4    | ±10        | ±16        | %          |

| Power Good (Inside This Window)                | % Relative to FB Ref Voltage                                                                                                                                          |   |       | ±7         |            | %          |

| Power Good Indicator Wait Time                 | Minimum Time That FB Must Stay within Power Good Window Before PGOOD Pin Goes Low                                                                                     |   |       | 175        |            | μs         |

| Power Good Leakage                             | PGOOD = 30V                                                                                                                                                           |   |       |            | ±1         | μA         |

| Power Good Output Low Voltage                  | Current into PGOOD Pin = 1mA                                                                                                                                          | ٠ |       | 0.2        | 0.3        | V          |

| Soft-Start (SS)                                |                                                                                                                                                                       |   |       |            |            | . <u> </u> |

| SS Wake-Up Slew Current                        | Current Exists Upon Part Wake Up, Shuts Off After SS Wake Up<br>Offset Voltage Is Satisfied (Note 6)                                                                  |   |       | 1          |            | mA         |

| SS Wake-Up Offset Voltage                      | V <sub>FB</sub> – V <sub>SS</sub> , Upon Part Wake Up SS Is Slewed Up to an Offset<br>Voltage Below FB by SS Wake-Up Slew Current                                     |   |       | 16         |            | mV         |

| SS Charge Current                              | SS = 0V, FB = 0.6V (Note 9)                                                                                                                                           | • | 9     | 10         | 11         | μA         |

| SS Pull-Down Amplifier Offset Voltage          | $V_{SS}$ – $V_{FB},$ Pull-Down Amplifier Prevents SS from Rising Beyond This Offset Voltage Above FB When the FB Pin Voltage Is Below 50% of the FB Reference Voltage |   |       | 100        |            | mV         |

| SS Pull-Down Amplifier Maximum<br>Sink Current | SS = 1.5V, FB = 0.6V (Note 7)                                                                                                                                         |   |       | 13         |            | mA         |

| SS High Clamp Voltage                          |                                                                                                                                                                       |   | 1.8   | 2          |            | V          |

| Opto Driver                                    | •                                                                                                                                                                     |   |       |            |            |            |

| COMP Buffer Input Offset Voltage               | 1.3V ≤ COMP (Note 5)                                                                                                                                                  |   |       | 0.9        |            | V          |

| Opto-Driver Reference Voltage                  | (Note 5)                                                                                                                                                              |   |       | 1          |            | V          |

| Opto-Driver DC Gain                            | (Note 5)                                                                                                                                                              |   |       | -7         |            | V/V        |

|                                                |                                                                                                                                                                       |   |       |            |            |            |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C,  $V_{IN} = 12$ V,  $V_{INTVCC} = 8$ V, PMODE = 5V,  $C_{CG} = C_{FG} = 100$ pF, unless otherwise noted. (Note 2)

|                                                        | CONDITIONS                                                                    |   | MIN                          | TYP                   | MAX  | UNITS    |

|--------------------------------------------------------|-------------------------------------------------------------------------------|---|------------------------------|-----------------------|------|----------|

| Inverting DC Gain From COMP Pin to                     | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , 1.290V $\leq$ COMP $\leq$ 1.310V        |   |                              | -5                    |      | V/V      |

| OPTO Pin                                               | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , 1.490V $\leq$ COMP $\leq$ 1.510V        |   |                              | -5.9                  |      | V/V      |

|                                                        | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , 1.890V $\leq$ COMP $\leq$ 1.910V        |   |                              | -6.2                  |      | V/V      |

| Opto-Driver –3dB Bandwidth                             | No Load (Note 5)                                                              |   |                              | 400                   |      | kHz      |

| Opto-Driver Output Swing Low                           | FB = 1V, COMP = SS = OPTO = Open                                              | • |                              | 0.5                   | 0.85 | V        |

| Opto-Driver Output Swing High                          | V <sub>IN</sub> = 3.7V, FB = 1.5V, COMP = SS = Open, I <sub>OPTO</sub> = 10mA | • | V <sub>IN</sub> – 1.7        | V <sub>IN</sub> – 1.4 |      | V        |

|                                                        | V <sub>IN</sub> = 30V, FB = 1.5V, COMP = SS = Open, I <sub>OPTO</sub> = 10mA  | • | 5.2                          | 6.5                   |      | V        |

| Opto-Driver Output Short-Circuit Current               | V <sub>IN</sub> = 30V, FB = 1.5V, COMP = SS = Open, OPTO = 0V (Note 6)        |   | 10.5                         | 15                    | 18   | mA       |

| Opto-Driver Output Sink Current                        | FB = 1V, OPTO = 1.2V (Note 7)                                                 | • | 200                          | 300                   | 420  | μA       |

| Internal Linear Regulator                              | -                                                                             |   |                              |                       |      | <u>.</u> |

| INTV <sub>CC</sub> Regulation Voltage                  | No Load                                                                       | • | 6.5                          | 7                     | 7.5  | V        |

| INTV <sub>CC</sub> Load Regulation                     | $(\Delta V_{INTVCC}/\Delta I_{INTVCC}), 0A \le I_{INTVCC} \le 20 \text{mA}$   |   |                              | 1.8                   | 3    | mV/mA    |

| INTV <sub>CC</sub> UVLO Rising                         |                                                                               | • |                              | 4.6                   | 4.8  | V        |

| INTV <sub>CC</sub> UVLO Falling                        |                                                                               |   | 4.1                          | 4.3                   |      | V        |

| INTV <sub>CC</sub> OVLO Rising                         |                                                                               | • |                              | 16.5                  | 17.5 | V        |

| INTV <sub>CC</sub> OVLO Falling                        |                                                                               | • | 14                           | 15                    |      | V        |

| INTV <sub>CC</sub> Current Limit                       | INTV <sub>CC</sub> > I <sub>INTVCC_UVLO_RISING</sub> (= 4.6V)                 | • | 38                           | 48                    | 58   | mA       |

|                                                        | INTV <sub>CC</sub> < I <sub>INTVCC</sub> UVLO FALLING (= 4.3V)                |   |                              | 20                    |      | mA       |

| INTV <sub>CC</sub> Dropout Voltage                     | V <sub>IN</sub> = 6V, I <sub>INTVCC</sub> = 10mA, Not Switching               |   |                              | 400                   |      | mV       |

| CG and FG Gate Drivers                                 |                                                                               |   |                              |                       |      |          |

| Driver Output Rise Time                                | $C_{CG} = C_{FG} = 3.3 nF$ , INTV <sub>CC</sub> = 8V (Note 4)                 |   |                              | 25                    |      | ns       |

| Driver Output Fall Time                                | $C_{CG} = C_{FG} = 3.3 nF$ , INTV <sub>CC</sub> = 8V (Note 4)                 |   |                              | 25                    |      | ns       |

| Driver Output High Voltage                             |                                                                               | • | V <sub>INTVCC</sub><br>- 0.2 |                       |      | V        |

| Driver Output Low Voltage                              |                                                                               | • |                              |                       | 0.7  | V        |

| PMODE Selection                                        | -                                                                             |   |                              |                       |      |          |

| PMODE Trip Voltage                                     | PMODE Ramp Up<br>Hysteresis                                                   | • | 1                            | 1.2<br>30             | 1.4  | V<br>mV  |

| PMODE Input Current                                    | PMODE = 18V                                                                   | • |                              | 60                    | 90   | μA       |

| Preactive Mode (Tie PMODE to OV)                       |                                                                               |   |                              |                       |      | ·        |

| Preactive Mode Operating<br>Frequency Range            |                                                                               | • | 100                          |                       | 300  | kHz      |

| CSW High Trip Voltage                                  | CSW Ramp Up                                                                   |   | 1                            | 1.2                   | 1.4  | V        |

| CSW High Input Current                                 | CSW = 150V (Note 7)                                                           | • |                              | 250                   | 500  | μA       |

| CSW Low Trip Voltage                                   | CSW Ramp Down                                                                 | • | -250                         | -150                  | -50  | mV       |

| FSW Trip Voltage                                       |                                                                               | • | 1                            | 1.2                   | 1.4  | V        |

| FSW High Input Current                                 | FSW = 150V (Note 7)                                                           | • |                              | 250                   | 500  | μA       |

| CG Falling Edge to CSW Rising Edge<br>Prediction Delay | CSW = 150kHz (Note 10), FSW = 0V, CSP = -500mV                                | • | 5                            | 100                   | 300  | ns       |

| CG Falling Edge Delay to FG Rising Edge                | CSW = 150kHz (Note 10), FSW = 0V, CSP = -500mV                                | • | 10                           | 50                    | 80   | ns       |

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25$ °C,  $V_{IN} = 12V$ ,  $V_{INTVCC} = 8V$ , PMODE = 5V,  $C_{CG} = C_{FG} = 100$  pF, unless otherwise noted. (Note 2)

| PARAMETER                                       | CONDITIONS                                                                                                                                                                                                                                      |   | MIN              | ТҮР               | MAX               | UNITS             |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|-------------------|-------------------|-------------------|

| SYNC Mode (Tie PMODE to INTV <sub>CC</sub> )    |                                                                                                                                                                                                                                                 |   | 1                |                   |                   | <u> </u>          |

| SYNC High Trip Voltage                          | SYNC Ramp Up<br>Hysteresis                                                                                                                                                                                                                      | • | 0.9              | 1.2<br>-2.4       | 1.5               | V<br>V            |

| SYNC Low Trip Voltage                           | SYNC Ramp Down<br>Hysteresis                                                                                                                                                                                                                    | • | -1.5             | -1.2<br>2.4       | -0.9              | V<br>V            |

| SYNC Minimum Pulse Width                        | SYNC = 0V to ±2V Pulse<br>SYNC = 0V to ±6V Pulse (Note 5)                                                                                                                                                                                       | • |                  | 40<br>20          | 100               | ns<br>ns          |

| SYNC Input Current                              | -3.5V < SYNC < 3.5V<br>SYNC = ±10V (Note 6, 7)                                                                                                                                                                                                  | • |                  | 300               | ±1<br>400         | μΑ<br>μΑ          |

| SYNC Propagation Delay To CG/FG<br>Outputs      | SYNC Rising Edge (0V to 2V) to CG Rising Edge (Note 8)<br>SYNC Rising Edge (0V to 6V) to CG Rising Edge (Notes 5, 8)<br>SYNC Falling Edge (0V to 2V) to FG Rising Edge (Note 8)<br>SYNC Falling Edge (0V to 6V) to FG Rising Edge (Notes 5, 8), | • |                  | 100<br>75<br>100  | 150<br>150        | ns<br>ns<br>ns    |

| TIMED Timeout Frequency                         | $C_{CG} = C_{FG} = 3.3$ nF                                                                                                                                                                                                                      |   | 425              | 85<br>505         | 585               | ns<br>kHz         |

| TIMER Timeout Frequency                         | R <sub>TIMER</sub> = 41.2k<br>R <sub>TIMER</sub> = 71.5k<br>R <sub>TIMER</sub> = 221k                                                                                                                                                           |   | 425<br>255<br>80 | 300<br>300<br>100 | 585<br>345<br>120 | kHZ<br>kHZ<br>kHZ |

| TIMER Short-Circuit Current                     | TIMER = 0V                                                                                                                                                                                                                                      | • |                  | 40                | 60                | μA                |

| Current Comparator                              |                                                                                                                                                                                                                                                 |   |                  |                   |                   |                   |

| Current Comparator Trip Threshold               | CSP Ramp Up, $R_{CSP} = R_{CSN} = 0\Omega$                                                                                                                                                                                                      | • | 48               | 62                | 72                | mV                |

|                                                 | CSP Ramp Up, $R_{CSP} = R_{CSN} = 1.62k\Omega$ (Note 5)                                                                                                                                                                                         |   |                  | 0                 |                   | mV                |

| Current Comparator Blank Time in Preactive Mode | From Rising CG Edge Until Blanking Ends (Note 5)                                                                                                                                                                                                |   |                  | 250               |                   | ns                |

| Current Comparator Blank Time in SYNC Mode      | From Rising CG Edge Until Blanking Ends                                                                                                                                                                                                         |   |                  | 400               |                   | ns                |

| CSP Current at Low CSP Voltage                  | CSP = 0V (Note 6)                                                                                                                                                                                                                               |   | 30               | 38                | 50                | μA                |

| CSP Current at High CSP Voltage                 | CSP = 150V (Note 7)                                                                                                                                                                                                                             |   |                  | 200               | 500               | μA                |

| CSN Current                                     | CSN = 0V (Note 6)                                                                                                                                                                                                                               |   |                  | 0.1               | 1                 | μA                |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT8311 is tested under pulsed load conditions such that  $T_J \sim T_A$ . The LT8311E is guaranteed to meet specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature are assured by design, characterization and correlation with statistical process controls. The LT8311I is guaranteed over the -40°C to 125°C operating junction temperature range. The LT8311H is guaranteed over the -40°C to 150°C operating junction temperature range, and the LT8311MP is guaranteed over the -55°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C.

**Note 3:** The LT8311 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction

temperature will exceed the maximum operating junction temperature when overtemperature is active. Continuous operating above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Rise and fall times of are measured between 10% and 90% points of a signal edge.

Note 5: Guaranteed by design and/or correlation to static test.

Note 6: Current flows out of pin.

Note 7: Current flows into pin.

**Note 8:** Propagation delay is measured between 50% point of the two signal edges of interest.

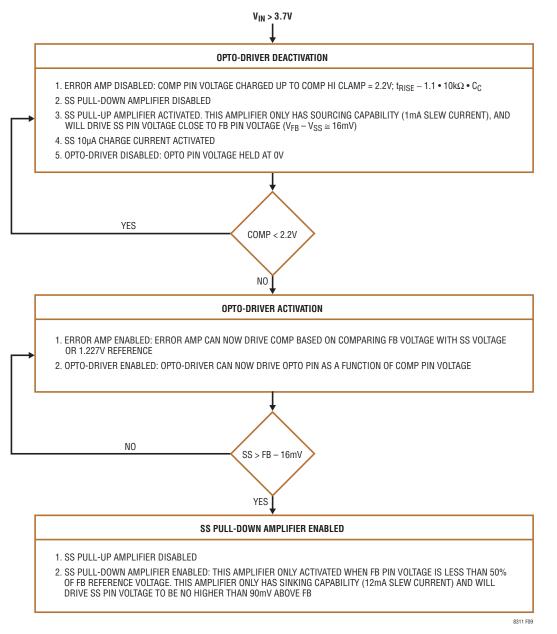

**Note 9:** SS charge current refers to current flowing out of SS pin after certain conditions satisfied upon LT8311 wake-up (see the flowchart for Opto-Control Operation at Start-Up in Figure 9).

Note 10: CSW is a square waveform (duty cycle = 50%) with  $V_{HIGH}$  = 7V and  $V_{LOW}$  = –0.7V.

83111

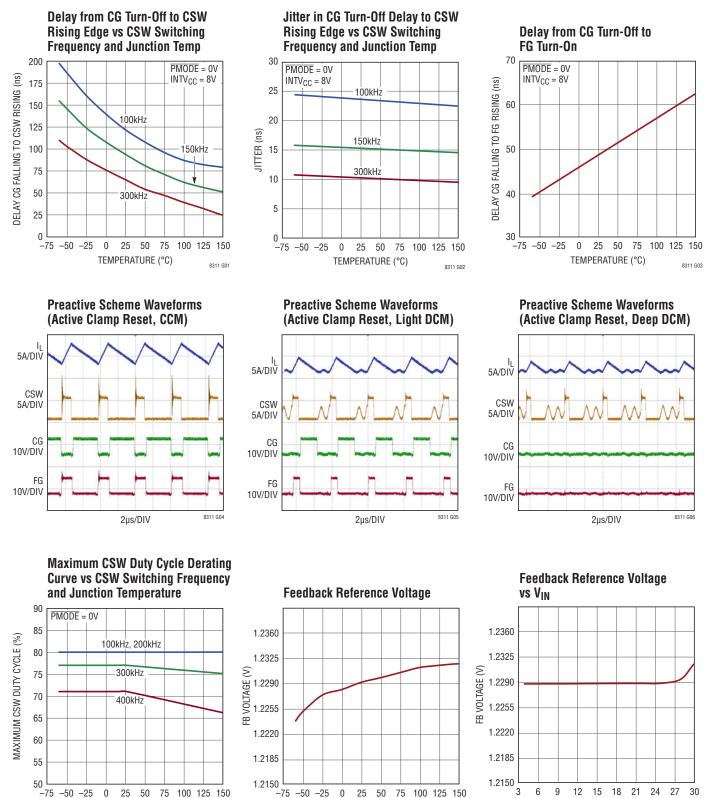

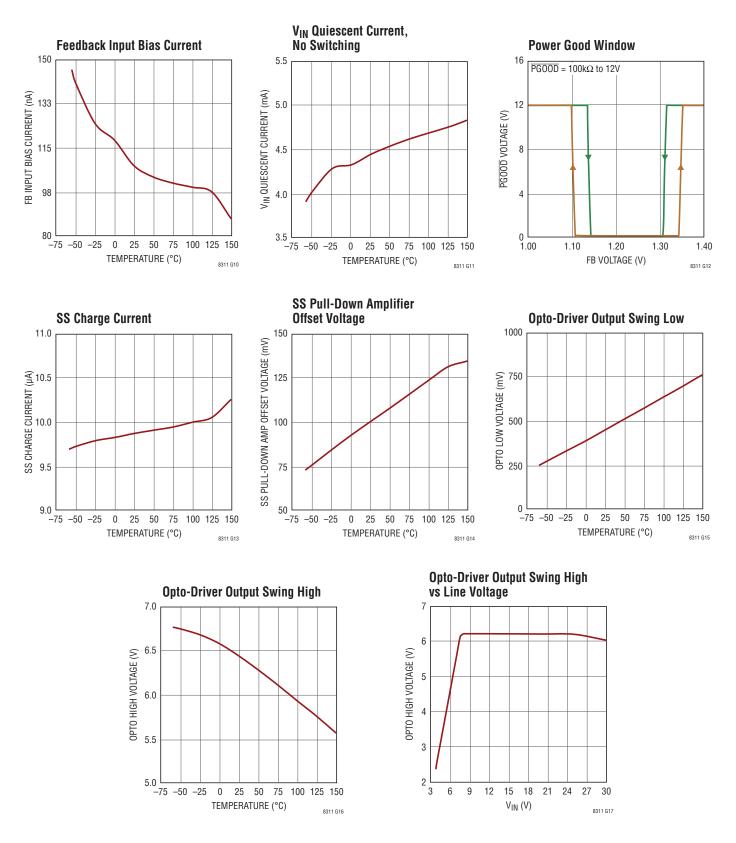

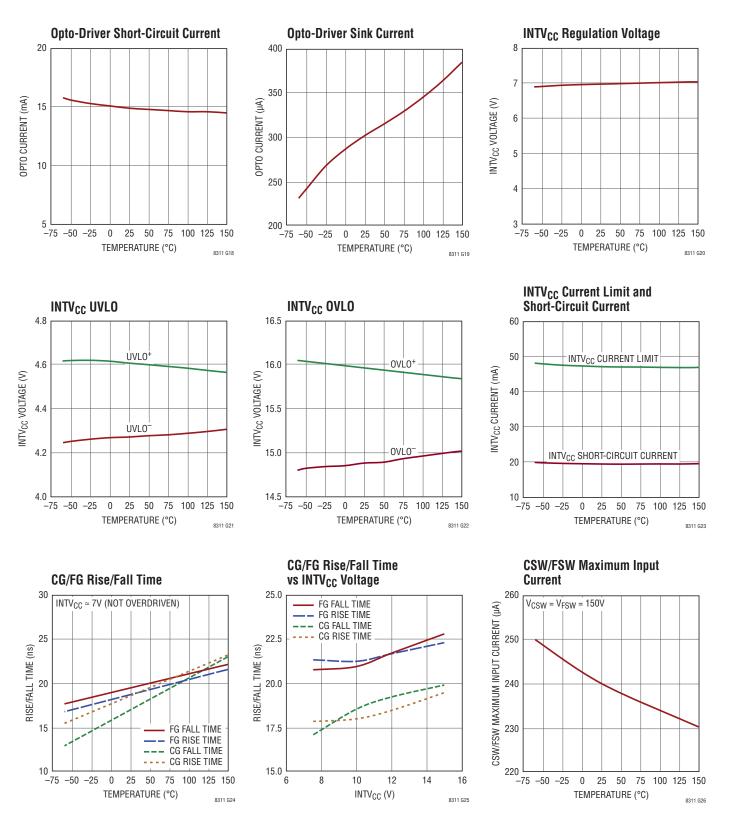

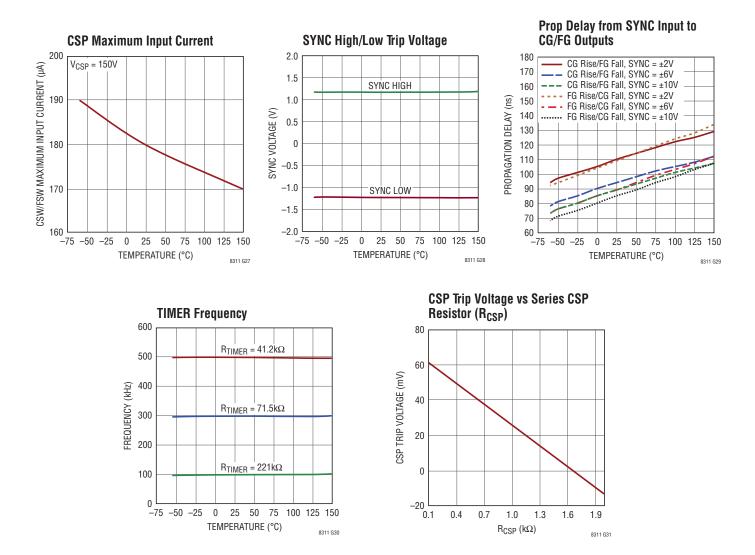

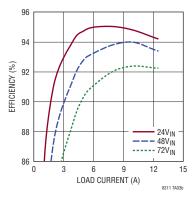

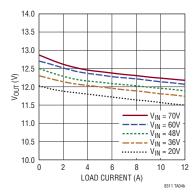

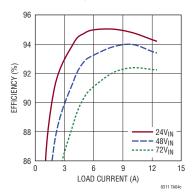

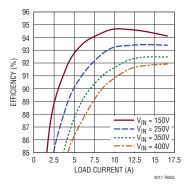

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

8311 G09

30

V<sub>IN</sub> (V)

TEMPERATURE (°C)

8311 G07

TEMPERATURE (°C)

8311 G08

8

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25$ °C, unless otherwise noted.

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

### PIN FUNCTIONS

**CSW (Pin 1):** Catch MOSFET Drain Sense Pin. Connect this pin to the external N-channel catch MOSFET's drain through a 2k resistor (typical) in preactive mode. Minimize parasitic capacitance on the pin. Connect to GND in SYNC mode.

**FSW (Pin 3):** Forward MOSFET Drain Sense Pin. Connect this pin to the external N-channel forward MOSFET's drain through 2k resistor (typical) in preactive mode. Minimize parasitic capacitance on the pin. Connect to GND in SYNC mode.

**FG (Pin 5):** Forward MOSFET Gate Driver Pin. This pin drives the gate of the external N-channel forward MOSFET. Minimize trace length between this pin and the forward MOSFET gate.

**INTV<sub>CC</sub> (Pin 6):** Internal Linear Regulator's Output Pin. INTV<sub>CC</sub> powers the gate drivers on the LT8311. The voltage on this pin is internally regulated to 7V. Alternatively, the pin can be overdriven externally. A minimum of  $4.7\mu$ F (ceramic capacitor) must be placed from this pin to GND.

$V_{IN}$  (Pin 7): Input Supply Pin. This pin must be locally bypassed.

**PMODE (Pin 8):** Preactive Mode Select Pin. Tying PMODE to GND enables preactive mode. Tying PMODE to INTV<sub>CC</sub> enables SYNC mode.

**OPTO (Pin 9):** Opto Driver Output Pin. Tie this pin, through a series resistor, to the input of the opto-coupler. This pin can source up to 10mA, sink 300µA typically, and is short-circuit protected.

**COMP (Pin 10):** Error Amplifier Output Pin. Tie an external compensation network to this pin when using the LT8311's transconductance error amplifier as part of a voltage feedback loop.

**FB (Pin 11):** Feedback Pin. This is the inverting input of the LT8311's internal error amplifier. The FB pin voltage tracks the lower of the internal 1.227V reference and the SS pin voltage. 75nA (bias current) typically flows out of the pin. Tie this pin to a resistor divider network from the output to set the desired output voltage.

**TIMER (Pin 12):** Switching Period Timeout Pin. A resistor from this pin to ground sets an upper limit on the sum of the forward and catch MOSFET on times (including dead time between the two MOSFETs on period), every

cycle. If the sum of the on times of the catch and forward MOSFET, per cycle (including the dead time), exceeds the timeout period programmed by the TIMER resistor, then all synchronous conduction will be shut down. Synchronous conduction resumes when the timeout period is reset again. See the Applications Information section for more details on programming the TIMER resistor. Keep the ground return trace of this pin short, and away from paths with switching noise.

**PGOOD** (Pin 13): Output Power Good Pin. The open-drain output will be pulled to ground when the FB pin voltage stays within  $\pm 7\%$  of the internal 1.227V reference for a period of 175 $\mu$ s. The internal PGOOD comparator has a hysteresis of  $\pm 3\%$ . Therefore, when FB exists outside  $\pm 10\%$ of the 1.227V reference, the PGOOD pin will be pulled high by an external pull-up resistor or current source.

**SS (Pin 14):** Soft-Start Pin. A capacitor from the SS pin to GND will be charged up by SS's internally trimmed 10µA current source. Since FB tracks the lower of the SS pin voltage and the internal reference of 1.227V, the charge rate of the SS pin can be used to set the slew rate at which the FB pin charges up to its regulation voltage of 1.227V. The SS pin typically charges up to 2V. When using the LT8311 as part of voltage feedback loop, place a ceramic capacitor of at least 1nF on this pin to GND. For details on SS start-up and overshoot control functions, please refer to the Applications Information section.

**SYNC (Pin 15):** Synchronization Pin. The SYNC pin, used only in SYNC mode, serves as an edge-sensitive input to receive timing information for synchronous switching. It is typically driven with PWM synchronization signals from the primary-side IC through a pulse transformer. A negative voltage slew on the SYNC pin (-1.2V threshold) turns on the forward MOSFET and turns off the catch MOSFET. Equivalently, a positive voltage slew (1.2V threshold) turns on the catch MOSFET and turns off the forward MOSFET. Tie the SYNC pin to GND in preactive mode.

**CG (Pin 16):** Catch MOSFET Gate Driver Pin. This pin drives the gate of the external N-channel catch MOSFET. Minimize trace length between this pin and the catch MOSFET gate.

**CSN, CSP (Pin 18, Pin 20):** Current Sense Differential Inputs. CSP and CSN are the positive and negative inputs, respectively, of the LT8311's internal current sense comparator. The pins are typically connected across the catch 8311f

### PIN FUNCTIONS

MOSFET to perform  $V_{DS}$  current sensing. Alternatively, if a more precise current sensing mechanism is desired, the pins may be connected across a sense resistor at the catch MOSFET's source. The current comparator trips at 62mV typical. The CSP pin sources 38µA current, allowing trip voltages less than 62mV to be set by placing a resistor in series with the CSP pin. It is recommended to place an identical resistor in series with the CSN pin to match any voltage offsets created by the input bias current (100nA) of the current comparator. In preactive mode, the CSP and CSN pins must be configured to trip at zero or positive values of source to drain current in the catch MOSFET (current in catch MOSFET cannot be allowed to flow from drain to source in preactive mode).

**GND (Exposed Pad Pin 21):** Ground. Exposed pad must be soldered directly to local ground plane.

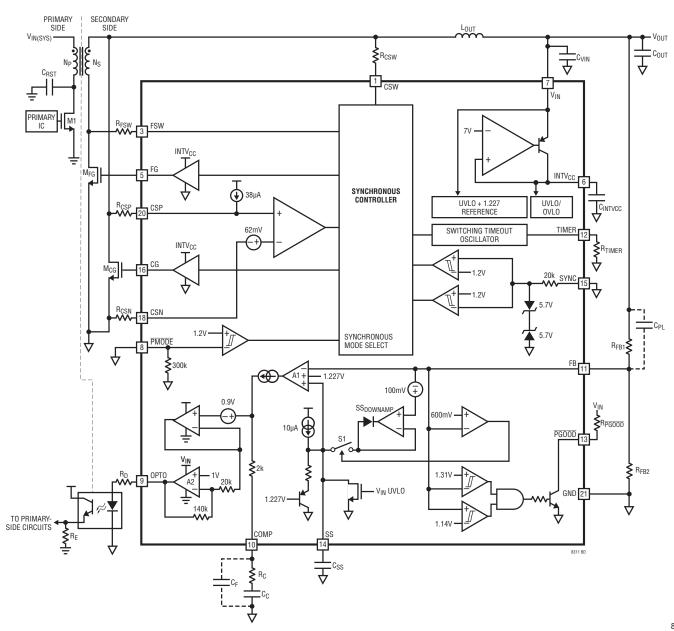

### **BLOCK DIAGRAM**

The LT8311 controls the synchronous MOSFETs and optocoupler on the secondary side of a forward converter. Synchronous control of low  $R_{DS(ON)}$  MOSFETs can typically lead to lower power dissipation in forward converters. The lower power dissipation can improve converter efficiency, resulting in long term cost savings by lowering input power requirements to support a certain level of output power. Improved efficiency can also reduce the size of heat sinks required to dissipate the heat generated in the rectifiers; consequently increasing the operating ambient temperature range which may be useful in many industrial applications.

The LT8311 also offers opto-coupler control for accurate output voltage regulation over line and load. The LT8311's opto-coupler control circuitry comes with a host of start-up and steady-state functions to ensure robust transient response during power-on and output short-circuit recovery.

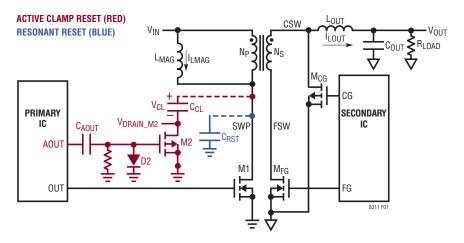

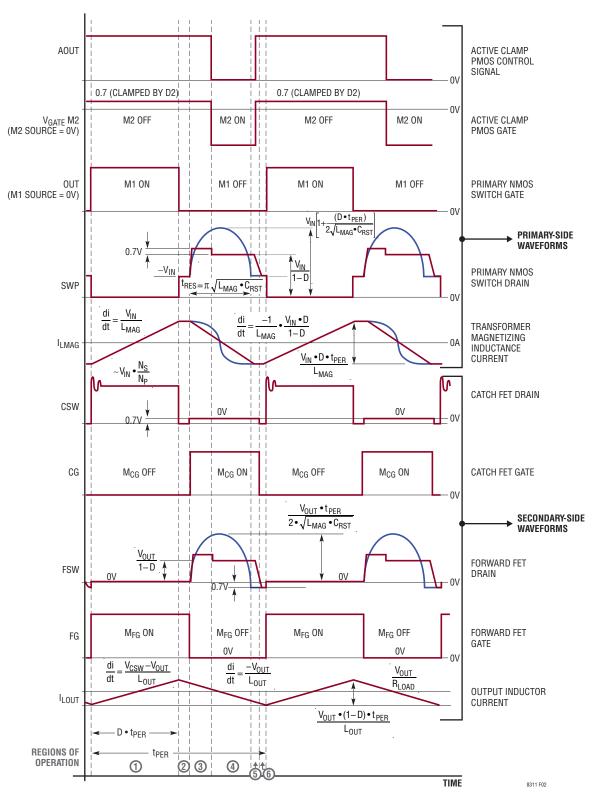

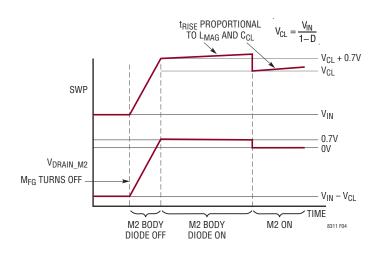

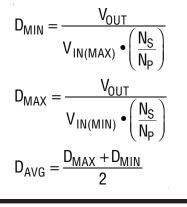

#### FUNDAMENTALS OF FORWARD CONVERTER OPERATION IN CCM

The timing diagram of a forward converter operating in continuous conduction mode (CCM) is shown in Figure 2. The timing diagram is broken into six regions of operation. Please refer to Figures 1 and 2 for the following explanation of each region of operation.

### Region 1 (Figure 2)

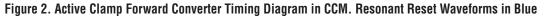

When OUT goes high, M1 turns on. CG should already be at OV before OUT goes high, to ensure that  $M_{CG}$  does not cross conduct with M1. The LT8311's preactive mode, which will be explained later, is an innovative scheme to turn off  $M_{CG}$  before M1 turns on. FG must be high during this period to keep the forward MOSFET,  $M_{FG}$  on, thereby conducting the output inductor current,  $I_{LOUT}$ , (via the transformer's secondary winding) through a low impedance path. During this phase, magnetizing current,  $I_{LMAG}$ , builds up in the transformer's magnetic core, and flows from  $V_{IN}$  to GND through M1. Output inductor current,  $I_{LOUT}$ , ramps up at a rate of  $(V_{CSW} - V_{OUT})/L_{OUT}$ .

#### Region 2 (Figure 2)

When OUT goes low, and turns off M1, the transformer becomes high impedance, and stops conducting  $I_{LOUT}$ . Since current in the output inductor cannot go to zero instantaneously, it pulls the drain of the catch MOSFET, CSW, towards ground. Ultimately CSW gets clamped at a diode voltage below ground by  $M_{CG}$ 's body diode which now sources the output inductor current (similar to a catch diode in a traditional buck converter). CSW collapsing equivalently causes the transformer's secondary winding voltage to become smaller. Through transformer action,

Figure 1. Forward Converter with Active Clamp Reset (in Red) or Resonant Reset (in Blue)

the primary winding voltage gets smaller too, effectively moving SWP towards V<sub>IN</sub>. Since  $M_{FG}$  is still on, and  $M_{CG}$ 's body diode is on, the secondary winding voltage gets clamped at about a diode voltage. Through transformer action, SWP gets clamped to approximately V<sub>IN</sub>. I<sub>LMAG</sub> flows in the secondary windings, as shown in Figure 3, flowing from the drain to source of  $M_{FG}$ , to ground.  $M_{CG}$ 's body diode sources I<sub>LOUT</sub> and I<sub>LMAG</sub>.

#### Region 3 (Figure 2)

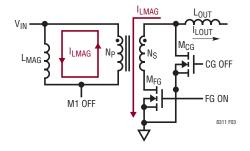

When FG goes low, it allows transformer reset action to begin.  $I_{LMAG}$  no longer has a low impedance path through  $M_{FG}$  on the secondary side. As a result, it "jumps back" to the primary side, flowing into the primary-side resonant

capacitor. In resonant reset,  $I_{LMAG}$  flows into  $C_{RST}$  as soon as  $M_{FG}$  turns off, causing SWP's voltage to rise up quasisinusoidally, with a time constant set by  $L_{MAG}$  and  $C_{RST}$ . In active clamp reset, when  $M_{FG}$  turns off,  $I_{LMAG}$  initially slews up SWP's voltage quickly. As shown in Figure 2,  $I_{LMAG}$ does not flow into the active clamp capacitor as soon as  $M_{FG}$  turns off. The voltage across  $C_{CL}$  (=  $V_{CL} = V_{IN}/(1-D)$ ) initially reverse biases M2's body diode. Only when SWP's voltage gets high enough to forward bias M2's body diode, does  $I_{LMAG}$  begin to flow into  $C_{CL}$ . The voltage where this happens is when SWP =  $V_{CL}$  + 0.7V. At this point, SWP's voltage rises up at a rate determined by the time constant of  $L_{MAG}$  and the active clamp capacitor, which is typically much larger than the resonant reset capacitor.

Figure 3. With FG On,  $I_{LMAG}$  Is Conducted Through  $M_{FG}$  to Ground on the Secondary Side When M1 Turns Off

Figure 4. Detail of Region 3 from the Timing Diagram in Figure 2. When  $M_{FG}$  Turns Off in Active Clamp Reset,  $I_{LMAG}$  Initially Slews Up SWP's Voltage from  $V_{IN}$  to  $V_{CL}$  + 0.7V, at Which Point M2's Body Diode Turns On and Allows  $I_{LMAG}$  to Flow into  $C_{CL}$

The ultimate goal of both reset mechanisms is to raise the SWP node to a voltage higher than  $V_{IN}$ , imposing appropriate volt seconds on  $L_{MAG}$ , and allowing the magnetizing current to reset. Resetting the magnetic core every cycle prevents magnetic flux buildup within the core, and thereby prevents transformer saturation. FSW tracks the SWP node during transformer reset. CG going high, allows  $I_{LOUT}$  to switch over from being conducted by  $M_{CG}$ 's body diode to  $M_{CG}$  itself.

### Region 4 (Figure 2)

- Active Clamp Reset Case (red waveform): AOUT going low causes the gate of M2 to be driven below ground by the decoupling capacitor, C<sub>AOUT</sub>. This causes M2, the active clamp PMOS, to turn on. M2 must be turned on before I<sub>LMAG</sub> becomes negative, to allow I<sub>LMAG</sub> to sustain conduction through the active clamp capacitor and get fully reset. Active clamp reset completes by the end of region 4, and I<sub>LMAG</sub> is reset to a negative value.

- 2. **Resonant Reset Case** (blue waveform): Resonant reset ultimately completes when SWP's quasi-sinusoidal waveform returns to V<sub>IN</sub>, by which point I<sub>LMAG</sub> is reset to a negative value. FSW is eventually clamped by M<sub>FG</sub>'s body diode, and conducts I<sub>LMAG</sub>, through the secondary windings, towards the output inductor (similar to Figure 3, but with I<sub>LMAG</sub> direction reversed on primary and secondary sides). With a diode voltage imposed across the secondary windings, transformer action

causes the primary winding to have a similar voltage (scaled by turns ratio), resulting in SWP's voltage getting clamped to  $V_{IN}$ .  $M_{CG}$  continues conducting  $I_{LOUT} - I_{LMAG}$ .

#### Region 5 (Figure 2)

Active Clamp Reset Case: AOUT goes high, turning off M2. I<sub>LMAG</sub>, being negative, causes the voltage on SWP (M1's drain) to get pulled towards  $V_{IN}$ , resulting in the transformer's primary winding voltage becoming smaller. By transformer action, the secondary winding voltage also becomes smaller. With M<sub>CG</sub> on (holding CSW at 0V), and the transformer secondary winding voltage becoming smaller, FSW collapses towards 0V.

#### Region 6 (Figure 2)

Eventually, in similar fashion to the resonant reset case, FSW is clamped to a diode voltage below GND by  $M_{FG}$ 's body diode, which now conducts  $I_{LMAG}$  through the secondary windings, towards the output inductor. With  $M_{FG}$ 's body diode on, and  $M_{CG}$  on, the secondary winding voltage gets clamped to about a diode voltage. Through transformer action, SWP gets clamped to approximately  $V_{IN}$ . CG goes low, turning off  $M_{CG}$  before M1 can turn on.  $I_{LOUT} - I_{LMAG}$  is conducted through  $M_{CG}$ 's body diode. FG goes high, turning on  $M_{FG}$ . Eventually, when M1 turns on,  $I_{LOUT}$  will be conducted through the transformer's secondary winding, and will flow from the source to drain of  $M_{FG}$ .

83111

#### LT8311 SYNCHRONOUS CONTROL SCHEMES

The LT8311 offers two modes of synchronous control:

- Preactive Mode: No pulse transformer needed; DCM operation at light load. Enabled by tying the PMODE pin to 0V. Use a Schottky diode across M<sub>CG</sub> (Figure 20).

- 2. **SYNC Mode:** Pulse Transformer needed; FCM or DCM operation at light load. Enabled by tying the  $\overline{\text{PMODE}}$  pin to  $\text{INTV}_{\text{CC}}$ .

#### PREACTIVE MODE SYNCHRONOUS CONTROL

#### M<sub>CG</sub> Turn-On/Off Timings in Preactive Mode

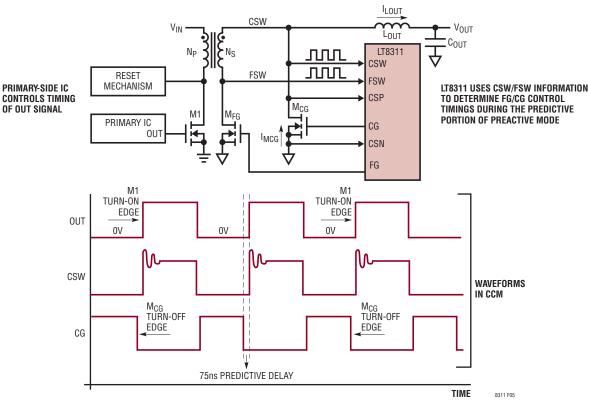

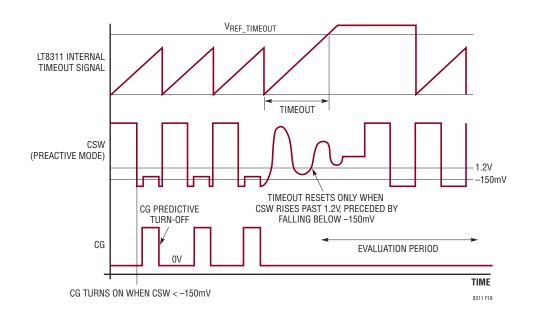

"Preactive" is short for "predictive" + "reactive". In preactive mode, the LT8311 controls the secondary synchronous MOSFETs without any communication from the primary-side IC. In preactive mode, the catch MOSFET,  $M_{CG}$ , is turned on (CG rising edge in Figure 5) when the voltage on its drain, CSW, is detected to be below –150mV, and the forward MOSFET,  $M_{FG}$ , is detected to be off.  $M_{CG}$  is turned off when the first of two events after  $M_{CG}$ 's turnon occurs:

- Predictive M<sub>CG</sub> Turn-Off (Figure 5): In predictive turnoff, the LT8311 predicts when M1 will turn on in the next cycle, and turns off M<sub>CG</sub> 100ns prior to this event. Predictive turn-off of M<sub>CG</sub> prevents cross conduction between M<sub>CG</sub> and M1. M1's turn-on timings are predicted by phase locking to the rising edge of present and past CSW cycles. Predictive turn-off relies on the periodicity of M1's turn-on edge, an inherent aspect of fixed-frequency operation. Furthermore, the predictive turn-off is designed to be independent of the duty cycle of the system, which allows M<sub>CG</sub> to be correctly turned off, even during load/line transients. Predictive turn-off will typically be the dominant turn-off mechanism for M<sub>CG</sub> in CCM.

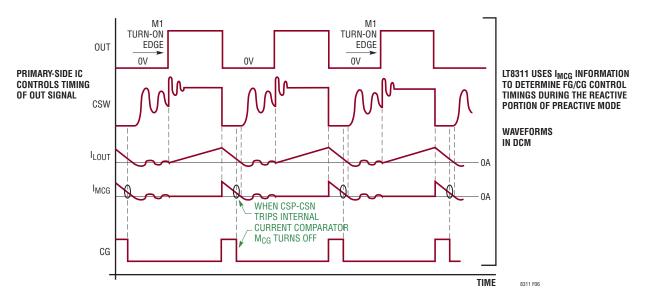

- **Reactive M<sub>CG</sub> Turn-Off** (Figure 6): Reactive turn-off forces the forward converter to operate in DCM at light load. In reactive turn-off, the LT8311 turns off  $M_{CG}$  when the current in  $M_{CG}$  (I<sub>MCG</sub>) trips the LT8311's internal current comparator. The inputs to this current comparator are the CSP and CSN pins. Typically, the CSP and CSN pins will be configured to trip at almost

zero current in  $M_{CG}$ , which should correspond to nearly zero current in the output inductor. Reactive turn-off will typically be the dominant turn-off mechanism for  $M_{CG}$  in DCM.

The LT8311's seamless transition between predictive and reactive portions of preactive mode allows the catch MOSFET to be turned off at the correct time to avoid cross conduction or avalanching.

#### M<sub>FG</sub> Turn-On/Off in Preactive Mode

In preactive mode,  $M_{FG}$  is turned on after  $M_{CG}$ 's turn-off edge is detected, and the voltage on the drain of the forward MOSFET, FSW, is detected to be below 1.2V. Waiting for FSW to fall below 1.2V ensures that transformer reset is close to completion.  $M_{FG}$  is turned off when the voltage on CSW is detected to be below –150mV.

Since preactive mode requires each MOSFET to be turned on only after the other MOSFET's turn-off edge is detected, the system requires a start point where one of the two MOSFETs begins switching. Preactive mode's start point happens by turning on  $M_{CG}$  first to commence switching.

#### Preactive Mode Shutdown and Start-Up

Preactive mode is designed with many features to facilitate smooth start-up of synchronous control and shut down of the scheme when necessary. Prior to starting switching activity, the LT8311 evaluates conditions on the forward converter's secondary side to determine if switching can commence. The evaluation period ends when four specific conditions, are satisfied for a period of three continuous CSW switching cycles (rising edge to rising edge). If any of the conditions are violated, the evaluation period is reset, and switching activity is kept shut off. During this evaluation period, the secondary side current will flow through the body diodes of  $M_{CG}$  and  $M_{FG}$ . The four conditions are:

- 1.  $V_{\mbox{\rm IN}}$  must be greater than its UVLO voltage

- 2. INTV<sub>CC</sub> must be within its UVLO/OVLO limits

- 3. The TIMER pin should not have timed out. This feature exists to ensure that the LT8311 ceases switching in the event that the primary side stops switching.

Figure 5. During the Predictive Portion of Preactive Mode, the LT8311 Phase Locks into the CSW Rising Edge and Turns Off  $\rm M_{CG}$  75ns Prior to This Edge

Figure 6. During the Reactive Portion of Preactive Mode, the LT8311 Turns Off M<sub>CG</sub> When the Current in M<sub>CG</sub>, I<sub>MCG</sub>, Trips the LT8311's Internal Current Comparator. The Inputs to the Comparator Are CSP and CSN and the Current Sense Trip Voltage Is Programmed by Choosing Appropriate CSP/CSN Series Resistors

4. The CSP and CSN pins must not trip the internal current comparator within a 150ns period of time called "current sample window." This function helps the LT8311 detect very light load conditions, during which time it will keep synchronous conduction shut off, thereby improving system efficiency.

#### How the current sample window works:

The current sample window exists regardless of whether  $M_{CG}$  is turned on or not, in any given cycle. When CSW is detected to fall below -150mV, the LT8311 starts a blank time of 200ns. Upon completion of this blank time, the LT8311 starts a 150ns current sample window. If the CSP/CSN pin inputs cause the internal current comparator to trip during this 150ns window, the LT8311 will interpret this as a condition of very light load, at which point it will stop synchronous conduction and start the evaluation period again. Please see "Configuring CSP/CSN Inputs of Current Sense Comparator in Preactive Mode" in the Applications Information section.

When all four conditions are valid for three continuous CSW cycles, the evaluation period ends and the LT8311 gets ready to start switching. Switching commences with the LT8311 turning on  $M_{CG}$  for its minimum on-time. If any of the four conditions listed are violated at any point during switching activity, the LT8311 will shut down all synchronous conduction and restart the evaluation period.

During preactive mode start-up, the LT8311 internally softstarts the on-time of  $M_{CG}$ , allowing the forward converter to gradually transition from full cycles of nonsynchronous  $M_{CG}$  conduction (secondary-side current flowing through body diode of  $M_{CG}$ ) to full cycles of synchronous  $M_{CG}$ conduction.

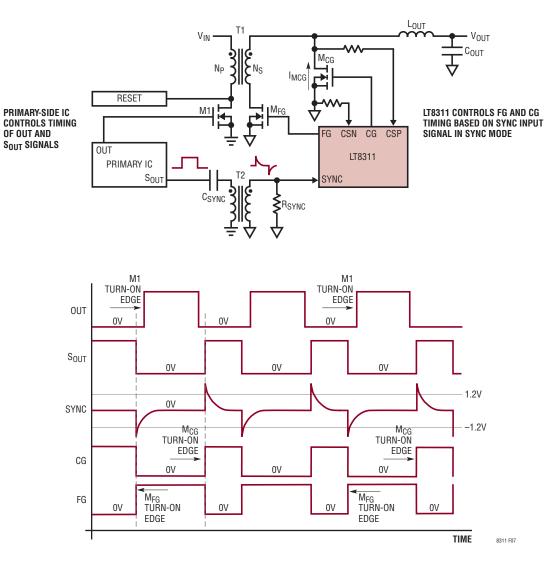

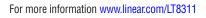

#### SYNC MODE SYNCHRONOUS CONTROL

SYNC mode allows the LT8311 to operate in forced continuous mode (FCM) at light loads. In SYNC mode, a pulse transformer (see T2 in Figure 7) is required to allow the LT8311 to receive synchronization control signals from the primary-side IC. These control signals are interpreted digitally (high or low) by the LT8311 to turn on/off the catch and forward MOSFETs.

FCM operation allows the forward converter to avoid operation in discontinuous conduction mode (DCM) at light loads, by letting the inductor current go negative. Hence, even at zero load, the inductor current remains continuous and the converter runs at a fixed frequency.

#### M<sub>CG</sub> Turn-On/Off Timings in SYNC Mode

In SYNC mode,  $M_{CG}$  turns on when the signal on the SYNC pin is higher than 1.2V.  $M_{CG}$  turns off when the signal on the SYNC pin is lower than -1.2V.

#### $M_{FG}\ Turn-On/Off\ Timings\ in\ SYNC\ Mode$

In SYNC mode,  $M_{FG}$  turns on when the signal on the SYNC pin is lower than -1.2V.  $M_{FG}$  turns off when the signal on the SYNC pin is higher than 1.2V.

The R<sub>SYNC</sub> and C<sub>SYNC</sub> time constant must be appropriately chosen to generate a sufficient pulse width at a particular overdrive voltage (see "Picking Pulse Transformer and High Pass Filter" in the Applications Information section). Typical values for C<sub>SYNC</sub> and R<sub>SYNC</sub> are 220pF and 560 $\Omega$ , respectively.

#### SYNC Mode Shutdown

In SYNC mode, the LT8311 will shut off both secondary-side MOSFETs,  $M_{CG}$  and  $M_{FG},$  if any of the following conditions are true:

- 1.  $V_{IN}$  is less than its UVLO voltage

- 2. INTV<sub>CC</sub> outside its UVL0/0VL0 limits

- 3. The TIMER pin has timed out (see the Applications Information section for details on programming the TIMER pin resistor).

- 4. The CSP and CSN pins have tripped the LT8311's internal current comparator during  $M_{CG}$ 's on-time. The current in  $M_{CG}$ ,  $I_{MCG}$ , is sensed after a 400ns blank time has expired. This blank time starts at the turn-on edge of  $M_{CG}$ . See the Applications Information section for details on configuring the CSP and CSN pins in SYNC mode.

Figure 7. In SYNC Mode, the Primary Side IC Sends S<sub>OUT</sub> Signals Through a Pulse Transformer to the LT8311's SYNC Pin. SYNC < 1.2V Turns on M<sub>FG</sub> and Turns Off M<sub>CG</sub>. SYNC > 1.2V Turns On M<sub>CG</sub> and Turns Off M<sub>FG</sub>

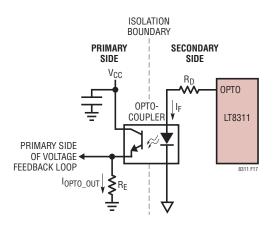

#### **OPTO-COUPLER CONTROL**

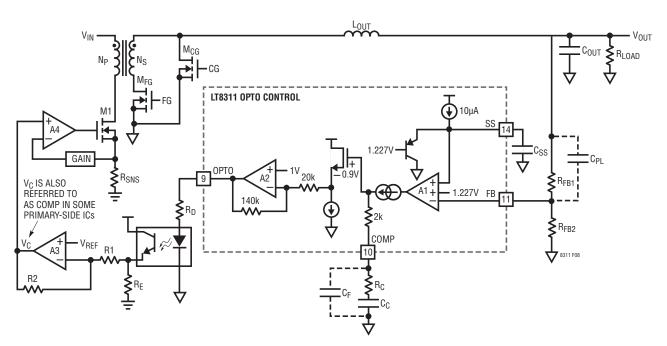

The LT8311 offers opto-coupler control to allow output voltage feedback from the secondary to the primary side in a forward converter. Used in conjunction with a primary-side IC, the entire system offers fixed frequency peak current mode control that has excellent line/load regulation and quick transient response.

A basic understanding of the LT8311's opto-coupler control scheme can be obtained by referring to Figure 8. The LT8311 senses the output voltage through a resistor divider ( $R_{FB1}$  and  $R_{FB2}$ ) connected to its FB pin. The FB pin voltage is compared to the lower of two inputs:

- An internal voltage reference of 1.227V

- Soft-start (SS) pin

At start-up, the SS pin capacitor,  $C_{SS}$ , is charged up by the LT8311's internally trimmed 10µA current source. Since FB tracks the lower of the SS pin and the 1.227V refer-

ence, the FB pin (and by extension the output voltage) is forced to soft-start at the slew rate set by the capacitor,  $C_{SS}$ , connected to the SS pin.

**NOTE:** To ensure that the soft-start time of the converter is controlled by the LT8311's SS capacitor,  $C_{SS}$ , it is important to program the primary IC's soft-start faster, to get out of the way. If this is not done, the converter's soft-start time will be dominated by the primary IC's soft start, and the LT8311 will simply adjust its SS pin voltage and slew rate to match the slower soft start time set by the primary-side IC.

When the SS pin voltage gets higher than the 1.227V reference, the FB pin starts to track the 1.227V reference. The output, therefore, regulates at a voltage set by the  $R_{FB1}/R_{FB2}$  divider network, and the FB pin's regulation voltage of 1.227V. The SS pin capacitor continues to get charged up by the 10µA current source until it reaches its internal clamp voltage of 2V.

Figure 8. The LT8311 Provides Voltage Feedback, as Part of a Peak Current Mode Control System, in a Forward Converter

Figure 9. Flowchart for LT8311 Opto Control Operation at Start-Up

With SS charged up to 2V, the transconductance error amplifier, A1, sinks or sources current from its output, COMP, if there is any voltage difference between the FB pin voltage and the 1.227V reference. The COMP pin, offset by 0.9V, serves as the input to the opto-driver, A2. If an increase in output load current causes the FB pin voltage to be lower than 1.227V, A1 drives the COMP pin high. COMP going high forces A2 to drive OPTO low, sourcing less current through  $R_D$  into the opto-coupler.

Since an opto-coupler's output current is directly proportional to its input current, this decreased input current for the opto-coupler will cause its output current, and therefore its emitter voltage at  $R_E$ , to decrease as well. The drop in  $R_E$  voltage causes A3, through its inverting action, to drive its output,  $V_C$ , higher. An increase in the  $V_C$  voltage causes the comparator, A4, to command a higher sense voltage across the  $R_{SNS}$  resistor, commanding M1 to run at a higher peak current. Since the current through M1 is

directly proportional to the output inductor current (M1 Current •  $N_P/N_S = I_{LOUT}$ ), an increase in M1's peak current translates into an increase in the output inductor's peak current. In essence, the feedback loop is commanding the output inductor peak current to meet the demands of the increased load current, with the ultimate goal of helping the output voltage recover from a load step and stay regulated.

#### **Opto-Control Operation at Start-Up**

For applications connecting the LT8311's V<sub>IN</sub> pin directly to the converter output, the LT8311 includes intelligent circuitry to ensure no interruption in the switching of the primary-side MOSFET upon the LT8311's turn-on. The LT8311 turns on when its V<sub>IN</sub> pin (and therefore the converter output voltage when VIN is directly connected to the output) exceeds 3.7V. Without intelligent circuitry, this V<sub>OUT</sub> level will cause the FB pin voltage of the LT8311 to be greater than the voltage on the LT8311's SS pin (which is typically at OV upon turn-on of the IC), causing amplifier A1 to drive the COMP pin low. This drives the OPTO pin high, which causes full current into the opto-coupler and terminates switching of the primary-side MOSFET. Termination of the primary-side MOSFET's switching can lead to the converter's output voltage dropping, which could cause the LT8311 to lose power and shut off. The LT8311's intelligent circuitry prevents this situation using two unique features. It has a built-in 100mV hysteresis on

its V<sub>IN</sub> UVLO voltage, so that upon getting power, it can tolerate up to a 100mV drop on its V<sub>IN</sub> pin before losing power again. Even more importantly, the LT8311 has an opto-control start-up system that keeps the LT8311's "opto-control brains" turned off until all relevant node voltages within the voltage loop are prebiased to a state where they will not cause switching activity to cease when the loop is eventually enabled.

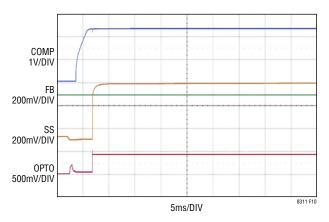

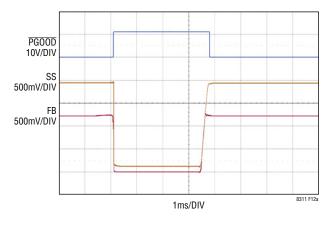

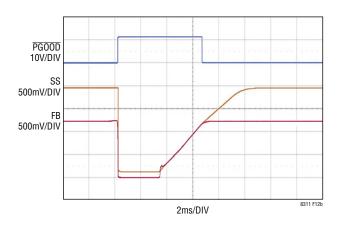

As shown in Figure 9 and the scope shot in Figure 10, the LT8311's opto-control operation at start-up involves slewing the SS pin voltage close to the FB pin voltage, slewing the COMP pin voltage to its high clamp voltage, and keeping the OPTO pin voltage held low. During this phase, the inductor current (and by extension, the output voltage) is controlled by the soft-start function provided by the primary-side IC. Upon completion of the state machine, the LT8311 allows the feedback loop to be functional again, and the FB pin voltage tracks the LT8311's SS pin voltage until FB finally gets to its regulation target of 1.227V.

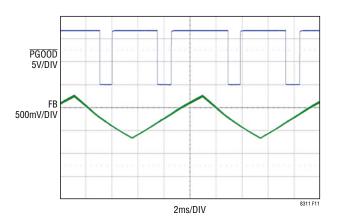

#### **Power Good**

The LT8311 offers output power good monitoring to assist with system level design. The LT8311's  $\overrightarrow{PGOOD}$  pin is pulled low internally when the FB pin voltage stays within a  $\pm 7\%$  window of the 1.227V reference for a period of 175µs. Waiting for 175µs to elapse prevents the  $\overrightarrow{PGOOD}$  pin from indicating false positives during transient events.

The  $\overline{PGOOD}$  comparator has ±3% hysteresis. Therefore, when the FB pin voltage is driven away from its regulated value of 1.227V by ±10%, the  $\overline{PGOOD}$  pin's internal pulldown shuts off immediately. As a result, the pin is pulled high by an external resistor or external current source connected to a supply voltage. The  $\overline{PGOOD}$  pin's output can be fed to a microcontroller that make decisions based on the state of the output voltage.

# Output Overshoot Control Helps with Short-Circuit Recovery

The LT8311 provides output overshoot control by activating its soft-start pull-down amplifier (SS<sub>DOWNAMP</sub> in the Block Diagram) any time the FB pin voltage is less than 50% of the FB reference voltage (1.227V). This is particularly helpful with output voltage recovery after the removal of a short-circuit condition or after a heavy load transient. The SS pull-down amplifier will sink whatever current is

(a) Output Overshoot Control with  $C_{SS} = 1nF$ . LT8311  $V_{IN}$ Powered from a 12V Housekeeping Supply, Which Also Pulls Up on the PGOOD Pin Through a 100k External Resistor

Figure 12. Output Overshoot Control at Start-Up

necessary (up to its maximum sink capability of 13mA), to ensure that the SS pin voltage gets no higher than 100mV above the FB pin voltage. During output short-circuit events, when the FB pin voltage is pulled to ground, the SS pulldown amplifier gets activated and pulls the SS pin voltage to 100mV above the FB pin voltage. Eventually, when the short-circuit condition is over, the FB pin voltage gradually rises up with the SS pin at a slew rate set by C<sub>SS</sub> and the 10µA charge current. This allows the output to recover gradually from the short-circuit condition. Note that when the LT8311 has its V<sub>IN</sub> pin powered directly from the output of the forward converter, it will lose all its brains during a short-circuit event. Under this scenario, output overshoot control will not be in effect until the LT8311 gets brains again, until which point, the output inductor current and the output voltage will be controlled by the primary-side IC's soft-start function.

(b) Output Overshoot Control with  $C_{SS} = 33nF$ . LT8311  $V_{IN}$ Powered from a 12V Housekeeping Supply, Which Also Pulls Up on the PGOOD Pin Through a 100k External Resistor

#### VIN BIAS SUPPLY

The LT8311's  $V_{IN}$  pin can be powered in various ways. Place at least a  $2.2\mu F$  ceramic bypass capacitor close to the pin.

Picking an appropriate bias supply to power up the LT8311 requires consideration of the following criteria:

- 1. The  $V_{IN}$  pin, in certain configurations, may be the only supply to the LT8311's INTV<sub>CC</sub> pin, which provides gate drive to the catch and forward MOSFETs. In such situations,  $V_{IN}$ 's bias supply must be high enough to provide adequate gate-drive voltage (typically 5V to 7V) for both synchronous MOSFETs.

- 2. V<sub>IN</sub>'s bias supply must be able to source:

- a. LT8311's VIN current (4.5mA typical)

- b.  $INTV_{CC}$  gate-drive current when using  $V_{IN}$  to supply the  $INTV_{CC}$  pin (typically 10mA to 30mA)

- c. Opto-driver source current (typically 1mA to 5mA)

- 3. V<sub>IN</sub> start-up and short-circuit conditions:

- a. V<sub>IN</sub> must come up in reasonable time to allow the LT8311 to begin synchronous and opto-coupler control. While synchronous control is shut off, the secondary-side current will flow through the body diodes of the secondary synchronous MOSFETs. While opto-control is off, the forward converter will operate open-loop, using a volt-second clamp to control V<sub>OUT</sub> if operating with LT3752, LT3752-1 or LT3753 on the primary side.

- b. V<sub>IN</sub> may be shorted to GND during transient events. For instance, V<sub>IN</sub> powered from the output voltage, will be driven to 0V during an output short-circuit. The forward converter must be able to ride through the momentary loss of power to the LT8311, which is often easily accomplished by appropriately configuring soft-start control on the primary-side ICs. Refer to the LT3752/LT8310 data sheets for details on configuring soft-start control on the primary-side IC.

With the previous criteria in mind, there are three methods (1-3), listed below, for powering up the LT8311. For preactive mode, use method 1, 2 or 3. For SYNC mode FCM, use method 1 or 3; for DCM, use method 1, 2 or 3.

- 1. Power from the LT3752's housekeeping supply (see Figure 21 in the Typical Application section). Being a flyback converter rather than a LDO, the LT3752's housekeeping supply is an efficient supply source. It can be connected through an external winding to the LT8311's  $V_{IN}$  and  $INTV_{CC}$  pins, and can be set high enough to provide adequate gate drive for the catch and forward MOSFETs, but low enough to minimize efficiency and thermal losses. The housekeeping supply comes up as soon as the LT3752 receives input power, so power is delivered to the LT8311 without delay.

- 2. Power directly from  $V_{OUT}$ . At output voltages lower than 10V, careful consideration must be given to the output voltage start-up time, ensuring that the LT8311 can turn on and provide synchronous/opto control well before the output voltage approaches regulation. It is also important to ensure, at these lower output voltages, that sufficient gate drive voltage can be provided to the external MOSFETs. At higher V<sub>OUT</sub> voltages, efficiency and thermal considerations related to the IC's internal power dissipation can become important criteria. In addition, at higher V<sub>OUT</sub> voltages, it is important to ensure that voltage transients on the V<sub>IN</sub> pin do not exceed the pin's abs max rating of 30V.

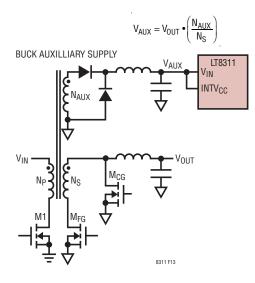

- 3. Use a buck circuit from an auxiliary transformer winding, as shown in Figure 13. This circuit has the benefit of being highly efficient, and is fairly simple to design. It is particularly useful for low output voltage applications (3.3V or 5V) that do not have an external house-keeping supply, and where powering directly from the output voltage is inadequate. In this configuration, the buck circuit's output voltage derives its energy from secondary-side switching pulses that also source energy to the forward converter's main output voltage, V<sub>OUT</sub>. Careful consideration must be given to ensure that the buck output voltage comes up well in time, and turns on the LT8311 to provide synchronous and opto control before the forward converter's actual output voltage gets close to regulation. If there is a need to speed up

the time taken by the buck converter output voltage to get to its target, relative to the forward converter's main output voltage, often a simple technique is to slow down the main output voltage start-up time by increasing the soft-start capacitor on the primary-side IC.

### INTV<sub>CC</sub> BIAS SUPPLY

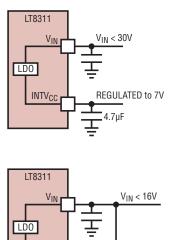

The INTV<sub>CC</sub> pin powers the catch and forward MOSFET gate drivers of the LT8311. Two configurations exist for biasing up the INTV<sub>CC</sub> pin, as shown in Figure 14:

1. In the first configuration, the LT8311's on-chip LDO regulates the INTV<sub>CC</sub> pin voltage from the  $V_{IN}$  supply. When the  $V_{IN}$  pin voltage is low, the internal LDO will operate in drop-out, driving the  $INTV_{CC}$  pin to about 400mV below the  $V_{IN}$  pin voltage. When the  $V_{IN}$  pin voltage is high, the internal LDO will regulate INTV<sub>CC</sub>'s voltage to 7V. Ensure that V<sub>IN</sub>'s supply voltage does not exceed V<sub>IN</sub>'s abs max voltage of 30V. If INTV<sub>CC</sub> drops below its UVLO voltage (4.6V rising and 4.3V falling), all synchronous switching will be stopped. The maximum guaranteed current that the INTV<sub>CC</sub> LDO can source is 40mA. Ensure that the total gate charge  $(Q_q)$  current required by both secondary MOSFETs,  $M_{CG}$  and  $M_{FG}$ , is less than 40mA:

$I_{MOSFET_TOTAL} = f_{SW} \bullet (Q_{g_MCG} + Q_{g_MFG}) < 40 \text{mA}$

where f<sub>SW</sub> is the converter's switching frequency,  ${\rm Q}_{g\_MCG}$  is the gate charge (  ${\rm Q}_g)$  rating of  ${\rm M}_{CG}$  and  ${\rm Q}_{g\_MFG}$ is the gate charge ( $Q_{q}$ ) rating of M<sub>FG</sub>.

This configuration, utilizing the LT8311's internal LDO, will suffice for most applications, limited only by thermal considerations related to the LDO's power dissipation. Keeping the power dissipation to a minimum will help lower the operating junction temperature of the LT8311, potentially allowing the system to operate over a wider ambient temperature range:

LDO Power Dissipation =  $(V_{IN} - INTV_{CC}) \bullet I_{MOSFET}$  TOTAL

LT8311 Operating Junction Temperature  $\approx$  $\theta_{JA} \bullet (V_{IN} \bullet 4.5 \text{mA} + \text{LDO Power Dissipation} + V_{IN} \bullet$  $I_{\text{OPTO}}$ ) +  $T_{\text{A}}$

where  $\theta_{JA}$  is LT8311's junction-to-ambient thermal resistance and is typically 38°C/W; I<sub>OPTO</sub> is the current

Figure 13. Buck Circuit Generates V<sub>AUX</sub> Supply, Which Powers LT8311's VIN and INTV<sub>CC</sub> Pins

8311 F14

**INTV**<sub>C</sub>

sourced into the opto-coupler by the LT8311's OPTO pin; 4.5mA is the typical V<sub>IN</sub> current of the LT8311;  $T_A$  is the ambient temperature.

2. In the second configuration, the V<sub>IN</sub> pin's bias supply drives the INTV<sub>CC</sub> pin through a direct connection, bypassing the internal LDO. This configuration reduces power dissipation inside the IC by not having to incur any power loss within the INTV<sub>CC</sub> LDO. Use this optional configuration for V<sub>IN</sub> voltages that are below 16V, allowing sufficient margin for INTV<sub>CC</sub> to stay below its OVLO(+) voltage of 16.5V. Ensure that V<sub>IN</sub>, during transients, does not exceed INTV<sub>CC</sub>'s abs max voltage of 18V.

When an external supply or auxiliary winding is available, use this configuration (tying  $V_{IN}$  and  $INTV_{CC}$  together) to deliver power to the IC. This configuration is most applicable when using the LT3752 as a primary-side IC. The LT3752's housekeeping supply can be connected to the LT8311's  $V_{IN}$  and  $INTV_{CC}$  through an auxiliary winding, as shown in Figure 21 in the Typical Applications section.

$INTV_{CC}$  should be bypassed with a minimum of  $4.7\mu F$  ceramic capacitor to ground for all three configurations.

Place the capacitor close to the  $INTV_{CC}$  pin, ensuring that the ground terminal of the capacitor has the shortest possible return path to the LT8311's ground (exposed pad).

### LT8311 OPTO CONTROL FUNDAMENTALS

#### **Setting Output Voltage**

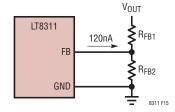

Figure 15 shows how to program the forward converter's output voltage with a resistor divider feedback network. Connect the top of  $R_{FB1}$  to  $V_{OUT}$ , the tap point of  $R_{FB1}/R_{FB2}$  to the FB pin, and the bottom of  $R_{FB2}$  to ground. The ground return of  $R_{FB2}$  must be kept as close as possible to the ground of the LT8311, and must be kept away from the forward converter's power path. The power path contains switching currents, and possibly large value currents (depending upon the load) which may introduce unintended noise, or I • R drops into the FB resistor divider path. The FB pin regulates to 1.227V and has a typical input pin bias current of 120nA flowing out of the pin. The output voltage is set by the formula:

$$V_{OUT} = 1.227 \bullet \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) - 120nA \bullet R_{FB1}$$

Figure 15. Setting Output Voltage of Forward Converter

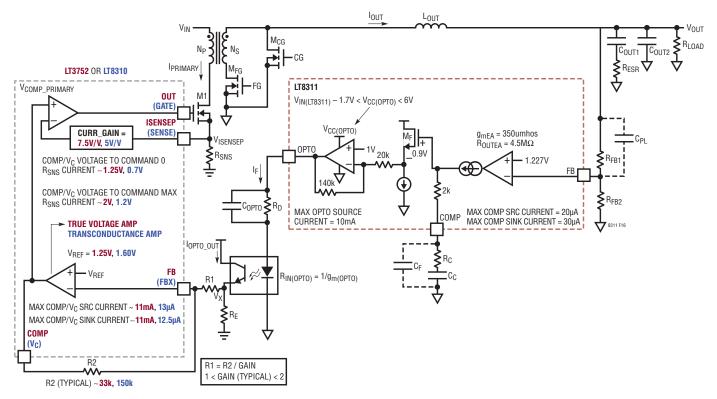

Figure 16. Forward Converter Voltage Feedback Loop with LT8311 on Secondary Side and LT3752 (or) LT8310 on Primary Side

#### **Picking Loop Compensation Components**

Figure 16 shows a typical loop associated with a forward converter, using the LT8311 on the secondary side, and the LT3752 or LT8310 as the primary-side ICs. Parametric values specific to the LT3752 are shown in red, while those specific to the LT8310 are shown in blue. The forward converter loop shown is a peak current mode control system.

The optimum values for loop compensation depend on the IC used on the primary side and the LT8311, as well as the operating conditions of the converter (input voltage range, output voltage, load current, etc.). To compensate the voltage feedback loop around the LT8311, a series resistor/capacitor network is usually connected from the LT8311's COMP pin to GND. For most applications, the capacitor C<sub>C</sub> should be in the range of 4.7nF to 47nF, and the resistor R<sub>C</sub> should be in the range of 2k to 20k. If the R<sub>C</sub> value is too large, the part will be more susceptible to high frequency noise and jitter. If the R<sub>C</sub> value is too small,