## Fixed Ratio High Power Inductorless (Charge Pump) DC/DC Controller

## FEATURES

- Low Profile, High Power Density, Capable of 500W+

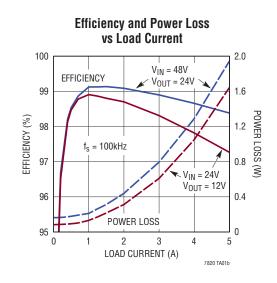

- Soft Switching: 99% Peak Efficiency and Low EMI

- V<sub>IN</sub> Max for Voltage Divider (2:1): 72V

- V<sub>IN</sub> Max for Voltage Doubler (1:2)/Inverter (1:1): 36V

- Wide Bias V<sub>CC</sub> Range: 6V to 72V

- Soft Startup into Steady State Operation

- 6.5V to 40V EXTV<sub>CC</sub> Input for Improved Efficiency

- Input Current Sensing and Overcurrent Protection

- Wide Operating Frequency Range: 100kHz to 1MHz

- Output Short-Circuit/OV/UV Protections with Programmable Timer and Retry

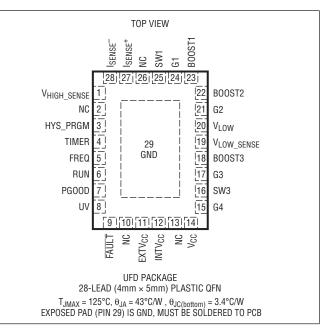

- Thermally Enhanced 28-Pin 4mm × 5mm QFN Package

## **APPLICATIONS**

- Bus Converters

- High Power Distributed Power Systems

- Communications Systems

- Industrial Applications

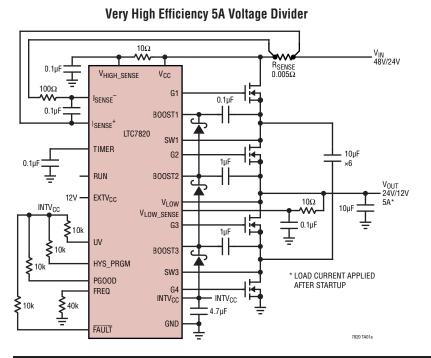

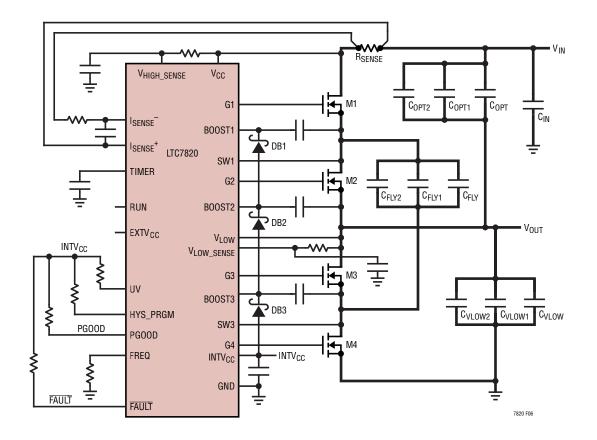

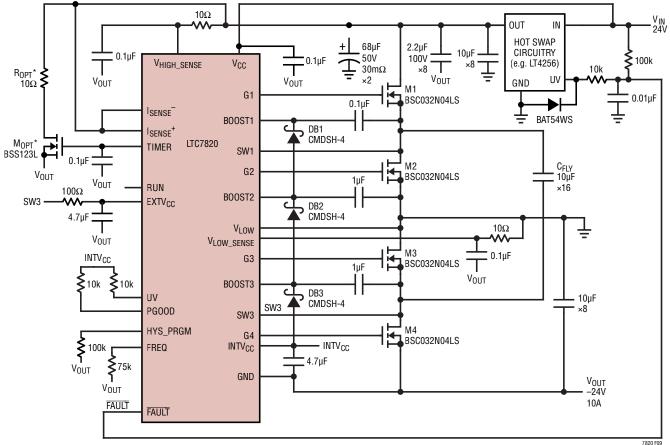

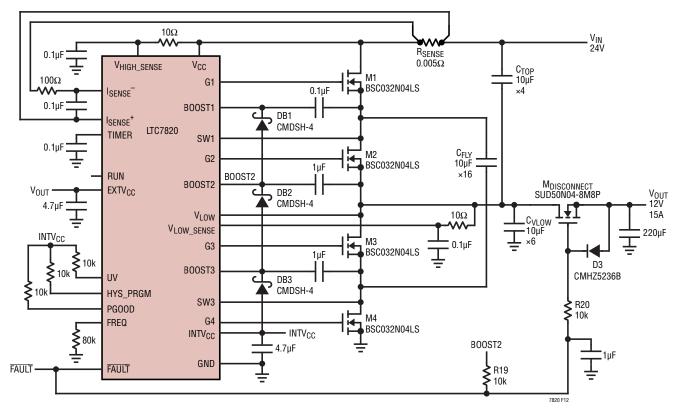

## TYPICAL APPLICATION

## DESCRIPTION

The LTC®7820 is a fixed ratio high voltage high power switched capacitor/charge pump controller. The device includes four N-channel MOSFET gate drivers to drive external power MOSFETs in voltage divider, doubler or inverter configurations. The device achieves a 2:1 stepdown ratio from an input voltage as high as 72V, a 1:2 step-up ratio from an input voltage as high as 36V, or a 1:1 inverting ratio from an input voltage up to 36V. Each power MOSFET is switched with 50% duty cycle at a constant pre-programmed switching frequency. System efficiency can be optimized to over 99%. The LTC7820 provides a small and cost effective solution for high power, non-isolated intermediate bus applications with fault protection.

The LTC7820 switching frequency can be linearly programmed from 100kHz to 1MHz. The device is available in a thermally enhanced 28-lead QFN package with some no-connect pins for high voltage compatible pin spacing.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 9484799.

7820fc

## ABSOLUTE MAXIMUM RATINGS

(Notes 1, 3)

| V <sub>CC</sub> , V <sub>HIGH_SENSE</sub><br>BOOST1               | -0.3V to 80V                 |

|-------------------------------------------------------------------|------------------------------|

| BOOST2, BOOST3                                                    |                              |

| SW1                                                               |                              |

| SW3                                                               | 5V to 45V                    |

| V <sub>LOW</sub> , V <sub>LOW_SENSE</sub>                         |                              |

| I <sub>SENSE</sub> <sup>+</sup> , I <sub>SENSE</sub> <sup>-</sup> |                              |

| (BOOST1 - SW1), (BOOST2 - V <sub>LOW</sub> )                      | 0.3V to 6V                   |

| (BOOST3 - SW3)                                                    | 0.3V to 6V                   |

| INTV <sub>CC</sub> , RUN                                          | 0.3V to 6V                   |

| EXTV <sub>CC</sub> , PGOOD                                        | 0.3V to 45V                  |

| HYS_PRGM, FREQ, TIMER, UV                                         | .–0.3V to INTV <sub>CC</sub> |

| FAULT                                                             | 0.3V to 80V                  |

| INTV <sub>CC</sub> Peak Current (Note 10)                         | 150mA                        |

| Operating Junction Temperature                                    |                              |

| Range (Notes 2, 11)                                               | –40°C to 125°C               |

| Storage Temperature Range                                         | –65°C to 150°C               |

## PIN CONFIGURATION

## ORDER INFORMATION http://www.linear.com/product/LTC7820#orderinfo

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC7820EUFD#PBF  | LTC7820EUFD#TRPBF | 7820          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC7820IUFD#PBF  | LTC7820IUFD#TRPBF | 7820          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 2). V<sub>CC</sub> = 12V, V<sub>RUN</sub> = 5V, unless otherwise specified.

| SYMBOL                           | PARAMETER                                                                                      | CONDITIONS                                                                                                                                       | MIN  | ТҮР          | MAX  | UNITS    |

|----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|----------|

| Input/Output Vol                 | tage                                                                                           |                                                                                                                                                  |      |              |      | ,        |

| V <sub>CC</sub>                  | IC Bias Voltage Range                                                                          |                                                                                                                                                  | 6    |              | 72   | V        |

| V <sub>VHIGH_SENSE</sub>         | V <sub>HIGH_SENSE</sub> Voltage Range                                                          | (Note 6)                                                                                                                                         | 0    |              | 72   | V        |

| V <sub>VLOW_SENSE</sub>          | V <sub>LOW_SENSE</sub> Voltage Range                                                           |                                                                                                                                                  | 0    |              | 36   | V        |

| V <sub>VLOW</sub>                | V <sub>LOW</sub> Voltage Range                                                                 | (Note 5)                                                                                                                                         | 0    |              | 36   | V        |

| lα                               | Input DC Supply Current<br>Shutdown<br>Normal Operation                                        | V <sub>RUN</sub> = 0V<br>V <sub>RUN</sub> = 5V, No Switching                                                                                     |      | 60<br>1.5    |      | μA<br>mA |

| V <sub>UVLO</sub>                | Undervoltage Lockout Threshold                                                                 | V <sub>INTVCC</sub> Falling<br>V <sub>INTVCC</sub> Rising                                                                                        |      | 4.85<br>5.05 |      | V<br>V   |

| <b>Overcurrent Prot</b>          | tection                                                                                        |                                                                                                                                                  |      |              |      |          |

| I <sub>ISENSE</sub> <sup>+</sup> | I <sub>SENSE</sub> <sup>+</sup> Pin Current                                                    | $I_{SENSE}^+ = I_{SENSE}^- = 24V$                                                                                                                |      | 220          | 350  | μA       |

|                                  |                                                                                                | $\label{eq:Pre-Balance Phase, V_{HIGH_SENSE} = 24V, \\ I_{SENSE}^{+} = I_{SENSE}^{-} = 24V, \\ V_{VLOW} = 12V, \\ V_{VLOW} = 11V \\ \end{array}$ |      | 93           |      | mA       |

| I <sub>ISENSE</sub> <sup>-</sup> | I <sub>SENSE</sub> <sup>-</sup> Pin Current                                                    |                                                                                                                                                  | -5   | 1            | 5    | μA       |

| VISENSE                          | Current Limit Threshold (V <sub>ISNESE</sub> <sup>+</sup> – V <sub>ISENSE</sub> <sup>-</sup> ) |                                                                                                                                                  | 45   | 50           | 55   | mV       |

| Gate Drivers                     |                                                                                                |                                                                                                                                                  |      |              |      |          |

| R <sub>G2,4</sub>                | Pull-Up On-Resistance<br>Pull-Down On-Resistance                                               |                                                                                                                                                  |      | 2.5<br>1.5   |      | Ω<br>Ω   |

| R <sub>G1,3</sub>                | Pull-Up On-Resistance<br>Pull-Down On-Resistance                                               |                                                                                                                                                  |      | 2.4<br>1.1   |      | Ω<br>Ω   |

| G1/G2 t <sub>D</sub>             | G1 Off to G2 On Delay Time<br>G2 Off to G1 On Delay Time                                       | (Note 4)                                                                                                                                         |      | 50<br>50     |      | ns<br>ns |

| G3/G4 t <sub>D</sub>             | G3 Off to G4 On Delay Time<br>G4 Off to G3 On Delay Time                                       | (Note 4)                                                                                                                                         |      | 60<br>60     |      | ns<br>ns |

| G1/G3 t <sub>D</sub>             | G1 On to G3 On Delay Time<br>G3 Off to G1 Off Delay Time                                       | (Note 4)                                                                                                                                         |      | 5<br>10      |      | ns<br>ns |

| G2/G4 t <sub>D</sub>             | G2 On to G4 On Delay Time<br>G4 Off to G2 Off Delay Time                                       | (Note 4)                                                                                                                                         |      | 5<br>10      |      | ns<br>ns |

| RUN Pin                          |                                                                                                |                                                                                                                                                  |      |              |      |          |

| V <sub>RUN</sub>                 | Run Pin On Threshold                                                                           | V <sub>RUN</sub> Rising                                                                                                                          | 1.1  | 1.22         | 1.35 | V        |

| V <sub>RUN,HYS</sub>             | Run Pin On Hysteresis                                                                          |                                                                                                                                                  |      | 80           |      | mV       |

| INTV <sub>CC</sub> Regulato      | )r                                                                                             |                                                                                                                                                  |      |              | ,    |          |

| VINTVCC_VCC                      | INTV <sub>CC</sub> Voltage No Load                                                             | $6V < V_{CC} < 72V, V_{EXTVCC} = 0V$                                                                                                             | 5.4  | 5.6          | 5.9  | V        |

|                                  | INTV <sub>CC</sub> Load Regulation                                                             | I <sub>CC</sub> = 0 to 60mA, V <sub>EXTVCC</sub> = 0V                                                                                            |      | 0.8          | ±2   | %        |

| V <sub>INTVCC_EXT</sub>          | INTV <sub>CC</sub> Voltage No Load with EXTV <sub>CC</sub>                                     | 12V < V <sub>EXTVCC</sub> < 45V (Note 7)                                                                                                         | 5.4  | 5.6          | 5.9  | V        |

|                                  | INTV <sub>CC</sub> Load Regulation with EXTV <sub>CC</sub>                                     | $I_{CC} = 0$ to 50mA, $V_{EXTVCC} = 12V$                                                                                                         |      | 0.5          | ±2   | %        |

|                                  | EXTV <sub>CC</sub> Switchover Voltage                                                          | V <sub>EXTVCC</sub> Ramping Positive (Note 9)                                                                                                    | 6.35 | 6.5          | 6.65 | V        |

|                                  | EXTV <sub>CC</sub> HYSTERESIS                                                                  |                                                                                                                                                  |      | 400          |      | mV       |

| V <sub>HIGH_SENSE</sub> and      |                                                                                                |                                                                                                                                                  |      |              |      |          |

| R <sub>VHIGH_SENSE</sub>         | V <sub>HIGH_SENSE</sub> to GND Resistance                                                      |                                                                                                                                                  |      | 1            |      | MΩ       |

|                                  | V <sub>LOW SENSE</sub> Pin Current                                                             | $V_{CC} = 51V, V_{LOW SENSE} = 45V$                                                                                                              |      | ±1           |      | 1        |

## ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{CC} = 12V$ ,  $V_{RUN} = 5V$ , unless otherwise specified.

| SYMBOL                        | PARAMETER                                          | CONDITIONS                                                                                                                           |   | MIN          | ТҮР          | MAX          | UNITS  |

|-------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---|--------------|--------------|--------------|--------|

| V <sub>LOW</sub>              |                                                    |                                                                                                                                      |   |              |              |              |        |

| ISOURCEVLOW                   | Source Current to $V_{LOW}$ Pin from $I_{SENSE}^+$ | $I_{SENSE}^+ = V_{HIGH\_SENSE} = 24V,$<br>$V_{LOW\_SENSE} = 11V, V_{LOW} = 12V, Timer = 1V$                                          |   |              | 93           |              | mA     |

| ISINKVLOW                     | Sink Current from $V_{\mbox{LOW}}$ Pin to GND      | $I_{SENSE}^+ = V_{HIGH\_SENSE} = 24V,$<br>$V_{LOW\_SENSE} = 13V, V_{LOW} = 12V, Timer = 1V$                                          |   |              | 50           |              | mA     |

| Oscillator                    |                                                    |                                                                                                                                      |   |              |              |              |        |

| fs                            | Oscillator Frequency Range                         |                                                                                                                                      |   | 100          |              | 1000         | kHz    |

| f <sub>NOM</sub>              | Nominal Frequency                                  | V <sub>FREQ</sub> = 1.02V                                                                                                            |   |              | 500          |              | kHz    |

| I <sub>FREQ</sub>             | FREQ Setting Current                               | V <sub>FREQ</sub> = 1.02V (Note 3)                                                                                                   |   | -9.5         | -10          | -10.5        | μA     |

| FAULTB and HYS_P              | RGM                                                |                                                                                                                                      |   |              |              |              |        |

| RFAULT                        | FAULT Pull-Down Resistance                         | V <sub>FAULT</sub> = 0.5V                                                                                                            |   |              | 200          | 400          | Ω      |

| FAULT_LEAK                    | FAULT Leakage Current                              | V <sub>FAULT</sub> = 80V                                                                                                             |   |              |              | ±2           | μA     |

| I <sub>HYS_PRGM</sub>         | HYS_PRGM Setting Current                           | V <sub>HYS_PRGM</sub> = 1V (Note 3)                                                                                                  | • | -9.3         | -10          | -10.7        | μA     |

| V <sub>VLOW_SENSE_FAULT</sub> | V <sub>LOW_SENSE</sub> Voltage Trigger Fault       | V <sub>VHIGH_SENSE</sub> = 24V, V <sub>HYS_PRGM</sub> = 0V<br>V <sub>VLOW_SENSE</sub> Ramp Up<br>V <sub>VLOW_SENSE</sub> Ramp Down   | • | 12.2<br>11.6 | 12.3<br>11.7 | 12.4<br>11.8 | V<br>V |

|                               |                                                    | V <sub>VHIGH_SENSE</sub> = 24V, V <sub>HYS_PRGM</sub> = 5V<br>V <sub>VLOW_SENSE</sub> Ramp Up<br>V <sub>VLOW_SENSE</sub> Ramp Down   | • | 12.7<br>11.1 | 12.8<br>11.2 | 12.9<br>11.3 | V<br>V |

|                               |                                                    | V <sub>VHIGH_SENSE</sub> = 24V, V <sub>HYS_PRGM</sub> = 2.4V<br>V <sub>VLOW_SENSE</sub> Ramp Up<br>V <sub>VLOW_SENSE</sub> Ramp Down | • | 14.15<br>9.5 | 14.3<br>9.65 | 14.45<br>9.8 | V<br>V |

| UV Comparator and             | I PGOOD                                            |                                                                                                                                      |   |              |              |              |        |

| V <sub>UVTH</sub>             | UV Pin Comparator Threshold                        | UV Pin Voltage Rising                                                                                                                |   | 0.985        | 1.01         | 1.035        | V      |

| V <sub>UVHYS</sub>            | Undervoltage Hysteresis                            |                                                                                                                                      |   |              | 120          |              | mV     |

| R <sub>PGOOD</sub>            | PGOOD Pull-Down Resistance                         | $V_{PGOOD} = 0.5V$                                                                                                                   |   |              | 150          | 300          | Ω      |

| I <sub>PGOOD_LEAK</sub>       | PGOOD Leakage Current                              | V <sub>PG00D</sub> = 45V                                                                                                             |   |              |              | ±1           | μA     |

| Timer                         |                                                    |                                                                                                                                      |   |              |              |              |        |

| ITIMER                        | Timer Pin Current                                  | V <sub>TIMER</sub> < 0.5V or V <sub>TIMER</sub> > 1.2V (Note 3)                                                                      |   |              | -3.5         |              | μA     |

|                               |                                                    | 0.5V < V <sub>TIMER</sub> < 1.2V (Note 3)                                                                                            |   |              | -7           |              | μA     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC7820 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC7820E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC7820I is guaranteed over the -40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$T_J = T_A + (P_D \bullet 43^{\circ}C/W).$

**Note 3:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

**Note 4:** Delay times are measured using 50% levels with SW3 =  $V_{LOW}$  = 6V, SW1 = 12V.

**Note 5:** The maximum output operating voltage for divider applications is 36V, the maximum input operating voltage for doubler applications is 36V. **Note 6:** The maximum input operating voltage for divider applications is 72V, the maximum output operating voltage for doubler applications is 72V. **Note 7:** When  $V_{CC} > 15V$ , EXTV<sub>CC</sub> lower than  $V_{CC}$  is recommended to improve efficiency and reduce IC Temperature.

**Note 8:** All the voltage is referred to the GND pin unless otherwise specified.

**Note 9:** EXTV<sub>CC</sub> is enabled only if  $V_{CC}$  is higher than 7V.

Note 10: Guaranteed by design.

**Note 11:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum junction temperature may impair device reliability or permanently damage the device.

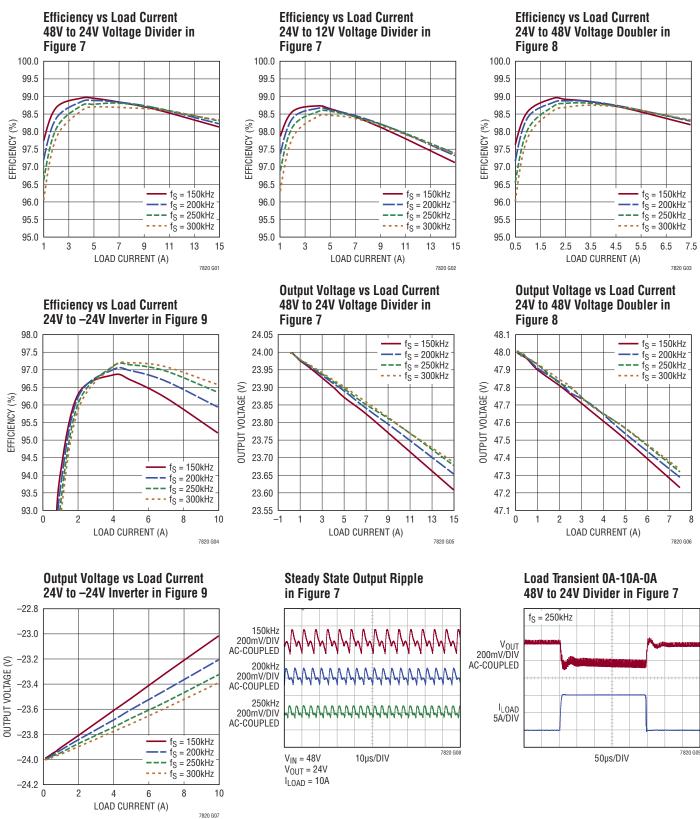

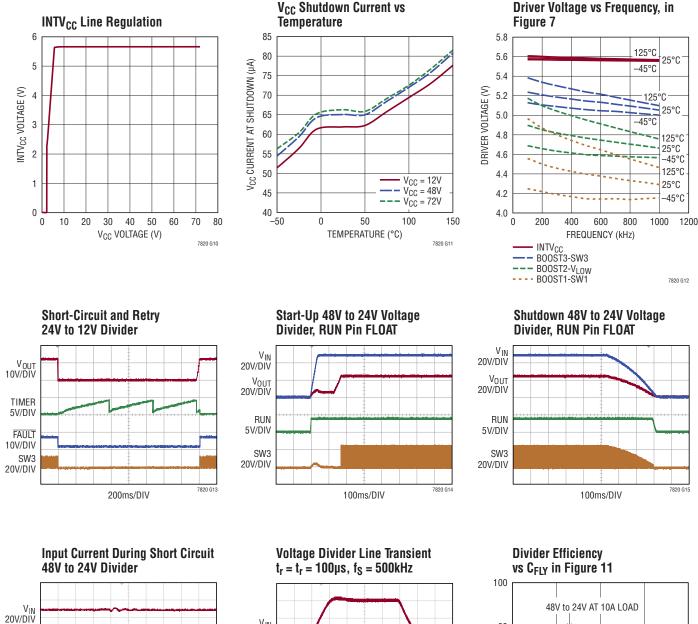

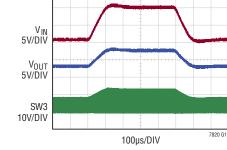

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25$ °C, unless otherwise noted.

7820 G16

5µs/DIV

V<sub>OUT</sub> 20V/DIV

20A/DIV

50V/DIV

IIN

SW3

## PIN FUNCTIONS

**UV (Pin 8):** Undervoltage Comparator Input. If the UV pin voltage is lower than 0.9V, the PGOOD pin is pulled down while the controller keeps switching. If the UV pin voltage is higher than 1V and no faults exist, PGOOD pin is released. Connect to  $INTV_{CC}$  if not used.

**I**<sub>SENSE</sub><sup>+</sup> (Pin 27): Current Sense Comparator Positive Input. Kelvin connected to the positive node of the current sensing resistor. The current sensing resistor has to be connected to the drain of the very top MOSFET. When the voltage between  $I_{SENSE}^+$  pin and  $I_{SENSE}^-$  pin is higher than 50mV, the controller indicates an overcurrent fault by pulling the FAULT pin down. The  $I_{SENSE}^+$  pin is also used to source 93mA current to the  $V_{LOW}$  pin during the capacitor's pre-balancing time at power-up in voltage divider applications. Connect directly to the drain of the very top MOSFET if not used.

$I_{SENSE}^-$  (Pin 28): Current Sense Comparator Negative Input. Kelvin connected to the negative node of the current sensing resistor. Short to  $I_{SENSE}^+$  if not used.

**RUN (Pin 6):** Run Control Input. Forcing RUN below 1.14V shuts down the controller. When RUN is higher than 1.22V, internal circuitry starts up. There is a  $1\mu$ A pull-up current flowing out of RUN pin when the RUN pin voltage is below 1.14V and additional  $5\mu$ A current flowing out of RUN pin when the Run pin voltage is above 1.22V.

**TIMER (Pin 4):** Charge Balance and Fault Timer Control Input. A capacitor between this pin and ground sets the amount of time to charge  $V_{LOW}$  to  $V_{HIGH\_SENSE}/2$  voltage during power-up. It also sets the short-circuit retry time. See the Application Information section for details.

**FAULT (Pin 9):** Open Drain Output Pin. FAULT is pulled to ground when the  $V_{LOW\_SENSE}$  voltage is out of its window thresholds or the voltage between  $I_{SENSE}^+$  and  $I_{SENSE}^-$  is higher than 50mV. FAULT pin is also pulled to ground under INTV<sub>CC</sub> UVLO.

**PGOOD (Pin 7):** Open Drain Output Pin. PGOOD is pulled to ground if there are any faults or if the UV pin indicates an undervoltage condition.

**HYS\_PRGM (Pin 3):** A resistor connected between this pin and ground will program the two thresholds of the window comparator that monitors the voltage difference between  $V_{HIGH\_SENSE}/2$  and  $V_{LOW\_SENSE}$ . There is a 10µA current flowing out of this pin.

**G4 (Pin 15):** High Current Gate Drive for the Bottom (Synchronous) N-Channel MOSFET. Voltage swing at this pin is from ground to  $INTV_{CC}$ .

**G3 (Pin 17):** High Current Gate Drive for the Third Upper Most N-Channel MOSFET. This is the output of the floating driver with a voltage swing from BOOST3 to SW3.

**G2 (Pin 21):** High Current Gate Drive for the Second Upper most N-Channel MOSFET. This is the output of the floating driver with a voltage swing from BOOST2 to  $V_{LOW}$ .

**G1 (Pin 24):** High Current Gate Drive for the Upper most N-Channel MOSFET. This is the output of the floating driver with a voltage swing from BOOST1 to SW1.

SW1/SW3 (Pin 25/Pin 16): Switch Node Connections.

**BOOST1, BOOST2, BOOST3 (Pins 23, 22, 18):** Bootstrapped supplies to the floating drivers. Capacitors are connected between these BOOST pins and their respective SWn and  $V_{LOW}$  pins.

**EXTV<sub>CC</sub> (Pin 11):** External Power Input to  $EXTV_{CC}$  LDO. This LDO supplies INTV<sub>CC</sub> power whenever  $EXTV_{CC}$  is higher than 6.5V and V<sub>CC</sub> is higher than 7V. Do not exceed 40V on this pin.

**INTV<sub>CC</sub> (Pin 12):** Output of the Internal Linear Low Dropout Regulator. The driver and control circuits are powered from this voltage source. Must be bypassed to power ground with a minimum of  $4.7\mu$ F ceramic or other low ESR capacitor.

$V_{CC}$  (Pin 14): Power Supply for Internal Circuitry and  $\mathsf{INTV}_{\mathsf{CC}}$  Linear Regulator. A bypass capacitor should be tied between this pin and the power ground.

**V<sub>HIGH\_SENSE</sub> (Pin 1):** Kelvin Sensing Input. Monitor the voltage of the drain of the top MOSFET.

## PIN FUNCTIONS

$V_{LOW}$  (Pin 20): Half Supply from  $V_{HIGH\_SENSE}$ . Connect a bypass capacitor from this node to PGND.

$V_{LOW\_SENSE}$  (Pin 19): Kelvin Sensing Input. Monitors the voltage on  $V_{LOW}.$

**FREQ (Pin 5):** Frequency Set Pin. There is a precision  $10\mu$ A current flowing out of this pin. A resistor to ground sets a voltage which in turn programs the frequency. See the Applications Information section for detailed information.

**NC (Pins 2, 10, 13, 26):** No Connection. Always keep these pins floating. These pins are intentionally skipped to isolate adjacent high voltage pins.

**GND (Exposed Pad Pin 29):** Signal and Power Ground. All small-signal components should connect to this ground, which in turn connects to system power ground at one point. The exposed pad must be soldered to the PCB, providing a local ground for the control components of the IC, which should be tied to system power ground under the IC. For inverter applications, GND should connect to the negative output and all small signal components still referred to GND pin.

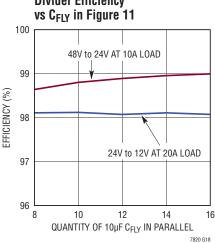

## **BLOCK DIAGRAM**

7820fc

9

## OPERATION

### **Main Control**

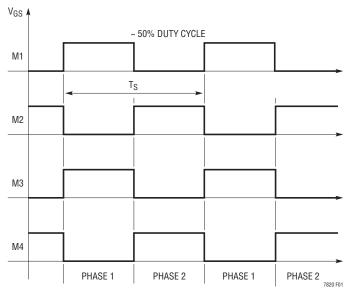

The LTC7820 is a constant frequency, open loop switched capacitor/charge pump controller for high power and high voltage applications. Please refer to the Block Diagram for the following discussion on its operation. In steady state operation, the N-channel MOSFETs M1 and M3 are turned on and off in the same phase with around 50% duty cycle at a pre-programmed switching frequency. The N-channel MOSFETs M2 and M4 are turned on and off complementarily to MOSFETs M1 and M3. The gate drive waveforms are shown in Figure 1.

Figure 1. Gate Drive Waveforms

During phase 1, M1 and M3 are on and the flying capacitor  $C_{FLY}$  is in series with  $C_{VLOW}$ . During phase 2, M2 and M4 are on and  $C_{FLY}$  is in parallel with  $C_{VLOW}$ . The  $V_{LOW}$  pin voltage is always close to half of the top voltage at the drain of MOSFET M1 (refer to GND pin) in steady state, and it is not sensitive to variable loads due to the very low impedance at its output. The LTC7820 does not regulate the output voltage with a closed-loop feedback system. However, it stops switching when fault conditions occur, such as  $V_{LOW}$  pin voltage overvoltage or undervoltage, an overcurrent event or an overtemperature protection event.

### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for the quad N-channel MOSFET drivers and most other internal circuitry is derived from the  $INTV_{CC}$  pin. Normally an internal 5.5V linear regulator supplies  $INTV_{CC}$  power from  $V_{CC}$ . If  $V_{CC}$  is connected to a high input voltage, an optional external voltage source on the EXTV<sub>CC</sub> pin enables a second 5.5V linear regulator and supplies  $INTV_{CC}$  power from the EXTV<sub>CC</sub> pin. To enable this more efficient second regulator,  $V_{CC}$  needs to be higher than 7V and the EXTV<sub>CC</sub> pin voltage has to be higher than 6.5V. Do not exceed 40V on the EXTV<sub>CC</sub> pin. Each top MOSFET driver is biased from the floating bootstrap capacitors  $C_B$ , which are normally recharged during each off cycle through an external Schottky diode when the respective top MOSFET turns off.

### Start-Up and Shutdown

The LTC7820 is in shutdown mode when the RUN pin is lower than 1.14V. In this mode, most internal circuitry is turned off including the INTV<sub>CC</sub> regulator and the LTC7820 consumes less than 100 $\mu$ A current. All gates G1/G2/G3/ G4 are actively pulled low to turn off the external power MOSFETs in shutdown. Releasing RUN allows an internal 1 $\mu$ A current to pull up this pin and enable the controller. Once the run pin rises above 1.22V, an additional 5 $\mu$ A flows out of this pin. Alternately, the RUN pin may be externally pulled up or driven directly by logic. Do not exceed the Absolute Maximum Rating of 6V on this pin.

After the Run pin is released and the INTV<sub>CC</sub> voltage passes UVLO, the LTC7820 starts up and monitors the V<sub>HIGH\_SENSE</sub> and V<sub>LOW\_SENSE</sub> voltages continuously. The LTC7820 starts switching only if V<sub>LOW\_SENSE</sub> voltage is close to half of V<sub>HIGH\_SENSE</sub> voltage or both V<sub>LOW\_SENSE</sub> and V<sub>HIGH\_SENSE</sub> voltages are close to GND. In voltage divider applications, V<sub>LOW</sub> is pre-balanced to half the V<sub>HIGH\_SENSE</sub> voltage and the LTC7820 may start up with capacitors at different initial conditions.

### Fault Protection and Thermal Shutdown

The LTC7820 monitors system voltage, current and temperature for faults. It stops switching and pulls down the FAULT pin when fault conditions occur. To clear voltage faults, the  $V_{LOW\_SENSE}$  pin voltage has to be within the

## OPERATION

programmed window around half of V<sub>HIGH\_SENSE</sub> voltage or the V<sub>HIGH\_SENSE</sub> and V<sub>LOW\_SENSE</sub> voltages must be lower than 1V and 0.5V respectively. To clear the current fault, the voltage drop from  $I_{SENSE}^+$  pin to  $I_{SENSE}^-$  pin has to be lower than 50mV. To clear temperature faults, the IC temperature has to be lower than 165°C.

The FAULT pin may be pulled up by external resistors to voltages up to 80V. It can be used to control an external disconnect FET to isolate the input and output during fault conditions.

### High Side Current Sensing

For over current protection, the LTC7820 uses a sense resistor R<sub>SENSE</sub> to monitor the current. The sensing resistor has to be placed at the drain of the very top MOSFET M1. For voltage divider and inverter applications, the current flows into the drain of the MOSFET M1, so the I<sub>SENSE</sub><sup>+</sup> pin should be connected to the sensing resistor then to the drain of the MOSFET M1. For voltage doubler applications, the current flows out of the drain of the MOSFET M1, so the I<sub>SENSE</sub><sup>+</sup> pin should be connected directly to the drain of the MOSFET M1. See Typical Applications section for examples. In most applications, the current through the sense resistor is a pulse current and the peak value is much higher than the average load current. A RC filter on the I<sub>SENSE</sub> pin, with a time constant lower than the switching frequency, may be used to set the precision average current protection. If overcurrent protection is not desired, short the I<sub>SENSE</sub><sup>+</sup> and I<sub>SENSE</sub><sup>-</sup> pins together and connect them to the drain of the top MOSFET M1 directly.

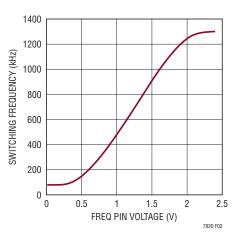

### **Frequency Selection**

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger capacitance to maintain low output ripple voltage and low output impedance. The FREQ pin can be used to program the controller's operating frequency from 100kHz to 1MHz. There is a precision 10µA current flowing out of the FREQ pin, so the user can program the controller's switching frequency with a single resistor to GND. The voltage on the FREQ pin is equal to the resistance multiplied by 10µA current (e.g. the voltage is 1V with a 100k resistor from the FREQ pin to GND). In the linear region, the switching frequency,  $f_S$ , can be estimated based on the equation:

$f_{S} (kHz) = R_{FREQ}(k\Omega) \bullet 8 - 317 kHz$

Figure 2 also shows the relationship between the voltage on the FREQ pin and switching frequency.

Figure 2. Relationship Between Switching Frequency and Voltage at the FREQ Pin

### Power Good and UV (PGOOD and UV pins)

When the UV pin voltage is lower than 1V, the PGOOD pin is pulled low. The PGOOD pin is also pulled low when the RUN pin is low or when the LTC7820 is starting up. The PGOOD pin is released only when the LTC7820 is switching and UV pin is higher than 1V. The PGOOD pin will flag power bad immediately when the UV pin is low. However, there is an internal 20µs power good mask and 120mV hysteresis when UV goes higher than 1V. The PGOOD pin may be pulled up by external resistors to sources up to 45V.

PGOOD signal can be used to enable or disable the output loads. If the loads are switching mode converters or LDOs with ENABLE/RUN pins, this allows easy for interfacing. With proper setup on the UV pin, PGOOD can enable the loads at the output when the output voltage is above a certain value. PGOOD can also be used to control the RUN pin of another LTC7820 if two or more parts are cascaded to achieve higher step-down ratios.

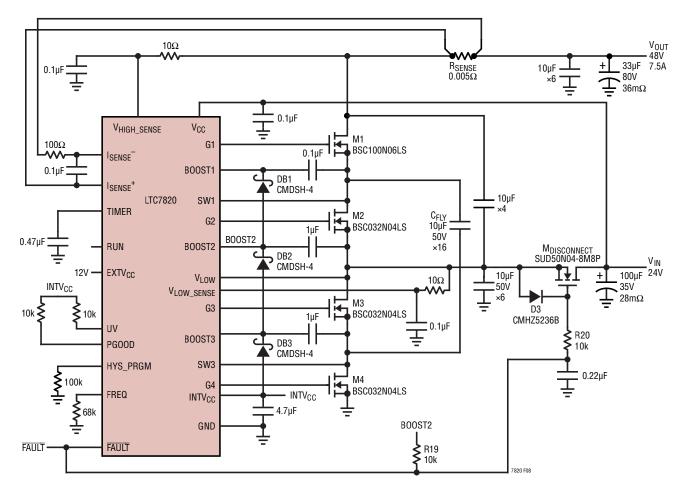

The Typical Application on the first page of this data sheet is a LTC7820 voltage divider circuit. For voltage divider applications, the input voltage is at the drain of very top MOSFET M1 and the output voltage is at the  $V_{I,OW}$  pin, which is connected to the source of MOSFET M2 and the drain of MOSFET M3. The output voltage is around half of the input voltage in steady state. Alternately, by swapping the input and output voltages, the voltage divider circuit can be transformed into a voltage doubler circuit. For voltage doubler applications, the input voltage is at the V<sub>LOW</sub> pin while output voltage is available at the drain of the top MOSFET M1 and equals two times the input voltage as shown in Figure 8. Similarly, for inverter applications, the input voltage is applied between the drain of the top MOSFET M1 and  $V_{IOW}$ , and the output voltage equals the negative input voltage at the GND pin with respect to the V<sub>LOW</sub> pin as shown in Figure 9. For divider applications, if the load current is applied before startup or heavy resistive loads are connected to the VLOW pin, the LTC7820 may not start up due to the limited drive ability of the pre-balance circuit. A disconnect FET may be used at the output for soft-start up. For doubler and inverter applications, a disconnect FET may also be required for soft start-up and shutdown. The disconnect FETs in divider/ doubler/inverter applications may be also controlled by hot swap controllers to achieve more programmable slew rates and fault protections.

### Voltage Divider Pre-Balance before Switching

In voltage divider applications, the V<sub>LOW\_SENSE</sub> voltage should be always close to V<sub>HIGH\_SENSE</sub>/2 in steady state. The voltages across the flying capacitors and V<sub>LOW</sub> capacitors are close to each other and close to half of the input voltage. The charging inrush current is minimized during each switching cycle because the voltage difference between capacitors is small. However, without special methods such as the LTC7820 pre-charging circuitry, during start-up or fault conditions such as V<sub>LOW</sub> short to GND, the difference between capacitors can be large and charging currents may be great enough to cause permanent MOSFET damage.

When the power MOSFETs are on, ideally, the inrush charge current,

$$I = \frac{V_{IN} - V_{CFLY} - V_{LOW}}{R_{ON} - M1} + R_{ON} - M3}$$

when switches M1 and M3 are on and:

$$I = \frac{V_{CFLY} - V_{LOW}}{R_{ON M2} + R_{ON M4}}$$

when switches M2 and M4 are on. Both currents are limited by the power MOSFET saturation current. With very low  $R_{DS(ON)}$  of the external power MOSFETs, the inrush charge current could easily achieve several hundreds of Amperes which can be higher than the MOSFET's Safe Operating Area (SOA).

The LTC7820 provides a proprietary pre-balance method to minimize the inrush charging current in voltage divider applications. The LTC7820 controller detects the  $V_{LOW\_SENSE}$  pin voltage before switching and compares it with the  $V_{HIGH\_SENSE}/2$  internally. If the  $V_{LOW\_SENSE}$  pin voltage is much lower than the  $V_{HIGH\_SENSE}/2$ , a current source will source 93mA current to the  $V_{LOW}$  pin to pull the  $V_{LOW}$  pin up. If the  $V_{LOW\_SENSE}$  pin voltage is much higher than the  $V_{HIGH\_SENSE}/2$ , another current source will sink 50mA from  $V_{LOW}$  pin to pull the  $V_{LOW}$  pin down. If the  $V_{LOW\_SENSE}$  pin voltage is close to  $V_{HIGH\_SENSE}/2$  and within the pre-programmed window, both current sources are disabled and LTC7820 starts switching. If the  $V_{LOW\_SENSE}$  voltage is still within the window after 36 switching cycles, the FAULT pin is released.

For voltage divider with pre-balance startup, the LTC7820 assumes *no load* current or a very small load current (less than 50mA) at the V<sub>LOW</sub> (output) otherwise the V<sub>LOW</sub> voltage cannot reach V<sub>HIGH\_SENSE</sub>/2 and the LTC7820 never starts up. This no load condition can be achieved by connecting the FAULT pin to the enable pins of the following electrical loads such as switching regulators and LDOs. If load current cannot be controlled off such as resistive loads, a disconnect FET is required to disconnect the load during startup as shown in the typical applications.

If the LTC7820 divider input voltage is controlled by a front end supply or hot swap controller and ramps up slowly, the LTC7820 capacitor voltages are naturally balanced. In this case the pre-balance and no load start-up requirements are not necessary.

### Voltage Doubler and Inverter Startup and Disconnect

In voltage doubler and inverter applications, LTC7820 can startup without capacitor inrush charging current if the input voltage is ramping slowly up from zero. As long as the input voltage ramps up slow (in milliseconds), the output voltage can track the input voltage and the voltage difference between capacitors are always small resulting in no huge inrush currents. The slew rate control of the input voltage can be achieved by using a disconnect FET at input or using hot swap controllers as shown in the typical application section. Different from voltage dividers, the voltage doubler and inverter applications have to start up from zero input voltage every time, but they can start up with heavy load currents directly.

Note that voltage divider applications can also startup with a slow ramping input voltage from zero to the steady state operation if there is a hot swap in front of the LTC7820, (pre-balance is not required).

### **Overcurrent Protection**

The LTC7820 provides overcurrent protection through a sensing resistor placed on the high voltage side. A precision rail to rail comparator monitors the differential voltage between the  $I_{SENSE}^+$  pin and the  $I_{SENSE}^-$  pin which are Kelvin connected to a sensing resistor. Whenever the  $I_{SENSE}^+$  pin voltage is 50mV higher than the  $I_{SENSE}^-$  pin voltage, an over current fault is triggered and the FAULT pin is pulled down to ground. At the same time the LTC7820 stops switching and starts retry mode based on the timer pin setup. The overcurrent fault will be cleared when the timer pin voltage reaches 4V and the voltage across the sensing resistor is less than 50mV. The current through the sensing resistor is a pulse current during charging/ discharging of the flying capacitors, which may result a voltage higher than the 50mV threshold at heavy loads. To prevent the inrush current from falsely triggering the overcurrent protection, an RC filter is required at the I<sub>SENSE</sub><sup>+</sup> pin and I<sub>SENSE</sub><sup>-</sup>. The RC filter timer constant has to be larger than a switching period. Typically a  $100\Omega$  and 0.1µF filter is good for most of applications. Due to the current flowing into the I<sub>SENSE</sub><sup>+</sup> pin, the resistor of the RC filter has to be placed at the ISENSE<sup>-</sup> pin. ISENSE<sup>+</sup> pin needs to be connected to the sensing resistor directly. The current limit can be selected by choosing different sense resistor values. For example, the  $10m\Omega$  sense resistor sets current limit at  $50 \text{mV}/10 \text{m}\Omega = 5 \text{A}$  ideally. Due to the switching ripple, the actual current limit is always lower than the ideal case. In real circuits, the current limit is around 4.2A with  $0.1\mu$ F/100 $\Omega$  filter and 200kHz switching frequency. The LTspice<sup>®</sup> simulation tool can be used to quantify the switching ripple.

The overcurrent protection can also be used in doubler and inverter applications for overcurrent and short-circuit conditions at both startup and steady state operation. If over current protection is not used, short the  $I_{SENSE}^+$  pin and the  $I_{SENSE}^-$  pin together and connect them to the drain of the top MOSFET M1.

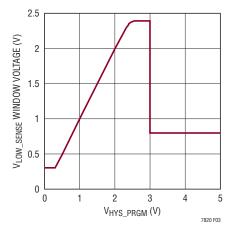

### Window Comparator Programming

In normal operation,  $V_{LOW\_SENSE}$  voltage should be always close to half of the  $V_{HIGH\_SENSE}$  voltage. A floating window comparator monitors the voltage on the  $V_{LOW\_SENSE}$  pin and compares it with  $V_{HIGH\_SENSE}/2$ . The hysteresis window voltage can be programmed and is equal to the voltage at the HYS\_PRGM pin. There is a precision 10µA current flowing out of HYS\_PRGM pin. A single resistor from HYS\_PRGM pin to GND sets the HYS\_PRGM pin voltage, which equals the resistor value multiplied by 10µA current (e.g. the voltage is 1V with a 100k resistor from the HYS\_PRGM pin, the V<sub>HIGH\\_SENSE</sub>/2 voltage has to be within a ( $V_{LOW\_SENSE} \pm 1V$ ) window during startup and normal operation, otherwise a fault is triggered and the LTC7820 stops switching.

The hysteresis window voltage can be linearly programmed from 0.3V to 2.4V as shown in Figure 3 with different resistor values on the HYS\_PRGM pin. If the HYS\_PRGM pin is tied to INTV<sub>CC</sub>, a default 0.8V hysteresis window is applied internally. The hysteresis window voltage has to be programmed large enough to tolerate the V<sub>LOW</sub> pin voltage ripple and voltage drop at maximum load conditions.

Figure 3. Relationship Between HYS\_PRGM Pin Voltage and  $V_{LOW\ SENSE}$  Window Comparator Voltage

During an input line transient, as long as the change of the input voltage in each switching cycle is less than the window hysteresis voltage, LTC7820 keeps switching and the output voltage tracks the input voltage cycle by cycle. If the input voltage step is large enough to force  $V_{LOW\_SENSE}$  out of the window within one switching period, a fault is triggered. The LTC7820 stops switching and starts its retry sequence based on the TIMER pin setup.

To make the window comparator work precisely,  $V_{HIGH\_SENSE}$  and  $V_{LOW\_SENSE}$  pins are provided for Kelvin connection to the capacitor at the drain of the top MOSFET M1 and the capacitors from  $V_{LOW}$  to GND respectively. Small RC filters may be used on these two pins to reject noise higher than the switching frequency.

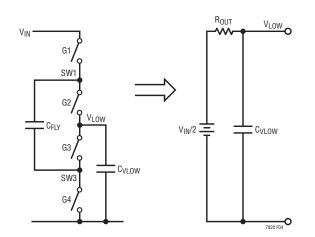

Figure 4. Thevenin Equivalent Circuit of Voltage Divider

# Effective Open Loop Output Resistance and Load Regulation

The LTC7820 does not regulate the output voltage through a closed loop feedback system. However, the output voltage is not sensitive to load conditions due to the low output resistance when it is operating with large flying capacitors and high switching frequency. The Thevenin equivalent circuit of voltage divider circuit is shown in the Figure 4.

When duty cycle is around 50%,

$$R_{OUT} = \frac{1 + e^{-\frac{1}{4f_{S}R_{DS}(ON)^{C}FLY}}}{4f_{S}C_{FLY}\left(1 - e^{-\frac{1}{4f_{S}R_{DS}(ON)^{C}FLY}}\right)}$$

where:

f<sub>S</sub> is the switching frequency

C<sub>FLY</sub> is the flying capacitor

R<sub>DS(ON)</sub> is the on resistance of one MOSFET (G1 to G4)

At low switching frequencies,  $R_{OUT} = 1/(4f_SC_{FLY})$ . As frequency increases,  $R_{OUT}$  finally approaches  $2R_{DS(ON)}$ . In high power applications, it is suggested to select the switching frequency around  $1/(16C_{FLY}R_{DS(ON)})$  or higher for decent load regulation and efficiency. At heavy load conditions, the output voltage will drop from  $V_{IN}/2$  by  $R_{OUT} \cdot I_{LOAD}$ . In many applications, multi-layer ceramic capacitors (MLCC) are selected as flying capacitors. The voltage coefficients of MLCC capacitors strongly depend on the type and size of capacitors. Normally larger size X7R MLCC capacitors are better than X5R in terms of voltage coefficient. The capacitance still drops 20% to 30% with high DC bias voltage. Capacitance derating needs to be considered when estimating the output resistance of these switched capacitor circuits.

### INTV<sub>CC</sub> Regulators and $EXTV_{CC}$

The LTC7820 features an internal PMOS LDO that supplies power to INTV<sub>CC</sub> from the V<sub>CC</sub> supply. INTV<sub>CC</sub> powers the gate drivers and most of the LTC7820's internal circuitry. The linear regulator regulates the voltage at the INTV<sub>CC</sub> pin to 5.5V when V<sub>CC</sub> is greater than 6V. EXTV<sub>CC</sub> connects to INTV<sub>CC</sub> through another PMOS LDO and can supply the needed power when its voltage is higher than 6.5V and V<sub>CC</sub> is higher than 7V. Each of these can supply a peak current of 150mA and must be bypassed to ground with a minimum of 4.7µF ceramic capacitor or low ESR electrolytic capacitor. No matter what type of bulk capacitor is used, an additional 0.1µF ceramic capacitor placed directly adjacent to the INTV<sub>CC</sub> and GND pins is highly recommended. Good bypassing is needed to supply the high transient currents required by the MOSFET gate drivers.

High input voltage applications in which large MOSFETs are being driven at high frequencies may cause the maximum junction temperature rating for the LTC7820 to be exceeded. The INTV<sub>CC</sub> current, which is dominated by the gate charge current, may be supplied by either the 5.5V linear regulator from V<sub>CC</sub> or the linear regulator from EXTV<sub>CC</sub>. When the voltage on the EXTV<sub>CC</sub> pin is less than 6.5V, the linear regulator from V<sub>CC</sub> is enabled. Power dissipation for the IC in this case is highest and is equal to V<sub>CC</sub> • I<sub>INTVCC</sub>. The gate charge current is dependent on operating frequency. The junction temperature can be estimated by using the equations given in Note 2 of the Electrical Characteristics.

For example, the LTC7820  $\rm INTV_{CC}$  current is limited to less than 27mA from a 48V supply in the UFD package and not using the EXTV\_{CC} supply:

$T_J = 70^{\circ}C + (27mA)(48V)(43^{\circ}C/W) = 125^{\circ}C$

Where ambient temperature is 70°C and thermal resistance from junction to ambient is 43°C/W

To prevent the maximum junction temperature from being exceeded, the input supply current must be checked while operating at maximum  $V_{IN}$ . When the voltage applied to EXTV<sub>CC</sub> rises above 6.5V and  $V_{CC}$  above 7V, the INTV<sub>CC</sub> linear regulator is turned off and the EXTV<sub>CC</sub> linear regulator is turned on. Using the EXTV<sub>CC</sub> allows the MOSFET driver and control power to be derived from other high efficiency sources such as the  $V_{LOW}$  pin of a 48V to 24V voltage divider or other voltage rails in the system. Using EXTV<sub>CC</sub> can significantly reduce the IC temperature in high  $V_{IN}$  applications. Tying EXTV<sub>CC</sub> to the output (24V) reduces the junction temperature in the previous example to:

$T_J = 70^{\circ}C + (27mA) (24V) (43^{\circ}C/W)$ = 98°C

Do not apply more than 40V to the  $\mathsf{EXTV}_{\mathsf{CC}}$  pin.

### Topside MOSFET Driver Supply (C<sub>B</sub>, D<sub>B</sub>)

External bootstrap capacitors  $C_{B1}/C_{B2}/C_{B3}$  in the Block Diagram, connected to the BOOST pins, supply the gate drive voltages for the top side MOSFETs M1/M2/M3. Capacitor  $C_{B3}$  in the Block Diagram is charged though external Schottky diode  $D_{B3}$  from INTV<sub>CC</sub> when the SW3 pin is low. Capacitor  $C_{B2}$  is charged through  $D_{B2}$  from BOOST3 when the SW3 pin is high. Capacitor  $C_{B1}$  is charged through  $D_{B1}$  from BOOST2 when the SW1 pin is low. When the MOSFETs M1/M2/M3 are to be turned on, the driver places the  $C_{B1}/C_{B2}/C_{B3}$  voltage across the gate source of the MOSFETs M1/M2/M3. This enhances the MOSFETs and turns them on. The switch node voltage, SW1/SW3, rises to  $I_{SENSE}^+/V_{LOW}$  and the BOOST pin follows. With continuous switching, the gate driver voltages on  $C_{B1}/C_{B2}/C_{B3}$  are:

$$V_{CB3} = V_{INTVCC} - V_{DB3}$$

$$V_{CB2} = V_{INTVCC} - V_{DB3} - V_{DB2}$$

$$V_{CB1} = V_{INTVCC} - V_{DB3} - V_{DB2} - V_{DB1}$$

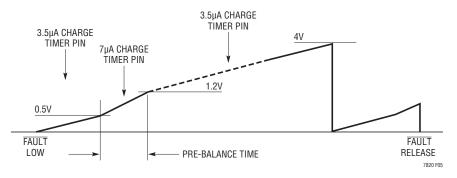

Figure 5. Timer Behavior During Fault or Startup

The value of the boost capacitors,  $C_{B1}/C_{B2}/C_{B3}$ , needs to be 100 times that of the total input capacitance of the topside MOSFET(s). The standard 6.3V MLCC ceramic capacitors are good for  $C_{B1}/C_{B2}/C_{B3}$ . The reverse breakdown of the external Schottky diodes must be greater than the maximum operation voltage between the V<sub>LOW</sub> and GND pins. When adjusting the gate drive level, the final arbiter is the threshold voltage of the top MOSFET M1. The Top driver voltage V<sub>CB1</sub> has to be higher than the top FET M1 threshold voltage in all conditions. Logic level MOSFET should be used, otherwise lower operating switching frequency and lower forward voltage drop diodes are necessary to raise the gate driver voltages.

### **Undervoltage Lockout**

The LTC7820 has a precision UVLO comparator constantly monitoring the INTV<sub>CC</sub> voltage to ensure that an adequate gate-drive voltage is present. It locks out the switching action when INTV<sub>CC</sub> is below 4.9V. To prevent oscillation when there is a disturbance on INTV<sub>CC</sub>, the UVLO comparator has 200mV of precision hysteresis.

Another way to detect an undervoltage condition is to monitor the input supply. Because the RUN pin has a precision turn-on reference of 1.22V, one can use a resistor divider to the input to turn on the IC when the input voltage is high enough. An extra  $5\mu$ A of current flows out of the RUN pin once the RUN pin voltage passes 1.22V. One can program the hysteresis of the RUN comparator by adjusting the values of the resistive divider.

### Fault Response and Timer Programming

The LTC7820 stops switching and pulls the FAULT pin low during fault conditions. A capacitor connected from the TIMER pin to GND sets the retry time to start-up if fault conditions are removed. A typical waveform on the TIMER pin during a fault condition is shown in Figure 5.

After the FAULT pin is pulled low, a  $3.5\mu$ A pull-up current flows out of TIMER pin and starts to charge the Timer capacitor. The pull-up current increases to  $7\mu$ A when the TIMER pin voltage is higher than 0.5V and back to  $3.5\mu$ A when the TIMER pin voltage is higher than 1.2V. The TIMER pin will be strongly pulled down whenever the fault conditions are removed or the TIMER pin voltage is higher than 4V. When the TIMER pin voltage is between 0.5V and 1.2V, the internal pre-balance circuit will source or sink current to the V<sub>LOW</sub> pin and regulate the V<sub>LOW</sub> pin to V<sub>HIGH\_SENSE</sub>/2 with around 93mA/50mA capability. The pre-balance time can be calculated based on the capacitor C<sub>TIMER</sub> on the TIMER pin:

$T_{PRE-BALANCE} = C_{TIMER} \bullet 0.7 V/7 \mu A$

So the pre-balance time is 100ms/µF (e.g. the pre-balance time is 10ms with 0.1µF  $C_{TIMER}).$

For voltage divider applications, the output capacitors and the flying capacitors are pre-balanced to half of the input voltage during the startup. Assuming zero initial conditions, the time to charge the capacitors,  $t_{CHARGE}$ , can be estimated from the equation:

$$t_{CHARGE} = (C_{OUT} + C_{FLY}) \cdot V_{IN}/2/93mA$$

Select the C<sub>TIMER</sub> such that the t<sub>CHARGE</sub> < t<sub>PRE-BALANCE</sub>. If the flying capacitor C<sub>FLY</sub> and the output capacitor are very large and input voltage is high, it may take several pre-balance time periods to pre-balance the V<sub>LOW</sub> pin to V<sub>HIGH\_SENSE</sub>/2 with a fixed C<sub>TIMER</sub>. A longer start-up time is expected. If there is a resistive load on the output, the load current needs to be smaller than 93mA and still meet t<sub>CHARGE</sub> = (C<sub>OUT</sub> + C<sub>FLY</sub>) • V<sub>IN</sub>/2/(93mA - I<sub>LOAD</sub>) < t<sub>PRE-BALANCE</sub>. Otherwise a disconnect FET may be required to disconnect the load during startup.

### Input/Output Capacitor and Flying Capacitor Selection

In high power switched capacitor applications, large AC currents flow through the flying capacitors and input/ output capacitors. Low ESR ceramic capacitors are highly recommended for high power switch capacitor applications. Make sure the maximum RMS capacitor current is within the spec; or higher RMS current rated capacitors are preferred. Note that capacitor manufacturers' ripple current ratings are often based on only 2000 hours of life. This makes it advisable to further derate the capacitor, or to choose capacitors rated at a higher temperature than required. Several capacitors may be paralleled to meet size or height requirements in the design.

The RMS current on the flying capacitors depends on their capacitance and the switching frequency. Higher capacitance and higher switching frequency results in lower RMS current. For a good trade-off between efficiency and power density, the RMS current on the flying capacitors should be lower than 140% of the maximum load current. If there are N identical flying capacitors in parallel, the maximum RMS current through each capacitor is:

$I_{RMS\_CFLY} = I_{OUT(MAX)} \bullet 140\%/N$

The input capacitor RMS current is approximately half of the load current. The input capacitor has to be selected to accommodate the maximum load conditions. LTspice simulation tool can be used to quantify the RMS current.

### Power MOSFETs and Schottky Diodes Selection

Four external N-channel MOSFETs must be selected for each LTC7820 controller. Four internal gate drivers are designed to drive the MOSFETs. The driver voltages are decided by the INTV<sub>CC</sub> voltage, schottky diodes forward voltage drop and switching frequency. The lowest driver voltage is the top MOSFET M1 drive voltage running at high switching frequency and cold temperature. It is normally around 4.2V. Consequently, logic-level threshold MOSFETs must be used in most applications. Be aware that the threshold voltage of some logic-level MOSFET varies with temperature. If switching frequency is high and temperature range is wide for specific applications. the top driver voltage of MOSFET M1 may be as low as 4V, and sub-logic level threshold MOSFETs ( $V_{GS(TH)} < 3V$ ) should be used. Selection criteria for the power MOSFETs also include the on-resistance R<sub>DS(ON)</sub>, output capacitance C<sub>OSS</sub>, input voltage, and maximum output current. Generally, low R<sub>DS(ON)</sub> and low C<sub>OSS</sub> MOSFETs are preferred in switched capacitor applications since they will minimize both conduction loss and switching loss. For a given input and output voltage, the uppermost MOSFET M1 always sees high voltage during start-up and shutdown. The Drain to Source voltage of M1 has to be high enough to survive at full input voltage range. Other MOSFETs normally only see half of the input voltage, so the breakdown voltage of M2/M3/M4 can be lower than M1 to optimize  $R_{DS(ON)}$ and  $C_{OSS}$ . If the reliability of M1 is a major concern, the same high voltage MOSFETs could also be used as M2/ M3/M4 to protect against M1 short conditions.

External schottky diodes are needed for the bootstrap circuits, and provide voltage for the floating drivers. To minimize the voltage drop on the top gate driver, low forward voltage drop schottky diodes are preferred with load current in the range of 10mA to 50mA. The reverse breakdown voltage of the diodes should be high enough to survive at the maximum operation voltage between the  $V_{LOW}$  and GND pins.

### PC Board Layout Checklist

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the IC.

- 1. Are the top 2 N-channel MOSFETs M1 and M2 located within 1cm of each other? Are the bottom 2 N-channel MOSFETs M3 and M4 located within 1cm of each other?

- 2. Is the exposed GND pad solid connected to the source of bottom MOSFET M4 and the negative terminal of  $C_{VLOW}$  capacitors? In divider and doubler applications, a solid ground plane is preferred for noise and thermal improvement.

- Are the I<sub>SENSE</sub><sup>+</sup> and I<sub>SENSE</sub><sup>-</sup> leads routed together with minimum PC trace spacing? The filter capacitor between I<sub>SENSE</sub><sup>+</sup> and I<sub>SENSE</sub><sup>-</sup> should be as close as possible to the IC. Ensure accurate current sensing with Kelvin connections at the sense resistor.

- 4. Is the INTV<sub>CC</sub> bypassing capacitor connected close to the IC, between the INTV<sub>CC</sub> and the ground plane? This capacitor carries the MOSFET drivers current peaks. An additional  $1\mu$ F ceramic capacitor placed immediately next to the INTV<sub>CC</sub> and GND can substantially improve noise performance.

- 5. Keep the switching nodes (SW1, SW3), top gate nodes (G1, G2, G3), and boost nodes (BOOST1, BOOST3) away from sensitive small-signal nodes. All of these nodes have very large and fast moving signals and therefore should be kept on the output side of the LTC7820 and occupy minimum PC trace area.

- 6. Use a modified star ground technique: a low impedance, large copper area central grounding point on the same side of the PC board as the input and output capacitors with tie-ins for the bottom of the INTV<sub>CC</sub> bypass capacitor.

Figure 6 illustrates the high current paths requiring thick and wide copper trace connection. Refer to demo boards on www.linear.com/demo for PCB layout examples.

### PC Board Layout Debugging

Start with one controller at a time. Monitor the switching nodes (SW1/SW3 pin) and probe the  $V_{LOW}$  voltage as well. Check for proper performance over the operating voltage and current range expected in the application. The frequency of operation should be maintained over the full input voltage range down to dropout.

The duty cycle percentage should be maintained from cycle to cycle in a well-designed, low noise PCB implementation.

Reduce  $V_{IN}$  from its nominal level to verify operation of the regulator in dropout. Check the operation of the undervoltage lockout circuit by further lowering  $V_{IN}$  while monitoring the outputs to verify operation.

Investigate whether any problems exist only at higher output currents or only at higher input voltages. If problems coincide with high input voltages and low output currents, look for capacitive coupling between the BOOST, SW, G1/2/3/4 connections and the sensitive voltage and current pins. The capacitor placed across the current sensing pins needs to be placed immediately adjacent to the pins of the IC. This capacitor helps to minimize the effects of differential noise injection due to high frequency capacitive coupling. If problems are encountered with high current output loading at lower input voltages, look for inductive coupling between C<sub>IN</sub>, Schottky and the top MOSFET components to the sensitive current and voltage sensing traces. In addition, investigate common ground path voltage pickup between these components and the GND pin of the IC.

Figure 6. High Current Path in Printed Circuit Board Layout Diagram

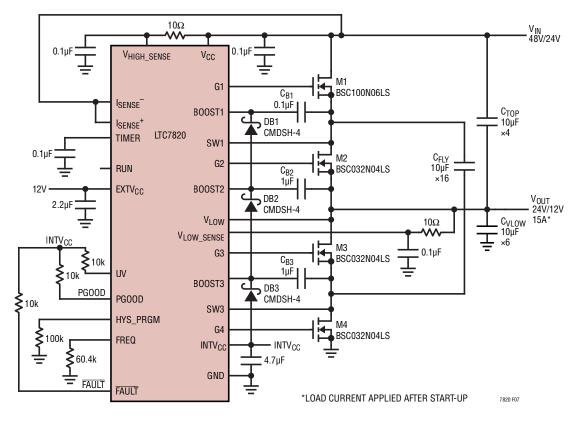

### **Design Example**

As a design example using LTC7820 for a high voltage high power voltage divider, assume  $V_{IN} = 48V$  (nominal),  $V_{IN} = 55V$  (maximum),  $V_{OUT} = 24V$  (nominal),  $I_{OUT} = 15A$  (maximum).

For high power and high voltage applications, always start with a low switching frequency e.g. 200kHz to minimize the switching losses. To set the 200kHz switching frequency, a 60.4k/1% resistor is connected from Freq pin to ground.

Setting the  $C_{FLY}$  voltage ripple to be 2% of the output voltage is a good starting point with trade-off between efficiency and power density. The  $C_{FLY}$  can be calculated based on the equation below:

$$C_{FLY} = \frac{I_{OUT(MAX)}}{2f_{S}V_{CFLY(RIPPLE)}} = \frac{15A}{2 \cdot 200 \text{kHz} \cdot 0.48\text{V}}$$

$$= 78.125\mu\text{F}$$

Considering the ceramic capacitance derating at 24V DC bias voltage, 16 of  $10\mu$ F/X7R/50V ceramic capacitors are paralleled as flying capacitors. The worst case RMS current may be 40% higher than the maximum output current. So the worst case RMS on each capacitor can be estimated by this equation:

$I_{RMS(MAX)} = \frac{I_{OUT(MAX)} \bullet 140\%}{N} = \frac{15A \bullet 140\%}{16} = 1.3125A$

where N is the number of flying capacitors. Double check and make sure the RMS current on each capacitor is below the ripple current ratings and temperature rise is below the limits. The output capacitor selection is similar to the flying capacitor selection. More output capacitors resulting smaller output voltage ripple. Because of the lower RMS current, the output capacitor value can be much less than the flying capacitor. Some of the capacitors may be connected between input and output to serve as input/output capacitors at the same time, as shown in Figure 6. However the voltage rating of those capacitors has to be selected based on the input voltage instead of the output voltage.

For MOSFET selection, the top MOSFET M1 drain to source voltage has to be higher than the maximum input voltage, while the other three MOSFETs drain to source voltage only needs to be higher than half of the maximum input voltage. Since logic level FETs are preferred, an Infineon BSC100N06LS is chosen as the top MOSFET M1 and BSC032N04LS are used as M2/3/4. Based on the output resistance equation in the application section, the output resistance is around  $20m\Omega$ , which will result 300mV drop at the 24V output at 15A load current. In reality, due to the finite dead time and parasitic resistance on the PCB, the voltage drop may be higher than the calculated value. Taking into account the output voltage ripple, a window comparator with ±1V programmed hysteresis is used to monitor the output voltage and compares it with the half of the input voltage during operation. To set the 1V hysteresis, a 100k/1% resistor is connected from HYS PRGM pin to ground.

Figure 7. High Efficiency 48V/24V to 24V/12V, 15A Voltage Divider

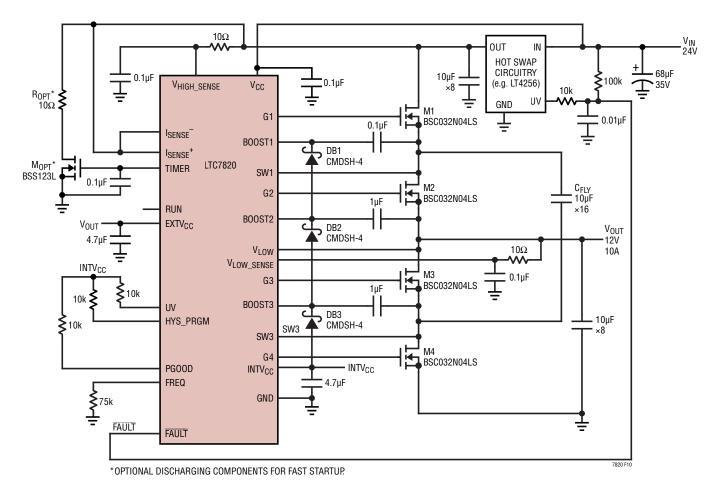

Figure 8. High Efficiency 24V to 48V, 7.5A Voltage Doubler with Disconnect FET at Input

\*OPTIONAL DISCHARGING COMPONENTS FOR FAST STARTUP.

### Figure 9. High Efficiency 24V to -24V, 10A Voltage Inverter with Hot Swap at Input

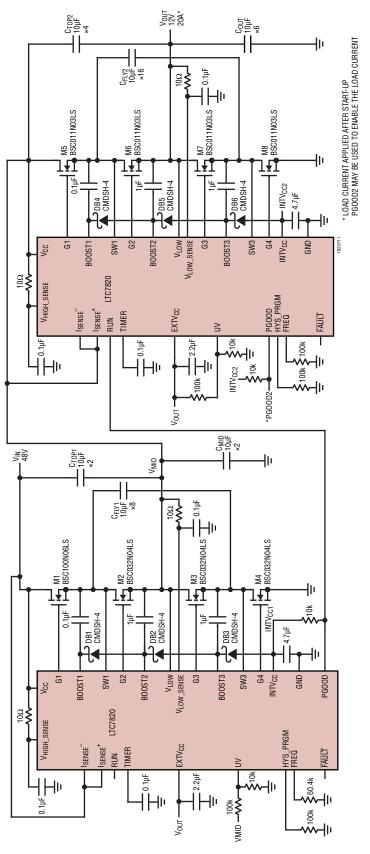

Figure 10. High Efficiency 24V to 12V, 10A Voltage Divider with Hot Swap at Input

Figure 11. High Efficiency 48V to 12V, 20A Voltage Divider

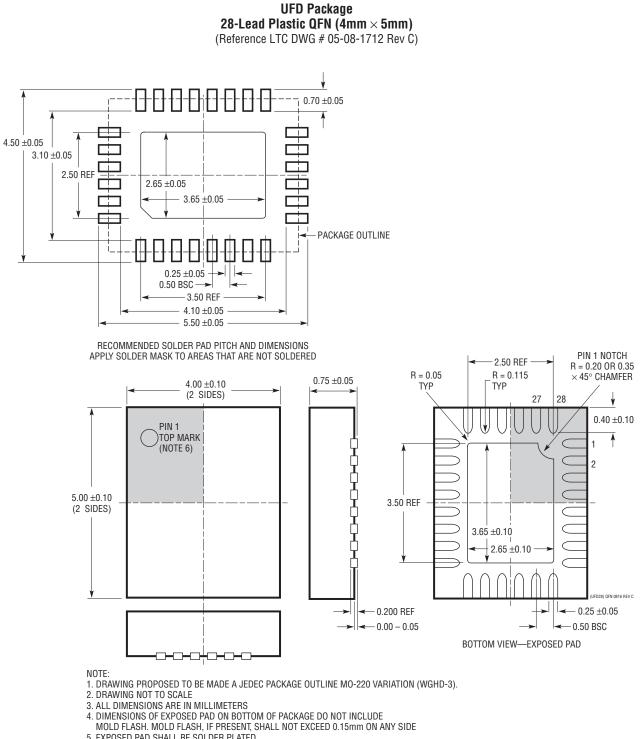

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LTC7820#packaging for the most recent package drawings.

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

- ON THE TOP AND BOTTOM OF PACKAGE

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                  | PAGE NUMBER |

|-----|-------|--------------------------------------------------------------|-------------|

| Α   | 06/17 | Removed TG/BG from EC tables                                 | 3S          |

| В   | 07/17 | Changed the # of Switching Cycles in Voltage Divider section | 12          |

|     |       | Modified INTV <sub>CC</sub> pin description                  | 7           |

|     |       | Changed hysteresis voltage in Power Good Section             | 11          |

| С   | 10/17 | Corrected hot swap part number call-out.                     | 23, 24      |

Figure 12. High Efficiency 24V to 12V, 15A Voltage Divider with Disconnect FET at Output

## **RELATED PARTS**

| PART NUMBER                         | DESCRIPTION                                                                             | COMMENTS                                                                                                                                                                                  |

|-------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3255                             | 48V Fault Protected 50mA Step-Down Charge Pump                                          | $4V \le V_{IN} \le 48V$ , $2.4V \le V_{OUT} \le 12.5V$ , $I_Q = 20\mu A$ , $3mm \times 3mm$ DFN-10, MSOP-10                                                                               |

| LTC3895                             | 150V Low I <sub>Q</sub> , Synchronous Step-Down DC/DC Controller                        | $4V \leq V_{IN} \leq 140V,~150V_{P-P},~0.8V \leq V_{OUT} \leq 24V,~I_Q$ = $50 \mu A$ PLL Fixed Frequency 50kHz to 900kHz                                                                  |

| LTC3891                             | 60V, Low I <sub>Q</sub> , Synchronous Step-Down DC/DC<br>Controller with 99% Duty Cycle | $4V \leq V_{IN} \leq 60V, \ 0.8V \leq V_{OUT} \leq 24V, \ I_Q$ = 50µA PLL Fixed Frequency 50kHz to 900kHz                                                                                 |

| LTC3897                             | 60V Multiphase Synchronous Boost Controller with Input/ Output Protection               | $4V \le V_{IN} \le 60V,  V_{OUT}$ Up to 60V, In-Rush Current Control, Overcurrent Protection and Output Disconnect                                                                        |

| LTC3784                             | 60V Single Output, Low I <sub>Q</sub> Multiphase Synchronous<br>Boost Controller        | 4.5V (Down to 2.3V After Start-Up) $\leq$ V_{IN} $\leq$ 60V, V_{OUT} Up to 60V, PLL Fixed Frequency 50kHz to 900kHz, 4mm $\times$ 5mm QFN-28, SSOP-28                                     |

| LTC3769                             | $60V \ Low \ I_{\rm Q}$ Synchronous Boost Controller                                    | 4.5V (Down to 2.3V After Start-Up) $\leq$ V_{IN} $\leq$ 60V, V_{OUT} Up to 60V, PLL Fixed Frequency 50kHz to 900kHz, 4mm $\times$ 4mm QFN-20, TSSOP-20                                    |

| LTC4442                             | High Speed Synchronous N-Channel MOSFET<br>Drivers                                      | Up to 38V Supply Voltage, $6V \le V_{CC} \le 9.5V$ , 2.4A Peak Pull-Up/5A Peak Pull-Down, MSOP-8                                                                                          |

| LT <sup>®</sup> 4256-1/<br>LT4256-2 | Positive High Voltage Hot Swap Controllers                                              | $10.8V \leq V_{IN} \leq 80V,$ Active Current Limit, Auto-Retry or Latchoff                                                                                                                |

| LTM4636/<br>LTM4636-1               | 40A, DC/DC μModule Regulator                                                            | 4.7V $\leq$ V $_{IN}$ $\leq$ 15V. 0.6V $\leq$ V $_{OUT}$ $\leq$ 3.3V, 16mm $\times$ 16mm $\times$ 7.07mm (BGA)                                                                            |

| LTM <sup>®</sup> 4650/<br>LTM4650A  | Dual 25A or Single 50A DC/DC µModule Regulator                                          | $4.5V \le V_{IN} \le 15V,  0.6V \le V_{OUT} \le 1.8V,  16mm \times 16mm \times 5.01mm$ (BGA) $4.5V \le V_{IN} \le 16V,  0.6V \le V_{OUT} \le 5.5V,  16mm \times 16mm \times 5.01mm$ (BGA) |