# SANYO Semiconductors

DATA SHEET

An ON Semiconductor Company

LV24250LS

# Bi-CMOS LSI Compact Portable Equipment 1-Chip FM Tuner IC

## **Overview**

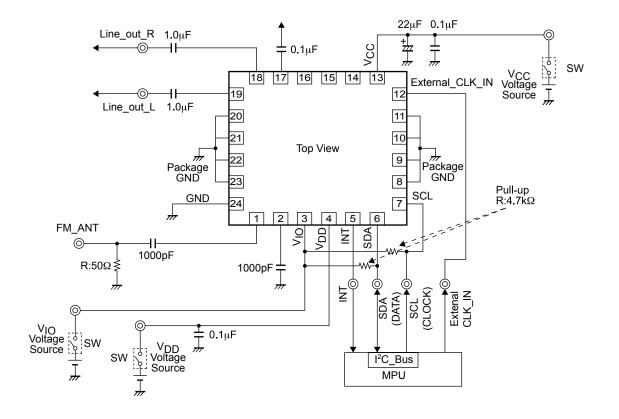

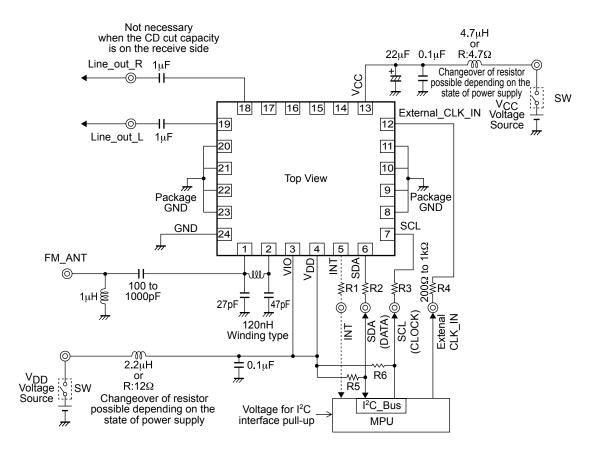

The LV24250LS is an I<sup>2</sup>C-controlled single-chip FM tuner IC that integrates external components which are necessary for tuning in a compact VQLP package with dimensions of only 3.5mm×3.5mm.

## Features

- FM FE

- FM IF

- MPX stereo decoder

- FLL Tuning

- Standby

## **Specifications**

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol                | Conditions                   | Ratings              | Unit |

|-----------------------------|-----------------------|------------------------------|----------------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max   | Analog block supply voltage  | 5.0                  | V    |

|                             | V <sub>DD</sub> max   | Digital block supply voltage | 4.0                  | V    |

| Maximum input voltage       | V <sub>IN</sub> 1 max | SCL, SDA, Int                | V <sub>DD</sub> +0.3 | V    |

|                             | V <sub>IN</sub> 2 max | External_clk_in              | V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pd max                | Ta ≤ 70°C *                  | 140                  | mW   |

| Operating temperature       | Topr                  |                              | -20 to +70           | °C   |

| Storage temperature         | Tstg                  |                              | -40 to +125          | °C   |

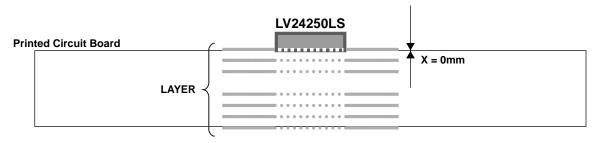

\*: When mounted on the specified printed circuit board (40.0mm × 50.0 mm × 0.8mm), Four layers glass epoxy (2S2P)

Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

> SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network

#### **Operating Conditions** at $Ta = 25^{\circ}C$

| Parameter                      | Symbol             | Conditions                   | Ratings    | Unit |

|--------------------------------|--------------------|------------------------------|------------|------|

| Recommended supply voltage     | V <sub>CC</sub>    | Analog block supply voltage  | 3.0        | V    |

|                                | V <sub>DD</sub>    | Digital block supply voltage | 3.0        | V    |

| Operating supply voltage range | V <sub>CC</sub> op |                              | 2.6 to 3.6 | V    |

|                                | V <sub>DD</sub> op |                              | 2.5 to 3.6 | V    |

|                                | V <sub>IO</sub> op | Interface voltage            | 2.2 to 3.6 | V    |

Note : Supply voltage V\_{IO} equal V\_{DD}, or V\_{IO} \leq V\_{DD} & V\_{IO}  $\geq$  2.2 V

\* Stabilize the service voltage so as not to cause the voltage change by the noise etc.

# **Operating Characteristics** at Ta = 25°C, $V_{CC}$ = 3.0V, $V_{DD}$ = 3.0V, Volume =15/16, Soft Mute = 1/Soft Stereo = off with the designated test circuit

Output level set with Radio Control 1 of control register map (0Dh Bit0, Bit1, Bit5 set to '1', '1')

Control 2 of control register map (0Dh Bit1 set to '1')

In addition, Set IF OSC = 170kHz, IF BW = 100% (Radio Control 1 : 0D Bit6, Bit7 set to '1', '1')

|                                       |                   | ,                                                                                 |                 | Ratings        |               |             |

|---------------------------------------|-------------------|-----------------------------------------------------------------------------------|-----------------|----------------|---------------|-------------|

| Parameter                             | Symbol            | Conditions                                                                        | min             | typ            | max           | Unit        |

| Current drain                         | I <sub>CC</sub> A | Analog block at 60dBµV EMF input                                                  |                 | 12             | 17            | mA          |

| (in operation)                        | ICCD              | Digital block at 60 dBµV EMF input                                                |                 | 0.3            | 0.8           | mA          |

| Current drain                         | ICCA              | Analog standby mode                                                               |                 | 3              | 30            | μA          |

| (in standby)                          | ICCD              | Digital standby mode                                                              |                 | 3              | 30            | μA          |

| FM receive band                       | F_range           | Refer to PCB mounting conditions to cover<br>the FM receive band of 76M to 108MHz | 76              |                | 108           | MHz         |

| FM receive characteristics; MONO      | : fc = 80MHz, fr  | m = 1kHz, 22.5kHzdev. Note that Soft_mute = 1, S                                  | Soft_stereo fur | nction OFF, IH | IF-BPF used   |             |

| 3dB sensitivity                       | -3dB LS           | 60dBμV, 22.5kHzdev output standard,<br>-3dB input.                                |                 | 5              | 17            | dBµV<br>EMF |

| Practical sensitivity 1               | QS1               | Input at S/N = 30dB<br>De-emphasis = 75µs, SG open display                        |                 | 8              | 16            | dBμ\<br>EMF |

| Practical sensitivity 2 (Reference)   | QS2               | Input at S/N = 26dB<br>De-emphasis = 75µs, SG terminal display                    |                 | 1.10           |               | μV          |

| Demodulation output                   | Vo                | 60dBμV EMF, pin 19 output                                                         | 80              | 110            | 160           | mVrm        |

| Channel balance                       | СВ                | 60dBµV EMF, pin 18 output/pin 19 output                                           | -2              | 0              | 2             | dB          |

| Signal-to-noise ratio                 | S/N               | 60dBμV EMF, pin 19 output                                                         | 48              | 58             |               | dB          |

| Total harmonic distortion 1<br>(MONO) | THD1              | 60dBμV EMF, pin 19 output, 22.5kHz dev.                                           |                 | 0.4            | 1.5           | %           |

| Total harmonic distortion 2<br>(MONO) | THD2              | 60dBμV EMF, pin 19 output, 75.0kHz dev.                                           |                 | 1.3            | 3             | %           |

| Field intensity display level         | FS                | Reg1Dh_bit0 = OFF<br>Input level at which Reg02h_bit1-3 change<br>from 1 to 2.    | 3               | 10             | 20            | dBμV<br>EMF |

| Mute attenuation                      | Mute-Att.         | 60dBμV EMF, pin 19 output                                                         | 60              | 70             |               | dB          |

| FM receive characteristics ; STER     | EO characterist   | t <b>ics :</b> fc = 80MHz, fm = 1kHz, V <sub>IN</sub> = 60dBμV EMF                | , Pilot = 10%   | (7.5kHzdev), N | MPX-Filter us | sed         |

| Separation                            | SEP               | L-mod, pin 19 / pin 18 output<br>L+R signals = 30% (22.5kHz dev.)                 | 20              | 35             |               | dB          |

| Total harmonic distortion (Main)      | THD-ST1           | Main-mod (for L + R input), 19 output<br>IHF BPF L+R signals = 30% (22.5kHzdev.)  |                 | 0.6            | 1.8           | %           |

#### Interface block allowable operation range at Ta = -20 to $+70^{\circ}$ C, V<sub>SS</sub> = 0V

| Devenuetor                         | Querra ha a l   | Conditions                                        |                    | Ratings |                    | Unit |

|------------------------------------|-----------------|---------------------------------------------------|--------------------|---------|--------------------|------|

| Parameter                          | Symbol          | Conditions                                        | min                | typ     | max                | Unit |

| Supply voltage                     | V <sub>DD</sub> |                                                   | 2.5                |         | 3.6                | V    |

| Digital block input                | VIH             | High-level input voltage range                    | 0.7V <sub>DD</sub> |         | V <sub>DD</sub>    | V    |

|                                    | VIL             | Low-level input voltage range                     | 0                  |         | 0.1V <sub>DD</sub> | V    |

| Digital block output               | IOL             | Output current at Low level                       | 2.0                |         |                    | mA   |

|                                    | V <sub>OL</sub> | Output voltage at Low level I <sub>OL</sub> = 2mA |                    |         | 0.6                | V    |

| External clock operating frequency | fclk_ext        | Clock frequency for external input                | 32k                | 32.768k | 20M                | Hz   |

Note : External clock input (pin 12) allows also input of the sine wave signal.

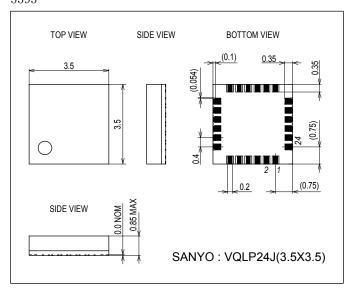

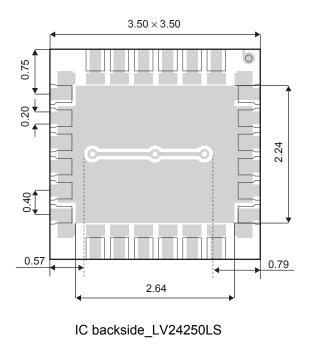

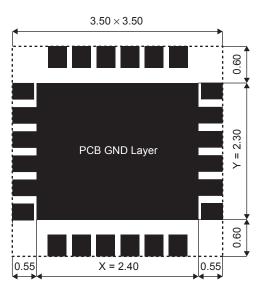

## **Package Dimensions**

unit : mm (typ) 3393

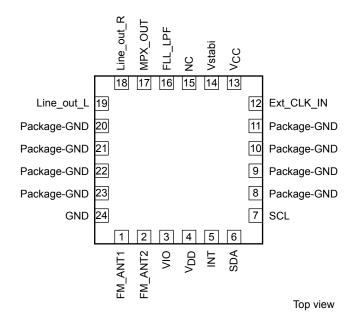

## **Pin Assignment**

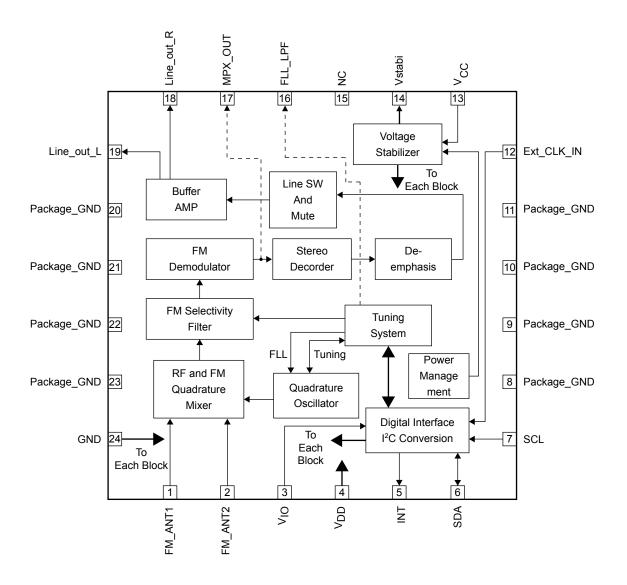

## **Block Diagram**

## **Pin Function**

| Pin No.            | Pin name           | Description                                                                                                                | Pin voltage      | Internal equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2             | FM-ANT1<br>FM-ANT2 | Antenna input<br>For pin 1 single input, pin 2 is set<br>to AC_GND via capacity                                            | 1V               | ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2<br>ANT2 |

| 3                  | V <sub>I/O</sub>   | Digital interface supply voltage<br>Power pin dedicated to the<br>interface input/output elements                          | V <sub>I/O</sub> | $V_{DD}$ $V_{I/O}$ $3$ to each interface block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4                  | V <sub>DD</sub>    | Digital supply voltage<br>Power pin for digital block                                                                      | V <sub>DD</sub>  | VDD<br>(4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                  | INT                | Interrupt line<br>Output pin dedicated to interrupt<br>(hardware output: used for<br>options)                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6                  | SDA                | Digital interface DATA ine<br>Bidirectional data line. Pull up to<br>Vio line with $3.3k\Omega$ to $10k\Omega$<br>resistor |                  | C − − − − − − − − − − − − − − − − − − −                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7                  | SCL                | Digital interface Clock line                                                                                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8<br>9<br>10<br>11 | Package-GND        | GND for package-shield<br>BND pin for package shield                                                                       | (GND)            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12                 | Ext_CLK_IN         | Reference clock-source input<br>for measurement<br>External standard CLK input pin.                                        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Continued on next page.

| Pin No.              | Pin name        | Description                                                                                                                                                             | Pin voltage     | Supplement                                                                                                    |

|----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|

| 13                   | V <sub>CC</sub> | Analog supply voltage<br>Power pin for analog (tuner)<br>block                                                                                                          | V <sub>CC</sub> | V <sub>CC</sub><br>13<br>Bias Regulater<br>777                                                                |

| 14                   | Vstabi          | Stabilizer voltage<br>Local oscillator reference bias<br>pin. NC pin to be used                                                                                         | 2.6V            | Vcc<br>Vstabi. line for<br>each block<br>Ustabi. line for<br>each block<br>Ucc<br>Bias Regulater<br>OSC block |

| 15                   | . NC            | Keep this open                                                                                                                                                          |                 |                                                                                                               |

| 16                   | FLL_LPF         | LPF for FLL<br>LPF pin for noise decrease when<br>FLL operates. Capacity(0.47µF<br>to 1.0µF) is added this pin and<br>between Vstabi pin of 14pin. NC<br>pin to be used |                 |                                                                                                               |

| 17                   | MPX_OUT         | MPX-signal output<br>Stereo decoder input monitor pin.<br>NC pin to be used                                                                                             | 2.3V            | Vstabi<br>100Ω<br>17<br>WV<br>4<br>100Ω                                                                       |

| 18                   | LINE-OUT-R      | Radio Rch Line-output<br>Audio R_ch output                                                                                                                              | 1.2V            | Vstabi Vstabi                                                                                                 |

| 19                   | LINE-OUT-L      | Radio Lch Line-output<br>Audio L_ch output                                                                                                                              | 1.2V            |                                                                                                               |

| 20<br>21<br>22<br>23 | Package-GND     | GND for package-shield<br>GND pin for package shield                                                                                                                    | (GND)           |                                                                                                               |

| 24                   | GND             | GND (Analog and Digital GND)<br>GND pin for analog (FM tuner)<br>block and digital (control) block                                                                      | (GND)           |                                                                                                               |

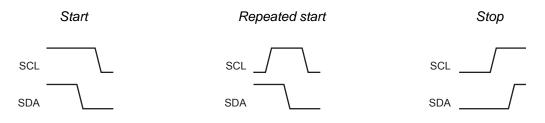

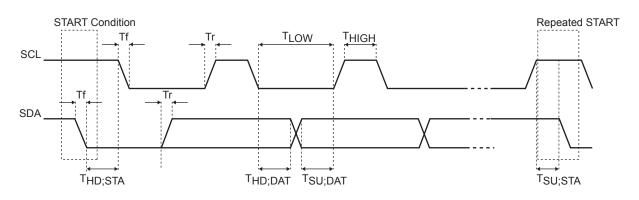

## Format of Bus Transfers

Bus transfers are primarily based on the I2C primitives

- Start condition

- Repeated start condition

- Stop condition

- Byte write

- Byte read

Start, restart, and stop conditions are specified as shown in Table 1 below.

Fig. 1 the I<sup>2</sup>C start, repeated start and stop conditions.

For details, like timing, etc., refer to specifications of I<sup>2</sup>C.

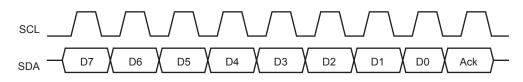

8-bit write

8-bit data is sent from the master microcomputer to LV24250LS.

Data bit consists of MSB first and LSB last.

Data transmission is latched at the rising edge of SCL in synchronization with the SCL clock generated at the master IC. Do not change data while SCL remains HIGH.

LV24250LS outputs the ACK bit between eighth and ninth falling edges of SCL

Fig. 2 Signal pattern of the I<sup>2</sup>C byte write

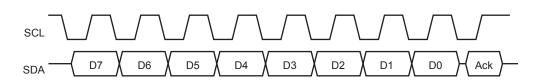

Read is of the same form as write, only except that the data direction is opposite. Eight data bits are sent from LV24250LS to the master while Ack is sent from the master to LV24250LS.

Fig. 3 Signal pattern of the I<sup>2</sup>C byte read

The serial clock SCL is supplied from the master side. It is essential that data bit is output from LV24250LS in synchronization with the falling edge while the master side performs latching at the rising edge.

#### LV24250LS latches ACK at the rising edge.

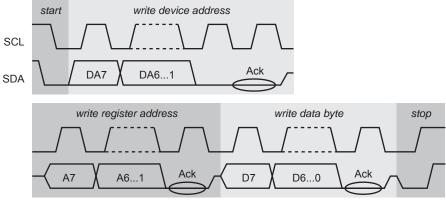

The sequence to write data D into the register A of LV24250LS is shown below.

- Start condition

- write the device address (C0h)

- write the register address, A

- write the target data, D

- stop condition

Fig. 4 Register write through I<sup>2</sup>C

When one or more data has been provided for writing, only the first data is allowed to be written.

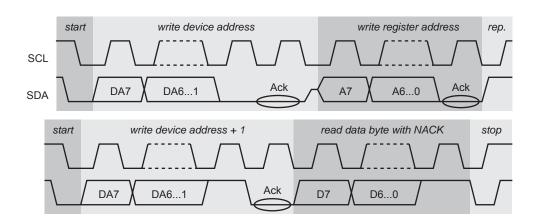

#### Read sequence

- start condition

- write the device address (C0h)

- write the register address, A

- repeated start condition (or stop + start in a single master network)

- write the device address + 1 (C1h)

- read the register contents D, transmit NACK (no more data to be read)

- stop condition

Fig. 5 Register read through I<sup>2</sup>C

## Interrupt Pin INT

LV24250LS has the dedicated interrupt output pin. For the active level to the host, either LOW or HIGH can be selected. The INT output pin is kept floating while the PWRAD bit is cleared during initialization.

Therefore, to avoid influence on the CPU side during initialization, it is recommended to secure the non-active state by means of the pull-up or pull-down resistor.

This enables direct INT output connection to non-masking interruption of the host CPU.

## Digital interface specification (interface specification : reference)

(1). Characteristics of SDA and SCL bus line relative to the I<sup>2</sup>C bus interface

| Deventer                           | 0 stat                | Standard | -mode | High_Spee | ed-mode |      |

|------------------------------------|-----------------------|----------|-------|-----------|---------|------|

| Parameter                          | Symbol                | min      | max   | min       | max     | unit |

| SCL clock frequency                | F <sub>SCL</sub>      | 0        | 100   | 0         | 400     | kHz  |

| Fall time of both SDA and SCL      | Tf                    |          | 300   | 20+0.1Cb  | 300     | ns   |

| Rise time of both SDA and SCL      | Tr                    |          | 1000  | 20+0.1Cb  | 300     | ns   |

| High time of SCL                   | T <sub>HIGH</sub>     | 4.0      |       | 0.6       |         | μS   |

| Low time of SCL                    | TLOW                  | 4.7      |       | 1.3       |         | μS   |

| Hold time of STAT condition        | T <sub>HD</sub> ; STA | 4.0      |       | 0.6       |         | μS   |

| Hold time of Data                  | T <sub>HD</sub> ; DAT | 0        | 3.45  | 0         | 0.9     | μS   |

| Set-up time of STAT condition      | T <sub>SU</sub> ; STA | 4.7      |       | 0.6       |         | μS   |

| Set-up time of STOP condition      | T <sub>SU</sub> ; sto | 4.0      |       | 0.6       |         | μS   |

| Set-up time of Data                | T <sub>SU</sub> ; DAT | 250      |       | 100       |         | ns   |

| Bus free time between a STOP and   | T <sub>BUF</sub>      | 4.7      |       | 1.3       |         | μS   |

| Capacitivie load for each bus line | Cb                    |          | 400   |           | 400     | pF   |

\*Cb = Total capacitance of one bus line

#### (2). Register map (On Register Map)

#### Following is Sub address map of LV24250LS. Each register becomes 8-bit constitution.

| Address | Register Name | Mode | Remark                        |

|---------|---------------|------|-------------------------------|

| 00h     | CHIP_ID       | R/W  | Chip ID                       |

| 02h     | RADIO_STAT    | R    | Status of Radio Station       |

| 0Bh     | RFCAP         | R/W  | RF Cap bank                   |

| 0Dh     | RADIO_CTRL1   | R/W  | Radio Control 1               |

| 0Eh     | RADIO_CTRL2   | R/W  | Radio Control 2               |

| 0Fh     | RADIO_CTRL3   | R/W  | Radio Control 3               |

| 10h     | TNPL          | R    | Tune Position Low             |

| 11h     | TNPH_STAT     | R    | Tune Position High and Status |

| 19h     | REF_CLK_PRS   | R/W  | Reference clock pre-scalar    |

| 1Ah     | REF_CLK_DIV   | R/W  | Reference clock divider       |

| 1Bh     | REF_CLK_OFF   | R/W  | Reference clock offset        |

| 1Dh     | SCN_CTRL      | R/W  | Scan control                  |

| 1Eh     | TARGET_VAL_L  | R/W  | Target value Low              |

| 1Fh     | TARGET_VAL_H  | R/W  | Target value High             |

R : Read only register R/W : Read and Write register

#### (3). Register description (ON Contents of each Register)

## Register 00h – CHIP\_ID – Chip identify register (Read/Write)

|           |                                    |                        | ID [7 | 7 : 0] |  |  |

|-----------|------------------------------------|------------------------|-------|--------|--|--|

| bit 7-0 : | <b>ID [7 : 0] :</b> 8<br>LV24250LS | 3-bit chip ID.<br>:15h |       |        |  |  |

#### Register 02h – RADIO\_STAT – Radio station status (Read-Only)

| 7                  | 6                     | 5                      | 4                  | 3                | 2          | 1 | 0     |

|--------------------|-----------------------|------------------------|--------------------|------------------|------------|---|-------|

| RAD_IF             | N/A                   | N/A                    | MO_ST              |                  | FS [2 : 0] |   | SF5DB |

| bit 7 :            | RAD_IF : R            | adio interrupt flag.   |                    |                  |            |   |       |

|                    | 0 = no ini            | terrupt                |                    |                  |            |   |       |

|                    | 1 = interr            | upt                    |                    |                  |            |   |       |

|                    | Note :                |                        |                    |                  |            |   |       |

| When status (fi    | eld strength, stereo  | /mono) changes, thi    | s bit is set.      |                  |            |   |       |

| If Interrupt of IF | RQ pin is enabled, Ir | nterrupt pin is set by | following IPOL reg | ister condition. |            |   |       |

| This bit is clear  | ed by register read.  | In stand-by mode (     | PW_RAD = 0), this  | bit is 1         |            |   |       |

| bit 6-5 :          | NA [1 : 0] :          | NA 0 fixed             |                    |                  |            |   |       |

| bit 4 :            | <b>MO_ST</b> : M      | ono/stereo indicato    | r                  |                  |            |   |       |

|                    | 0 = Force             | ed monaural            |                    |                  |            |   |       |

|                    | 1 = Norm              | nal (Receiving in ste  | reo mode)          |                  |            |   |       |

| bit 3-1            | FS [2 : 0] :          | Fieldstrength :        |                    |                  |            |   |       |

|                    | 0 = Low 1             | field strength         |                    |                  |            |   |       |

|                    |                       |                        |                    |                  |            |   |       |

|                    | 7 = High              | field strength         |                    |                  |            |   |       |

|                    |                       |                        |                    |                  |            |   |       |

| bit 0 :            |                       | eldstrength +5dB :     |                    |                  |            |   |       |

|                    | 0 = FS5d              |                        |                    |                  |            |   |       |

|                    | 1 = FS5d              | IR Ob                  |                    |                  |            |   |       |

| For details, refer | to Application note.  |                        |                    |                  |            |   |       |

#### Register 0Bh – RFCAP – RF Cap bank (Read/Write)

| 7         | 6          | 5                   | 4        | 3         | 2 | 1 | 0 |

|-----------|------------|---------------------|----------|-----------|---|---|---|

|           |            |                     | RFCA     | P [7 : 0] |   |   |   |

| bit 7-0 : | RFCAP [7 : | 0]: RF Oscillator ( | CAP bank |           |   |   |   |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                        | VOL [1 : 0] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| bit 6 :<br><b>IFBWSEL</b> : IF band width setting<br>0 = 50%<br>1 = 100%<br>bit 5 :<br><b>VOL_2</b> : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1<br>bit 4 :<br><b>DEEM</b> : de-emphasis<br>$0 = 50\mu s$ : Korea, China, Europe, Japan<br>$1 = 75\mu s$ : USA<br>bit 3 :<br><b>ST_M</b> : Stereo/mono setting<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode) |             |

| $1 = 170 \text{kHz}$ bit 6 :IFBWSEL : IF band width setting<br>$0 = 50\%$<br>$1 = 100\%$ bit 5 :VOL_2 : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1bit 4 :DEEM : de-emphasis<br>$0 = 50\mu s$ : Korea, China, Europe, Japan<br>$1 = 75\mu s$ : USAbit 3 :ST_M : Stereo/mono setting<br>$0 = Stereo enabled1 = Stereo disabled (mono mode)$                               |             |

| bit 6 : IFBWSEL : IF band width setting<br>0 = 50%<br>1 = 100%<br>bit 5 : VOL_2 : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1<br>bit 4 : DEEM : de-emphasis<br>0 = 50µs : Korea, China, Europe, Japan<br>1 = 75µs : USA<br>bit 3 : ST_M : Stereo/mono setting<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                   |             |

| $0 = 50\%$ $1 = 100\%$ bit 5 : VOL_2 : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1<br>bit 4 : DEEM : de-emphasis<br>$0 = 50\mu s : Korea, China, Europe, Japan$ $1 = 75\mu s : USA$ bit 3 : ST_M : Stereo/mono setting<br>0 = Stereo enabled $1 = Stereo disabled (mono mode)$                                                                                           |             |

| 1 = 100%bit 5 : $VOL_2$ : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1bit 4 : $DEEM$ : de-emphasis<br>$0 = 50\mu s$ : Korea, China, Europe, Japan<br>$1 = 75\mu s$ : USAbit 3 : $ST_M$ : Stereo/mono setting<br>$0 =$ Stereo enabled<br>$1 =$ Stereo disabled (mono mode)                                                                                                 |             |

| bit 5 : VOL_2 : Volume setting<br>For details, refer to Bit0,1 for RADIO_CTRL1<br>bit 4 : DEEM : de-emphasis<br>0 = 50μs : Korea, China, Europe, Japan<br>1 = 75μs : USA<br>bit 3 : ST_M : Stereo/mono setting<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                                                                                     |             |

| For details, refer to Bit0,1 for RADIO_CTRL1         bit 4 :       DEEM : de-emphasis $0 = 50 \mu s$ : Korea, China, Europe, Japan $1 = 75 \mu s$ : USA         bit 3 :       ST_M : Stereo/mono setting $0 =$ Stereo enabled $1 =$ Stereo disabled (mono mode)                                                                                                                             |             |

| bit 4 :<br>DEEM : de-emphasis<br>$0 = 50\mu s : Korea, China, Europe, Japan$<br>$1 = 75\mu s : USA$<br>bit 3 :<br>$ST_M : Stereo/mono setting$<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                                                                                                                                                     |             |

| 0 = 50μs : Korea, China, Europe, Japan<br>1 = 75μs : USA<br>bit 3 : ST_M : Stereo/mono setting<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                                                                                                                                                                                                     |             |

| <pre>1 = 75μs : USA bit 3 : ST_M : Stereo/mono setting 0 = Stereo enabled 1 = Stereo disabled (mono mode)</pre>                                                                                                                                                                                                                                                                             |             |

| bit 3 : ST_M : Stereo/mono setting<br>0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                                                                                                                                                                                                                                                                 |             |

| 0 = Stereo enabled<br>1 = Stereo disabled (mono mode)                                                                                                                                                                                                                                                                                                                                       |             |

| 1 = Stereo disabled (mono mode)                                                                                                                                                                                                                                                                                                                                                             |             |

|                                                                                                                                                                                                                                                                                                                                                                                             |             |

| bit 2 : nMUTE : Audio Mute                                                                                                                                                                                                                                                                                                                                                                  |             |

| bit 2. INFOTE Additionate                                                                                                                                                                                                                                                                                                                                                                   |             |

| 0 = Mute On                                                                                                                                                                                                                                                                                                                                                                                 |             |

| 1 = Mute Off                                                                                                                                                                                                                                                                                                                                                                                |             |

| bit 1-0 : VOL [1 : 0] : Volume Setting<br>* It controls by Bit5 of RADIO_CTRL1 and combination 4Bit with Bit1 of RADIO_CTRL2.                                                                                                                                                                                                                                                               |             |

| Vol_3 Vol_2 Vol_1 Vol_0                                                                                                                                                                                                                                                                                                                                                                     |             |

| $\begin{array}{ccccc} 0 & 0 & 0 \\ 0 & 0 & 0 \end{array} $ Minimum level $\begin{array}{cccc} 0 & 0 & 0 \end{array}$                                                                                                                                                                                                                                                                        |             |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                        |             |

| <br>1 1 1 1 1: Max level                                                                                                                                                                                                                                                                                                                                                                    |             |

## Register 0Eh – RADIO\_CTRL2 – Radio control 2 (Read/Write)

| 7         | 6                                    | 5                      | 4           | 3              | 2 | 1   | 0        |  |  |

|-----------|--------------------------------------|------------------------|-------------|----------------|---|-----|----------|--|--|

|           | SOFTST [2 : 0]                       |                        |             | SOFTMU [2 : 0] | • | N/A | STABI_BP |  |  |

| bit 7-5 : | SOFTST [2 : 0] : Soft Stereo setting |                        |             |                |   |     |          |  |  |

|           | 000b = Sc                            | ft stereo level 3      |             |                |   |     |          |  |  |

|           | 001b = Dis                           | sable soft stereo      |             |                |   |     |          |  |  |

|           | 010b = So                            | ft stereo level 1 (*)  |             |                |   |     |          |  |  |

|           | 100b = So                            | ft stereo level 2      |             |                |   |     |          |  |  |

|           | Note : do                            | not use without the    | se value.   |                |   |     |          |  |  |

|           | (*) : recom                          | mended setting         |             |                |   |     |          |  |  |

| bit 4-2 : | SOFTMU [2                            |                        |             |                |   |     |          |  |  |

|           | 000b = Sc                            |                        |             |                |   |     |          |  |  |

|           | 001b = Disable soft audio mute       |                        |             |                |   |     |          |  |  |

|           | 010b = So                            | ft audio mute level    | 1           |                |   |     |          |  |  |

|           | 100b = So                            | ft audio mute level    | 2 (*)       |                |   |     |          |  |  |

|           | Note : do                            | not use without the    | se value.   |                |   |     |          |  |  |

|           | (*) : recom                          | mended setting         |             |                |   |     |          |  |  |

| bit 1 :   | VOL_3 : Volu                         | ume setting            |             |                |   |     |          |  |  |

|           | For details                          | s, refer to Bit0,1 for | RADIO_CTRL1 | I              |   |     |          |  |  |

| bit 0 :   | STABI_BP :                           | Internal regulator b   | y-pass bit  |                |   |     |          |  |  |

|           | 0 = Interna                          | al regulator operate   | (normal)    |                |   |     |          |  |  |

|           | 1 = Interna                          | al regulator by-pass   |             |                |   |     |          |  |  |

| 7         | 6                                     | 5                           | 4                   | 3         | 2       | 1         | 0      |  |  |  |

|-----------|---------------------------------------|-----------------------------|---------------------|-----------|---------|-----------|--------|--|--|--|

| IPOL      | SM_IE                                 | RAD_IE                      | SD_PM               | nIF_PM    | EXT_CLK | CFG [1:0] | PW_RAD |  |  |  |

| bit 7 :   | IPOL : Inter                          | rupt (IRQ) Polarity         | L                   | 1 I       |         |           | •      |  |  |  |

|           | 0 = IRQ a                             | active high                 |                     |           |         |           |        |  |  |  |

|           | 1 = IRQ a                             | active low                  |                     |           |         |           |        |  |  |  |

|           |                                       |                             |                     |           |         |           |        |  |  |  |

| bit 6 :   |                                       | mmand end interru           | pt                  |           |         |           |        |  |  |  |

|           | 0 = Disab                             |                             |                     |           |         |           |        |  |  |  |

|           | 1 = Enab                              | le                          |                     |           |         |           |        |  |  |  |

| bit 5 :   | RAD_IE : R                            | adio Interrupt (field       | strength/stereo ch  | anges)    |         |           |        |  |  |  |

|           | 0 = Disab                             | ble                         |                     |           |         |           |        |  |  |  |

|           | 1 = Enab                              | le                          |                     |           |         |           |        |  |  |  |

| bit 4 :   | SD_PM : Stereo decoder clock PLL mute |                             |                     |           |         |           |        |  |  |  |

|           | 0 = SD PLL On (Normal Operation)      |                             |                     |           |         |           |        |  |  |  |

|           | 1 = SD PLL Off (Adjustment)           |                             |                     |           |         |           |        |  |  |  |

|           |                                       |                             |                     |           |         |           |        |  |  |  |

| bit 3 :   | nIF_PM:IF                             | PLL mute                    |                     |           |         |           |        |  |  |  |

|           | 0 = IF PLL Off (Adjustment)           |                             |                     |           |         |           |        |  |  |  |

|           | 1 = IF PL                             | L On (Normal Oper           | ation)              |           |         |           |        |  |  |  |

| bit 2-1 : | EXT_CLK_                              | CFG [1:0]: Exterr           | nal Clock Setting   |           |         |           |        |  |  |  |

|           |                                       |                             |                     |           |         |           |        |  |  |  |

|           | EXT_CLK_CFG                           | 6 [1 : 0]                   | Reference clock     |           |         |           |        |  |  |  |

|           | 00                                    |                             | Off                 |           |         |           |        |  |  |  |

|           | 01                                    |                             | NA:Do not use       |           |         |           |        |  |  |  |

|           | 10                                    |                             | Oscillator clock so | urce / 32 |         |           |        |  |  |  |

|           |                                       | (for high frequency source) |                     |           |         |           |        |  |  |  |

|           | 11                                    |                             |                     |           |         |           |        |  |  |  |

|           |                                       |                             | (for low frequency  | source)   |         |           |        |  |  |  |

| bit 0 :   | PW_RAD :                              | Radio Circuit Powe          | r                   |           |         |           |        |  |  |  |

|           | _                                     | er Off (Stand-by).          |                     |           |         |           |        |  |  |  |

|           | 1 = Powe                              | er On                       |                     |           |         |           |        |  |  |  |

| No        | te : At the time of start             | . PW RAD become             | es 0 (Stand-by)     |           |         |           |        |  |  |  |

## Register 10h – TNPL – Tune position low (Read-Only)

| 7         | 6         5         4         3         2         1         0 |  |  |  |  |  |  |  |  |  |

|-----------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|           | TUNEPOS [7 : 0]                                               |  |  |  |  |  |  |  |  |  |

| bit 7-0 : | bit 7-0 : TUNEPOS [7 : 0] : Current RF Frequency (Low 8bit)   |  |  |  |  |  |  |  |  |  |

| 7                            | 6                                                                                                                                                  | 5                                                                                                                                                     | 4                       | 3                      | 2                  | 1                   | 0            |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|--------------------|---------------------|--------------|--|

|                              | ERROR [2 : 0]                                                                                                                                      |                                                                                                                                                       | SM_IF                   | TUNED                  | NA                 | TUNEP               | OS [9 : 8]   |  |

| bit 7-5 :                    | ERROR [2                                                                                                                                           | : 0] : Error Code                                                                                                                                     | ·                       |                        |                    |                     |              |  |

|                              | ERROR [2 :                                                                                                                                         | 0]                                                                                                                                                    | Remark                  |                        |                    |                     |              |  |

|                              | 0                                                                                                                                                  |                                                                                                                                                       | OK, Command             | l end (No Error)       |                    |                     |              |  |

|                              | 1                                                                                                                                                  |                                                                                                                                                       | Default value           | after or during reset  |                    |                     |              |  |

|                              | 2                                                                                                                                                  |                                                                                                                                                       | Band Limit Err          | or                     |                    |                     |              |  |

|                              | 3                                                                                                                                                  |                                                                                                                                                       | DAC Limit Erro          | or                     |                    |                     |              |  |

|                              | 6                                                                                                                                                  |                                                                                                                                                       | Command for             | ed End                 |                    |                     |              |  |

|                              | 7                                                                                                                                                  |                                                                                                                                                       | Command bus             | Command busy           |                    |                     |              |  |

|                              | 0 = No In<br>1 = Interr                                                                                                                            | •                                                                                                                                                     | rupt nag                |                        |                    |                     |              |  |

| This bit is set w            |                                                                                                                                                    | terrupt<br>rupt                                                                                                                                       |                         | wed, the pin status is | changed, Reading   | this register caus  | es clearing. |  |