## **Bi-CMOS LSI**

## **Step-down Switching Regulator**

http://onsemi.com

#### Overview

LV58063MC is a 1ch step-down switching regulator.  $0.13\Omega$  FET is incorporated on the upper side to achieve high-efficiency operation for large output current.

Low-heat resistance and compact-package SOP8L (200mil) employed.

Current mode control gives superior load current response with easy phase compensation.

EN pin, allowing the standby mode with the current drain of  $70\mu A$ .

Pulse-by-pulse over-current protection and overheat protection available for protection of load devices.

Externally adjustable soft start time.

#### **Features**

- 3A 1ch step-down switching regulator

- Wide input range (8 to 28V)

- High efficiency (90% I<sub>OUT</sub>=1A, V<sub>IN</sub>=12V, V<sub>OUT</sub>=5V) Fixed frequency: 370kHz

- Standby mode

- Over-current protection

- Overshoot control after over-current protection event

- Thermal shutdown

- Reference voltage: 0.8V

- Soft start

- Compact package: SOP8L (200mil) with exposed pad

#### **Application**

• LCD/PDP-TV

STB

White Goods

Office equipment

General consumer electronics

#### **Specifications**

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                             | Conditions             | Conditions                   | Ratings             | Unit |

|---------------------------------------|------------------------|------------------------------|---------------------|------|

| Maximum input V <sub>IN</sub> voltage | V <sub>IN</sub> max    |                              | 32                  | V    |

| BOOT pin maximum voltage              | V <sub>BT</sub> max    |                              | 37                  | V    |

| SW pin maximum voltage                | V <sub>SW</sub> max    |                              | V <sub>IN</sub> max | V    |

| BOOT pin-SW pin maximum voltage       | V <sub>BS-SW</sub> max |                              | 7                   | V    |

| FB, EN, COMP, SS pin maximum          | Vfs max                |                              | 7                   | V    |

| voltage                               |                        |                              |                     |      |

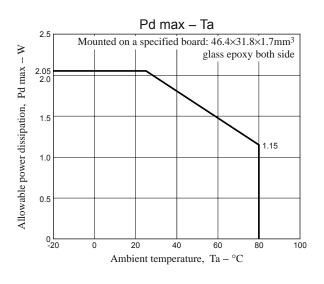

| Allowable power dissipation           | Pd max                 | Mount on a specified board * | 2.05                | W    |

| Junction temperature                  | Tj max                 |                              | 150                 | °C   |

| Operating temperature                 | Topr                   |                              | -20 to +80          | °C   |

| Storage temperature                   | Tstg                   |                              | -40 to +150         | °C   |

<sup>\*</sup> Specified board: 46.4mm  $\times$  31.8mm  $\times$ 1.7mm, glass epoxy.

Note: Plan the maximum voltage while including coil and surge voltages, so that the maximum voltage is not exceeded even for an instant.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                    | Conditions         | Conditions | Ratings                 | Unit |

|------------------------------|--------------------|------------|-------------------------|------|

| V <sub>IN</sub> pin voltage  | V <sub>IN</sub>    |            | 8 to 28                 | V    |

| BOOT pin voltage             | V <sub>BT</sub>    |            | -0.3 to 34              | V    |

| SW pin voltage               | V <sub>SW</sub>    |            | -0.4 to V <sub>IN</sub> | V    |

| BOOT pin-SW pin voltage      | V <sub>BS-SW</sub> |            | 6.5                     | V    |

| FB, EN, COMP, SS pin voltage | V <sub>FSO</sub>   |            | 6                       | V    |

#### **Electrical Characteristics** at Ta = 25 °C $V_{IN} = 12$ V, unless otherwise specified.

| D                                                     | 0 1717            | ions Conditions                                                                     |     | Ratings |     |      |

|-------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|-----|---------|-----|------|

| Parameter                                             | Conditions        |                                                                                     | min | typ     | max | Unit |

| IC current drain at standby                           | I <sub>CC</sub> 1 | EN=0V                                                                               |     | 70      |     | μΑ   |

| IC current drain in operation                         | I <sub>CC</sub> 2 | EN=open, FB=1V                                                                      |     | 5       |     | mA   |

| Efficiency                                            | Effcy             | V <sub>IN</sub> =12V, I <sub>OUT</sub> =1A, V <sub>O</sub> =5V<br>Design target: *1 |     | 90      |     | %    |

| Reference voltage                                     | Vref              | V <sub>IN</sub> =8V to 28V (±2%)                                                    | -2% | 0.8     | +2% | V    |

| FB pin bias current                                   | Iref              | FB=0.8V application                                                                 |     | 10      | 100 | nA   |

| High-side ON resistance                               | RonH              | BOOT=5V                                                                             |     | 0.13    |     | Ω    |

| Low-side ON resistance                                | RonL              |                                                                                     |     | 7       |     | Ω    |

| Oscillation frequency                                 | Fosc              |                                                                                     | 296 | 370     | 444 | kHz  |

| Oscillation frequency during short-circuit protection | Foscs             |                                                                                     | 30  | 38      | 46  | kHz  |

| EN high-threshold voltage                             | Venh              |                                                                                     |     |         | 1.9 | V    |

| EN low-threshold voltage                              | Venl              |                                                                                     | 0.8 |         |     | V    |

| EN pull-up corrent                                    | len               | EN=0V                                                                               |     | 16      |     | μА   |

| Maximum ON DUTY                                       | D max             |                                                                                     |     | 80      |     | %    |

| Current limit peak value 1                            | Icl1              | V <sub>IN</sub> =12V, V <sub>OUT</sub> =5V, L=10μH                                  | 3.8 |         |     | Α    |

| Thermal shutdown temperature                          | Ttsd              | *Design guarantee *2                                                                |     | 160     |     | °C   |

| Thermal shutdown temperature hysteresis               | Dtsd              | *Design guarantee *2                                                                |     | 40      |     | °C   |

| Soft start current                                    | I <sub>SS</sub>   | SS=0V                                                                               | 6   | 10      | 14  | μА   |

<sup>\*1:</sup> Reference value (not tested before shipment)

<sup>\*2:</sup> Design guarantee (value guaranteed by design and not tested before shipment)

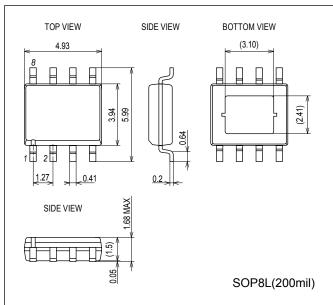

## **Package Dimensions**

unit: mm (typ)

3439

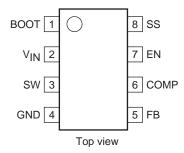

#### **Pin Assignment**

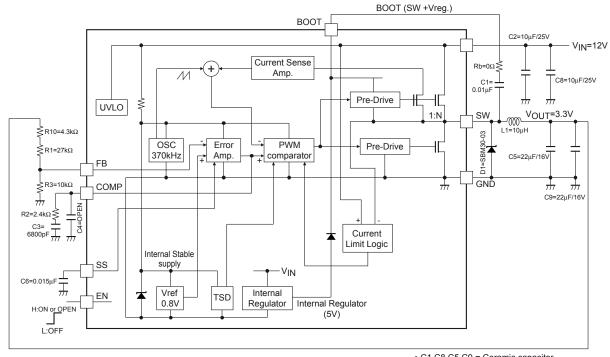

## **Block Diagram and Sample Application Circuit (3.3V output)**

- C1,C8,C5,C9 = Ceramic capacitor L1=CDRH105RNP-100NC (sumida)

#### **Pin Function**

| Pin No. | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                 | Equivalent Circuit                              |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 1       | BOOT     | Internal high side nmos fet boot strap capacitor terminal. Connect around 22nF capacitor or greater between SW and BOOT. To operate within absolute maximum rating of SW, to keep stable operation, and to reduce switching noise, please, use a series resistor, Rb (value is around $100\Omega$ ) is recommended to use.                                                                  | CBOOT  Hi side MOS  Low side MOS                |

| 2       | VIN      | Input Voltage Pin. Large Filter Capacitor ( equal or larger than 20μF) should be connected between V <sub>IN</sub> and GND to eliminate noise on the input and to operate properly.                                                                                                                                                                                                         | See BOOT                                        |

| 3       | SW       | Power Switching Pin. Connect the output LC filter. Connect the above-mentioned capacitor between this pin and BOOT pin.                                                                                                                                                                                                                                                                     | See BOOT                                        |

| 4       | GND      | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                 |                                                 |

| 5       | FB       | Feedback pin.  Connect a voltage divider resistor across FB to set the regulated output voltage. The output voltage is given by next equation. $V_{OUT} = Vref \times \left\{1 + \frac{(R1 + R10)}{R3}\right\}$ $Vref = 0.8V$ Example: 3.3V output voltage (See Block Diagram and Sample Application Circuit) $V_{OUT} = 0.8 \times \left\{1 + \frac{(27k + 4.3k)}{10k}\right\}$ $= 3.304V$ | VIN Internal regulated  10μΑ  10μΑ  VREF 0.8V   |

| 6       | COMP     | Phase compensation pin.  Connect an external capacitor and a resistor for the DC DC converter close loop-phase compensation.                                                                                                                                                                                                                                                                | COMP Clump circuit                              |

| 7       | EN       | Enable terminal.  If applying logically high voltage, or left open, the converter operates.  If connected to GND, the converter's operation stops.                                                                                                                                                                                                                                          | V <sub>IN</sub> 1kΩ  274.5kΩ  4186kΩ  93kΩ  2pF |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin name       | Description                                                                                                                                                                                                                                                               | Equivalent Circuit        |

|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Pin No. | Pin name<br>SS | Description  Soft start terminal  Internal source current (10 $\mu$ A) and external capacitor will make soft start time.  Soft start capacitor, C6 is given by next equation,  C6 = 10 $\mu$ A × $\frac{Tss}{Vref}$ Where, Tss: soft start time,  Vref: reference voltage | Equivalent Circuit See FB |

|         |                | Example : soft start time = 1.2ms $C6 = 10\mu A \times \frac{1.2ms}{0.8 \text{ V}} = 0.015\mu F$                                                                                                                                                                          |                           |

#### Considerations for the design

- Insertion of serial beads in the Schottky diode for removal of noise may cause generation of the negative voltage on SW pin deviating from the absolute maximum rating at the SW pin, resulting in failure of normal operation. Please, do not insert beads as above described. Instead, remove noise by Rb resistor.

- Exposed pad on the bottom side of the IC should be soldered. We cannot recommend other usages of the exposed pad.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa