# Step-Down Regulator

**PRODUCTION DATA SHEET**

## **DESCRIPTION**

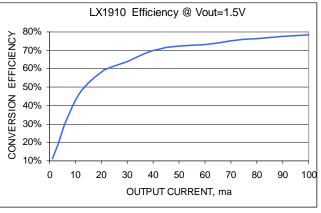

The LX1910 PWM buck regulator achieves very high efficiencies over a broad range of operating load conditions. The LX1910 implements a load-detection architecture and enters a power-saving PFM mode when driving small load currents ensuring optimal regulator efficiency over the entire output current range thus maximizing battery life.

The PWM operating mode implements a fixed frequency of 1 MHz (typ), the transconductance error amplifier has  $12 \mu A$  of drive with an output voltage swing rail to rail. Compensation is external for maximum user flexibility.

The LX1910 does not require a minimum load current for stable operation. There is no Under Voltage Lockout for the input voltage, operational range includes 4V to 6V. The regulator is capable of providing an output dc load current of 850mA. The SHDN pin places the device in a sleep-mode drawing less than 1µA of quiescent current.

The LX1910 comes in space-saving MSOP package allowing a complete application circuit to occupy a very small PCB area. These features make the LX1910 ideal for use in SmartPhones, PDAs, or other battery-operated devices

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com

## **KEY FEATURES**

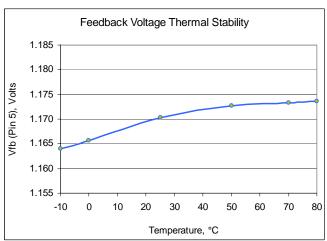

- Internal Reference 1.17V ±2% Accuracy (Line and Temperature)

- 4V to 6.0V Input Range

- Adj. Output From 1.17V to V<sub>IN</sub>

- Output Current (I<sub>DC</sub> >850mA)

- Quiescent Current < 300μA</li>

- 1MHz Operation Frequency

- MSOP 8-Pin

#### APPLICATIONS/BENEFITS

- Portable Microprocessor Core Voltage Supplies

- 5V to 3V

## PRODUCT HIGHLIGHT

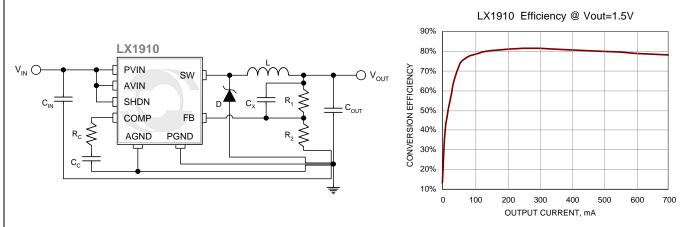

Figure 1 - LX1910 Circuit Topology and Typical Efficiency Performance

| PACKAGE ORDER INFO  |                  |                          |                                                      |  |  |

|---------------------|------------------|--------------------------|------------------------------------------------------|--|--|

| T <sub>J</sub> (°C) | Input<br>Voltage | Output<br>Voltage Range  | DU Plastic MSOP<br>8-PIN<br>RoHS Compliant / Pb-free |  |  |

| 0 to 85             | 4.5V - 6.0V      | 1.17V to V <sub>IN</sub> | LX1910CDU                                            |  |  |

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX1910-13016CDU-TR)

## **Step-Down Regulator**

**PRODUCTION DATA SHEET**

# **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage (IN) or SHDN to GND                                           | 0.3V to 7.0V              |  |  |  |  |

|-----------------------------------------------------------------------------|---------------------------|--|--|--|--|

| SW to GND.                                                                  | 0.3V to $(V_{IN} + 0.3V)$ |  |  |  |  |

| V <sub>FB</sub> to GND                                                      | 0.3V to +2V               |  |  |  |  |

| SW Peak Current (Internally Limited)                                        |                           |  |  |  |  |

| Operating Temperature Range                                                 | 40°C to +125°C            |  |  |  |  |

| Storage Temperature Range, T <sub>A</sub>                                   | 65°C to 150°C             |  |  |  |  |

| Maximum Junction Temperature 150°C                                          |                           |  |  |  |  |

| RoHS / Pb-free Peak Package Solder Reflow Temperature                       |                           |  |  |  |  |

| (40 seconds maximum exposure)                                               |                           |  |  |  |  |

| Note: Exceeding these ratings could cause damage to the device. All voltage | ges are with respect to   |  |  |  |  |

PACKAGE PIN OUT PVIN 📖 Ⅲ SW AVIN [ T PGND SHDN III Ⅲ AGND Ⅲ FB COMP III DU PACKAGE RoHS / Pb-free 100% Matte Tin Lead Finish

## THERMAL DATA

Ground. Currents are positive into, negative out of specified terminal.

**Plastic MSOP 8-Pin**

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{\text{JA}}$

206°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \ x \ \theta_{JA})$ . The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

| FUNCTIONAL PIN DESCRIPTION                                                             |                                                                                                                      |  |  |  |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                                                                                   | DESCRIPTION                                                                                                          |  |  |  |  |

| SW Inductor and commutation diode connection point. Connects to internal MOSFET drain. |                                                                                                                      |  |  |  |  |

| AGND                                                                                   | Analog circuit ground providing bias for IC operation.                                                               |  |  |  |  |

| FB                                                                                     | Feedback input for setting adjustable output voltage                                                                 |  |  |  |  |

| SHDN                                                                                   | Enable control input. Reduces quiescent current to 1μA. Pin 8, Output becomes high impedance.                        |  |  |  |  |

| PVIN                                                                                   | Unregulated supply voltage input connected to PMOS Source. Input range from +2.7V to 6.0V                            |  |  |  |  |

| COMP                                                                                   | Frequency Compensation of the overall loop is effected by placing a series R/C combination between COMP pin and GND. |  |  |  |  |

| AVIN                                                                                   | Unregulated supply voltage input. Input range from +4V to 6.0V                                                       |  |  |  |  |

| PGND                                                                                   | Power ground (return path for internal PMOS gate driver).                                                            |  |  |  |  |

# **Step-Down Regulator**

## **PRODUCTION DATA SHEET**

## **ELECTRICAL CHARACTERISTICS**

Specifications apply over junction temperature of:  $0^{\circ}\text{C} \le T \le 85^{\circ}\text{C}$  for  $V_{\text{IN}} = 5V$  (except where otherwise noted). Typical values are at  $T_A = 25^{\circ}\text{C}$ .

| Parameter Syml                 |                     | Test Conditions                                               |            | Min                 | Тур   | Max                 | Units |

|--------------------------------|---------------------|---------------------------------------------------------------|------------|---------------------|-------|---------------------|-------|

| Operating Range                | $V_{IN}$            | Functional operation guaranteed by design                     |            | 3.5                 |       | 6.0                 | V     |

| Output Voltage Range           | V <sub>OUT</sub>    | Closed loop operating range                                   |            | $V_{FB}$            |       | 0.95*VIN            | V     |

| Feed Back Threshold            | V <sub>FBT</sub>    | $4V \le V_{IN} \le 6V$                                        |            | 1.146               | 1.170 | 1.193               | V     |

| FB Input Current               | I <sub>FB</sub>     | V <sub>FB</sub> = 1.2V                                        |            |                     | 300   | 500                 | nA    |

| EA Drive Comment (COMP Div)    | I <sub>SOURCE</sub> | V <sub>FB</sub> -125mV of Overdrive, V <sub>COMP</sub> = 2.5V |            | 10                  | 16    |                     | μΑ    |

| EA Drive Current (COMP Pin)    | I <sub>SINK</sub>   | V <sub>FB</sub> +125mV of Overdrive, V <sub>COMP</sub> = 2.5V |            | 10                  | 16    |                     | μΑ    |

| EA Outside Outside (OOMB Bid)  | <b>1</b> ,,         | VOL, Sinking 10μA                                             |            |                     | 95    |                     | mV    |

| EA Output Swing (COMP Pin)     | V <sub>EA OUT</sub> | VOH, Sourcing 10μA                                            |            |                     | 4.86  |                     | V     |

| Quiescent Operating Current    | IQ                  | Pin 2 Supply Current                                          |            |                     | 250   | 400                 | μΑ    |

| Class (Chatdous Made) Carret   | IQVIN <sub>SD</sub> | V <sub>SHDN</sub> = 0V, SW Pin open                           |            |                     |       | 1                   | μA    |

| Sleep (Shutdown Mode) Current  | IQVINSD             | V <sub>SHDN</sub> = 0V, SW grounded                           |            |                     | 2     | 5                   | μA    |

| Shutdown Input Bias Current    | I <sub>SD_IB</sub>  | SHDN = GND or SHDN = 5V                                       |            | -100                |       | 100                 | nA    |

| 0                              | V <sub>SD</sub>     |                                                               | Device Off |                     |       | 0.2*V <sub>IN</sub> | V     |

| Shutdown Voltage Threshold     |                     |                                                               | Device On  | 0.8*V <sub>IN</sub> |       |                     | V     |

| P-Channel Switch ON Resistance | R <sub>DS(ON)</sub> | I <sub>SW</sub> = 0.5A                                        |            |                     | 0.53  | 0.8                 | Ω     |

| Maximum Duty Cycle             | D                   | I <sub>sw</sub> = 0.5A (assured by design, not ATE tested)    |            | 80                  | 100   |                     | %     |

| SW Leakage Current             | I <sub>LEAK</sub>   | И                                                             |            |                     | 1     | 5                   | μΑ    |

| P-Channel Current Limit        | I <sub>LIM</sub>    |                                                               |            | 900                 | 950   |                     | mA    |

| Frequency                      | F <sub>OP</sub>     |                                                               |            | 0.80                | 1.07  | 1.2                 | MHz   |

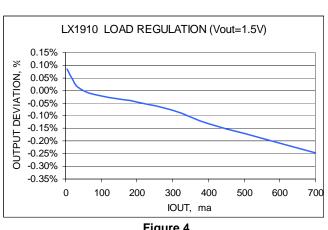

| Closed Loop Load Regulation    | Load Reg            | $V_O = 1.5V$ , 5mA $\leq I_O \leq$ 700mA, ckt figure 3        |            |                     | 0.35  | 0.5                 | % Vo  |

| Thermal Shutdown               | T <sub>SD</sub>     |                                                               |            | 125                 | 150   |                     | °C    |

# Step-Down Regulator

**PRODUCTION DATA SHEET**

## Step-Down Regulator

**PRODUCTION DATA SHEET**

#### **APPLICATION NOTE**

#### **FUNCTIONAL DESCRIPTION**

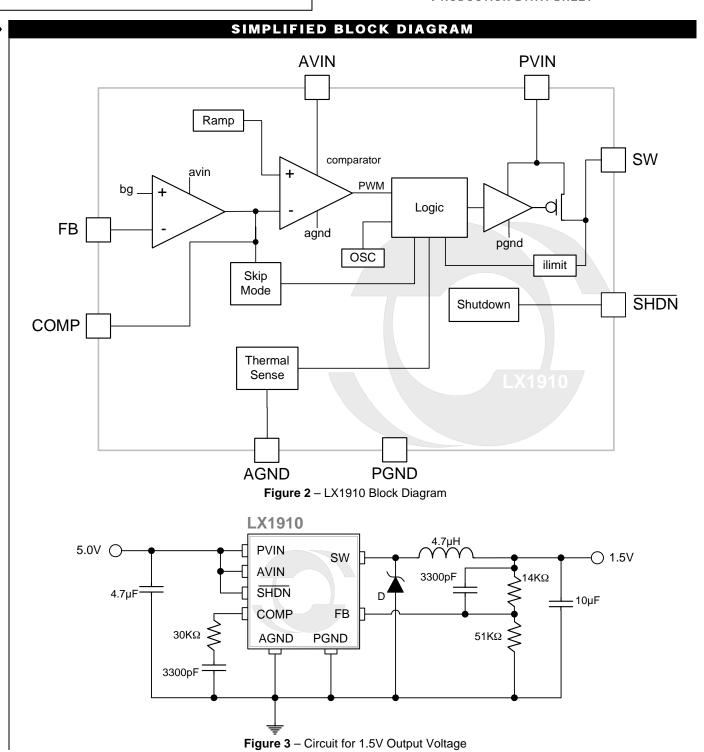

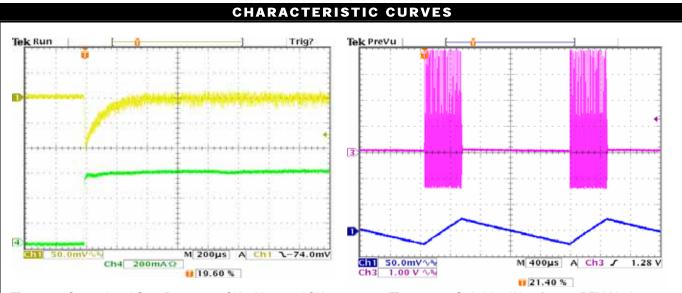

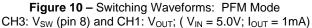

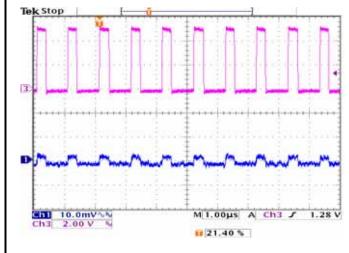

The LX1910 implements a PFM / PWM architecture that improves power management efficiency across the output load range.

#### **OUTPUT VOLTAGE PROGRAMMING**

Resistors R1 and R2 program the output voltage. An optional capacitor  $C_X$  may be inserted across R1 to improve the transient response (see Figure 1). The value of R2 should be less than  $100 K \Omega$ . The value of R1 can be determined using the following equation, note  $V_{REF}$  is also referred to as  $V_{FBT}$ .

$$R1 = R2 \left[ \left( \frac{V_{OUT}}{V_{REF}} \right) - 1 \right]$$

#### DESIGN EXAMPLE:

Let R2 equal 50K and the required  $V_{OUT}$  equal to 3.0V.

$$R1 = 50K \left[ \left( \frac{3V}{1.17} \right) - 1 \right] = 78K\Omega$$

#### **DIODE SELECTION**

A Schottky diode is recommended for use with the LX1910 because it provides fast switching and superior reverse recovery performance. The *Microsemi* UPS5817 (20V @ 1A) makes an effective choice for most applications.

#### INDUCTOR SELECTION

Selecting the appropriate inductor type and value ensures optimal performance of the converter circuit for the intended application. This selection process requires the designer to make trade-offs between circuit performance and cost. A primary consideration requires the selection of an inductor that will not saturate at the peak current level. Other considerations that affect inductor choice include EMI, output voltage ripple, and overall circuit efficiency. The inductor that works best depends upon the application's requirements. Further, some experimentation with actual devices in-circuit is typically necessary to make the most effective choice.

The LX1910 allows for a broad selection of inductor values and choosing a value between  $2.2\mu H$  and  $30\mu H$  supports a majority of applications. Selecting a larger inductor value can increase efficiency and reduce output voltage ripple. Smaller inductors typically provide smaller package size (critical in many portable applications) at the expense of increasing output ripple current. Regardless of inductor value, selecting a device manufactured with a ferrite-core produces lower losses at higher switching frequencies and thus better overall performance.

#### CAPACITOR SELECTION

To minimize ripple voltage, output capacitors with a low series resistance (ESR) are recommended. Multi-layer ceramic capacitors with X5R or X7R dielectric make an effective choice because they feature small size, very low ESR, a temperature stable dielectric, and can be connected in parallel to increase capacitance. Typical capacitance values of 4.7 to 30 $\mu$ F have proven effective. Other low ESR capacitors such as solid tantalum, specialty polymer, or organic semiconductor, make effective choices provided that the capacitor is properly rated for the output voltage and ripple current. Finally, choose an input capacitor of sufficient size to effectively decouple the input voltage source impedance (e.g.,  $C_{IN} \ge 4.7 \mu$ F).

## **LAYOUT CONSIDERATIONS**

The high peak currents and switching frequencies present in DC/DC converter applications require careful attention to device layout for optimal performance. Basic design rules include: (1) maintaining wide traces for power components (e.g., width > 50mils); (2) place  $C_{\rm IN},\,C_{\rm OUT},$  the Schottky diode, and the inductor close to the LX1910; (3) minimizing trace capacitance by reducing the etch area connecting the SW pin to the inductor; and (4) minimizing the etch length to the FB pin to reduce noise coupling into this high impedance sense input. Other considerations include placing a 0.1uF capacitor between the LX1910  $V_{\rm OUT}$  pin and GND pin to reduce high frequency noise and decoupling the  $V_{\rm IN}$  pin using a  $0.1\mu{\rm F}$  capacitor.

# Step-Down Regulator

**PRODUCTION DATA SHEET**

## CHARACTERISTIC CURVES

Figure 4

Figure 5

Figure 7

## **Step-Down Regulator**

**PRODUCTION DATA SHEET**

Figure 9– Output Load Step Response: CH1:  $V_{OUT}$  and CH4:  $I_{OUT}$ ; Condition:  $V_{IN} = 5.0V$ ;  $I_{STEP} = 50$  to 600mA

Figure 11 – Switching Waveforms: PWM Mode CH3:  $V_{SW}$  (pin 8) and CH1:  $V_{OUT}$ ; ( $V_{IN} = 5.0V$ ;  $I_{OUT} = 10$ mA)

# Step-Down Regulator

**PRODUCTION DATA SHEET**

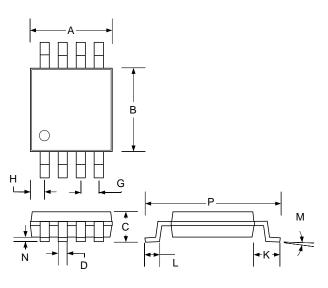

## PACKAGE DIMENSIONS

**DU** 8-Pin Miniature Shrink Outline Package (MSOP)

| Dim   | MILLIMETERS |          | INCHES    |           |  |  |

|-------|-------------|----------|-----------|-----------|--|--|

| Dilli | MIN         | MAX      | MIN       | MAX       |  |  |

| Α     | 2.85        | 3.05     | .112      | .120      |  |  |

| В     | 2.90        | 3.10     | .114      | .122      |  |  |

| С     | _           | 1.10     | _         | 0.043     |  |  |

| D     | 0.25        | 0.40     | 0.009     | 0.160     |  |  |

| G     | 0.65        | 0.65 BSC |           | 0.025 BSC |  |  |

| Н     | 0.38        | 0.64     | 0.015     | 0.025     |  |  |

| J     | 0.13        | 0.18     | 0.005     | 0.007     |  |  |

| K     | 0.95 BSC    |          | 0.037 BSC |           |  |  |

| L     | 0.40        | 0.70     | 0.016     | 0.027     |  |  |

| M     | 3°          |          | 3°        |           |  |  |

| N     | 0.05        | 0.15     | 0.002     | 0.006     |  |  |

| Р     | 4.75        | 5.05     | 0.187     | 0.198     |  |  |

**Note:** Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm(0.006") on any side. Lead dimension shall not include solder coverage.

## NOTES

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.